# 介绍

## PCI Express™ 测量

**Tektronix**

Enabling Innovation

## PCI Express™ 测量介绍

► 入门手册

### 目录

|                                  |    |

|----------------------------------|----|

| 检验、调试和一致性测试 PCI EXPRESS 设计 ..... | .3 |

| 结构和规范概述 .....                    | 4  |

| 物理层的特点 .....                     | 5  |

| 物理层一致性测试：数字领域的模拟视图 .....         | 8  |

| 检验和一致性测量 .....                   | 8  |

| 幅度测量 .....                       | 9  |

| 定时测量 .....                       | 9  |

| 抖动测量 .....                       | 10 |

| 实时眼图和模板测试 .....                  | 14 |

| 噪声及其对抖动的影响如何？ .....              | 14 |

| 频域测量 .....                       | 15 |

| 接收机灵敏度和抖动容限测量 .....              | 16 |

| 在模拟测量中保证信号保真度 .....              | 17 |

| 连接串行被测设备 .....                   | 18 |

| 模拟采集考虑因素 .....                   | 22 |

| PINPOINT® 触发和数据解码工具调试链路 .....    | 25 |

| 定位和触发误码 .....                    | 25 |

| 检验和触发 8B/10B 符号 .....            | 26 |

| 数字检验和调试 .....                    | 27 |

| 探测意味着进行适当连接 .....                | 28 |

| 采集信号：从分组信号到并行信号 .....            | 30 |

| 触发是调试效率的关键 .....                 | 30 |

| 分析结果 .....                       | 31 |

| PCI EXPRESS 测量解决方案概述 .....       | 33 |

| 示波器 .....                        | 33 |

| 实时 (RT) 示波器 .....                | 33 |

| 等时 (ET) 取样示波器 .....              | 34 |

| 信号源 .....                        | 34 |

| 逻辑分析仪 .....                      | 35 |

| 小结 .....                         | 35 |

## 检验、调试和一致性测试 PCI Express 设计

随着第一代 (Gen1) PCI Express 部署的顺利进行，业内已经成功地实现了各种元器件、系统和板卡。现在，市场上提供了拥有 PCI Express 插槽的主板和笔记本电脑及可以广泛选择的采用这种新型扩展槽的图形处理器单元 (GPUs) 和网卡。在短短几年内成功地部署 Gen1 设备在一定程度上可以归功于厂商实验室及 PCI-SIG (PCI 特殊利益集团) 赞助的接插集会 (plug fests) 对设备测试作出的巨大投入。PCI-SIG 已经成功地实现了 PCI Express 板卡电气机械规范 (CEM) Rev1.0a 版的一致性和互操作能力测试，多家厂商已经成功地入选 SIG 集成商清单。在 Rev1.0a 部署过程中，很明确必需对规范作出部分改动（主要是物理层），以保证不同 PCI-E 设计之间更加可靠地通信。基本规范和 CEM 规范 Rev1.1 现在已经植入这些变动，SIG 已经开始在讨论会中根据 Rev1.1 规范进行测试。PCI-SIG 正在审核第二代基本规范和 CEM 规范及第一个能够通过外设对总线扩容的布线规范。Gen2 把基本信令频率提高了一倍，从 2.5 Gb/s 提高到 5 Gb/s，在系统设计中增加电缆则进一步提高了复杂程度。这无疑会给设备的检验和一致性测试带来部分新的挑战。

除了入选集成商清单要求的 PCI-SIG 合格/不合格指标外，各厂商还必须在许多条件下检验自己的设计。例如，您的设计可能在讨论会上、在测试夹具的电源条件下、在室温中通过了测试，但在温度和电源条件变化时会发生什么情况呢？如果把您的设备与系统中另一个厂商的设备插在一起、另一条总线导致您的设备失效会怎么样呢？

本读物介绍了 PCI Express 测试的各个方面，包括检验、调试和一致性测试及基本原理、测量技术及保证成功设计所需的工具。不管是已经成功地处理 Gen1 设备、着手测试 Gen2 设备，还是刚刚进入 PCI Express 领域，本读物都可以帮助您了解 PCI Express 的结构、规范和测量解决方案。

### PCI Express 开发人员的部分有用链接

泰克 PCI Express 主页：

[http://www.tek.com/Measurement/applications/

serial\\_data/pci\\_express.html](http://www.tek.com/Measurement/applications/serial_data/pci_express.html)

PCI-SIG 一致性测试主页：

[http://www.pcisig.com/specifications/pciexpress/

compliance/](http://www.pcisig.com/specifications/pciexpress/compliance/)

## PCI Express™ 测量介绍

▶ 入门手册

▶ 图 1. PCI Express 链路的各个层

▶ 图 2. PCI Express PHY 链路实现方案

| 信号速率                | 按通路宽度划分的原始位速率 (Gb/s) |    |    |     |     |

|---------------------|----------------------|----|----|-----|-----|

|                     | X1                   | X4 | X8 | X16 | X32 |

| 第一代 – 每条通路 2.5 Gb/s | 2.5                  | 10 | 20 | 40  | 80  |

| 第二代 – 每条通路 5 Gb/s   | 5                    | 20 | 40 | 80  | 160 |

▶ 原始位速率

### 结构和规范概述

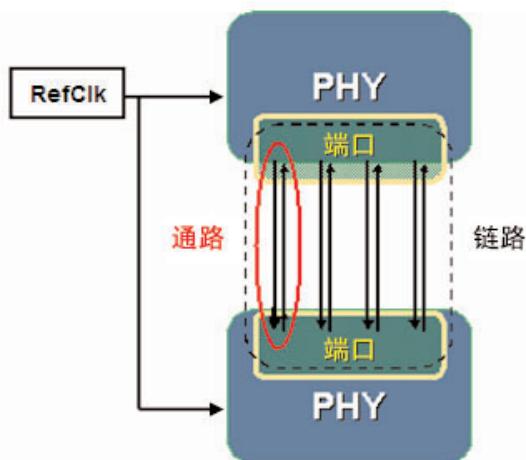

与任何串行数据标准一样，PCI Express 可以视作“由多个层组成的堆栈”，如图 1 所示。各个层相互通信，同时相互缓冲相邻层的操作。

堆栈中包括通过传输介质传送电子信号的物理层；把信号解释为有意义的数据的逻辑层；传输层等等。每个层有相应标准和一致性测试程序。

图 1 显示了串行数据链路的物理层 (PHY) 划分情况。PHY 与协议堆栈的高层隔开，涵盖了两个层：逻辑层和电气层。PHY 的物理部分处理高速串行分组交换和电源管理机制。

PHY 的逻辑层处理复位、初始化、编码和解码。电气子模块和逻辑子模块还可能包括特定标准功能。

在构成 PHY 的两个模块中，每个模块都有独特的测试要求。在进行电接口测量时，数据眼图和系统参考时钟的模拟波形特点处于优先位置。在逻辑层中，必须解释数字分组，提取嵌入式时钟，等等。

图 2 显示了 4X PCI Express 链路的典型物理层拓扑。PCI Express 链路由称为通路的双单工传输方案集合组成。每条通路有一个发送和接收差分对，每条通路共有四根走线。

▶ 图 3. PCI Express 分组的各个层

每条通路的发送速率为 2.5 Gb/s (Gen1) 或 5 Gb/s (Gen2)。

规范支持 X1, X4, X8, X16 和 X32 的通路宽度配置。链路的原始位速率是每条通路基本位速率的倍数。

在通过嵌入时钟发送数据时，发送电路和接收电路共享一个参考时钟 (RefClk)，因此其 PLL 电路可以跟踪什么时候使用扩频时钟 (SSC)，如图 2 所示。SSC 用来最大限度地降低来自计算机主板的电磁辐射。参考时钟以 30-33 kHz 的频率在 100 MHz 和 99.5 MHz 之间调制。

#### 分组化数据

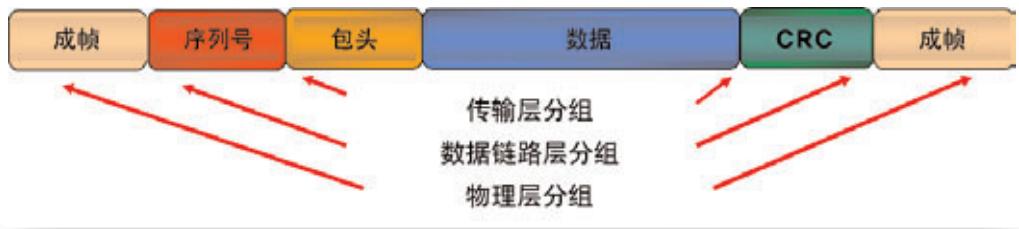

PCI Express 数据从多个层进行分组化，如图 3 所示。

- ▶ PHY 的逻辑子模块增加了成帧，表明每个分组的开头和结尾。这个子模块负责传输和对准符号。

- ▶ 数据链路层提供错误校验和重试服务。分组中包括 ACK (确认)、电源管理信息等等。

- ▶ 传输层处理初始化、指令生成和处理以及流量控制。

#### 物理层的特点

物理层是上面描述的分组化差分信号的载体。从功能角度看，物理层结构为以二进制信号形式表示的数据提供了一条路径，其中包括电路板走线、连接器和电缆。在使用示波器调试、检验和一致性测试设计时，这些二进制信号是物理层测量对象。

在 PCI Express 内部，可以定义多种不同的总线配置。图 4、图 5 和图 6 说明了三种典型的机械实现方式。

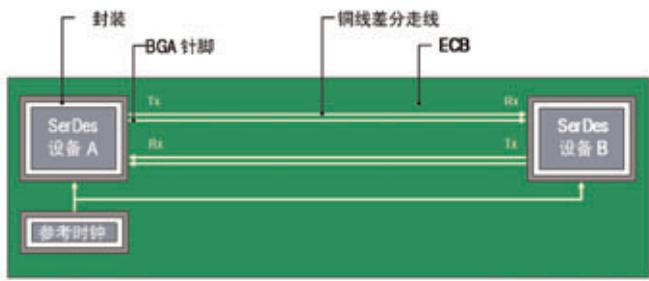

PHY 的各条通路都由发送和接收差分对组成。发送对及传输介质通常称为通道。在通道内部，信号可以流经三种基本铜线路径。

## PCI Express™ 测量介绍

### ▶ 入门手册

#### 芯片到芯片通路（图 4）

芯片到芯片通路通常位于作为传输介质的蚀刻电路板 (ECB) 上。典型应用是系统主板上的 PCI Express 总线，这里需要从一台设备向另一台设备传送大量的数据。

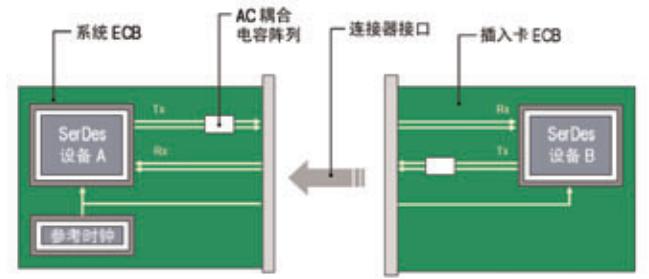

#### 板卡到板卡通路（图 5）

当连接器是通路的一部分时，如在插件应用中，规范要求链路的发送一侧有 AC 耦合电容器。这消除了发送设备和接收设备之间潜在的共模偏置不匹配。低成本链路可能会在 FR4 电路板上采用长走线及采用低价连接器，这两者都会增加抖动、串扰及布局导致的潜在不平衡。台式机和服务器应用的 CEM 规范及笔记本电脑等移动设备的 PCMCIA（个人电脑内存条国际协会）ExpressCard 文件中提供了这种配置的测试点。

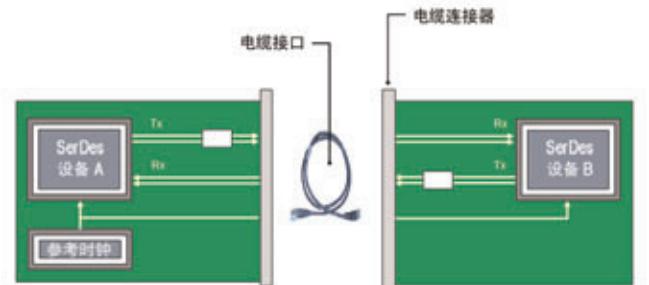

#### 板卡到电缆通路（图 6）

在通路中引入电缆连接还增加了另一个损耗和抖动来源。电缆连接的 PCI Express 已经进入早期开发阶段。但是，PCI Express 电缆规范草案中为电缆的发送一侧和接收一侧定义了测试点。在这种拓扑中，参考时钟和三种其它边带信号沿着电缆中心线对及 X16 发送机和接收机对传送。

#### 不要忘了参考时钟 (RefClk)

除高速串行数据信号路径外，测试参考时钟 (RefClk) 的信号完整性也非常关键。参考时钟参数包括在 Gen1 的 CEM 规范中，是 Gen2 基本规范的主体。从 Rev1.0a 和 Rev1.1 起，Gen1 规范变化在很大程度上是由于参考时钟抖动对数据眼图闭合的影响推动的。

▶ 图 4. 芯片到芯片通路

▶ 图 5. 通路的连接器部分

▶ 图 6. 通路的电缆连接部分

▶ 图 7. PCI Express 中的测试点

### 一致性测试和互操作能力

一致性和互操作能力测试是任何标准成功的关键，特别是在标准的早期阶段，这一阶段的细节还在变动，理解可能会有所变化。

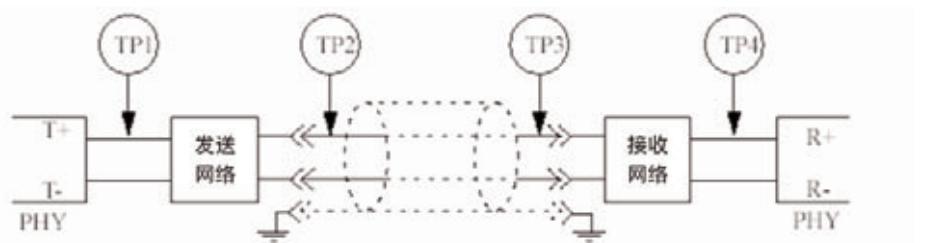

PCI Express 标准解决了发送和接收损耗预算的重要问题，它们还定义了必须执行系统级测试的一致性测试点。从本质上讲，一致性测试点是系统各个器件（通常来自不同的厂商）必需互操作的点。图 7 汇总了由互连的多个单元组成的整个系统中部分典型的互操作能力点。在 PCI Express 中，基本规范中规定了 TP1 和 TP4，CEM 和布线规范中规定了 TP2 和 TP3，具体取决于接口配置。

这些点显示为测试点，因为标准中把它们专门称为测试仪器的探测连接点。对板卡到板卡连接或板卡到电缆连接，非常重要的是要了解一致性测试点是测量中包括还是不包括连接器。注意，一致性测试点可能没有位于连接器中间，因为插好的连接器和没插好的连接器的性能会有相当大的差异。此外，测量中的任何 ECB 通道长度或电缆损耗都会影响结果。在 Gen1 中，PCI Express 规范（和 PCI-SIG 测试程序）在很大程度上忽略了测试夹具和仪器电缆的损耗廓线（或把其包括在测试余量中）。在 5 Gb Gen2 中，规范要求考虑这些问题。PCI Express 的另一个趋势是更加明确地定义在系统级测试接收机灵敏度时使用的程序。在 Gen1 中，接收机灵敏度测试定义主要留给开发人员自己理解。

## PCI Express™ 测量介绍

### ▶ 入门手册

#### 物理层一致性测试：数字领域的模拟视图

PCI Express 在数字领域运行，但大部分一致性测试任务由模拟测量组成。为什么呢？这难道不是数字数据吗？

回答可以是“不是”，但有一些非常重要的例外情况。数字信号存在的环境包括分布式电容、噪声、电源变化、串扰及其它各种不理想的条件。每种现象都会偏离“理想的”数字信号，有时会达到损害数据传送能力的程度。结果，规范规定了信号失真和劣化的极限。被测设备必须满足这些极限，才能被视为“符合规范”。标准中详细解释了测试条件和测试点。PCI-SIG 在一致性测试主页上提供了详细的一致性测试程序，包括特定仪器，有时甚至会包括仪器的型号。另外 PCI-SIG 还提供了信号质量测试 (SigTest) 软件。SigTest 针对系统和插件一致性测试点，在实时示波器捕获的波形数据上进行强制性信号完整性测量。

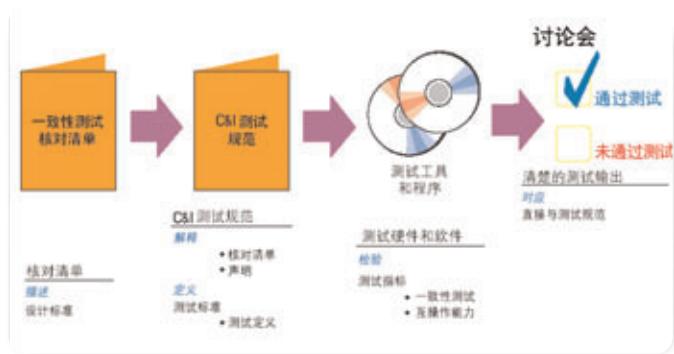

图 8 汇总了 PCI Express 的典型一致性测试流程。

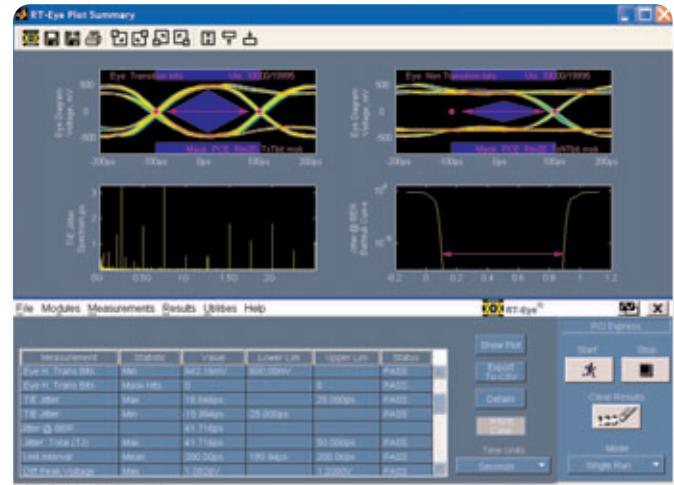

#### 采用 SigTest 还是采用 RT-Eye® 软件？

PCI Express 开发人员经常问的一个问题是：如果 SigTest 是免费的，并告诉我是否通过测试，那么为什么示波器上还需要使用其它分析工具呢？答案在于您对设计余量的信心有多高。泰克信号质量软件工具如 RT-Eye、TDSJIT3 和 JNB，为检验、调试和一致性测试设计提供了广泛的功能。在下面几节中我们将进一步对此进行介绍。

#### 一致性测试使用的测试夹具

一旦定义了测试点，必须开发测试夹具，提供探测附着点。PCI-SIG 为系统测试提供了一致性负载电路板 (CLB)，为插件测试提供了一致性基本电路板 (CBB)。PCMCIA 为笔记本系统发射机测试提供了系统发射机一致性测试卡。

▶ 图 8. PCI-SIG 一致性和互操作能力测试流程

#### 检验和一致性测量

PCI Express 基本规范包括发射机和接收机幅度、定时、抖动和眼图测量。这些测量通常称为信号完整性测量。另外还为通道定义了插入损耗、回波损耗和频域串扰。CEM 和布线规范在系统级一致性测试点定义了抖动和眼图余量，表示在接插集会 (plug-fests) 上执行的测试。通常使用自动测量/分析工具，加快这些测试的选择和应用速度。下面的列表封装了接插集会 (plug-fests) 要求执行的部分关键测量（以验证一致性和互操作能力）以及检验系统器件、保证满足规范所需的测量。

- ▶ 幅度测量

- ▶ 定时测量

- ▶ 抖动测量

- ▶ RT-Eye 眼图和模板测试

- ▶ 噪声和抖动

- ▶ 频域测量

- ▶ 接收机灵敏度和抖动容限测量

## 幅度测量

信号是否达到了能够可靠地通过传输介质传送及向接收电路传达正确的“1”或“0”的电压电平和可靠性？这些测试保证了信号拥有足够的幅度容限，能够在最坏情况下完成工作。

差分电压 – 峰到峰差分电压规范为保证收发机发送正确的电压水平提供了基础规范。它指定了最低发射机差分电压，以便在最坏情况的介质条件下（最大损耗）使规定的最低差分电压到达接收机。这保证了能够正确传送数据。PCIExpress 规范对差分峰值电压的规定如下：

$$VTX\text{-DIFF}_{p-p} = 2 * |VTX\text{-D+} - V_{TX\text{-D-I}}|, \text{ 在从数据信号中恢复时钟后从波形数据中测得}$$

注意，差分峰到峰电压不等于示波器菜单中看到的传统峰到峰指标。这通常会引起混淆。这一测量需要使用 PCI Express 特定算法。

去加重 – 这是“转换位”之后第二个位和后续位的幅度与“转换位”的幅度之比。去加重也称为预加重和平衡。去加重用于串行数据传输系统中，补偿“有损耗的”介质的频率特点，如台式电脑中使用的低成本 FR4 电路板和连接器。通过使转换位的幅度高于后续位，信号将以“睁开的眼图”到达接收机针脚。

共模电压测量 (**AC, DC**) – 发射机上的共模不平衡和噪声会在差分信号中产生不希望的效应。通常要把差分信号分离成单端成分，以诊断这些问题。这种技术还可以发现可能会耦合到差分对一侧、但不会耦合到另一侧的串扰和噪声效应。

波形眼高 – 眼高是幅度域中数据眼图的张开程度。它提供了非常重要的测量数据，因为它提供了接收机电路的实际样点。它在 .5 单位间隔 (UI) 点上测得，其中由恢复的时钟定义 UI 定时参考。如需与眼图有关的更详细信息，请参阅“眼图”部分。

## 定时测量

信号是否有定时变化？其转换是否足够快，可以保留信号希望提供的关键数据值？这些测试要求测量工具集部分提供完善的性能，检测分布式电容、串扰等因素导致的畸变和信号劣化。

单位间隔和位速率 – 通过在大量的连续周期上考察嵌入式时钟的平均测量结果，可以测量嵌入式时钟的频率变化。在 PCI Express 中，如果平均值偏离规定值（没有 SSC）大于百万分之 300 (PPM)，那么设备不符合规范。

## PCI Express™ 测量介绍

### ► 入门手册

**上升/下降转换时间** – 在进行发射机测量时，测量精确转换时间使用的工具最为重要。Gen2 PCI Express 允许的最小发射机上升时间是 30 ps (使用 20-80% 参考电平测得)。上升时间太快会导致 EMI 问题，上升时间太慢会导致数据错误。

**波形眼宽** – 波形眼宽是指一个间隔减去测得的合成抖动；其中抖动在 OV 差分参考电平上测得。如需与眼图有关的详细信息，请参阅“眼图”部分。

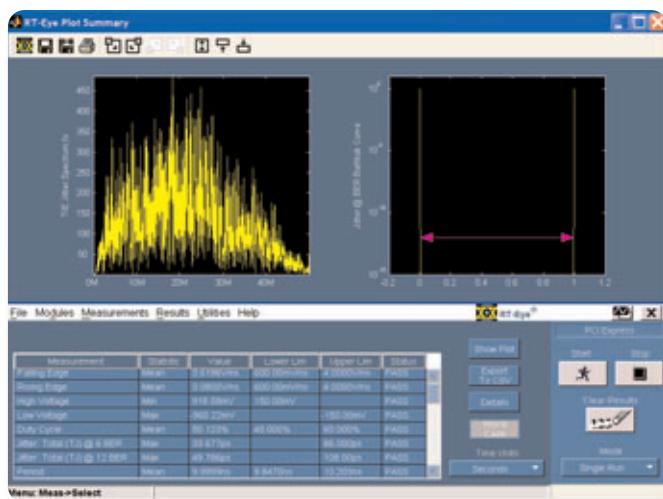

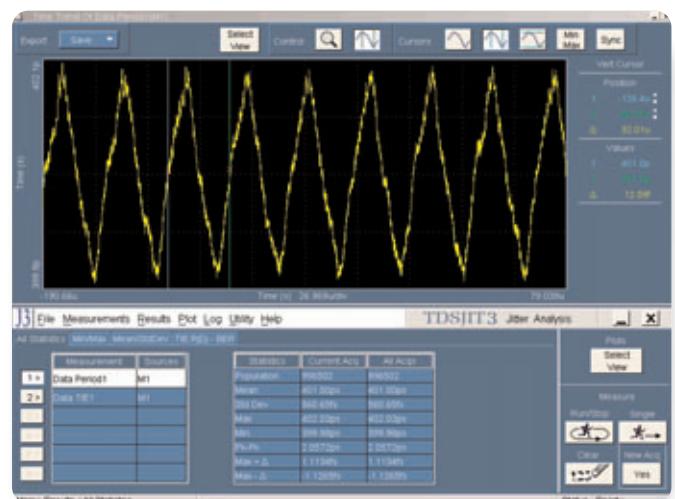

### 抖动测量

抖动测量方法一直是 PCI Express 开发人员和规范编写人员讨论的主要话题。本节介绍了 PCI Express 中抖动分析的演进情况，其适用于规范中的测量项目。

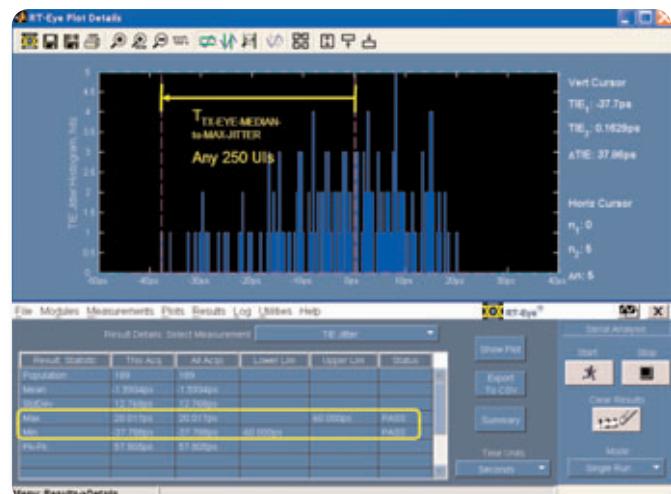

**中值-最大值-抖动** – 最初的 Gen1 PCI Express 规范 (Rev1.0a) 规定在任意 250 个连续位上测量“中值-最大值-抖动”。中值-最大值-抖动是使用中值作为定时参考，时间间隔误差 (TIE) 正方向或负方向的最大偏差。图 9 显示了怎样在 250 个单位间隔上从 TIE 直方图中测量中值-最大值-抖动。测量极限 (图 9 中以高亮度显示) 放在 TIE 的最大值和最小值周围，表示中值-最大值-抖动规范。

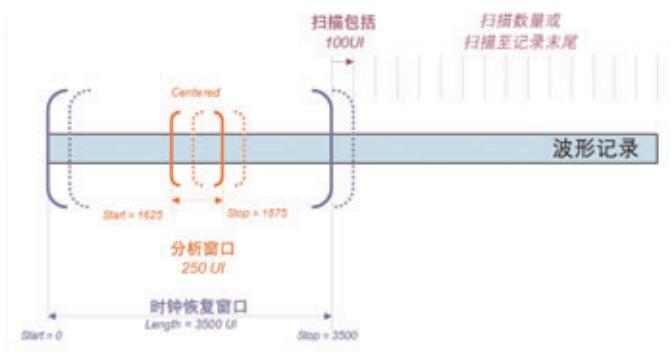

时钟恢复方法需要取 3500 个连续位的中间值，然后在时钟恢复窗口中心应用 250 位分析窗口。这种分析方法为评估相位校准接收机行为提供了一种良好的模型。3500:250 方法近似于抖动的三阶滤波函数 (-60 dB/decade 衰减，截止频率为 1.5 MHz)。它滤除低频 SSC，不管 SSC 是否打开，均可以在系统上使用这一技术。

► 图 9. 在任意 250 UI 上 Rev1.0a 中值-最大值-抖动

► 图 10. 3500:250 窗口使用的 SmartGating

泰克已经在拥有 SmartGating 功能的 RT-Eye 软件中普及这种方法。SmartGating (图 10) 允许用户指定时钟恢复和分析窗口，在时间间隔误差测量上表示不同的有效滤波函数。ClockRecovery: Analysis 窗口还可以设置成使用用户定义的增量扫描波形。通过设置 3500:250 窗口，以 100 UI 增量扫描波形，可以获得与 PCI-SIG 的 SigTest 软件相对应的结果。

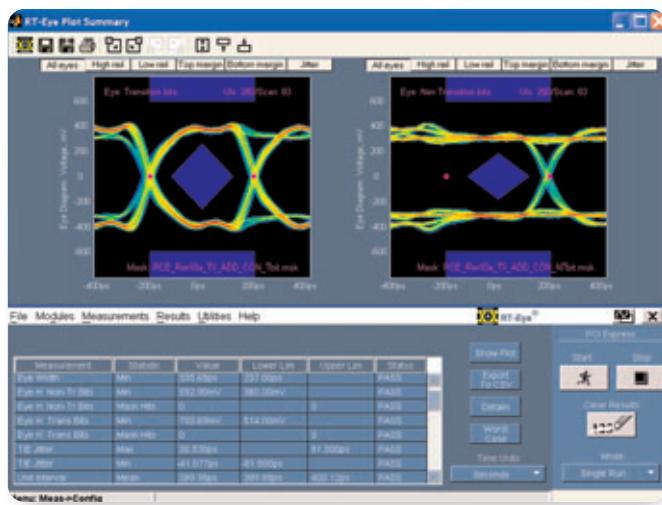

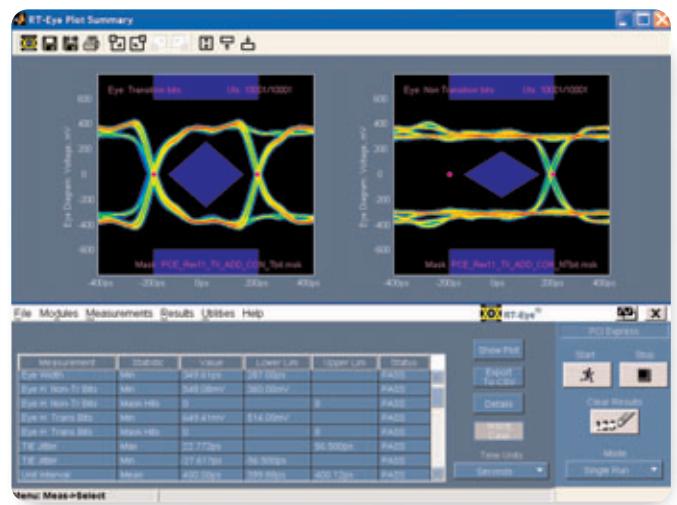

▶ 图 11a. 使用 Gen1 (Rev1.0a) 方法测试插卡

在测试了实际环境设备后，业内确定需要更强健的抖动规范，以保证互操作能力。新的规范 (Rev1.1) 独立于参考时钟相位抖动测量发射机抖动。它通过对抖动数据应用一阶 (1.5 MHz 拐角频率时的衰减为 -20 dB/decade) 滤波函数，并通过对发射机设备的参考时钟输入应用“干净的时钟”，来实现时钟恢复。Rev1.1 规范规定在 100 万单位间隔的总量上测量抖动，1.0a 规范则没有明确规定这一点，而是指定“在任意 250 个单位间隔”上的抖动。对发射机器件和插卡测试，一致性测试中使用新的 Rev1.1 发射机抖动规范。对启动 SSC 的系统，一致性测试中要观察 Rev1.0a 规范中的原始三阶函数。

▶ 图 11b. 使用 Gen1 (Rev1.1) 方法测试插卡

图 11 是使用这两种规范测试的插卡实例。图 11a 是采用 3500:250 方法通过 Rev1.0a 一致性基本电路板 (CBB) 测试的，其中启用了扫描模式。图 11b 则采用一阶软件 PLL 通过 Rev1.1 CBB 测试同一设备。可以看出，Rev1.1 拥有更严格的抖动容限（更宽的模板），但是由于对 DUT 应用干净的时钟，测得的 TIE 抖动要小得多（中值-最大值-抖动是 27.6 ps，而不是 41.07 ps）。最终结果是在这两种方法下设备都通过了测试。

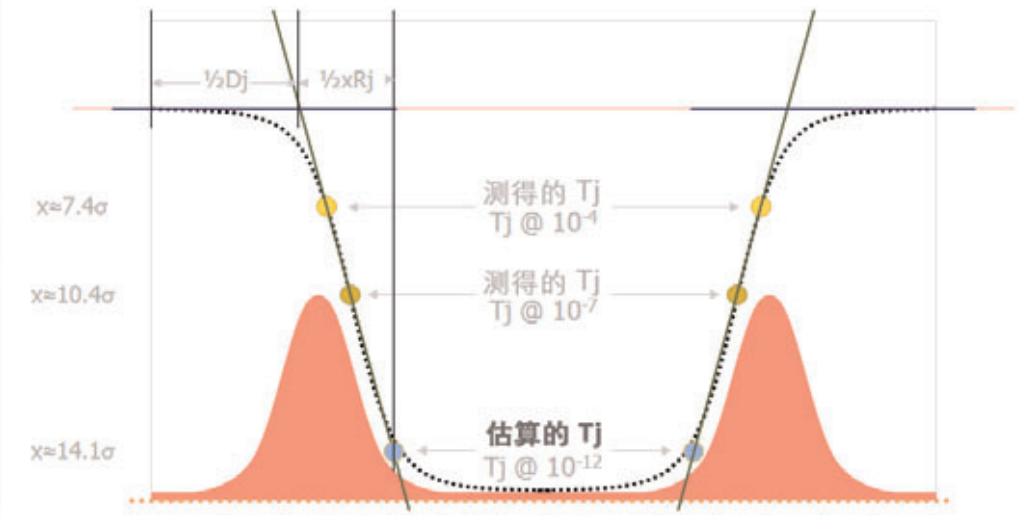

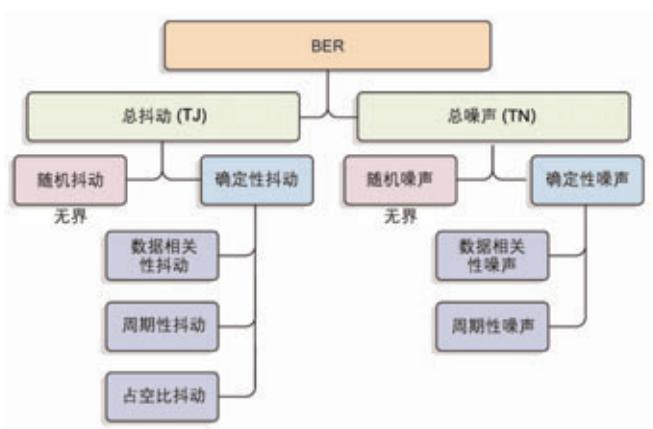

**假设双模分布 (Dual-Dirac)，在两种 BER 上测量，

对各点拟合曲线，斜率为 Rj，截距是 Dj**

▶ 图 12a. 估算抖动使用的 Dual-Dirac 模型

**Dual-Dirac 抖动** – 如中值-最大值抖动测试中所述，Gen1 PCI Express 规范依赖 TIE 直方图方法测量抖动。Gen2 规范则更进一步，使用 Dual-Dirac 模型指定抖动。这种方法估算总抖动 ( $T_j$ )、随机抖动 ( $R_j$ ) 和确定性抖动 ( $D_j$ )，如图 12a 所示。业内已经开发了多种采集和分析技术，推导 Dual-Dirac 曲线。其中一种方法是在扩展的时间周期上构建时间间隔误差 (TIE) 直方图，这种方法主要用于时间间隔分析仪 (TIA) 中。可以测量两种不同 BER 水平上的  $T_j$ ，如  $10^{-4}$  和  $10^{-7}$  BER。一旦测得这些值，可以画一条直线，估算  $10^{-12}$  BER 时的  $T_j$ 。然后可以画出斜率和截距，导出  $R_j$  和  $D_j$  值。与之相对应，采用 TDSJIT3 或 RT-Eye 的实时 (RT) 示波器使用“抖动频谱测量方法”估算  $10^{-12}$  BER 时的  $T_j$ 。然后使用相同的方法测量  $10^{-9}$  BER 时的  $T_j$ 。一旦确定了这两种水平上的  $T_j$ ，可以确定同一条直线，估算

▶ 图 12b. 使用 Gen2 Dual-Dirac 方法进行发射机测试

$R_j$  和  $D_j$ 。抖动频谱方法（由泰克开发）包括一种把随机抖动成分与确定性抖动成分分开的专利技术。

▶ 图 13. 差分参考时钟一致性测试

▶ 图 14. 采用 TDSJIT3 软件的扩频廓线

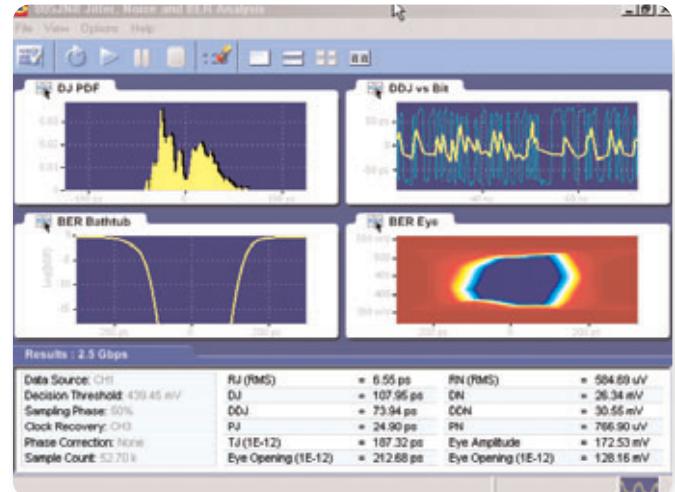

频谱方法一直与测量抖动使用的 BERT 扫描方法相关。它已经被串行数据开发人员广泛采用，因为它可以精确地估算抖动，而所需的时间只是基于直方图的技术的几分之一。图 12b 显示了使用这种技术测试 Gen2 PCI Express 发射机的结果。

**参考时钟 (RefClk) 抖动** – 如前所述，Rev1.1 规范要求独立测量发射机抖动和参考时钟抖动。由于各自 PLL 的传函变化、传输延迟差异及位于接收机中的 CDR 的跟踪带宽，PCI Express 发射机和接收机会表现出不同的相位抖动跟踪行为。必需规定参考时钟在发射机和接收机最坏情况组合下将传播和滤波的抖动量。这可以通过 Rev1.1 CEM 规范和 Gen2 基本规范中指定的抖动模板功能完成。另外

还指定了  $10^{-6}$  和  $10^{-12}$  BER 时允许的抖动。图 13 是使用 RT-Eye 软件对参考时钟设备应用要求的 Rev1.1 CEM 规范后获得的结果。除总抖动外，这一工具还测量转换速率、高低电压和时钟占空比等参数。

**SSC 廓线** – 除时钟的信号完整性外，PCI Express 规范还规定时钟频率可以扩展 -0.5%，它以 30-33 kHz 的调制频率从基本数据速率扩展。这会导致数据周期从 400 ps 扩展到 402 ps。为从数据信号中获得 SSC 的廓线，必须测量和滤波数据周期。TDSJIT3 高级抖动分析软件用来分析高性能实时示波器捕获的长记录。图 14 显示了在数据周期测量中应用 5 MHz 低通滤波器的结果，以使用一致性负载电路板 (CLB) 检验主板上的 SSC 廓线。

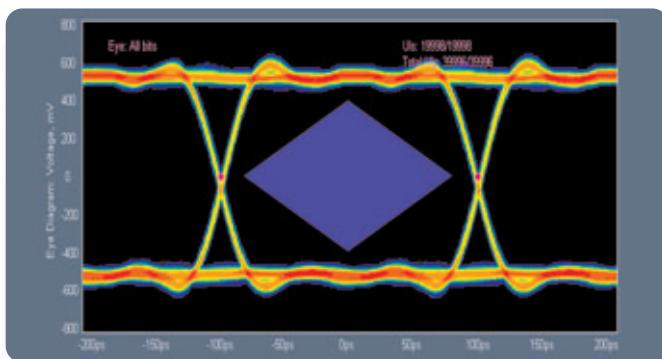

## 实时眼图和模板测试

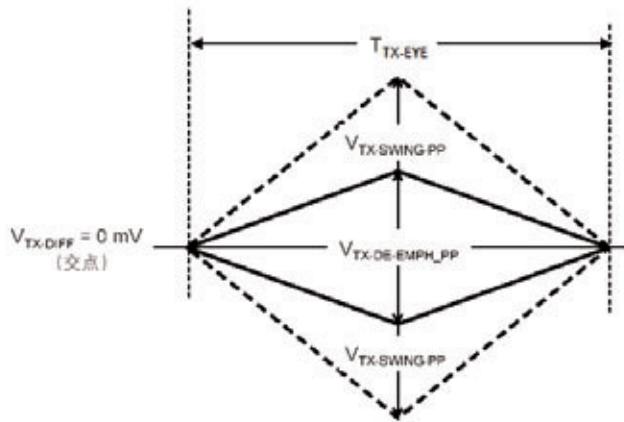

“眼图”是把一系列数据波形重叠在一起得到的示波器画面，它为确定 PCI Express 发射机信号的质量提供了重要工具。为生成眼图，必需从数据中恢复时钟，以同步传输随机码型、伪随机码型或一致性码型的数据流。泰克以软件时钟恢复重叠实时波形数据的专利技术是泰克实时示波器上运行的 RT-Eye (实时眼图) 软件的基础。如前所述，有多种技术可以恢复时钟，具体取决于被测设备和规范版本。除恢复时钟外，发射机和互连测试点要求跳变位与去加重位分离，并在每种位类型上执行模板测试。图 15 显示了规范中出现的模板几何形状定义。图 11 和图 12 说明了怎样使用 RT-Eye 软件同时显示得到的多个眼图。如前所述，针对 Gen1 的  $T_{TX-EYE}$  规范是一个“波形眼图模板”，定义为一个单位间隔减去合成 TIE 抖动。在 Gen2 中， $T_{TX-EYE}$  规范是一个“抖动模板”，使用 Dual-Dirac 模型定义为一个单位间隔减去  $10^{-12}$  BER 时的总抖动。在这两种情况下，幅度测量都基于示波器采集的电压。

### 噪声及其对抖动的影响如何？

前面介绍的抖动测量中使用的分析技术主要使用实时示波器完成。发射机使用的 3500:250 滤波方法和参考时钟使用的相位抖动滤波方法主要依赖实时捕获的边沿信息。实时采集是保证知道抖动的频率成分、从而能够在频域中使用后期处理算法滤波抖动的频率成分的唯一方式。但是，实时示波器中的垂直噪声在抖动域和幅度域中都增加了误

▶ 图 15. PCI Express 波形模板规范

差。这是因为实时示波器在前端使用模拟放大器采集波形。由于模拟放大器的噪声和带宽乘积是恒定的，拥有的带宽越多，采集的信号中的噪声也就越多。此外，实时示波器的模数 (A/D) 转换器分辨率在设计时限定在 8 位，这不可避免地产生了量化误差。系统噪声和量化相结合，增加了测量误差。在许多情况下，误差并不明显，可以忽略不计，但在 PCI Express 开发人员设计更长的传输通道时，实时示波器的分辨率和信噪比可能会变成限制。对这些应用，可以使用等时取样示波器，实现更高的测量精度。此外，业内已经开发出新的软件工具，不仅可以分析高速串行数据信号的抖动，还可以分析噪声。

▶ 图 16a. 抖动和噪声分解图

在图 16a 中，图的左侧显示了串行数据抖动的传统分解结果，图的右侧显示了取样示波器中新增的技术，其在幅度域中分解噪声，其方式与时域中分解的方式大体相同。结果得到了一个代表二维概率密度函数 (PDF) 的 BER 眼图。图 16b 显示了在泰克取样示波器上使用 TDS8JNB（高级抖动、噪声和 BER 分析软件）对 PCI Express 插件进行分析的结果，进一步考察了眼图闭合的确切原因。

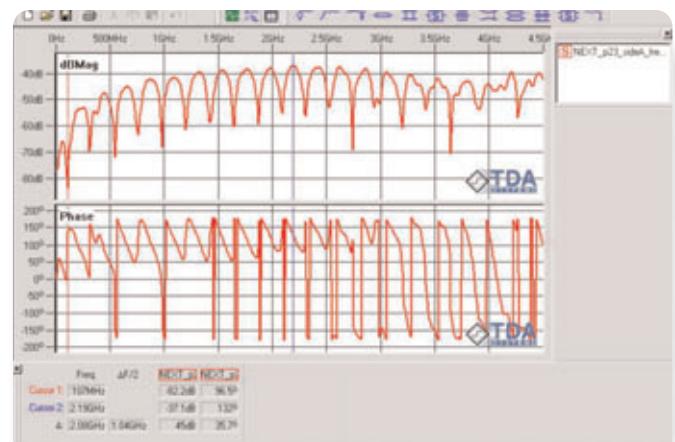

### 频域测量

互连链路一致性测试正日益要求频域测量，如插入损耗、回波损耗和频域串扰。它还经常要求测量回波损耗。这些频域测量也称为 S 参数，主要在差分模式下完成，因为差模测量直接与数字系统中的带宽劣化和抖动相关。某些标准开始要求共模测量或模式转换测量。这种测量可以使用支持 TDR 的、拥有差分功能及近似上升时间的示波器完成，其直接与测量带宽相关。图 17 显示了使用泰克取样示波

▶ 图 16b. 来自 JNB 软件的抖动和噪声 PDF

▶ 图 17. 频域串扰测量

器上运行的 80SSPAR IConnect S-Parameter 和 Z-line 软件进行分析，得到的 PCI Express 互连的频域串扰测量结果。

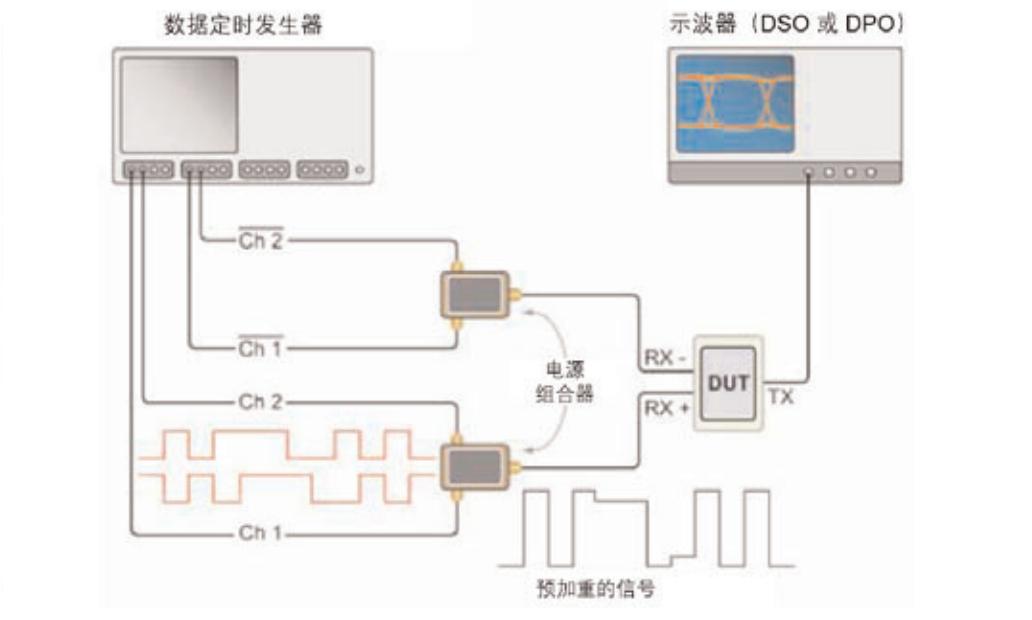

▶ 图 18. 从两条 DTG 通道中创建去加重的信号

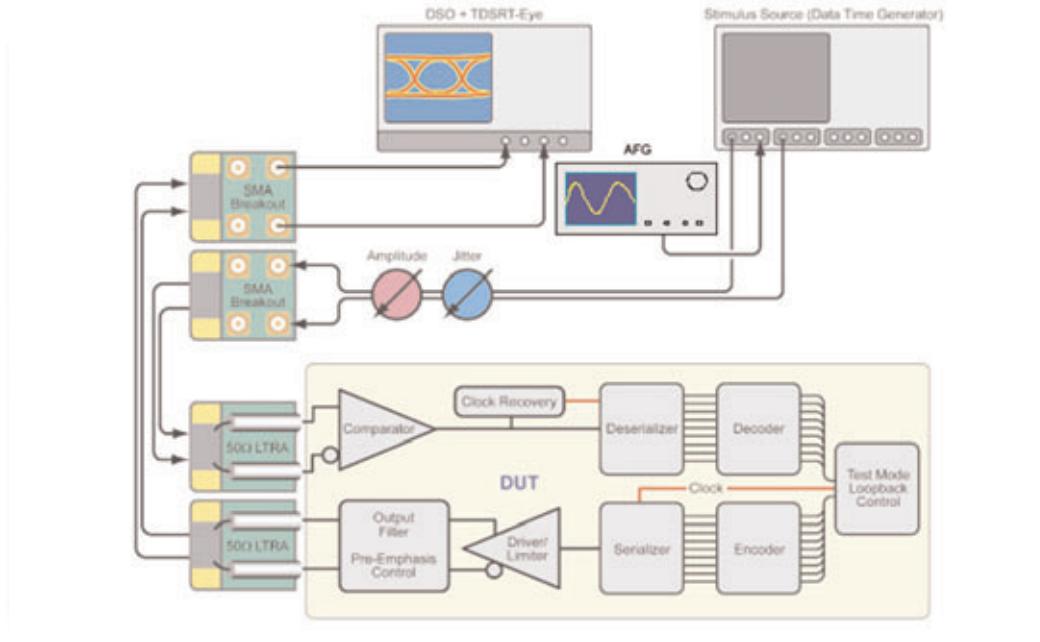

### 接收机灵敏度和抖动容限测量

Gen1 接收机测试要求激励源，驱动采用环回模式配置的被测设备 (DUT)。码型发生器为完成这一工作提供了适当的工具（也称为数据定时发生器），可以生成定义的 2.5 Gb/s 测试码型，如训练序列 (TS1 & TS2)，并把它们应用到设备上。在 DUT 的接收机部分识别训练序列时，发射机部分会发出一个类似的序列。可以使用示波器和/或逻辑分析仪观察和分析这个发送的序列。通常要改变训练序列，以便能够在各种极限条件下检定 DUT 的性能，这些极限条件包括幅度电平变化、眼图闭合程度变化、差分偏移变化及增加的噪声和抖动。

全面测试接收机还要求数据定时发生器预加重连续的跳变位，以测试 SerDes 电路。图 18 说明了可以怎样把两条数字定时发生器 (DTG) 通道结合起来，创建去加重的信号。

DTG 中不仅可以调节幅度电平，还可以调节：

定时容限 – 可以改变频率，查找接收机极限。

交叉电平容限 – 可以改变差分信号 D+ 支脚和 D- 支脚之间的交叉电压，以仿真共模不对称性。

偏移容限 – 可以改变差分信号 D+ 支脚和 D 支脚之间的延迟，仿真差分偏移。

抖动容限 – 可以改变抖动频率调制和幅度，根据指定要求对设备执行测试。

▶ 图 19. 抖动容限测试设置

接收机的抖动容限定义为存在抖动时成功恢复数据的能力。满足规范保证了即使在存在一定的抖动量时，SerDes 和 PLL 电路仍能恢复时钟。抖动容限测试是用来保证互操作能力的比较重要的测试之一。严格的抖动测试在 PCI Express 等应用中特别关键。它绝对要求信号源能够提供具有特定幅度和频率调制特点的抖动。

PCI Express 基本规范规定抖动是眼图交点相对于恢复的发射机单位间隔 (UI) 的变化。如图 19 所示，DTG 在幅度成分和频率成分方面提供了抖动控制。通过这种组合，可以全面测试 PCI Express 接收机的抖动容限。

#### 在模拟测量中保证信号保真度

不管是进行一致性测试、检验还是进行调试，早期 PCI Express 测量都包括探测设备、采集信号数据、分析捕获的信息。选择适当的工具、并正确使用这些工具，可以保证快速精确的测量结果。本章将讨论不同的被测设备连接技术以及在选择示波器时的模拟性能考虑因素。

## 连接串行被测设备

在测量时，首先要连接被测设备。这就出现了一个问题：被测通路的机械接口是什么？推荐的测试定义中通常会回答这个问题，也可以由设计中的接入点解决这个问题。可以有各种不同的配置，每种配置都有自己独特的特点。

机械接口对电气和逻辑测试中的探测具有深远影响。探头可能需要匹配微小的物理特点，同时为测量仪器提供完整的高速差分信号。探头可能需要适应原型夹具，如装有SMA连接器的测试点。

迎接探测挑战有四种方法：

- ▶ 伪差分有源探测

- ▶ 真正的差分有源探测

- ▶ 伪差分 SMA 连接

- ▶ 真正的差分 SMA 连接

记住，PCI Express信号以差分方式传送，因此这里介绍的所有解决方案都采用差分连接。

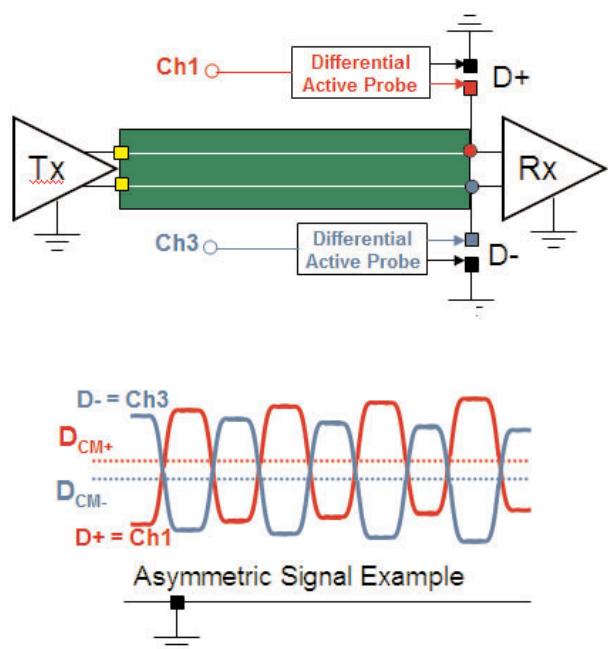

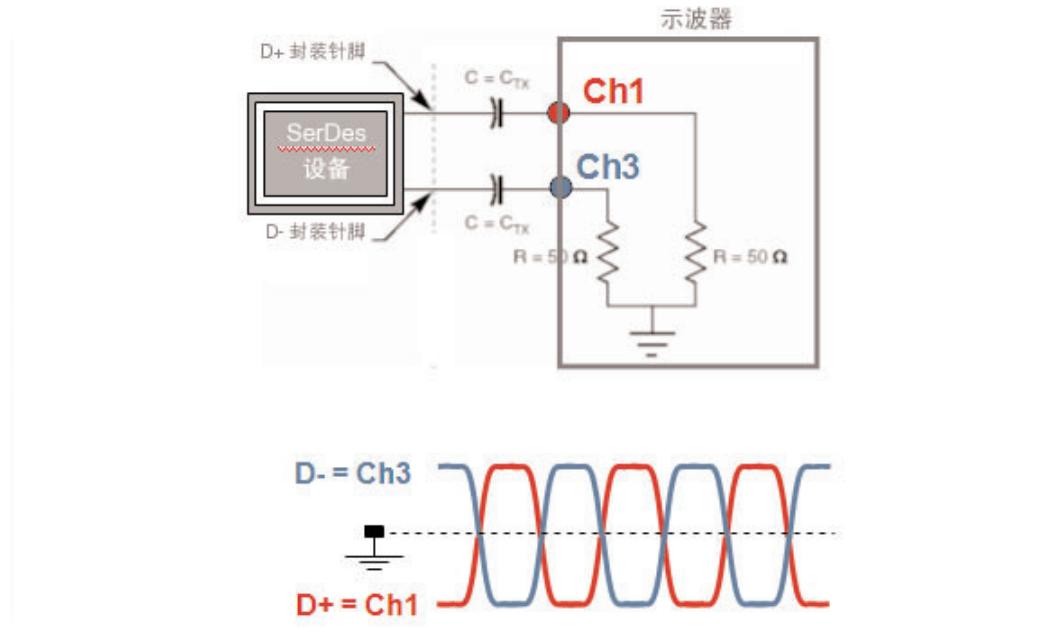

**伪差分有源探测** – 可以使用两个差分有源探头进行伪差分测量，每侧差分信号各一个探头。图 20 显示了芯片到芯片应用实例，其中可以把两个探头焊接到相对于接地的差分对的 D+ 支脚和 D- 支脚上。示波器的两条通道捕获两路数据。探头可以同时捕获信号的 AC 成分和 DC 成分，为考察差分链路上的共模效应提供了最优秀的工具。尽管链路的接收机只能查看来自发射机的差分摆幅，但共模电压变化可能会导致不希望的幅度变化，改变周期。图 20 中测量的信号

▶ 图 20. 伪差分有源探测

是使用伪差分探测设置捕获的不对称信号。PCI Express 基本规范要求最大共模 AC 电压 ("V<sub>CM</sub>")，还规定了可以接受的共模 DC 电压范围。把 D+ 波形和 D- 波形相减，可以获得差分电压波形 VDIFF。将在这个数学运算波形上进行眼图、幅度及抖动和定时测量。由于波形的两侧进入伪差分探测中两条不同的示波器输入通道，必须校正输入的偏移，然后才能进行测量。

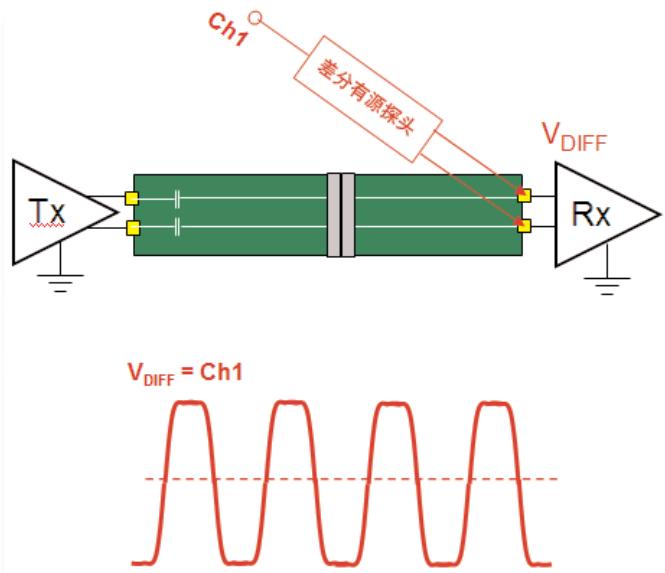

真正的差分有源探测 – 图 21 是一个差分探头，捕获基于连接器的插件到插件串行链路的接收一侧。与伪差分连接不同的是，这个探头只要求一条示波器通道，不需后续的数学运算步骤。除其它优势外，它还可以使用示波器的多条通道，捕获多条通路。另外它还可以调试多个高速测试点。图 21 中的差分波形只要求一条示波器通道，不需校正偏移。在这种情况下，只提供了差模测量。需要指出的是，任何探头都会给被测设备 (DUT) 带来一定的负荷。每个探头都有自己的电路模型，其阻抗会随着频率提高而变化。这会影响观察的电路的行为，影响测量，在评估结果时必须考虑这些因素。在设计“芯片到芯片”接口时，非常重要的一点是在电路板设计中包括测试连接盘，并考虑预计探头的机械要求。探测连接盘应尽可能接近接收机端接电阻器，以避免由于反射引起的信号失真。

▶ 图 21. 真正的差分有源探测

▶ 图 22. 伪差分 SMA 连接

**伪差分 SMA 连接** – 许多一致性测试夹具和原型电路预计在输出上拥有特性负荷。如果夹具/原型配有 SMA 高频连接器，SMA 伪差分方法可以接入信号，如图 22 所示的发射机一致性测试。在本图中，DUT 输出直接连接到示波器的两个输入，每个输入的输入阻抗均为 50 欧姆。高性能示波器一般都会提供 SMA 输入，不要求差分探头进行测量。如图 22 所示，可以在差分对的两个支脚上进行共模 AC

测量。信号必须实现 AC 耦合，因为示波器端接到地上。与有源探测中一样，通过从另一个共模信号中减去一个共模信号，可以得到差模波形。在使用这种技术时，必须注意校正通道偏移，同时在测量中要考虑与 DUT 到示波器输入的电缆相关的任何损耗。

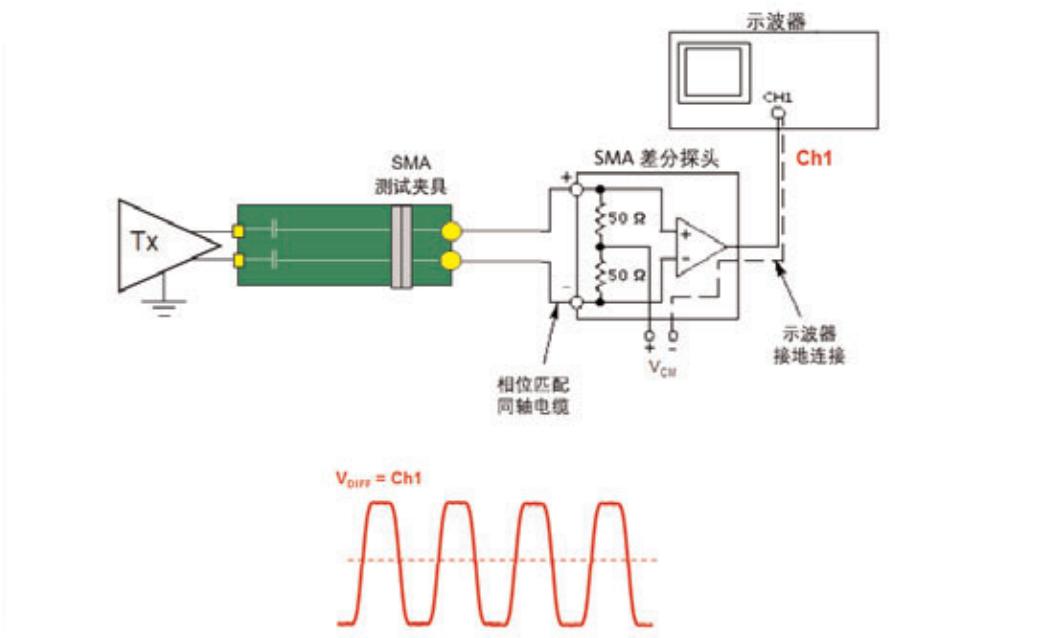

▶ 图 23. 真正的差分 SMA 探测

真正的差分 SMA 连接 – 图 23 显示了为满足发射机路径一致性测量而设计的新型示波器探头。SMA 输入差分探头特别适合在“插件到插件”或“插件到电缆”接口上规定了互操作点的一致性测试。100 欧姆匹配端接网络把差分信号的两个支脚正确端接到任何共模电压上。共模电压可以由用户提供，在某些情况下直接由示波器提供。图 23 演示了真正的差分 SMA 探头，它使用差分放大器把单端信

号转换成差分信号，而不需要校正通道偏移。在泰克 P7380SMA（带有 SMA 输入的差分信号采集系统）中，它在制造时在探头外面校准匹配的 SMA 电缆的相关损耗，比伪差分 SMA 方法提供了更加精确的测量结果，后者需要校准电缆损耗或把电缆损耗作为余量考虑。

▶ 图 24. 理想的低通滤波器的脉冲响应

## 模拟采集考虑因素

### 系统性能推动着测量精度

在为关键高速测量选择解决方案时，必须作为一个系统成对考虑示波器和探头。仪器的性能成为测量的一部分。系统的模拟采集特点及其数字化规范在提供有意义的测量结果中都发挥着一定的作用。在为手边的任务选择适当的仪器时，了解性能规范也发挥着关键作用。

### 评估采集系统的性能

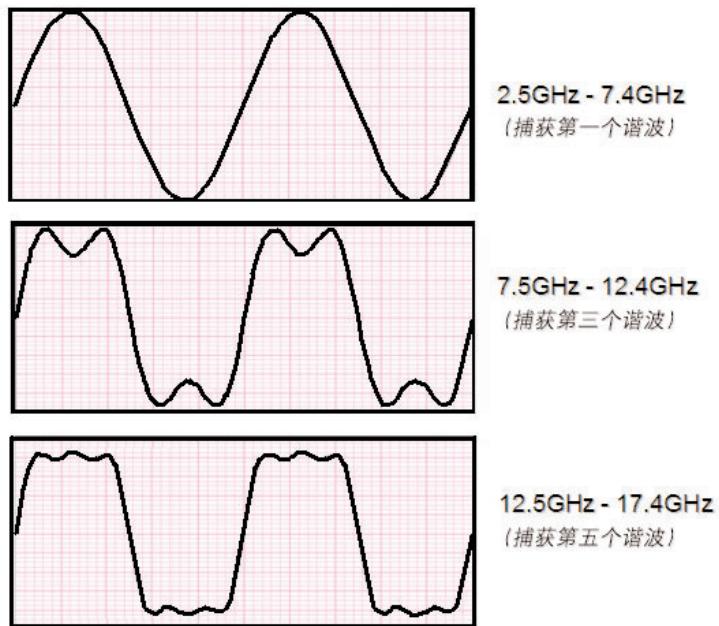

**带宽** – “带宽”是指示波器输入电路（垂直放大器）将以某些容限接纳的频率范围。仪器的取样速率通常进行优化，

以处理同一频率范围。必需保证系统带宽足以执行测量。多少带宽才算足够呢？回答这一问题取决于被测信号的频率成分。把示波器输入想象成理想的“砖墙”滤波器，把 5 Gb/s PCI Express 信号（发送 101010 重复码型）作为完美的 2.5 GHz 方波，示波器屏幕上显示的信号将如图 24 所示。三个示意图显示了理想的带宽滤波器在带宽变化时发生的情况。注意只通过第三个谐波的示波器产生的幅度和转换时间误差要远远超过通过第五个谐波的示波器。为实现最佳的信号保真度，很明显至少要求第五个谐波，以使测量误差达到最小。

► 图 25. 使用 15 GHz 示波器捕获的 5 Gb/s 信号

在实践中，大多数示波器并不是“砖墙”滤波器，示波器的滚降特点会对信号保真度产生巨大影响。例如，15 GHz 示波器经过校准后在 12.5 GHz 时拥有平坦的频响（0 dB 的损耗），其 3 dB 下降点是 15 GHz；在 17.5 GHz（第七个谐波）时有部分能量。这产生了非常精确的眼图响应，如图 25 所示，因为它测量高速 BERT 发生器的 5 Gb/s 输出。图中的模板表示 Gen2 PCI Express 发射机跳变位模板。如果使用带宽较低的仪器，那么余量不大。

上升时间 – 如图 24 所示，带宽和上升时间相关。PCI Express 基本规范对发射机设备有最低转换时间要求。对 Gen1，最低转换时间是 0.125 UI (50 ps)，对 Gen2 为 0.15 UI

(30 ps)。非常重要的一点是不要混淆示波器的传统上升时间指标（在 10-90% 电平上测得）与规范中的转换时间指标（在 20-80% 电平上测得）。由于这一原因，大多数示波器制造商会在产品资料中同时注明 10-90% 和 20-80% 上升时间指标。如果系统上升时间远远低于指定测量，那么精度要更高。例如，在 15 GHz 实时示波器中，20-80% 上升时间指标是 19 ps，在最快的 Gen2 转换 (30 ps) 中会产生 5% 的转换时间测量误差。

第五个谐波精度是发射机一致性测试的最低要求（在 SerDes 针脚上）。带宽高达 70 GHz 及上升时间低达 5 ps (10-90%) 的取样示波器可以实现更高的精度，以检定系统。对 CEM 和其它互连测试点的下行测量，使用带宽较低（上升时间较慢）的示波器通常是不够的。其原因是一旦信号电平离开发射机针脚，并沿着铜缆传输通道传送，那么将进一步滤波信号，降低信号的第五个谐波成分。如果信号的转换时间下降到其占单位间隔很高的百分比，在使用带宽较低的仪器时，上升时间和幅度误差会大大下降。但是，了解能否使用带宽较低的示波器获得精确测量的真正方式是使用拥有第五个谐波性能的仪器进行同一测量，并比较结果。

**取样速率** – 在实时示波器中，内奎斯特取样定理定义了精确重建模拟信号要求的取样速率。这一定理规定为捕获足够的数据精确重建波形，要求的取样速率要比输入信号的最高频率成分高两倍。因此，15 GHz 输入带宽的仪器可以有 40 GS/s 的取样速率。在取样示波器中，取样速率要低几倍，但不是主要性能指标。

**内插** – 对拥有快速转换时间的信号（如 PCI Express 中的 30-50 ps 转换），取样的数据的  $\sin(x)/x$  内插提高了基于幅度的测量和眼图的精度。应把内插系数设置成保证至少有三个样点发生在被测边沿上。对于在差分信号的开关门限或“零电平”上获取参考电平的抖动测量，内插对结果的影响一般可以忽略不计。某些实时示波器作为采集路径的一部分提供了  $\sin(x)/x$  内插，它是默认的内插方式。这提供了捕获结果，而不会降慢波形和测量吞吐量。

**本底噪声** – 在实时示波器中，可以使用信号上的时间间隔误差 (TIE) 的随机成分定义抖动本底噪声 (JNF)，其中要去掉所有数据相关抖动。通过为示波器输入提供理想的时钟信号 (101010) 重复码型，测量 TIE 的标准偏差 (RMS)，可以直接测量本底噪声。性能最高的实时示波器提供了一般 <400 fs RMS 的抖动本底噪声。由于较低的本底噪声和较高的数字转换器分辨率，类似设置的取样示波器（但不是实时示波器）的抖动本底噪声一般为 <200 fs RMS。实时示波器有 8 位数字转换器分辨率 DC，而取样示波器则提

供了 14 位分辨率。如前所述，实时示波器较低的分辨率与输入放大器导致的噪声相结合，使得相对 JNF 要高出两倍。

**记录长度** – 实时示波器中的记录长度基本上定义了可以捕获的信号的频率成分。这在测量抖动时特别重要。在捕获时，只能测量 TIE 的低频成分（抖动频谱）。长记录长度示波器可以以全部取样速率捕获这些频率。例如，在 100M 记录长度时，可以以 50 ps/pt 的速率捕获 5 ms 的波形数据。这代表着 12.5 M UI 的 Gen1 PCI Express 业务或 150 个周期的扩频时钟。

在 PCI Express 中，低频抖动问题导致 Rev1.1 规范要求 1M UI 的统计确定性。为在一次采集中捕获 1M UI，示波器必须要有最低 8M 的记录长度。为了滤出高频成分，从数据信号中解析 30 KHz SSC 帘线，必须捕获超过 10 个周期 (333us) 或 13M 的数据。

**触发** – 在实时示波器中，触发性能在调试应用中至关重要。为捕获可能会导致误码的异常信号，仪器必须能够以信号相同的带宽触发采集。例如，5 Gb/s 信号中的异常信号可能是宽约 100 ps 的毛刺。在系统级，触发特定符号可能也非常重要。下一章介绍了可以使用泰克独特的触发系统调试 PCI Express 设计问题的部分用例。

▶ 图 26a. 检测到的误码

▶ 图 26b. 触发误码

## Pinpoint® 触发和数据解码工具调试链路

### 定位和触发误码

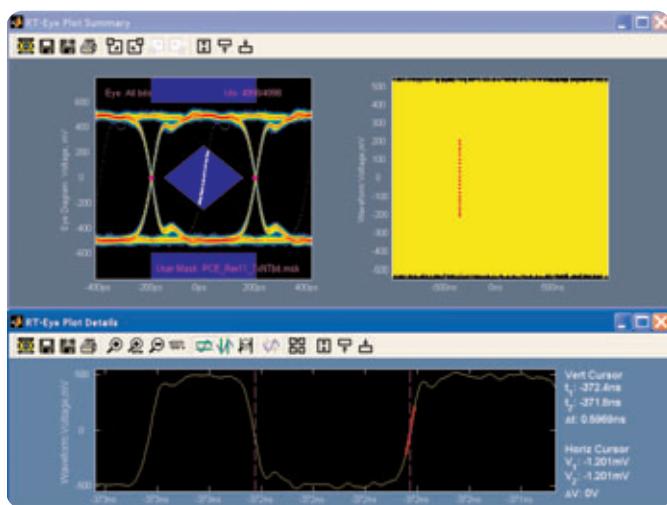

通常在进行信号完整性测量过程中，会发生意想不到的行为，表明可能存在设计问题。在这些情况下，调试设计变得至关重要，以迅速隔离和解决问题。通常可以结合使用分析工具和仪器的触发系统，指明这些问题。图 26a 表明了 RT-Eye 软件检测到一个不频繁的误码。乍一看，其似乎是 2.5 Gb/s 数据内部随机地不频繁地发生的一个 200 ps 脉冲。通过启动 RT-Eye 软件的误码定位程序，可以同时

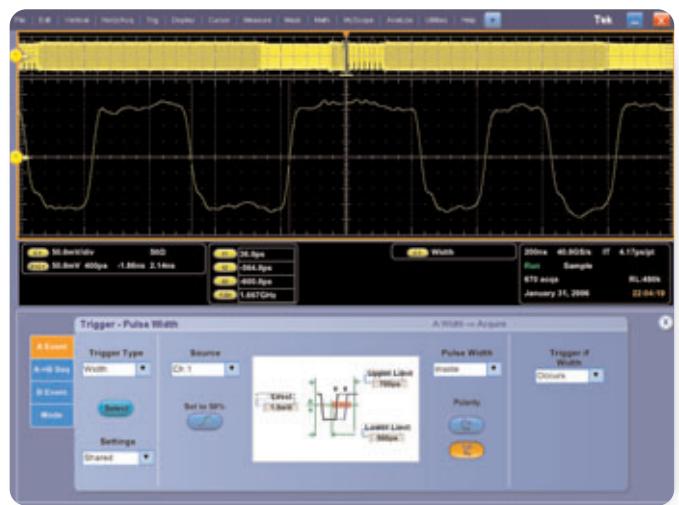

显示眼图（左上图）和采集的波形（右上图）。在超出模板时，在波形图上用红点高亮度显示超出模板的每个样点。通过放大波形图细节（底部），可以发现异常信号的真实特点。失败的位实际上是宽 600 ps 的位！现在已经发现失败的位，怎样进行调试呢？由于我们知道脉冲宽 600 ps，我们可以设置脉宽触发器，只在发生 600 ps 脉冲时才触发示波器。图 26b 显示了确定数据流中宽 600 ps 的脉冲的触发设置，可以进一步考察根本原因。

## PCI Express™ 测量介绍

### ▶ 入门手册

▶ 图 27a. 从波形中解码数据

▶ 图 27b. 触发四个符号的任意组合

### 检验和触发 8b/10b 符号

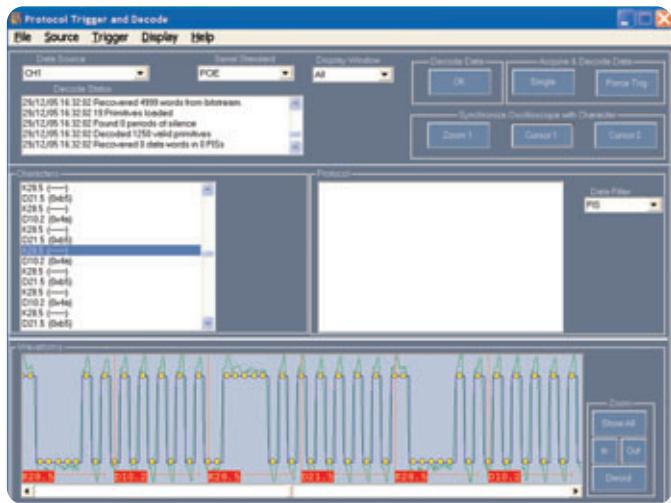

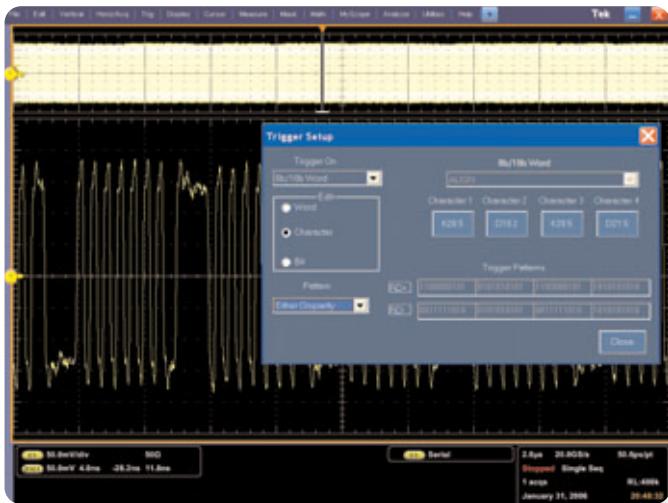

除 PHY 模拟部分发生的误码外，非常重要的一点是通过链路传输正确的数字数据。尽管训练眼图可以查看模拟波形，并转换成符号（K28.5, D10.2 等等），但这样做会非常麻烦，而且容易出错。通过使用配有 PTD（协议触发和

解码）软件的实时示波器（图 27a），将从采集的波形中自动解码数据（底部），另外还会提供符号列表（中间），从而可以检验数字数据。图 27b 显示了 PTD 软件的触发设置菜单，可以触发数据的任何 4 个符号（40 位）。基于 SerDes 的触发技术还可以实时触发奇偶和字符错误。

## 数字检验和调试

物理层一致性测试通常是艰辛的长期产品开发流程的最后一个环节。但在一致性测试之前和之后还有许多其它问题。毕竟，设备不仅要传送脉冲，还要传送有效的二进制数据。在上面的讨论中，没有什么东西证明设备能够在数据级和协议级提供正确的信息。与一致性测试准备工作一样，在数据级和协议级进行调试、诊断和设计检验在很大程度上也是项目的一部分。

这意味着，这里需要使用逻辑分析仪，作为整体、而不是各个脉冲特点采集和解释数据。在逻辑分析仪的数字环境中，捕获数据生成了总线活动的定时图。串行数据扇出为并行形式，存储在仪器的存储器中。通过相应的解码工具，甚至可以分解这些记录的数据，帮助工程师确认正确执行高级程序指令。

尽管本文主要介绍模拟测试挑战和解决方案，但有必要考察逻辑分析仪系统，这些系统可以在 PCI Express 测量中有效补充示波器和信号源。

▶ 图 28. PCI Express Mid-bus 探头连接盘

### 探测意味着进行适当连接

所有测量都从探测开始，保持信号保真度与模拟采集一样重要。我们在上面讨论了怎样使用配有 SMA 连接器的夹具原型设备，为示波器提供最大的信号保真度。逻辑分析仪为这种方法提供了自己的解决方案，并考虑了相同的信号保真度目标。

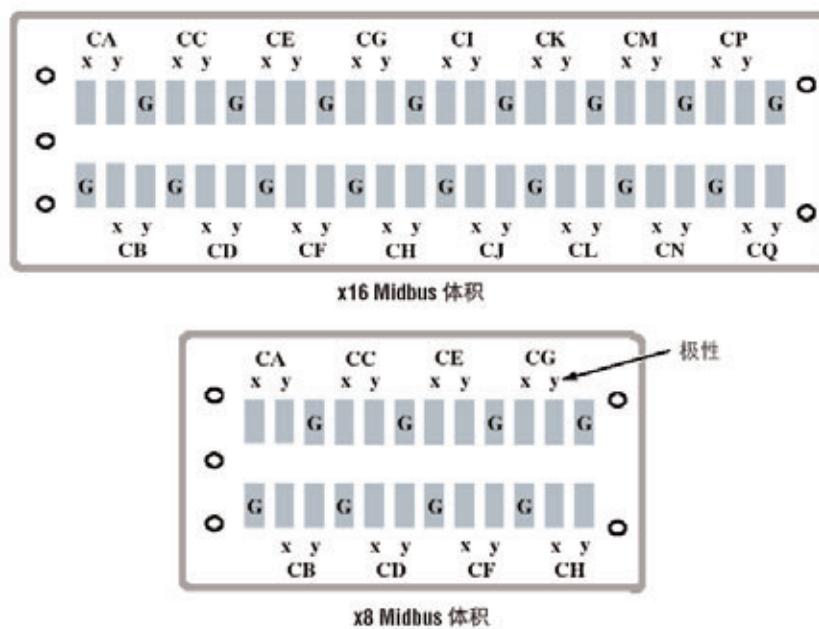

在 2.5 Gb/s 及更高频率上，简单地夹上常用的逻辑分析仪探头是不够的。飞线和微型夹子会引起接地环路和其它不可预测的模拟效应。甚至把信号路由到针头也会影响低压高频串行信号。它们不能容忍短电线或连接器引起的损耗。相反，在电路板布局过程中必须考虑探测方法。PCI Express 标准化探测方法是 mid-bus 探头接口。图 28 显示了 mid-bus 探头的体积。

▶ 图 29. PCI Express Mid-bus 探头连接盘

与基于连接器的接入点不同，在不使用探头时，连接盘几乎对信号没有任何影响。当然，连接盘要求逻辑分析仪探头上拥有匹配的模型。图 29 中的探头是为这一目的专门设计的。

很明显，其目标是使探头的负载影响达到最小。但是，任何探头都会影响信号损耗预算。高速信号对探头的阻抗非常灵敏，特别是其电容负荷。在信号的带宽提高时，探头

电容的影响也会提高。PCI Express 采集使用的“理想”探头拥有下述特点：

- ▶ 高模拟带宽

- ▶ 高阻抗

- ▶ 低电容

- ▶ 最小的残桩效应

▶ 图 30. 在本例中，逻辑视图解扰、校正偏移和解码数据，把各位设置成正确的奇偶性。结果以十六进制数据流显示

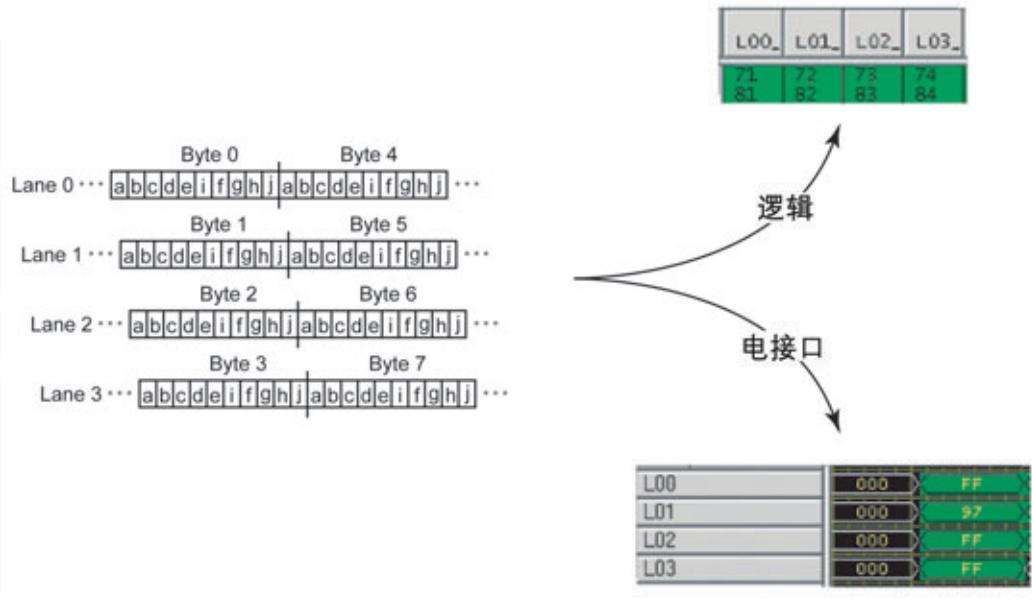

### 采集信号：从分组信号到并行信号

串行信号提供几位宽的深数据包；并行信号表现为 1 位深、但很多位宽的“字”的形式。逻辑分析仪固有并行结构，许多通道（位）同时接收数据。但由于专用处理器和总线支持软件，逻辑分析仪可以象并行数据一样随时采集和分析串行数据。广泛的处理器和总线支持软件是一流逻辑分析仪的主要特点。

图 30 说明了逻辑分析仪画面怎样区分串行数据，并以逻辑和电气子块格式显示这些数据。

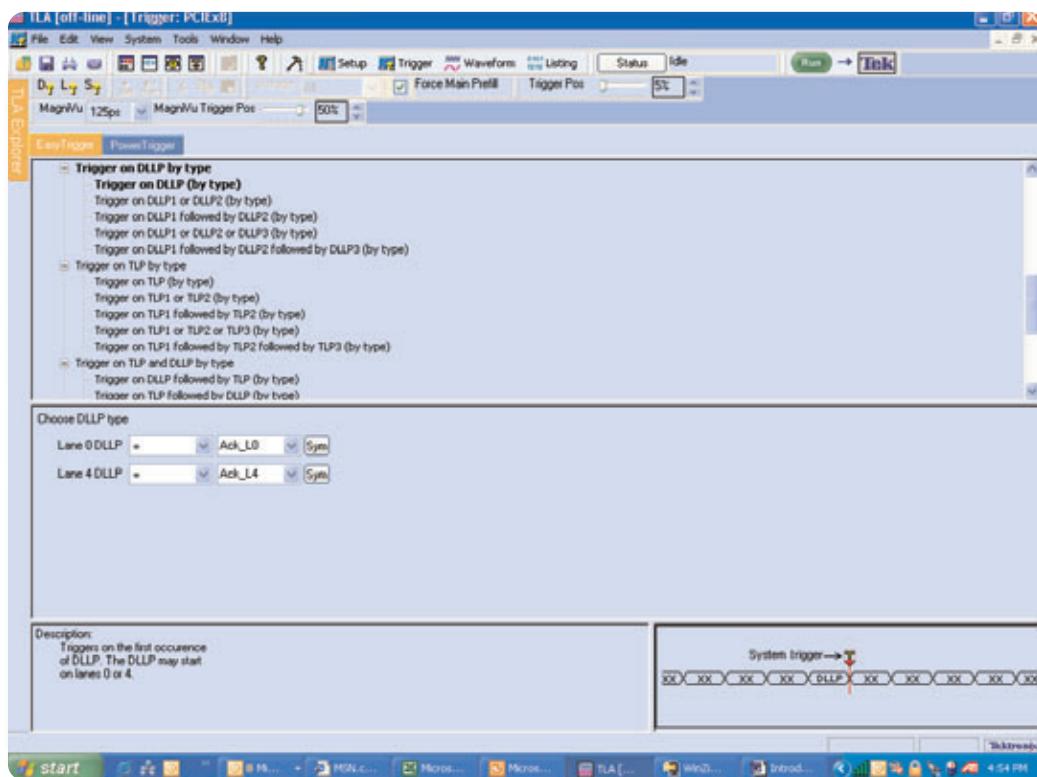

### 触发是调试效率的关键

对任何逻辑分析仪来说，决定其性能的因素之一是触发系统的灵活性。在与为某种串行标准 (PCI Express) 设计的配套软件相结合时，逻辑分析仪提供了先进的触发功能，可以简便地隔离和捕获指定事件。

在逻辑分析仪允许触发（快速）事件或其它分组单元（如控制符号）时，可以迅速推进调试工作。某些仪器甚至包

▶ 图 31. 逻辑分析仪触发模板

括触发模板，如图 31 所示。模板进行预置（出厂时提供或用户定制），用户可以“填表”，指定感兴趣的事件。可以针对每种串行协议的独特要求，优化模板字段。

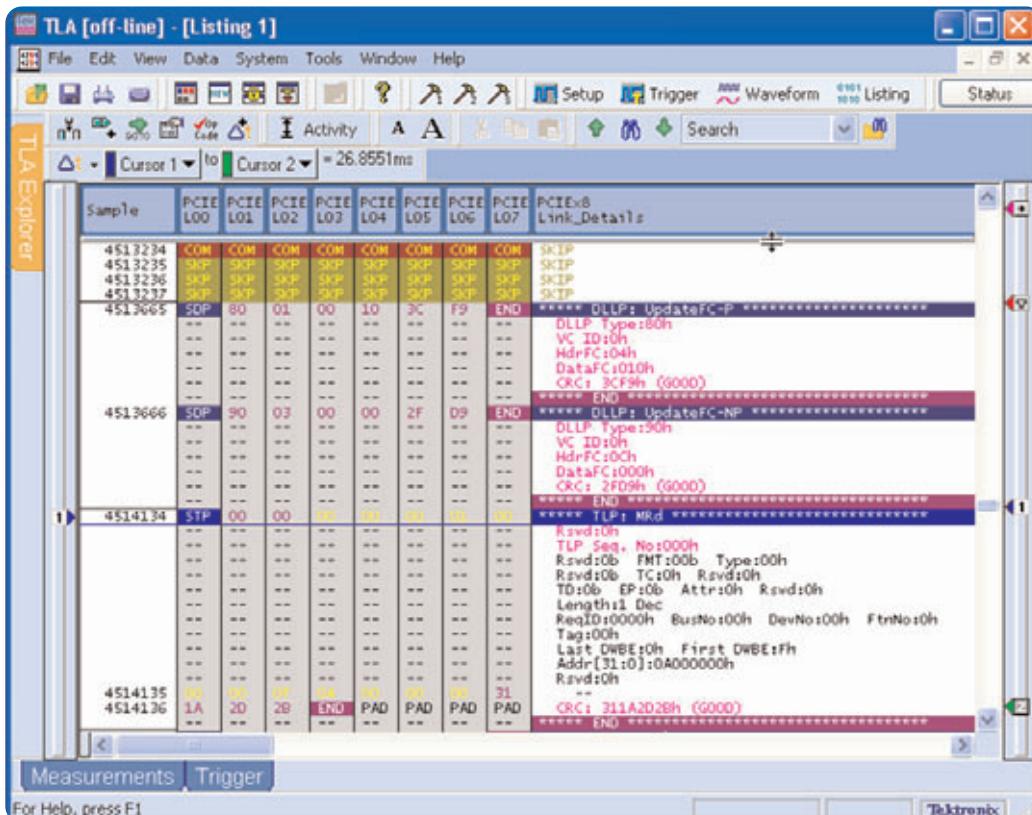

#### 分析结果

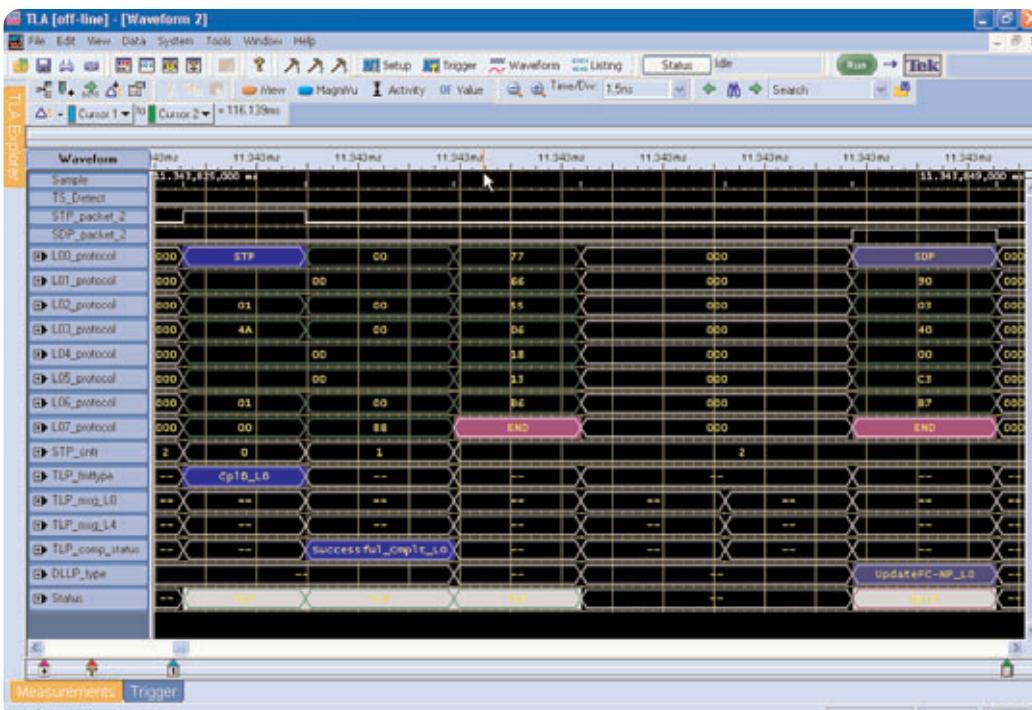

在采集结束时，存储的数据必须解码成有意义的结果，并以相应的方式显示。总线支持套件包括完善的软件工具，可以使用列表窗口，在分组式视图中分解、解码和显示捕获的数据，如图 32 所示。这是从 X8 PCI Express 总线上获得的采集结果。

图 32a 显示了逻辑分析仪提供的列表显示。显示中包括三个单元：分组/控制符号摘要、分组/控制符号各字段的详细解码、以及原始数据。色码把这三个单元中的文字隔开，在分组/控制符号摘要中把控制符号与分组区别开。颜色还可以区分细节栏中请求和响应分组的事务和操作等级。图 32b 显示了同一数据的波形视图。

在配备优化的配套软件包时，逻辑分析仪提供了高级分解功能，如深入捕获与发送端口和接收端口相关的板载处理器活动，同时深入显示这些端口。反汇编程序为物理层中的各个字段提供了控制符号解码和显示功能；对物理层、传输层和逻辑协议层中的各个字段提供了分组解码和显示功能；并同时解码发送数据端口和接收数据端口。

## PCI Express™ 测量介绍

► 入门手册

► 图 32a. X8 PCI Express 链路的列表显示

► 图 32b. X8 PCI Express 链路的波形显示

## PCI Express 测量解决方案概述

目前应该明确的是，串行一致性测量要求高性能测量仪器资源。PCI Express 检验和一致性测试及调试任务中最常用的仪器有五种。

### 示波器

测量有源 PHY 电气部分的首选工具是高性能示波器。一流的数字示波器可以以非常好的信号完整性，捕获几千兆位范围内的波形。

一旦从串行码流中恢复时钟，示波器可以从波形中创建眼图。示波器创建的眼图可以很好地查看信号特点。它提供了全面的内置测量库，立即量化评估眼图和采集的波形。

使用专用工具进一步进行处理，可以得到时间间隔误差 (TIE)。可以分析 TIE，把随机抖动和确定性抖动分开，通过这种分析，还可以估算  $10^{-12}$  误码率 (BER) 时的总抖动。

除把多种仪器的功能融合到一部仪器中外，示波器还提供了其它优势：探测灵活性、丰富的显示功能、触发功能等等。

### 实时 (RT) 示波器

实时示波器捕获连续的相邻数据记录。在串行链路分析中，示波器必需从每个位中至少捕获多个样点。当前一流的数字存储示波器 (DSO)、数字荧光示波器 (DPO) 和数字串行分析仪 (DSA) 可以实现直到 25 ps 的样点间分辨率（40 GS/s 的取样速率），由于高达 15 GHz 的带宽，它们可以以高达 8 Gb/s 的速率检定信号。实时示波器的连续实时记录功能提供了特定的优势：

- ▶ 数字信号处理 (DSP) 软件算法可以从数字化串行数据码流中恢复嵌入式时钟。这种基于软件的时钟恢复方法是最灵活的方法，此外，它不需要时钟恢复硬件，自然也没有时钟恢复硬件中不能避免的抖动。

- ▶ 由于最优秀的实时示波器中的信号路径可以实现仪器带宽或接近仪器带宽，因此可以使用这些实时示波器中硬件触发器的全面触发功能，触发感兴趣的数据或事件，其通常会捕获频率非常低的通过其它方式看不到的事件。

- ▶ 实时捕获数据可以以最少的限制分析数据；它捕获了仪器的整个带宽，因此抖动频谱信息非常全面，对所有抖动类型都没有假信号；即使完全随机的数据，也可以被捕获和存储/解码。

- ▶ 最后，数据捕获的完整性在调试意想不到的、不可预测的行为中具有重要的意义。

## 等时 (ET) 取样示波器

等时取样示波器是以非常高的速度分析信号完整性的示波器，也称为“取样示波器”及“通信（信号）分析仪”。这些仪器的最大带宽可以达到 70 +GHz，能够分析从低于 1 Gb/s 直到 40 Gb/s 以上速率的光接口信号和电接口信号。由于取样示波器不企图以实时速度捕获数据，它们有机会实现更精确的信号捕获能力，所以取样示波器提供了更高的数字转换器分辨率和杰出的噪声性能，这两个特点都特别适合采集当前串行链路中的低压信号。类似的，由于只在“等时”顺序中捕获样点，因此它们之间可以间隔几飞秒，消除了与取样间隔或内插有关的任何问题。另一方面，抖动分析要更加复杂，有时会限制被测信号，如限定在重复码型。

由于带宽高，取样示波器还提供了 TDR 和 S 参数测量功能，而不需要单独的 VNA（矢量网络分析仪）在串行数据设备上执行 S 参数测量。

取样示波器还配有时钟恢复功能；在这种情况下，时钟恢复功能由硬件提供。某些实时示波器采用硬件时钟恢复功能同时提供了实时 (RT) 眼图和等时 (ET) 眼图读取技术，每种技术都有自己的优点。

## 信号源

良好的高速工程设计方法是在“实际环境”条件下对设计执行测试。尽可能模拟这些条件的适当工具是程控信号源。以当前的数据速率生成测试信号要求高速数据定时发生器 (DTG) 和任意波形发生器 (AWG)。如果没有这些仪器，那么没有任何方式测试和检验新的物理层设计。许多信号源可以重放示波器捕获的信号。信号可以作为参考信号，也可以进行修改，测试被测设备的极限。

数据定时发生器特别适合生成由并行数据组成的多条通道流，当前最先进的仪器可以支持最多 96 条通道。这些工具提供了 3.3 Gb/s 的数据速率。同时，这些先进仪器提供了一系列信号处理功能，包括独立电平、上升/下降时间和抖动控制功能。

高速数字信号不可避免地拥有模拟特点。任意波形发生器可以在总线通道上提供拥有模拟成分的激励信号（通常表明损耗）。AWG 能够提供任何类型或形状的波形，广泛用于设计和制造中。当前 AWG 拥有超过 4 GS/s (2 GHz 带宽) 的取样速率，相当于 4 Gb/s 的数据速率。

## 逻辑分析仪

逻辑分析仪是测量格式化串行数据（而不是单独的脉冲特点）的首选工具。与 RT 和 ET 示波器不同，逻辑分析仪捕获二进制数据，用时钟、周期和边沿转换表示数据。逻辑分析仪的用途是简化串行传输纯数字方面的采集和分析工作。为完成调试串行总线的使命，它必须提供与高速总线需求相一致的特点：高取样速率、深内存、灵活的触发和同步能力等等。与示波器一样，它必须提供影响低的探测工具。

## 小结

PCI Express 技术已经投入使用，随着计算机市场需要的数据速率越来越快，这种技术的重要性注定也将增长。设计和检验工程师需要学习新的、可能并不熟悉的学科 – 串行一致性测量，与此同时，他们面临着更紧迫的开发时间和快速变化的标准。

幸运的是，业内拥有 PCI-SIG 之类的工作小组，正在着手稳定技术，传播与设计、结构和一致性测试要求有关的信息。

同时，从实时示波器和取样示波器到逻辑分析仪和信号源的各种测量工具，可以帮助工程师迎接 PCI Express 测量挑战。这些解决方案提供了杰出的性能，可以捕获、显示和分析最复杂的串行信号。由于这些创新的自动工具，工程师可以迅速简便地执行一致性测试和检验测试，加快产品开发周期。

### DSA70000 系列

DSA70000 系列是新一代实时 DPO，为解决极具挑战性的信号完整性问题提供了业内最优秀的解决方案。

### TDS6000B/C 系列

TDS6000B/C DSO 系列提供了完善的性能和功能集，可以解决检验、调试和一致性测试挑战。Pinpoint 触发技术提供了 1,400 多种组合，可以更快地解决问题。

### TDS8200 系列

TDS8200 系列是为要求几十 GHz 带宽的应用研究、设计评估和制造测试而开发的。

### TLA7000 系列

TLA7000 系列提供了突破性的数字系统分析工具，可以捕获和分析复杂问题的来源。TLA7000 系列为捕获复杂问题来源提供了所需的速度，同时使用大显示器和快速系统数据吞吐量提供了用户想要的查看能力。

### DTG5000 系列

DTG5000 系列把数据发生器的处理能力与脉冲发生器组合到一个通用的台式仪器中。其模块化平台可以简便地根据现有需求和新兴需求，配置仪器性能，最大限度地降低设备成本。

与 Tektronix 联系：

奥地利 +41 52 675 3777

巴西和南美 55 (11) 3741-8360

比利时 07 81 60166

波兰 +41 52 675 3777

丹麦 +45 80 88 1401

德国 +49 (221) 94 77 400

东南亚国家联盟/澳大拉西亚 (65) 6356 3900

俄罗斯、独联体 +7 (495) 748 4900

法国和北非 +33 (0) 1 69 86 81 81

芬兰 +41 52 675 3777

韩国 82 (2) 528-5299

荷兰 090 02 021797

加拿大 1 (800) 661-5625

卢森堡 +44 (0) 1344 392400

美国 1 (800) 426-2200

墨西哥、中美洲和加勒比海 52 (55) 56666-3333

南非 +27 11 254 8360

挪威 800 16098

欧洲中东地区、乌克兰和波罗地海 +41 52 675 3777

葡萄牙 80 08 12370

日本 81 (3) 6714-3010

瑞典 020 08 80371

瑞士 +41 52 675 3777

台湾 886 (2) 2722-9622

西班牙 (+34) 901 988 054

香港 (852) 2585-6688

意大利 +39 (02) 25086 1

印度 (91) 80-22275577

英国和爱尔兰 +44 (0) 1344 392400

中东、亚洲和北非 +41 52 675 3777

中华人民共和国 86 (10) 6235 1230

中欧和希腊 +41 52 675 3777

其他地区请联系 Tektronix 公司 1 (503) 627-7111

最后更新日期：2006 年 2 月 28 日

如需了解更多产品信息，请访问泰克公司网站 [www.tektronix.com](http://www.tektronix.com)

© 2006 年 Tektronix. 版权所有。全权所有。Tektronix 产品，不论已获得专利和正在申请专利者，均受美国和外国专利法的保护。本文提供的信息取代所有以前出版的资料。本公司保留变更技术规格和售价的权利。TEKTRONIX 和 TEK 是 Tektronix, Inc. 的注册商标。本文提及的所有其它商号分别为其各自所有公司的服务标志、商标或注册商标。

1/06 FLG/BT

4HC-19375-0

**Tektronix**

Enabling Innovation