Ensuring Proper Board Design and Layout for Digital Debug and Verification Using Tektronix PCIe Protocol Analyzer

The industry has widely adopted PCI Express as the standard of choice for I/O interconnect in order to cater to the growing I/O bandwidth requirements. PCI Express is evolving and is currently in its third generation and offers up to 8Gb/s of data bandwidth.

Probing a system at such high data rates without affecting the performance is an important consideration. Tektronix offers three different types of probing solutions in order to meet the needs of different applications as shown in Figures 1, 2, and 3.

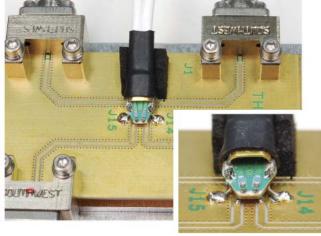

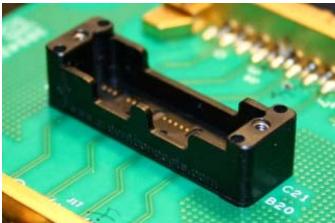

Figure 1: Slot Interposer Figure 2: Solder Down Probe

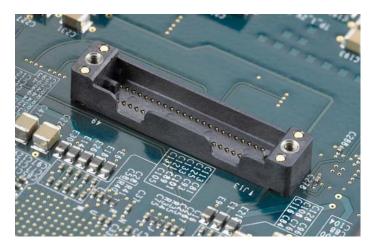

Figure 3: Midbus Probe

**Slot Interposers** are ideal for probing in situations where there is a PCIe slot available on the system under test. There are several manufacturers that make add-on cards that support different functions. The slot interposers provide visibility into PCIe transactions that occur between the system and the add-on cards. Several types of Slot Interposer probes are available to suit different types of slots.

Using the Tektronix Protocol Analyzer

Figure 4: Different Types of PCIe Slots

Figure 5: x16 PCle 3 Slot Interposer with Lane Converters

Appropriate lane converters are included for each type of slot interposer probe, e.g., the x16 slot interposer probe comes with x16-to-x8, x16-to-x4, and x16-to-x1 lane converters. This enables the x16 slot interposer probe to probe PCIE connectors of different lane width thus increasing its value. All three generations of PCIe use the same mechanical connector. The slot interposers are compatible mechanically with the PCIe slot defined as per the PCIe Specifications. See Figures 4 and 5.

**Solder-Down** probes are recommended for low lane count implementations of PCIe or when there is no space for a connector or a slot. The solder-down probes can be soldered to a via or a ball / pin of the device or to the decoupling capacitor on the PCIe channel. See Figure 6.

Figure 6: Solder Down probe tip connected to DUT

Using the Tektronix Protocol Analyzer

**Midbus** probes are recommended for probing multi-lane implementations of PCIe. They provide a common access point in embedded environment where there is no PCIe slot.

The industry has settled on **two different incompatible Midbus connector standards** for PCIe Gen2 and PCIe Gen3. Careful attention needs to be paid early in the design stage in order to layout the correct footprint on the board, Choosing the correct footprint type will ensure that the test equipment you buy is compatible with the performance needs of the system that needs to be validated.

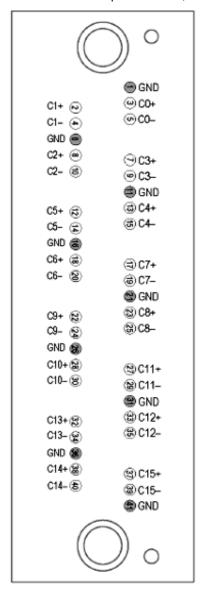

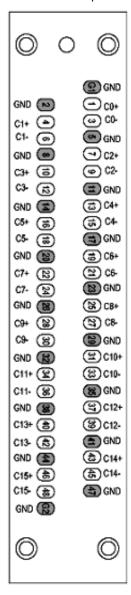

Figures 7, 8, 9, and 10 show the different types Midbus footprints and pin input assignments for probing PCIe. The Gen2 footprint has all of the individual pads in a row, whereas the Gen3 footprint has clumps of 5 pads on each side.

Figure 7: PCle Gen1, Gen2 and Gen3 16-Channel Midbus Footprints

Figure 8: PCle Gen1 and Gen2 16-Channel Midbus Footprints

Figure 9: PCle Gen1, Gen2 and Gen3 8-Channel Midbus Footprints

Figure 10: PCle Gen1 and Gen2 8-Channel Midbus Footprint

Using the Tektronix Protocol Analyzer

Figure 11: PCle Gen2 Midbus Footprint with Retention Module

Figure 12: PCle Gen3 Midbus Footprint with Retention Module

| Footprint                                 | Speed        | Probe     | Instrument Module |

|-------------------------------------------|--------------|-----------|-------------------|

| Gen1 and Gen2 8-Channel Footprint         | Up to 5 Gb/s | P6708     | TLA7S08 / TLA7S16 |

|                                           |              | P67SA08G2 | TLA7SA08/TLA7SA16 |

| Gen1 and Gen2 16-Channel Footprint        | Up to 5 Gb/s | P6716     | TLA7S08 / TLA7S16 |

|                                           |              | P67SA16G2 | TLA7SA08/TLA7SA16 |

| Gen1, Gen2, and Gen3 8-Channel Footprint  | Up to 8 Gb/s | P67SA08   | TLA7SA08/TLA7SA16 |

| Gen1, Gen2, and Gen3 16-Channel Footprint | Up to 8 Gb/s | P67SA16   | TLA7SA08/TLA7SA16 |

**Table 1: Footprint Compatibility Table**

The footprint that is chosen during the layout has important implications across the following areas:

- Supported speed grades (2 Gb/s, 5 Gb/s, 8 Gb/s)

- Number of lanes supported

- Retention Mechanism compatibility

- Probe and Instrument compatibility

Tektronix recognizes that some users may plan to buy the new TLA7SAxx module that supports up to 8Gb/s but their current board has the old Gen1/Gen2 footprint. For this situation, Tektronix offers the P67SA16G2 (x8) and the P67SA08G2 (x4) for speeds up to 5 Gb/s compatible with PCIe Gen2 rate.

No matter how you need to access your signal, Tektronix has you covered with multiple ways of probing your signal without affecting performance of the design.

For more information on footprints, probes, or modules, please visit us at www.tektronix.com.

Copyright © 2011, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.

6/11 52W-27115-0