## Memory Testing Solutions

### Fast and Accurate Testing Solution to Resolve Your Memory Design Challenges

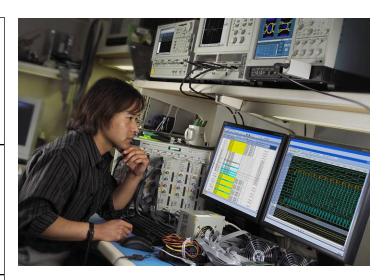

Continual demand for memories to be larger, faster, lower powered and physically smaller is driving the advancement of SDRAM technology. Tektronix' powerful and comprehensive test instrument portfolio for SDRAMs, memory controllers, DIMMs, computer motherboards and embedded systems will help you resolve design challenges quickly and efficiently.

#### **Memory Testing Challenges:**

| Digital Validation and Debug    | <ul> <li>Read and write data analysis</li> <li>Export data to simulation programs and other ATE</li> <li>SDRAM initialization analysis</li> <li>SDRAM commands sequences and timing analysis</li> <li>Data valid windows analysis with high resolution timing</li> <li>Time correlated memory analysis with system-level visibility of other buses</li> </ul> |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Validation and Debug | <ul> <li>Address and command signal integrity</li> <li>Address and command timing analysis</li> <li>Clock, strobe and data signal integrity</li> <li>Clock, strobe and data timing analysis</li> <li>MCH to DRAM and system debugging</li> <li>Ref clock parametrics and analysis</li> <li>Ref clock DLL performance</li> </ul>                               |

| Signal Path Characterization    | <ul> <li>Cross talk (single-ended and differential)</li> <li>Trace impedance (single-ended and differential)</li> <li>Trace length (single-ended and differential)</li> </ul>                                                                                                                                                                                 |

### **Memory Testing Solutions**

### Fast and Accurate Testing Solution to Resolve Your Memory Design Challenges

Application Fact Sheet

# Digital Validation and Debug

TLA Series Logic Analyzers with Nexus Technology Memory Supports

- Up to 20 ps timing resolution on all channels, all the time

- SDRAM protocol violation analysis

- Selective clocking stores useful data in the logic analyzer

- Complete system visibility with digital/analog correlation

- Data valid window analysis for setting sample point positions

- No preprocessor is required

- Industry leading high resolution timing

## Electrical Validation and Debug

DPO/DSA/MSO Series Oscilloscopes and Analysis Software

- Support for multiple DDR standards (DDR1, DDR2, DDR3, GDDR3, LPDDR, LPDDR2, custom rates, and more)

- Built-in clock, strobe and data JEDEC compliance measurements

- SDRAM eye diagram with strobe information for read or write cycles

- Advanced measurement debug capabilities with DPOJET jitter and eye analysis tools

- Command bus triggering and decoding for complete system insight including logic qualified triggering using MSO Series

- Automatic read and write bursts identification with Advanced Search and Mark

#### Signal Path Characterization

DSA Series Sampling Oscilloscopes and Application Software

- TDR impedance measurements and S-parameter characterization of the PCB traces

- Emulate the channel effect on jitter and noise using the channel's TDR/TDT or Touchstone® (S-parameter) description

- Over 70 GHz of sampling bandwidth and the lowest jitter floor

# SDRAM Probing Solutions

TriMode Probes, Interposers, and Mid-Bus Probes

- Wide selection of TriMode<sup>™</sup> probe tips provide quick and easy attachment, improved usability and low cost per solder point

- Multiple connection solutions, including BGA/slot interposers, mid-bus probes, and instrumented DIMMs

- Eliminate double probing with iCapture™ multiplexing to achieve simultaneous digital and analog acquisition through a single probe connection