## e-Guide to High Speed Interface Standards

PCI Express | DDR4 | USB | SAS/SATA

## Introduction High Speed Interface Standards

Next generation interface standards are pushing the limits of today's compliance and debug tools. Electrical validation of PCle 4.0 16 Gb/s, SAS 12 Gb/s, SuperSpeed USB 10Gb/s, and DDR4 3200 MT/s and other high-speed bus technologies require even more complex test considerations than before. Transmitter performance, for example, is best evaluated with new analysis techniques that can accurately identify jitter & noise from sources such as crosstalk or other multi-lane noise coupling. With a closed eye architecture, commonly found in long channel designs, physical layer testing requires advanced techniques such as channel de-embedding and end-to-end link simulation with reference receivers.

Tektronix automation software simplifies the complexities of validating next-generation high-speed interfaces.

### **Design Challenges**

- Smaller device geometries coupled with multi-layer PCBs incorporating buried via limit signal access

- Bus behavior with new power-saving schemes including frequency switching and clock gating

- Initiating test mode in-band through the channel, i.e., talk to the receiver's link training and status state machine

- Validating new signal encoding and equalization capability found in high-speed signaling interfaces

- Increasing complexity and quantity for electrical validation so many tests, so little time!

#### Standards

- a. PCI Express

- b. DDR4

- c. USB

- d. SAS/SATA

## PCI Express High Speed Interface Standards

PCI Express is a high-speed serial computer expansion bus standard designed to replace the older PCI, PCI-X, and AGP bus standards. PCIe has a variety of improvements over the older standards, including higher maximum system bus throughput, lower pin count and smaller physical footprint. PCI Express recently released its 3rd generation specification to operate @ 8 Gb/s and work is underway to define the next or 4th generation specification targeted to operate @ 16 Gb/s.

PCISIG.com

**Get our Primer on PCI Express® Transmitter PLL Testing – A Comparison of Methods**

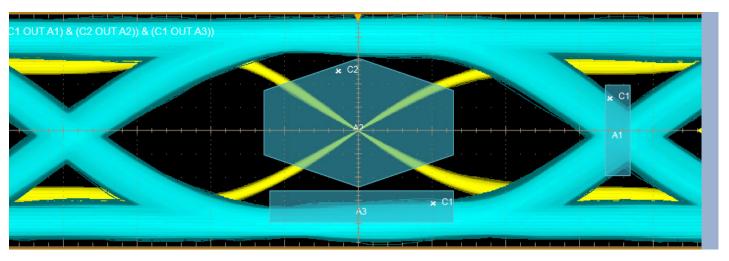

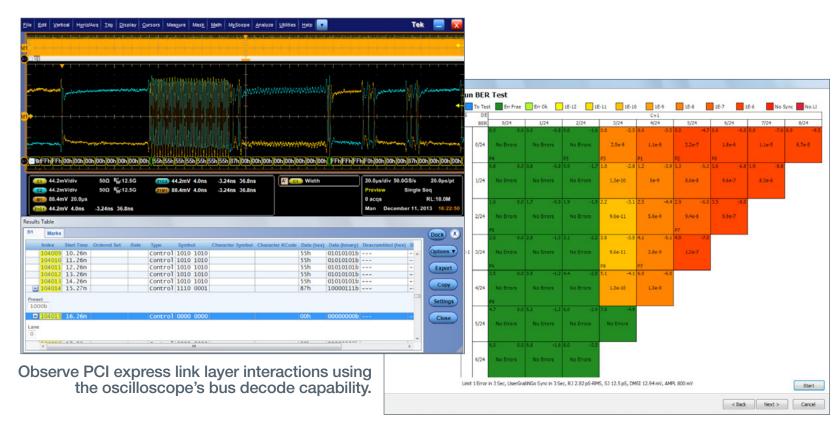

Observe receiver bit error map for all of the PCI Express' preset levels to assess BER margin.

#### **Design Challenges**

- Validating all bus speeds and presets per lane, for example, 8 Gb/s requires testing at 5 Gb/s and 2.5Gb/s with 11 de-emphasis presets on up to 16 lanes

- Placing the device into loopback to perform stressed receiver eye measurements

- Tracking link training sequences to validate speed and link width negotiation between transmitter and receiver

# 9

#### **Tektronix Solution**

- TekExpress for PCI Express automation software for in-depth compliance testing

- DPOJET and SDLA advanced link analysis for host and device system modeling

- BERTScope PCle automation simplifies calibration and receiver tolerance testing

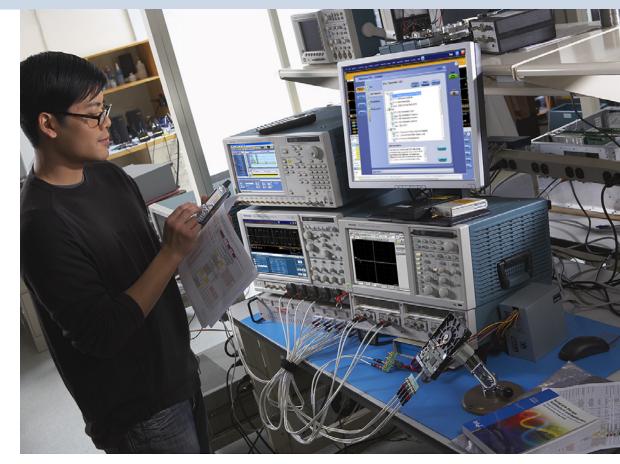

- TLA Logic Protocol Analyzer to trace and validate link layer behavior

High Speed Interface Standards

## DDR4 High Speed Interface Standards

DDR4 is the next generation memory standard targeted for enterprise computing. The standard enables higher capacity DIMM's (128 GB), doubles the data rate (3200 MT/s) and operates at lower voltage (1.2V) compared to the previous generation.

JEDEC.org

Watch our Webinar on Memory Interface Verification and Debug

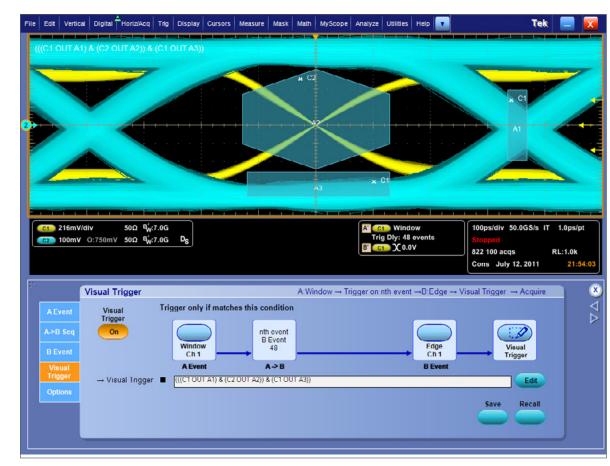

Tektronix Visual Trigger can accurately capture fast reads & writes on DDR signaling

#### **Design Challenges**

- Signal Access for debug and validation

- Read / Write separation for analysis

- De-embedding to remove the effects of the interposer and probe, and to view signals @ the memory controller

- Triggering on error conditions such as data-dependent errors

- Protocol error checking

#### **Tektronix Solution**

- Interposer solutions enable signal access for both electrical and protocol validation

- DDRA automatically separates Reads / Writes then performs the relevant measurements

- SDLA enables generation of de-embed filters

- Visual Trigger can be used to define complex conditions, enables capturing conditions of interest

- The TLA7000 Logic Analyzer and the MCA5000 Memory compliance analyzers can be used to perform Logic validation and protocol compliance

High Speed Interface Standards

INDEX

## JSB High Speed Interface Standards

With the continued trend towards more bandwidth driven by larger and faster storage solutions, higher resolution video, and broader use of USB as an external expansion/docking solution, USB 3.1 extends the performance range of USB up to 1GB/s by doubling the SuperSpeed USB clock rate to 10Gbps and enhancing data encoding efficiency. Additionally, the new USB Type-C connector greatly improves the user experience through high power, high bandwidth and more flexible usage.

**USB.org**

**Get your FREE application kit for USB 3.1 Transmitter and Receiver Testing**

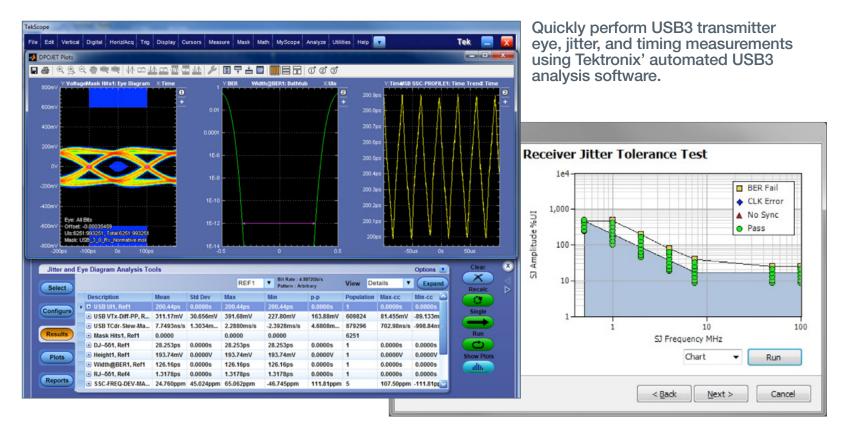

Characterize your USB3 receiver performance with built-in jitter tolerance margin testing with the BSAUSB31 testing software.

#### **Design Challenges**

- Higher data rate means lower margins

- Long-channel signal recovery requires complex equalization

- 128b/132b encoding requires new LTSSM

- Backwards compatibility means more tests

#### **Tektronix Solution**

- DPOJET and SDLA advanced link analysis for host and device system modeling

- BERTScope USB 3.1 automation simplifies calibration and receiver tolerance testing

- TekExpress USB 3.1 Transmitter test software with comprehensive support for 5/10 Gb/s

High Speed Interface Standards

## SATA/SAS Storage High Speed Interface Standards

Next-generation storage technologies such as 12 Gb/s SAS and SATA enable a new performance class of storage hierarchy that unlocks the performance of servers and solid-state drives.

t10.org

scsita.org

sata-io.org

**Methods of Implementation**

- SAS MOI

- SATA MOI

Perform timing, jitter and amplitude analysis with DPOJET software

#### **Design Challenges**

- Complex bus topology and routing requires advanced equalization such as FFE/DFE.

- New host architectures include extensive Tx emphasis capabilities which can cause interoperability issues

- Independent clock domains require inclusion of logical idle characters between a transmitter and receiver

#### **Tektronix Solution**

- DPOJET and SDLA advanced link analysis for host and device system modeling

- BERTScope jitter tolerance search mode simplifies receiver margin testing while filtering align primitives

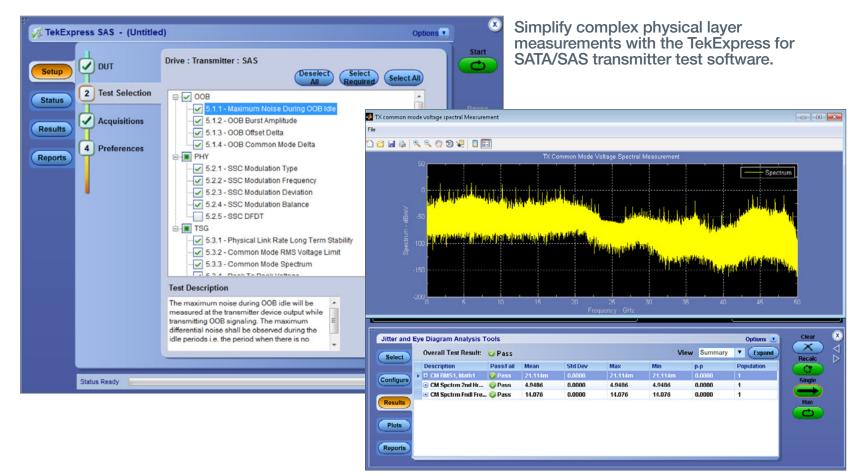

- TekExpress SATA/SAS Transmitter test software with comprehensive support for Tx equalization characterization

#### Contact Tektronix:

**ASEAN / Australia** (65) 6356 3900

Austria\* 00800 2255 4835

Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777

Belgium\* 00800 2255 4835 Brazil +55 (11) 3759 7627

Canada 1 (800) 833-9200

Central East Europe and the Baltics +41 52 675 3777

Central Europe & Greece +41 52 675 3777

Denmark +45 80 88 1401

Finland +41 52 675 3777

France\* 00800 2255 4835

Germany\* 00800 2255 4835

Hong Kong 400-820-5835

Ireland\* 00800 2255 4835

India +91-80-30792600

Italy\* 00800 2255 4835

Japan 0120-441-046

Luxembourg +41 52 675 3777 Macau 400-820-5835

Mongolia 400-820-5835

Mexico, Central/South America & Caribbean 52 (55) 56 04 50 90 Middle East, Asia and North Africa +41 52 675 3777

The Netherlands\* 00800 2255 4835

Norway 800 16098

People's Republic of China 400-820-5835

Poland +41 52 675 3777 Portugal 80 08 12370

Puerto Rico 1 (800) 833-9200

Republic of Korea +822-6917-5000

Russia +7 495 664 75 64

Singapore +65 6356-3900 South Africa +27 11 206 8360

Spain\* 00800 2255 4835 Sweden\* 00800 2255 4835

Switzerland\* 00800 2255 4835

Taiwan 886-2-2656-6688

United Kingdom\* 00800 2255 4835

USA 1 (800) 833-9200

\* If the European phone number above is not accessible, please call +41 52 675 3777

Contact List Updated June 2013

#### For Further Information

Tektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit www.tektronix.com

Copyright © 2015, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.

2/15 RL/WWW 55W-60038-0