## **Instruction Manual**

## **Tektronix**

92DM74 R3000 & R3000A Microprocessor Support 070-8090-00

This manual supports software Release 2, Version 1.50 and above.

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

Please check for change information at the rear of this manual.

First Edition: November 1990 Last Revised: June 1994 Online Version: April 1997 Copyright © Tektronix, Inc. 1990. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) months from the date of shipment and that the cathode-ray tubes (CRTs) in such products will be free from defects in materials and workmanship for an additional period of nine (9) months. If any such product proves defective during the initial three-month period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product. If, during the succeeding nine-month period, the CRT proves defective, Tektronix will replace the defective CRT without charge for parts and labor.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the respective warranty period and make suitable arrangements for the performance of service. Tektronix will provide such service at Customer's site without charge during the warranty period, if the service is performed within the normal on-site service area. Tektronix will provide on-site service outside the normal on-site service area only upon prior agreement and subject to payment of all travel expenses by Customer. When or where on-site service is not available, Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### WARRANTY

Tektronix warrants that this software product will conform to the specifications in the documentation provided with the product, when used properly in the specified operating environment, for a period of three (3) months. The warranty period begins on the date of shipment, except that if the program is installed by Tektronix, the warranty period begins on the date of installation or one month after the date of shipment, whichever is earlier. If this software product does not conform as warranted, Tektronix will provide remedial services as described in the documentation provided with the product. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that operation of the programs will be uninterrupted or error-free or that all errors will be corrected.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for such service in accordance with the instructions received from Tektronix. If Tektronix is unable, within a reasonable time after receipt of such notice, to provide remedial services, Customer may terminate the license for this software product and return this software product and any associated materials to Tektronix for credit or refund.

This warranty shall not apply to any software product that has been modified or altered by Customer. Tektronix shall not be obligated to furnish service under this warranty with respect to any software product a) that is used in an operating environment other than that specified or in a manner inconsistent with the User Manual and documentation or b) when the software product has been integrated with other software if the result of such integration increases the time or difficulty of analyzing or servicing the software product or the problems ascribed to the software product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THE LISTED PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO PROVIDE REMEDIAL SERVICE WHEN SPECIFIED, REPLACE DEFECTIVE MEDIA, OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **TABLE OF CONTENTS**

| Preface:   | A GUIDE TO DAS 9200 DOCUMENTATIONGENERAL SAFETY SUMMARY | vii<br>viii      |

|------------|---------------------------------------------------------|------------------|

| Section 1: | OVERVIEW                                                |                  |

|            | BASIC INFORMATION                                       | 1-1              |

|            | DAS 9200 System Software Compatibility                  | 1-1              |

|            | About This Manual                                       | 1-2              |

|            | Other Necessary Manuals                                 | 1-3              |

|            | DAS 9200 Configuration                                  | 1-3              |

|            | DIFFERENCES BETWEEN THE 92A96 AND                       |                  |

|            | 92A60/90 MODULES                                        | 1-5              |

|            | R3000/A SYSTEM REQUIREMENTS AND RESTRICTIONS            | 1-5              |

| Section 2: | QUICK START                                             |                  |

|            | INSTALLING SOFTWARE                                     | 2-1              |

|            | CONFIGURING THE PROBE ADAPTER                           | 2-2              |

|            | CONNECTING THE DAS 9200 TO THE R3000 SYSTEM             | $\frac{-}{2}$ -2 |

|            | SETTING UP THE DISASSEMBLER                             | 2-6              |

|            | ACQUIRING AND DISPLAYING DATA                           | $\frac{2}{2}$ -7 |

| Section 3: | INSTALLATION AND CONNECTIONS                            |                  |

|            | INSTALLING SOFTWARE                                     | 3-1              |

|            | Viewing the Refmem Files                                | 3-2              |

|            | Setting Up Disassembler Software                        | 3-3              |

|            | Channel Groups and Assignments                          | 3-4              |

|            | What You Can Change During Setup                        | 3-4              |

|            | Symbol Tables                                           | 3-4              |

|            | Merging Symbol Tables                                   | 3-7              |

|            | Copying and Editing the Predefined Symbol Tables        | 3-9              |

|            | LABELS                                                  | 3-10             |

|            | CONFIGURING THE PROBE ADAPTER                           | 3-10             |

|            | CONNECTING THE PROBE ADAPTER                            | 3-11             |

|            | Connecting the Probes to the Probe Adapter              | 3-12             |

|            | Placing the Probe Adapter in the SUT                    | 3-12             |

|            |                                                         | 3-13             |

|            | Connecting the Interface Housings                       | 3-17             |

|            |                                                         | 0 10             |

| Section 4: | ACQUIRING AND VIEWING DISASSEMBLED DATA CLOCKING        | 4-1              |

|            | TRIGGERING                                              | 4-1              |

|            | ACQUIRING DATA                                          | 4-2              |

|            |                                                         | 4-3<br>4-3       |

|            | DISPLAYING DISASSEMBLED DATA                            |                  |

|            | Display Formats                                         | 4-4              |

|             | Hardware Display Format                             |

|-------------|-----------------------------------------------------|

|             | Software Display Format                             |

|             | Control Flow Display Format                         |

|             | Subroutine Display Format                           |

|             | Disassembly Format Definition Overlay               |

|             | R3000 Exception Handler Entry Points                |

|             |                                                     |

|             | Bus Cycle Types                                     |

|             | Displaying the Address Group Symbolically           |

|             | Moving the Cursor                                   |

|             | Marking Cycles                                      |

|             | Manually Overriding Disassembled Instructions       |

|             | Marking a Data Sample                               |

|             | Searching Through Data                              |

|             | PRINTING DATA                                       |

| Section 5:  | HARDWARE ANALYSIS                                   |

| section 5:  | R3000 SUPPORT HARDWARE ANALYSIS                     |

|             |                                                     |

|             | Clocking                                            |

|             | Internal Clocking                                   |

|             | External Clocking                                   |

|             | Triggering                                          |

|             | Acquiring Data                                      |

|             | Displaying Data                                     |

|             | R3000 TIMING ANALYSIS                               |

|             | Restoring the R3K_Timg_96 Setup File                |

|             | Clocking                                            |

|             | Triggering                                          |

|             | Acquiring Data                                      |

|             | Displaying Data                                     |

|             | State Menu                                          |

|             | Timing Menu                                         |

|             | SEARCHING THROUGH DATA                              |

|             | PRINTING DATA                                       |

|             |                                                     |

| Appendix A: | ERROR MESSAGES AND DISASSEMBLY PROBLEMS             |

|             | MODULE ERROR MESSAGES                               |

|             | DISASSEMBLER ERROR MESSAGES                         |

|             | OTHER DISASSEMBLY PROBLEMS                          |

| Appendix B: | HOW DATA IS ACQUIRED                                |

| Khorem 19   | 92A96 CUSTOM CLOCKING                               |

|             | CUSTOM CLOCKING                                     |

|             |                                                     |

|             | ACQUIRED SIGNALS                                    |

|             | SIGNALS NOT ACQUIREDSUPPLEMENTAL TIMING INFORMATION |

|             | SUPPLEMENTAL TIMING INFORMATION                     |

| Appendix C: | SERVICE INFORMATION                                       |      |

|-------------|-----------------------------------------------------------|------|

| • •         | SERVICING SAFETY INFORMATION                              | C-1  |

|             | PROBE ADAPTER DESCRIPTION                                 | C-2  |

|             | CARE AND MAINTENANCE                                      | C-2  |

|             | SPECIFICATIONS                                            | C-4  |

|             | DISCONNECTING CLOCK AND 8-CHANNEL PROBES                  | C-11 |

|             | REMOVING AND REPLACING PODLETS                            | C-12 |

|             | Removing a Clock Probe or 8-Channel Probe Podlet from the |      |

|             | Interface Housing                                         | C-12 |

|             | Replacing a Clock Probe                                   | C-13 |

|             | Removing 8-Channel Probe Podlets from the Podlet Holder   | C-13 |

|             | Replacing 8-Channel Probe Podlets                         | C-14 |

|             | REMOVING AND REPLACING SOCKETS                            | C-15 |

|             | ZIF Socket                                                | C-16 |

|             | Replaceable Protective Sockets                            | C-16 |

|             | REPLACEABLE ELECTRICAL PARTS                              | C-19 |

|             | REPLACEABLE MECHANICAL PARTS                              | C-23 |

## **LIST OF FIGURES**

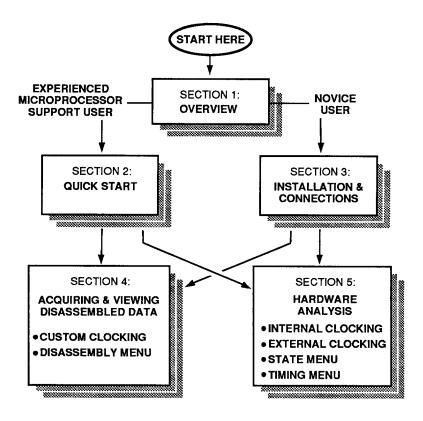

| Figure 1-1.  | How to proceed through this manual                                                            | 1-2  |

|--------------|-----------------------------------------------------------------------------------------------|------|

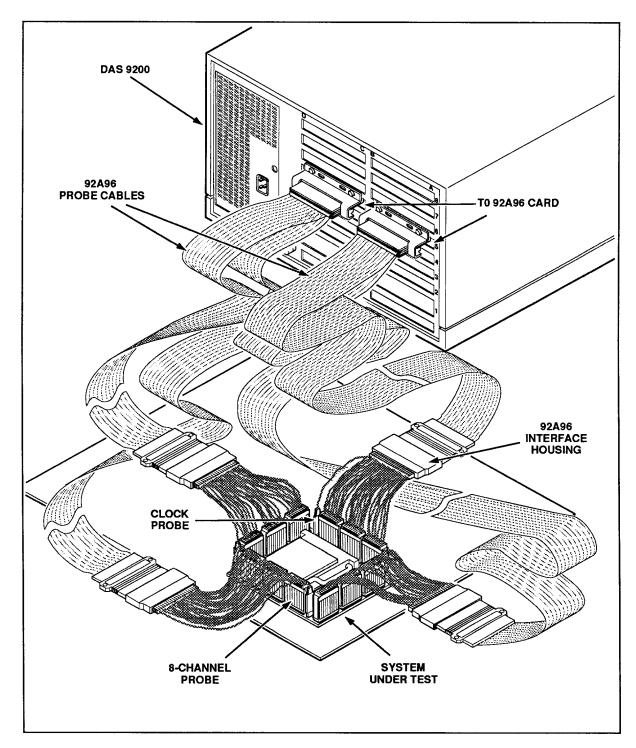

| Figure 1-2.  | Overview of a DAS 9200 connected to a system under test                                       | 1-4  |

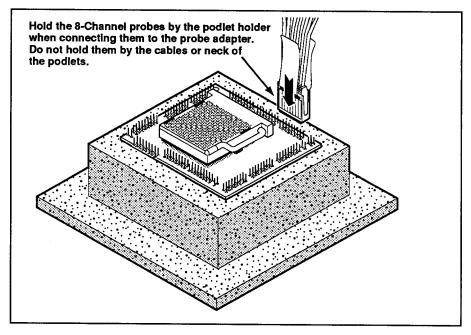

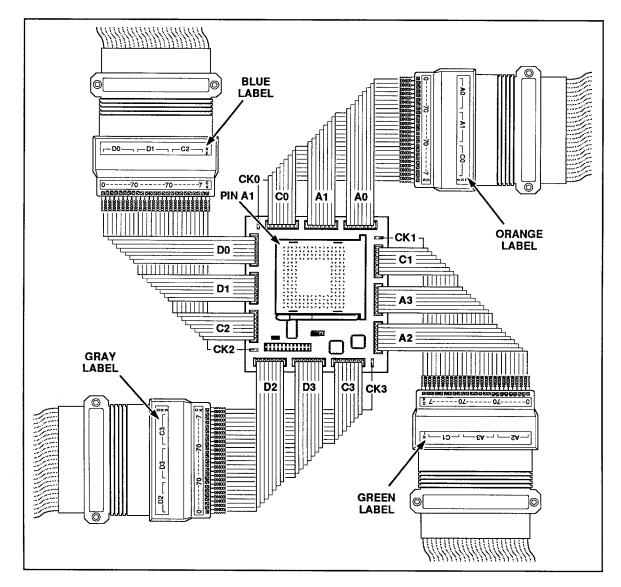

| Figure 2-1.  | Connecting the probes to the probe adapter.                                                   | 2-3  |

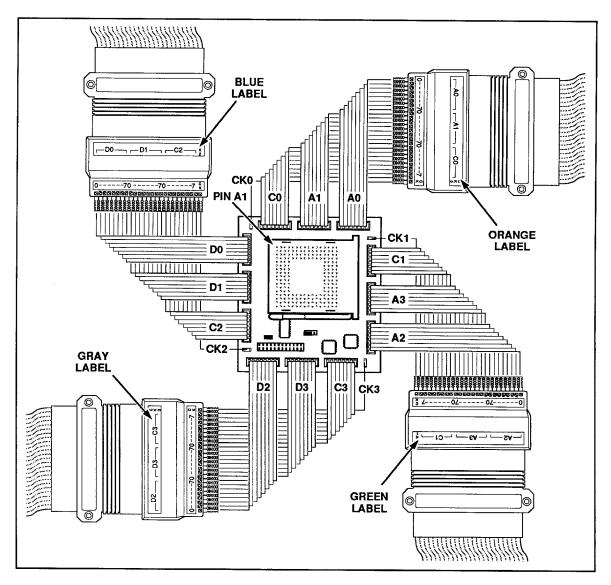

| Figure 2-2.  | Connections from the 92A96 probe cables to the probe adapter                                  | 2-4  |

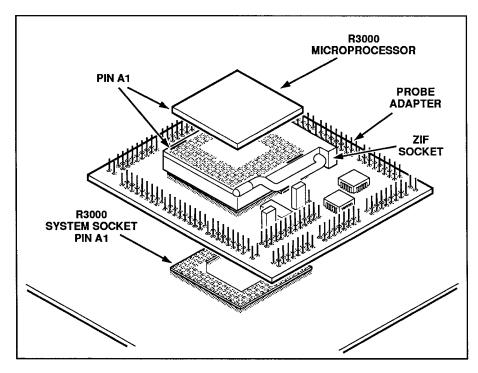

| Figure 2-3.  | Placing the probe adapter in the R3000 system                                                 | 2-5  |

| Figure 3-1.  | Probe channel color and labels on an 8-channel probe                                          | 3-10 |

| Figure 3-2.  | Applying slot number labels.                                                                  | 3-11 |

| Figure 3-3.  | Connecting the probes to the probe adapter                                                    | 3-13 |

| Figure 3-4.  | Connections from the 92A96 probe cables to the probe adapter                                  | 3-14 |

| Figure 3-5.  | Placing the probe adapter in the R3000 system                                                 | 3-16 |

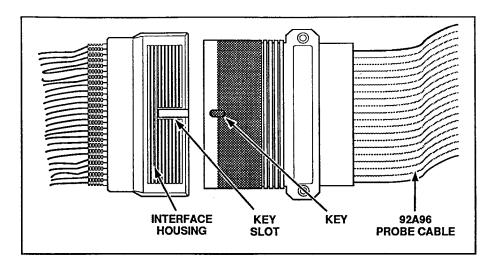

| Figure 3-6.  | Connecting the interface housing to the 92A96 probe cable                                     | 3-17 |

| Figure 4-1.  | Clock menu.                                                                                   | 4-2  |

| Figure 4-2.  | Disassembly menu.                                                                             | 4-4  |

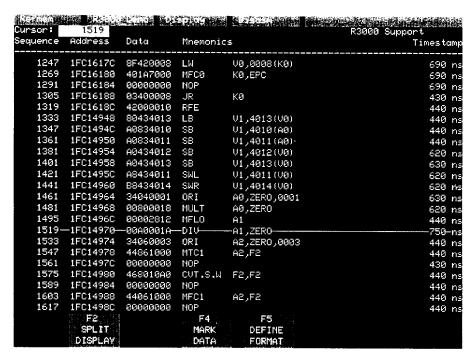

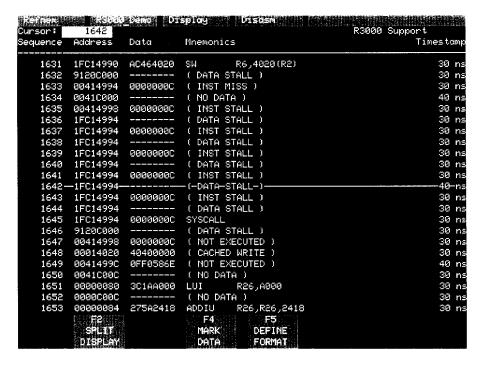

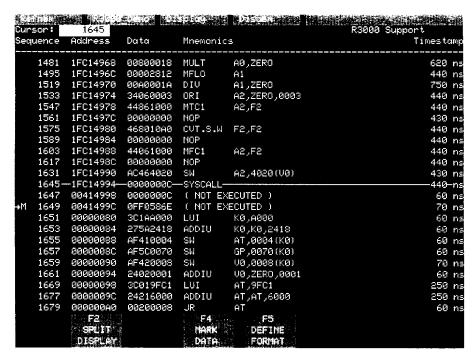

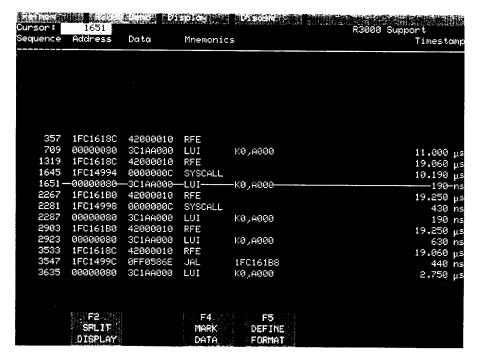

| Figure 4-3.  | Hardware display format                                                                       | 4-7  |

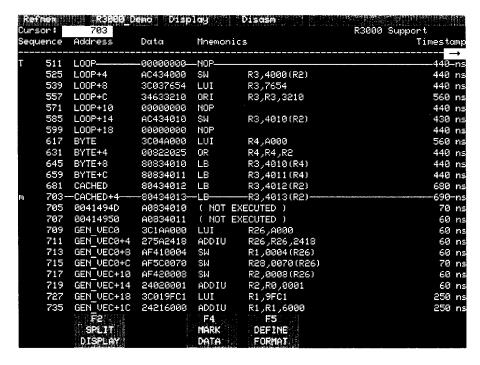

| Figure 4-4.  | Software display format                                                                       | 4-8  |

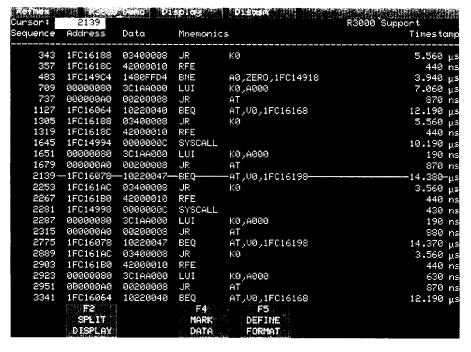

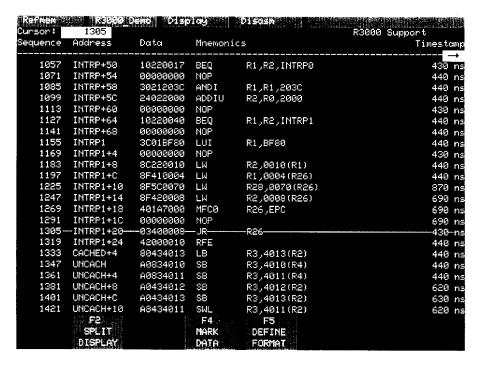

| Figure 4-5.  | Control Flow display format                                                                   | 4-9  |

| Figure 4-6.  | Subroutine display format.                                                                    | 4-10 |

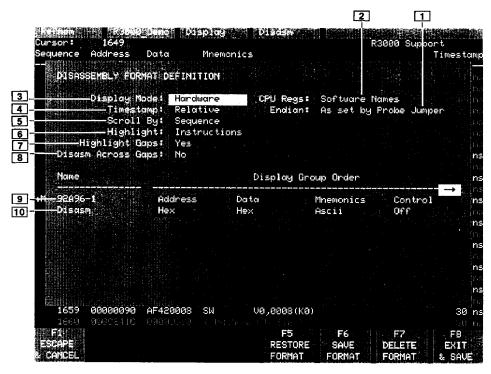

| Figure 4-7.  | Disassembly Format Definition overlay                                                         | 4-12 |

| Figure 4-8.  | Bus cycle types in the Hardware display format                                                | 4-16 |

| Figure 4-9.  | Address group displayed symbolically using the R3000_Demo file and the R3000_Addr symbol file | 4-18 |

| Figure 4-10. | Marked opcode.                                                                                | 4-21 |

| Figure 4-11. | State and Disassembly split-screen display used to                                            |      |

| Di 4 10      | perform searches.                                                                             | 4-23 |

| Figure 4-12. | Disassembly Print overlay.                                                                    | 4-25 |

| Figure 5-1.  | State data acquired with the R3K_Timg_96 setup                                                | 5-6  |

| Figure 5-2.  | Timing data displayed using the R3K_Timg_96 Timing                                            |      |

|              | Format file                                                                                   | 5-7  |

| Figure B-1   | Memory read, single-word instruction cache miss                                               | B-3  |

| Figure C-1.  | Minimum Clearance of the standard probe adapter with                                          | C-10 |

| Figure C-2.  | 8-channel probes attached                                                                     | 0-10 |

| _            | 8-channel probes attached.                                                                    | C-10 |

| Figure C-3.  | Disconnecting clock and 8-channel probes                                                      | C-11 |

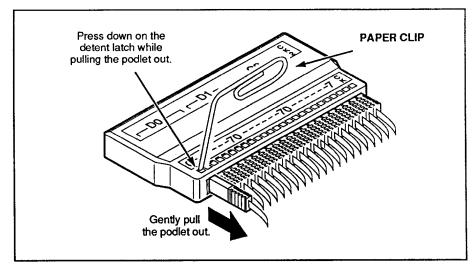

| Figure C-4.  | Removing a clock or an 8-channel probe podlet from the interface housing.                     | C-12 |

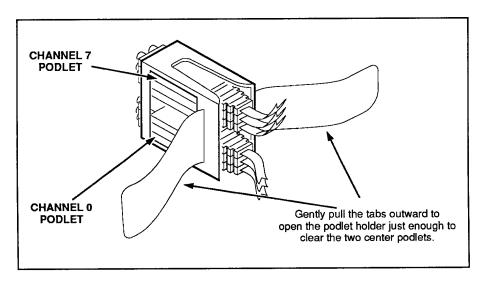

| Figure C-5.  | Ganging together the 8-channel probe podlets.                                                 | C-13 |

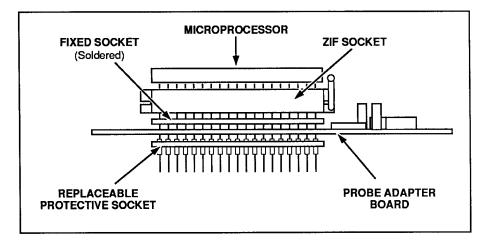

| Figure C-6.  | Side view of the probe adapter board                                                          | C-18 |

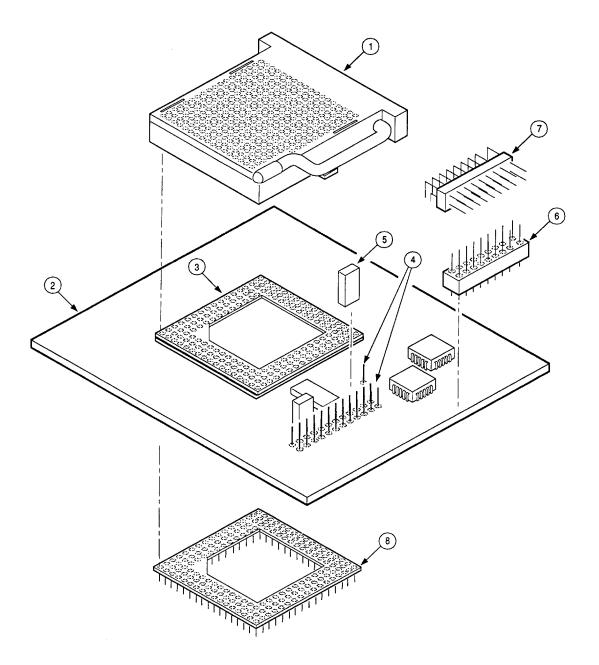

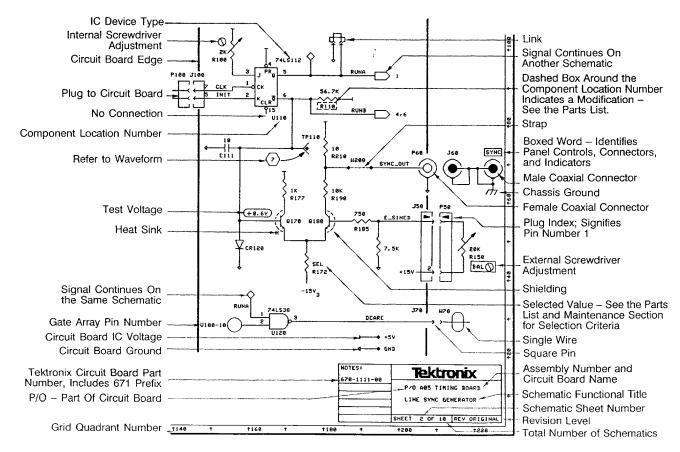

| Figure C-7.  | Probe adapter exploded view.                                                                  | C-25 |

|              |                                                                                               | U 20 |

## **LIST OF TABLES**

| Table 1-1 | Differences Between 92A96 and 92A60/90 Data Acquisition Modules | 1-5  |

|-----------|-----------------------------------------------------------------|------|

| Table 2-1 | Control Group Symbol Table (R3000_Ctrl)                         | 2-9  |

|           | Control Group Symbol Table (R3000_Ctrl)                         | 3-5  |

| Table 3-2 | Label Information                                               | 3-10 |

| Table 3-3 | Channels Available for Alternate Connections                    | 3-18 |

| Table 4-1 | Displayed Interrupt Vectors – Real Address Mode                 | 4-14 |

|           | 92DM74 Bus Cycle Types                                          | 4-15 |

| Table 5-1 | Channel Assignments for the R3K_Timg_96 Setup file              | 5-8  |

| Table B-1 | Signals Not Required for Disassembly                            | B-5  |

|           | R3000 Signals Not Acquired                                      | B-5  |

| Table B-3 | AC Characteristics of a 16-MHz R3000 Running at 16.67 MHz       | B-8  |

|           | AC Characteristics of a 20-MHz R3000 Running at 20 MHz          | B-11 |

|           | AC Characteristics of a 25-MHz R3000 Running at 25 MHz          | B-14 |

|           | AC Characteristics of a 33-MHz R3000A Running at 33.33 MHz      | B-17 |

| Table C-1 | Electrical Specifications                                       | C-4  |

|           | Physical Specifications                                         | C-6  |

|           | Environmental Specifications                                    | C-6  |

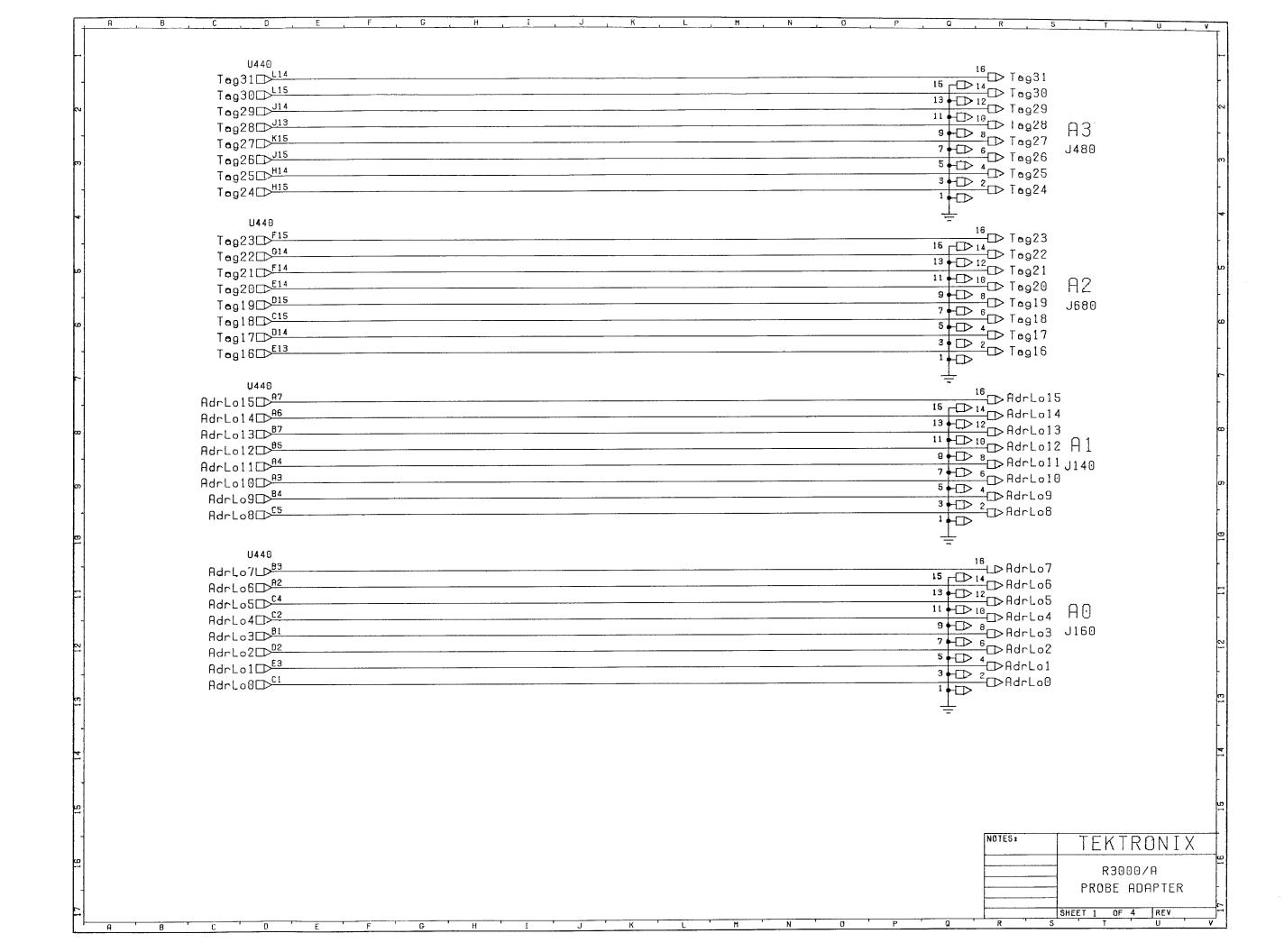

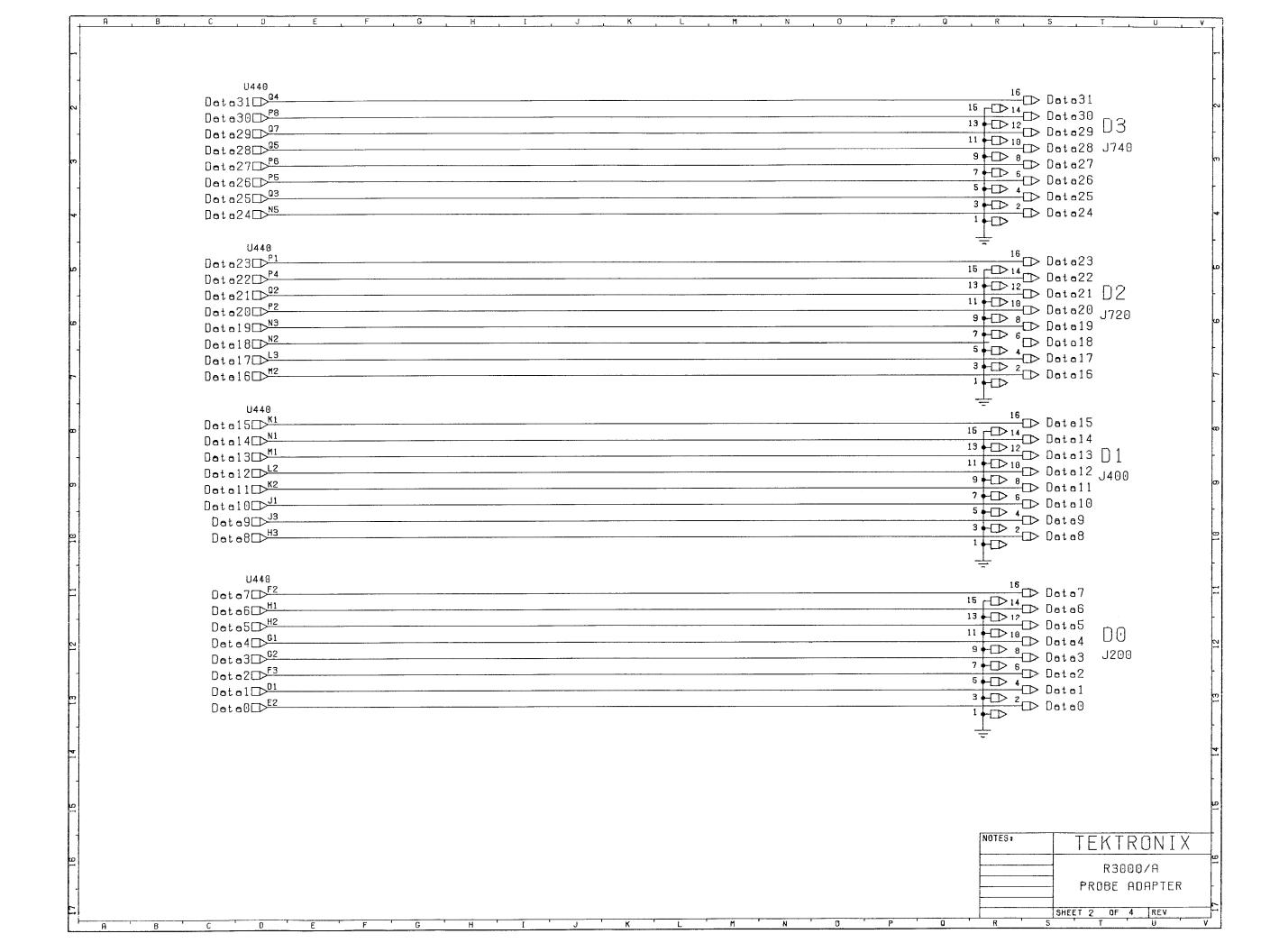

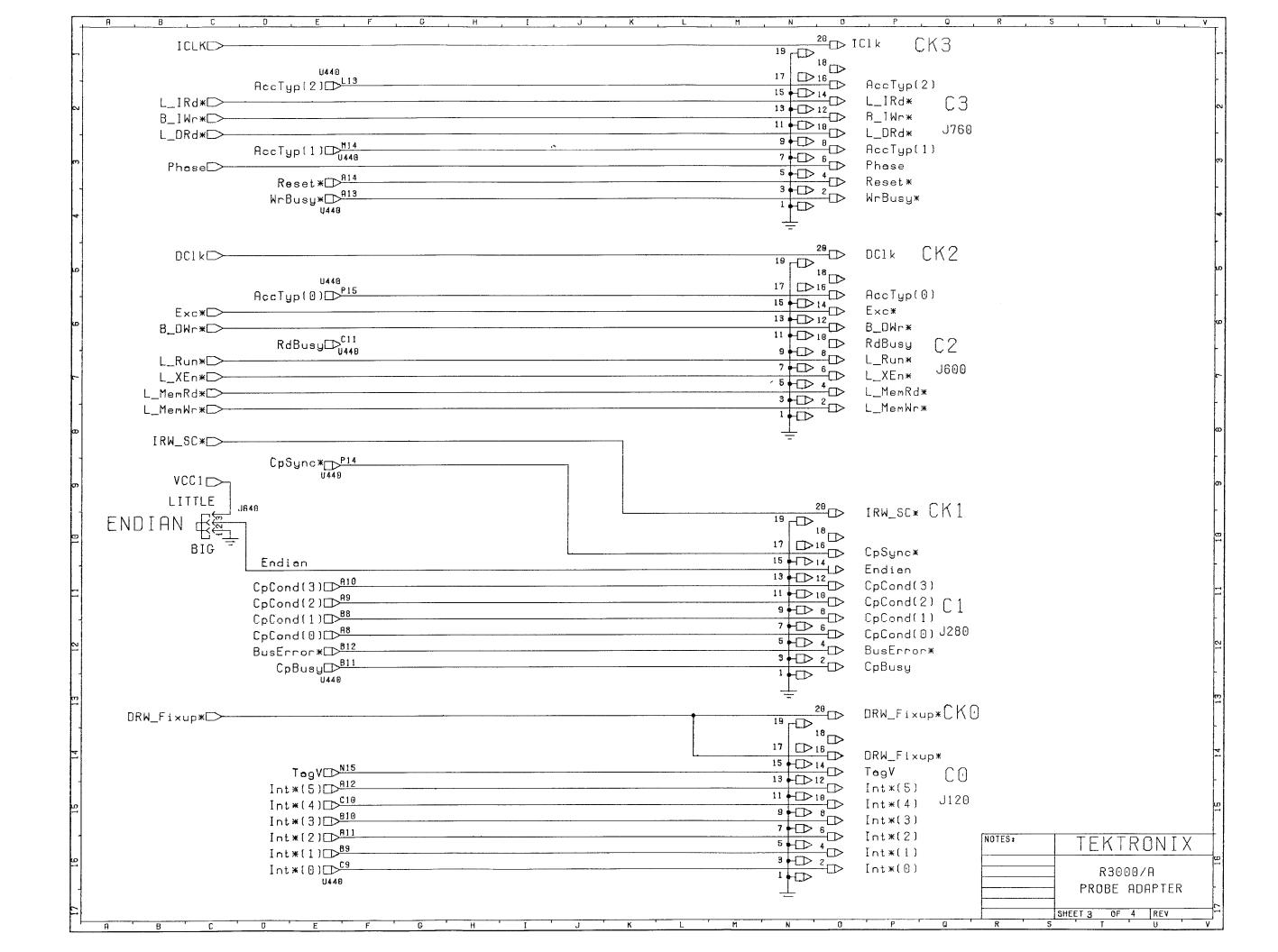

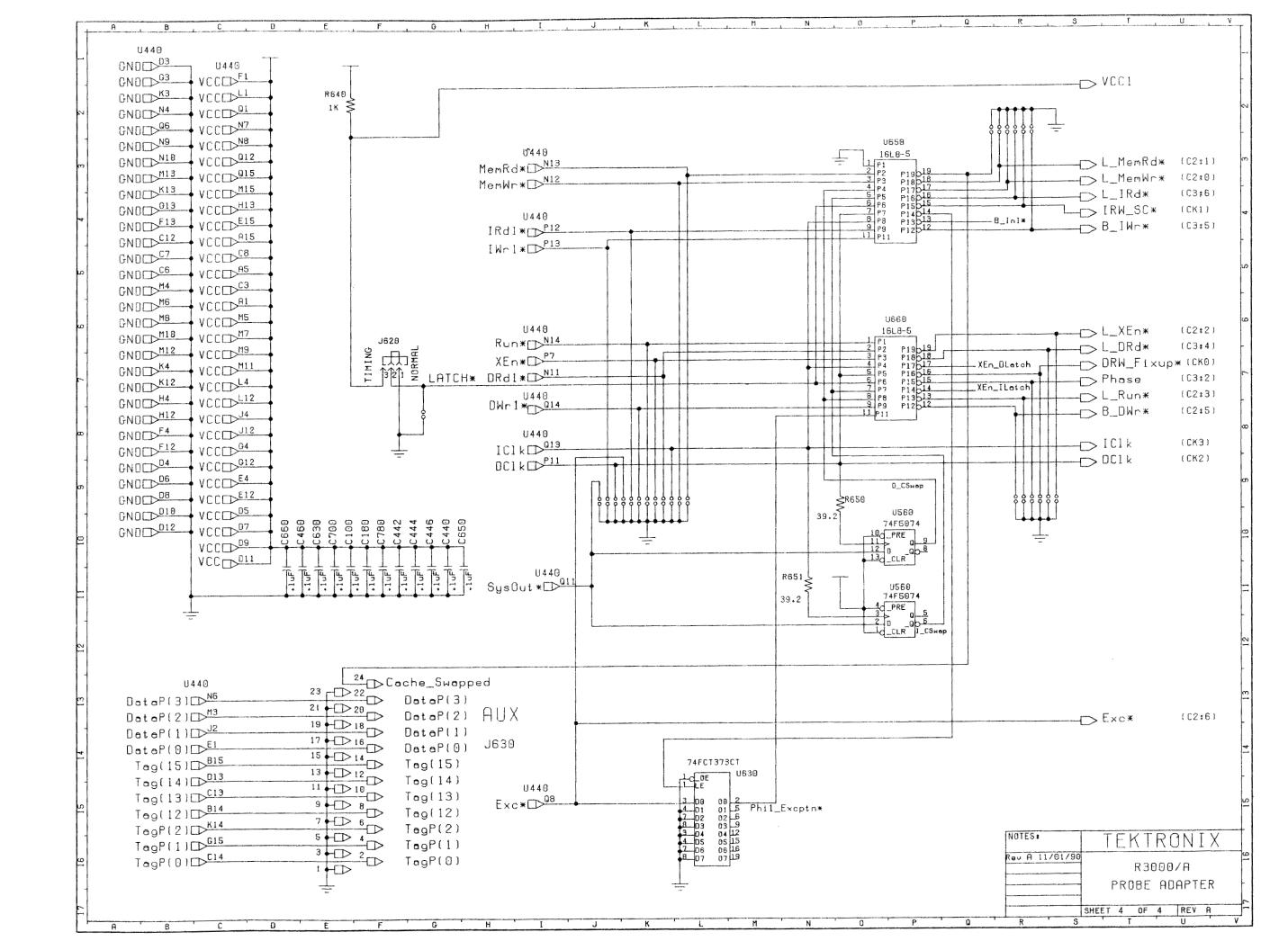

|           | 92DM74 Channel Assignments                                      | C-7  |

|           | Podlet-to-Channel Color Code                                    | C-14 |

# Preface: A GUIDE TO DAS 9200 DOCUMENTATION

The Digital Analysis System (DAS) 9200 documentation package provides the information necessary to install, operate, maintain, and service the DAS 9200. The DAS 9200 documentation consists of the following:

- a series of microprocessor-specific microprocessor support instructions that describe the various microprocessor support packages

- a system user's manual that includes a beginning user's orientation, a discussion of DAS 9200 system-level operation, and reference information such as installation procedures, specifications, error messages, and a complete system glossary

- a series of module user's manuals that describe each of the DAS 9200 acquisition, pattern generation, and optional I/O modules

- an on-line documentation package that includes "context sensitive" technical notes

- a programmatic command language user's manual that describes the set of programmatic commands available for remotely controlling the DAS 9200

- a series of **application software user's manuals** that describe the various application software packages

- a technician's reference manual that helps a qualified technician isolate DAS 9200 problems to the individual module level and determine corrective action (including onsite removal and replacement of modules)

- a verification and adjustment procedures manual that allows a qualified technician to make necessary adjustments and verify specifications of the mainframe and modules

- a series of **workbooks** that teach concepts about DAS 9200 acquisition modules and pattern generation modules

## **GENERAL SAFETY SUMMARY**

The general safety information in this summary is for operating and servicing personnel. Specific warnings and cautions can be found throughout the manual where they apply, and may not appear in this summary.

#### **TERMS IN THIS MANUAL**

CAUTION

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### TERMS AS MARKED ON EQUIPMENT

CAUTION indicates a hazard to property, including the equipment itself, and could cause minor personal injury.

WARNING indicates solely a personal injury hazard not immediately accessible as you read the marking.

DANGER indicates a personal injury hazard immediately accessible as you read the marking.

#### SYMBOLS AS MARKED ON EQUIPMENT

DANGER-High voltage.

Protective ground (earth) terminal.

ATTENTION—REFER TO MANUAL.

#### GROUNDING THE PRODUCT

This product is intended to operate from a power source that does not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground.

WARNING: This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle. A protective-ground connection by way of the grounding conductor in the power cord is essential for safe operation. (I.E.C. Safety Class I)

#### DANGER ARISING FROM LOSS OF GROUND

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulated) can render an electric shock.

#### POWER DISCONNECT

The main power disconnect is by means of the power cord or, if provided, an ac power switch.

#### **USE THE PROPER POWER CORD**

Use only the power cord and connector specified for your product. Use only a power cord that is in good condition. CSA Certification includes the equipment and power cords appropriate for use on the North America power network. All other power cords supplied are approved for the country of use.

#### **USE THE PROPER FUSE**

To avoid fire hazard use only a fuse of the correct type, voltage rating, and current rating.

#### **USE THE PROPER VOLTAGE SETTING**

Make sure the line selector is in the proper position for the power source being used.

#### **REMOVE LOOSE OBJECTS**

During disassembly or installation procedures, screws or other small objects may fall to the bottom of the mainframe. To avoid shorting out the power supply, do not power-up the instrument until such objects have been removed.

#### DO NOT OPERATE WITHOUT COVERS

To avoid personal injury or damage to the product, do not operate this product with covers or panels removed.

#### **USE CARE WITH COVERS REMOVED**

To avoid personal injury, remove jewelry such as rings, watches, and other metallic objects before removing the cover. Do not touch exposed connections and components within the product while the power cord is connected.

#### REMOVE FROM OPERATION

If you have reason to believe that the instrument has suffered a component failure, do not operate the instrument until the cause of the failure has been determined and corrected.

#### DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

## Section 1: OVERVIEW

The 92DM74 Microprocessor Support product disassembles data from systems based on the MIPS R3000 or R3000A RISC microprocessor. The 92DM74 product runs on a DAS 9200 system equipped with a 92A96 Data Acquisition Module.

This product consists of software on a floppy disk, a probe adapter, and this manual. The software includes both setup files and a disassembler program.

Included in the software files are two demonstration reference memory files. One file (called R3000\_Demo) shows disassembled data; all figures in Section 4 that show acquired data are taken from this demonstration reference memory. A second reference memory file contains timing information and is discussed in Section 5. In addition to the two reference memory files, there is a module setup file (called R3K\_Timg\_96) used to set up the DAS 9200 for asynchronous bus analysis as described in Section 5. All of these files are automatically installed on the DAS 9200 when you install the disassembler software.

#### BASIC INFORMATION

To use this product, you need to have the following:

- this manual

- other DAS 9200 mainframe and data acquisition module user's manuals

- knowledge of your specific DAS 9200 configuration and its operation

- the mips RISC Architecture (1988, Prentice Hall), IDT RISC R3000 Family System Programmer's Guide (1988, Integrated Device Technology), and R3000 Family Hardware User Manual (1988, Integrated Device Technology) or any of the equivalent manuals from the R3000 component vendors

- knowledge of your R3000 system

## **DAS 9200 System Software Compatibility**

The R3000/A application software is compatible with DAS 9200 System Software Release 2, Version 1.5 or greater. It is not compatible with previous versions.

#### About This Manual

The organization of this manual is based on the sequence of steps necessary to use the disassembler. If you are an experienced DAS 9200 user familiar with loading software and connecting microprocessor support probe adapters to a system under test, you can use the *Quick Start* section. The *Quick Start* section gives brief instructions on how to install the R3000/A software, connect the DAS 9200 to your R3000 system, configure the probe adapter, and acquire data. You can then proceed to either Section 4 or 5 depending on whether you're using disassembly or performing hardware analysis.

If you are using DAS 9200 microprocessor support for the first time, you should read some sections sequentially. Read Sections 1, 3, and 4 if you are going to acquire and view disassembled data. Read Sections 1, 3, and 5 if you are going to acquire and view timing or state data for hardware analysis. Figure 1-1 shows how to proceed through this manual.

Figure 1-1. How to proceed through this manual.

In this manual, the following conventions are used:

- the terms disassembler and disassembler software are used interchangeably throughout this manual in reference to the software that disassembles the bus cycles into instruction mnemonics and cycle types

- the terms system under test and SUT are used interchangeably when referring to the microprocessor system under test

- references to the 92A96 Data Acquisition Module include all versions of that module unless otherwise noted

- active low signals in this document have an asterisk (\*)

following the signal name; for example, Reset \*

- the term R3000 applies to both R3000 and R3000A systems

### **Other Necessary Manuals**

Before using these instructions, you should be familiar with the operation of a DAS 9200 with the data acquisition module you are using. For general instructions on the use of the DAS 9200 and a data acquisition module, refer to both the DAS 9200 System User's Manual and the data acquisition module user's manual.

Refer to the mips RISC Architecture (1989, Prentice Hall), IDT RISC R3000 Family System Programmer's Guide (1988, Integrated Device Technology), and R3000 Family Hardware User Manual (1988, Integrated Device Technology), or equivalent manuals for information about the R3000 microprocessor.

## **DAS 9200 Configuration**

To use the R3000 microprocessor support package, your DAS 9200 must be equipped with at least one 92A96 Data Acquisition Module with probe cables and standard probes.

The standard probe assemblies consist of four sets that have one clock data probe and three 8-channel data probes each. The clock probe (a single channel), and each channel of the 8-channel probe, has one signal connection and one ground connection. Leadsets and grabber tips are not required.

Figure 1-2 shows an overview of the DAS 9200 connected to the system under test.

Figure 1-2. Overview of a DAS 9200 connected to a system under test.

# DIFFERENCES BETWEEN THE 92A96 AND 92A60/90 MODULES

If you have used a DAS 9200 with a 92A60/90 Module but haven't used a 92A96 Module, there are some key differences you should note. Table 1-1 lists the key differences.

Table 1-1

Differences Between 92A96 and 92A60/90 Data Acquisition Modules

| Characteristic                            | 92A96 Module                                                                | 92A60/90 Module                            |

|-------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------|

| Maximum synchronous data sampling rates   | 100 MHz                                                                     | 20 MHz                                     |

| Maximum asynchronous data sampling rates  | 400 MHz, 24 channels or<br>200 MHz, 48 channels or<br>100 MHz, 96 channels  | 20 MHz, 60 or 90 channels                  |

| Memory depth                              | 92A96, 8K<br>92A96D, 32K                                                    | 92A90, 32K<br>92A90D, 128K                 |

| Physical connections to the probe adapter | 4 probe cables, each connecting to 1 clock probe and three 8-channel probes | 2 or 3 cables connecting to 1 buffer probe |

| Clock channels                            | Not stored as data                                                          | Stored as data                             |

| Clock Menu selections                     | Custom, Internal, External                                                  | Micro, Demux, Internal, External           |

| Flags                                     | 1 flag                                                                      | 2 flags                                    |

| Counter/timers                            | 2 counter/timers                                                            | 3 counter/timers                           |

| Counter/timer width                       | 32-bit counter/timer                                                        | 24-bit counter/timer                       |

| Word/range recognizers                    | 8 word and 0 range or<br>6 word and 1 range or<br>4 word and 2 range        | 8 word and 2 range                         |

# R3000/A SYSTEM REQUIREMENTS AND RESTRICTIONS

You should consider your system requirements and restrictions of the R3000 microprocessor before operating the disassembler. You should also consider all electrical, environmental, and mechanical specifications in Appendix C as they pertain to your system under test. The remainder of this section describes R3000 constraints.

**System Clock Rate.** The microprocessor support package supports the R3000 microprocessor running up to 33 MHz<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Specification at time of printing. Contact your DAS 9200 sales representative for current information on the fastest devices supported.

**Timing Constraints.** The 92DM74 supports various speed versions of the R3000 microprocessor. The 92DM74 timing requirements can cause timing constraints that are more restrictive than the microprocessor requirements. In addition, the microprocessor timing specifications vary from vendor to vendor. Refer to *Supplemental Timing Information* in Appendix B for information on the timing constraints of the various speed versions.

Cache Swapping. To facilitate cache invalidation and diagnostics, the R3000 microprocessor can swap the Instruction and Data caches under program control. During the cache swapping operation, the disassembler can lose a few samples or acquire a few invalid samples as it compensates for the cache swapping.

Cache Miss and Branch Detection. The disassembler detects cache misses and determines when branches are taken by scanning adjoining samples in the acquisition memory. The disassembler may not complete the scan when it disassembles samples near the beginning or near the end of the acquisition memory. Qualification gaps, extremely long stalls, or reassertion of the Reset signal can also prevent the disassembler from completing its scan. In such cases, the disassembler will assume that a cache access failed (missed) or a branch was not taken. Also, in such cases, the disassembler can incorrectly calculate the target address of a jump instruction.

Exception Processing. The disassembler monitors a signal from the R3000 CPU that indicates when the start of exception processing has blocked an instruction from executing in the instruction pipeline. The disassembler marks those instructions as Not Executed (unless it is obvious that the instruction caused the exception). You can disassemble instructions labeled ( NOT EXECUTED ) by using the Mark Data function as described in *Marking Cycles* in Section 4.

R3000 Register Nomenclature. The disassembler can display the names of the CPU's general purpose registers using either software or hardware formats as selected in the Disassembly Format Definition overlay. The disassembler uses F0–31 for the R3010 Floating Point Coprocessor general registers and descriptive names for the various coprocessor control registers. The disassembler makes no attempt to flag illegal register usage (such as specifying odd-numbered registers for floating point operations).

Byte Ordering. The disassembler uses either Big-Endian or Little-Endian memory byte ordering for instruction disassembly depending on the position of the Big/Little jumper on the probe adapter. Depending on your system's requirements, you should set this jumper to the correct position before acquiring data. You can also override the jumper position while in the Disassembly menu (refer to the Disassembly Format Definition Overlay in Section 4).

**Probe Adapter Clearance.** Your R3000 system must have a minimum amount of horizontal and vertical clearance surrounding the R3000 microprocessor to accommodate either the standard or optional probe adapter. Figures C-1 and C-2 in *Appendix C: Service Information* show these dimensions.

**R3000 System and Probe Adapter Cooling.** You must be sure to retain the original level of cooling for your R3000 system after you install the probe adapter. To maintain the required operating temperature, you may be required to provide additional cooling for the probe adapter.

**Probe Loading.** Any electrical connection to your system adds an additional ac and dc load. The 92A96 probes and R3000 probe adapter were carefully designed to add the minimum possible load to your system. This additional load may affect the operation of the R3000 system in systems with extremely tight timing margins. Appendix C contains complete specifications on how the R3000 probe adapter affects your system.

**Pin Alignment.** Because of the low profile design of the probe adapter, it is easy to misalign the probe adapter when placing it in the system under test and can damage the microprocessor, probe adapter, or the system under test. It is important to verify the proper pin alignment prior to applying power to the system under test.

## Section 2: QUICK START

If you are an experienced user of a 92A60, 92A90, or 92A96 Data Acquisition Module, you can use this section to quickly set up your system and use it. Before setting up your system, read the discussion on R3000/A System Requirements and Restrictions in Section 1.

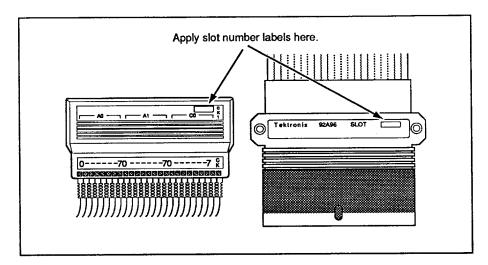

If you have more than one 92A96 Module in the DAS 9200, you should apply slot number labels to various parts of the DAS 9200 equipment. Refer to the discussion on *Labels* in Section 3 for a description of where to apply the slot number labels. These slot numbers will help you identify which 92A96 Module is connected to the probe adapter in a multimodule system.

A Symbol table is presented at the end of this Section for you to remove or photocopy. This provides you with an easy reference when setting up the Trigger menu using symbols. The symbol table is duplicated in Section 3 in case it is lost or damaged after being removed.

The probe adapter is shipped with a 145-pin replaceable protective socket installed in addition to a 175-pin socket. If your R3000 system uses the R3000A microprocessor, you need to replace the 145-pin socket with the 175-pin socket. Refer to Removing and Replacing Sockets in Appendix C for instructions on replacing the protective sockets.

#### INSTALLING SOFTWARE

To install the R3000 support software, follow these steps:

- 1. Power on the DAS 9200 and select the Disk Services menu.

- 2. Select Install Application and press F8: EXECUTE OPERATION.

- 3. Follow the on-screen prompts.

You may need to remove applications or files from the hard disk if there is not enough available disk free space to accommodate the microprocessor support files.

#### CONFIGURING THE PROBE ADAPTER

The R3000 probe adapter has two user-configurable jumpers that must be configured before you acquire data the first time.

The Big/Little Endian jumper lets you select the byte ordering: Big-Endian or Little-Endian. Determine which byte ordering is required by your system and set the jumper accordingly. The jumper is shipped in the Big-Endian position.

The Timing/Normal jumper lets you configure the disassembler to run in Timing (Transparent) mode. The Timing mode bypasses the additional latching or stretching of selected signals on the probe adapter. Signals that are buffered or latched in the Normal mode are buffered in the Timing mode. For Disassembly purposes, you should leave the jumper in the Normal position. Determine whether or not you need to run in Transparent mode and set the jumpers accordingly.

# CONNECTING THE DAS 9200 TO THE R3000 SYSTEM

To connect the 92A96 Module clocks and 8-channel probes to the probe adapter, follow this procedure:

## CAUTION

Static discharge can damage the microprocessor, 8-channel probes, clock probes, or the 92A96 Module. To prevent static damage, observe the following precautions while following all connection procedures.

Handle the microprocessor only in a static-free environment.

Always wear a grounding wrist strap, or similar device, while handling the microprocessor and probe adapter.

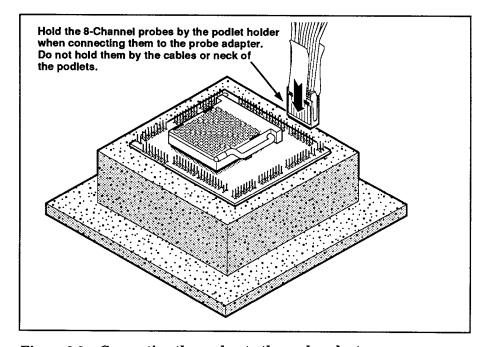

Discharge stored static electricity from the probe adapter by touching any of the ground pins (the row of pins closest to the edge of the probe adapter circuit board). 1. Use the antistatic shipping material to support the probe adapter while connecting the clock and 8-channel probes as shown in Figure 2-1. This prevents the circuit board from being flexed and the socket pins from being bent.

Figure 2-1. Connecting the probes to the probe adapter.

2. Match the Section names and channel numbers on the interface housing to the probe adapter.

## CAUTION

Connect only the signal connectors to the signal pins and the ground connectors to the ground pins. Connecting any R3000 signal to a probe adapter ground pin can damage the microprocessor or the probe adapter circuitry.

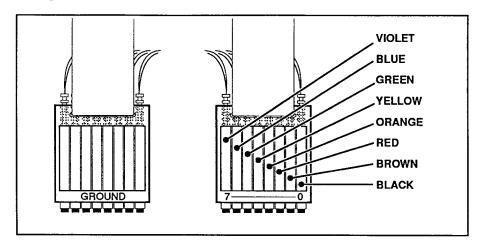

3. Connect the clocks and 8-channel probes to the appropriate sets of square pins on the probe adapter as shown in Figure 2-2. The signal connector is on the color-coded side of the podlet; the ground connector is on the opposite side of the podlet.

#### NOTE

If your podlets are not installed in a podlet holder, or are not installed in the proper order, refer to Removing and Replacing Podlets in Appendix C.

4. Power down your R3000 system and carefully remove the microprocessor. (It is not necessary to power down the DAS 9200.)

Figure 2-2. Connections from the 92A96 probe cables to the probe adapter.

### CAUTION

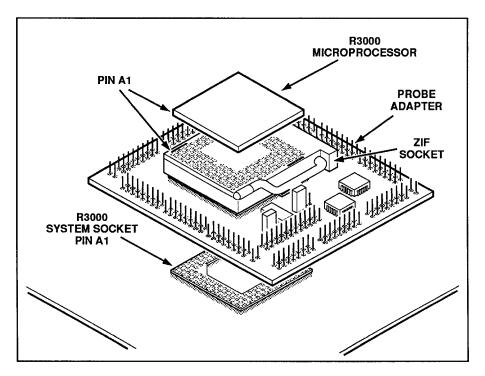

The microprocessor can be permanently damaged if you insert it improperly on the probe adapter. Pin A1 on the microprocessor must align with pin A1 on the ZIF socket of the probe adapter.

Offsetting the probe adapter by one row of pins on the SUT can damage the microprocessor, probe adapter, or SUT. The probe adapter must align with pin A1 of the SUT. See Figure 2-3 for proper alignment of pin A1 on the microprocessor, the ZIF socket, and the R3000 system socket.

5. Refer to Figure 2-3 and carefully plug the probe adapter into the R3000 system socket. Align pin A1 on the probe adapter to pin A1 on the R3000 system socket.

Figure 2-3. Placing the probe adapter in the R3000 system.

#### NOTE

If your system under test has a ZIF socket with a lever attached, you might need to remove the protective socket from the bottom of the probe adapter, place it in your system's ZIF socket, close the ZIF socket, and install the probe adapter in the protective socket. Refer to Removing and Replacing Sockets in Appendix C for information on removing the protective sockets from the probe adapter.

- 6. Open the ZIF socket by pulling the lever up and away from the socket.

- 7. Carefully plug the microprocessor into the ZIF socket. Align pin A1 on the microprocessor to pin A1 of the socket.

- 8. Push the ZIF socket's lever down to lock the ZIF socket.

If the 92A96 Module probe cables are not already connected to the interface housings, refer to Figure 2-2 and follow this procedure:

- 1. Match the color of the label on the interface housing to the color of the label on the loose end of a 92A96 probe cable.

- 2. Line up the key and key slot and connect them.

- 3. Repeat steps 1 and 2 for the other three interface housings and probe cables.

#### SETTING UP THE DISASSEMBLER

The 92DM74 software is designed to work with a single 92A96 Module only. If your DAS 9200 contains more than one 92A96 Module, you will have to use the System Configuration menu to reconfigure the 92A96 Modules into singlecard modules prior to setting up the disassembler.

To set up the disassembler, perform the following steps:

1. Access the Configuration menu and select R3000 Support in the Software Support field. When you do this, the Channel, Clock, and Trigger menus will be set up for microprocessor support.

#### NOTE

Remember to read the discussion R3000 System Requirements and Restrictions in Section 1 prior to setting up the 92A96 Module for disassembly. Do not disturb the Address, Data, Jumper, or Control groups (in the Channel menu) or the channel assignments within them while using the disassembler. Changing these groups causes invalid instruction mnemonics disassembly. You can find the channel group definitions and channel assignments in Appendix C.

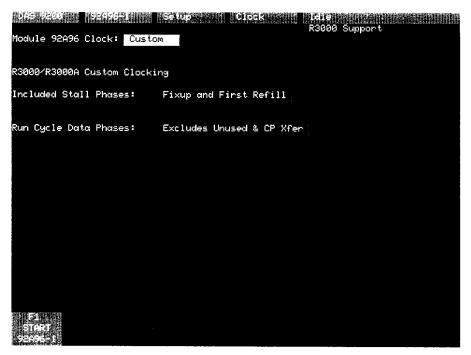

- 2. Refer to the Clock menu and set up your Custom clocking choices. Refer to Appendix B for details on the clocking selections available with the Custom clocking menu.

- If you are performing hardware analysis, you can select Internal or External clocking in the Clock menu.

Mnemonic disassembly and the Control group Symbol Table labels can be invalid with either of these clocking modes.

- 4. The default trigger program will trigger on the first data sample acquired after pressing F1: START. Select the Trigger menu if you want to change the trigger program.

Table 2-1 is a Control group symbol table intended for you to remove or photocopy and use while performing disassembly. Refer to Section 4 for information on displaying the Control group with the Disassembly menu.

#### **ACQUIRING AND DISPLAYING DATA**

After completing the DAS 9200 and probe adapter setups, you can acquire and display data. Perform the following steps:

- 1. Power on the R3000 system under test.

- 2. Press F1: START.

After satisfying the trigger program and filling acquisition memory, the DAS 9200 will display data in the default State menu.

- 3. Select the Disasm menu from the Menu Selection overlay to view disassembled data.

- 4. Select the State menu or the Timing menu from the Menu Selection overlay to view data for hardware or timing analysis. (Note that the probe adapter circuitry latches and stretches some signals to help the disassembly unless the Timing/Normal jumper is placed in the Timing position.)

The Disassembly menu displays the disassembled data in different formats:

- Hardware format shows instruction mnemonics on Fetch cycles and cycle-type information for all other cycles.

- Software format shows only opcode fetches; all other cycle types are suppressed.

- Control Flow format shows only instructions that change the control flow.

- Subroutine format shows only subroutine calls, exceptions, and returns.

Refer to Appendix A: Error Messages and Disassembly Problems if you have problems acquiring and displaying data.

This is the end of the Quick Start section.

Table 2-1 Control Group Symbol Table (R3000\_Ctrl)

|                        |     |   |            |      |     | (   | Cor      | ntrol G | rou | p Va        | alue         | )       |     |             |              |         |                                                         |

|------------------------|-----|---|------------|------|-----|-----|----------|---------|-----|-------------|--------------|---------|-----|-------------|--------------|---------|---------------------------------------------------------|

|                        | Rur |   | ase<br>Exc | ·•   | IRd | lWr | •<br>DRo | J*      | Ме  | mRd⁴<br>Mem | Wr⁴<br>RdBus | sy      | Res | et*<br>AccT | yp2<br>AccTy | vp1     |                                                         |

| Symbol                 |     |   |            | XEn* |     |     |          | DWr*    |     |             | ,            | ŴrBusy* |     |             |              | АссТур0 | Meaning                                                 |

| INSTR_<br>STREAMING    | 0   | 1 | Х          | 0    | Х   | χ   | Χ        | Х       | Х   | Х           | Χ            | Χ       | 1   | Х           | Х            | Χ       | Instruction fetched during streaming                    |

| SWAPPED_<br>INST_RUN   | 0   | 1 | X          | Χ    | X   | Χ   | 0        | X       | Χ   | X           | Χ            | Χ       | 1   | Χ           | Χ            | Χ       | Swapped Instruction run cycle                           |

| INST_RUN/<br>EXC1W     | 0   | 1 | 0          | X    | X   | Χ   | X        | X       | X   | X           | X            | X       | 1   | X           | Х            | Χ       | Exception indication Exc1W†                             |

| INST_RUN               | 0   | 1 | X          | Χ    | X   | Χ   | Χ        | X       | X   | Χ           | Χ            | X       | 1   | Χ           | Χ            | X       | Instruction Phase of a run cycle                        |

| INST_STALL/<br>RETRY   | 1   | 1 | Х          | 0    | Х   | Χ   | Χ        | X       | X   | X           | 1            | X       | 1   | Χ           | Χ            | Х       | Instruction Phase of a<br>Stall, read with Retry        |

| INST_FIXUP/<br>READ    | 1   | 1 | 0          | 0    | X   | X   | Х        | X       | Χ   | X           | X            | X       | 1   | Χ           | Χ            | Х       | Instruction Read from main memory during                |

| INST_REFILL            | 1   | 1 | 1          | 0    | Χ   | χ   | X        | Χ       | X   | Χ           | Χ            | X       | 1   | Χ           | Χ            | Х       | a Fixup cycle<br>Instruction Phase of a<br>Refill cycle |

| INST_FIXUP             | 1   | 1 | 0          | Χ    | Χ   | Χ   | Χ        | X       | X   | X           | Χ            | X       | 1   | Χ           | Χ            | Χ       | Instruction Phase of a Fixup cycle‡                     |

| INST_STALL             | 1   | 1 | 1          | Χ    | Χ   | Χ   | Χ        | X       | X   | Χ           | Χ            | X       | 1   | Χ           | Χ            | Х       | Instruction Phase of a<br>Stall cycle‡                  |

| UNCACHED_<br>INST      | Х   | 1 | Χ          | 0    | Х   | 1   | Χ        | 1       | X   | X           | Χ            | X       | 1   | Χ           | Χ            | Χ       | Any uncached Instruction fetch                          |

| MAIN_MEM_<br>INST_READ | Х   | 1 | Χ          | 0    | Х   | Χ   | X        | Χ       | Х   | Χ           | Χ            | X       | 1   | Χ           | Χ            | Χ       | Read instruction from main memory                       |

| DATA_RUN/<br>RD_BYTE   | 0   | 0 | Х          | Х    | Х   | Χ   | 0        | Χ       | X   | Χ           | Χ            | X       | 1   | 0           | 0            | 0       | Data Phase run cycle single-byte read                   |

| DATA_RUN/<br>RD_2-BYTE | 0   | 0 | Х          | Χ    | Χ   | Χ   | 0        | Χ       | Χ   | Χ           | Χ            | X       | 1   | 0           | 0            | 1       | Data Phase run cycle<br>half word read                  |

| DATA_RUN/<br>RD_3-BYTE | 0   | 0 | Χ          | Χ    | Χ   | Χ   | 0        | X       | Χ   | Х           | Χ            | X       | 1   | 0           | 1            | 0       | Data Phase run cycle tribyte read                       |

| DATA_RUN/<br>RD_WORD   | 0   | 0 | Х          | X    | Χ   | Χ   | 0        | X       | X   | X           | Х            | Χ       | 1   | 0           | 1            | 1       | Data Phase run cycle<br>word read                       |

| DATA_RUN/<br>READ      | 0   | 0 | Х          | Χ    | Χ   | Χ   | 0        | X       | Χ   | Х           | Χ            | X       | 1   | Χ           | Χ            | Х       | Data Phase run cycle read from D cache                  |

| SWAPPED_<br>DATA_READ  | 0   | 0 | Χ          | Χ    | 0   | Χ   | Х        | X       | X   | Χ           | Χ            | X       | 1   | Χ           | Χ            | Х       | Data Phase run cycle read from I cache                  |

| DATA_RUN/<br>WR_BYTE   | 0   | 0 | Х          | X    | Х   | Χ   | Χ        | X       | X   | 0           | Χ            | X       | 1   | 0           | 0            | 0       | Data Phase run cycle single-byte write                  |

| DATA_RUN/<br>WR_2-BYTE | 0   | 0 | Χ          | X    | Х   | χ   | X        | Χ       | Χ   | 0           | Χ            | χ       | 1   | 0           | 0            | 1       | Data Phase run cycle half word write                    |

| DATA_RUN/<br>WR_3-BYTE | 0   | 0 | Х          | Χ    | X   | Χ   | X        | X       | Χ   | 0           | Χ            | X       | 1   | 0           | 1            | 0       | Data Phase run cycle tribyte write                      |

| DATA_RUN/<br>WR_WORD   | 0   | 0 | X          | X    | Χ   | χ   | X        | X       | X   | 0           | Χ            | X       | 1   | 0           | 1            | 1       | Data Phase run cycle<br>word write                      |

| DATA_RUN/<br>WRITE     | 0   | 0 | Χ          | Χ    | Χ   | Χ   | Χ        | X       | X   | 0           | Χ            | X       | 1   | Х           | Χ            | Х       | Data Phase run cycle write                              |

| CP_TRANSFER            | 0   | 0 | Х          | 1    | 1   | 1   | 1        | 1       | Х   | 1           | Х            | Χ       | 1   | 0           | Χ            | Х       | Coprocessor transfer                                    |

(Cont.)

Table 2-1 (Cont.)

Control Group Symbol Table (R3000\_Ctrl)

|                                           | Control Group Value |     |            |           |        |        |     |           |        |                     |        |               |     |             |             |                |                                                             |

|-------------------------------------------|---------------------|-----|------------|-----------|--------|--------|-----|-----------|--------|---------------------|--------|---------------|-----|-------------|-------------|----------------|-------------------------------------------------------------|

| Symbol                                    | Run                 | Pha | ase<br>Exc | *<br>XEn* | IRd    | lWr    | DRd | ÷<br>DWr⁴ | Mei    | mRd*<br><b>M</b> em | RdBus  | sy<br>WrBusy⁺ | Res | et*<br>AccT | yp2<br>Acc⊺ | /p1<br>AccTyp0 | Meaning                                                     |

| DATA_<br>TRANSFER                         | 0                   | 0   | Χ          | Χ         | Χ      | Х      | Х   | Х         | Χ      | Х                   | Х      | Х             | 1   | 0           | Х           | Х              | Data Phase run cycle<br>with data transfer<br>scheduled     |

| NO_DATA                                   | 0                   | 0   | Χ          | Χ         | Χ      | Χ      | Χ   | Х         | X      | Χ                   | X      | X             | 1   | 1           | Х           | Χ              | Data Phase run cycle with no data                           |

| DATA_RUN/<br>INTGR2M                      | 0                   | 0   | 0          | Χ         | Χ      | Χ      | Χ   | X         | Χ      | Χ                   | Χ      | Χ             | 1   | χ           | Χ           | X              | transfer scheduled<br>Interrupt grant signal<br>IntGr2M†    |

| DATA_RUN                                  | 0                   | 0   | Χ          | X         | X<br>X | X<br>X | X   | X         | X<br>X | X<br>X              | Х<br>1 | Χ             | 1   | Χ           | Χ           | Χ              | Data Phase run cycle                                        |

| DATA_STALL_/<br>READ_RETRY<br>DATA_STALL/ | 1 1                 | 0   | 1          | 0         | X<br>X | X<br>X | X   | X<br>0    | X      | X                   | 1<br>X | X             | 1   | X           | X           | X<br>X         | Read Retry caused<br>by RdBusy                              |

| RD_CACHED<br>SWAPPED_                     | 1                   | 0   | 1          | 0         | X      | 0      | X   | Х         | X      | X                   | X      | X             | 1   | X           | X           | X              | Data Phase Stall<br>cycle cached read<br>Swapped Data Phase |

| DATA_STALL/<br>RD_CACHED<br>DATA_STALL/   | 1                   | 0   | 1          | 0         | Χ      | 1      | Χ   | 1         | Х      | Х                   | Χ      | X             | 1   | χ           | Х           | Х              | Stall cycle cached read Data Phase Stall                    |

| RD_<br>UNCACHED                           |                     | _   | 4          |           |        |        |     |           |        |                     |        |               |     |             |             |                | cycle uncached read                                         |

| DATA_STALL/<br>RD_BYTE                    | 1                   | 0   | 1          | 0         | Х      | Χ      | Χ   | X         | Χ      | Χ                   | X      | Χ             | 1   | Χ           | 0           | 0              | Data Phase Stall cycle single-byte read                     |

| DATA_STALL/<br>RD_2-BYTE                  | 1                   | 0   | 1          | 0         | X      | Χ      | Х   | Χ         | X      | Χ                   | X      | X             | 1   | χ           | 0           | 1              | Data Phase Stall cycle half word read                       |

| DATA_STALL/<br>RD_3-BYTE                  | 1                   | 0   | 1          | 0         | X      | Χ      | Χ   | Χ         | X      | Χ                   | Χ      | Χ             | 1   | Χ           | 1           | 0              | Data Phase Stall cycle tribyte read                         |

| DATA_STALL/<br>RD_WORD                    | 1                   | 0   | 1          | 0         | X      | Χ      | Χ   | Χ         | X      | Χ                   | Χ      | X             | 1   | Χ           | 1           | 1              | Data Phase Stall cycle word read                            |

| DATA_STALL/<br>READ                       | 1                   | 0   | 1          | 0         | X      | Χ      | Χ   | χ         | X      | X                   | X      | X             | 1   | Χ           | χ           | Χ              | Data Phase Stall cycle read                                 |

| DATA_STALL/<br>WR_BYTE                    | 1                   | 0   | 1          | 1         | X      | X      | X   | Χ         | X      | 0                   | X      | Х             | 1   | X           | 0           | 0              | Data Phase Stall cycle single-byte write                    |

| DATA_STALL/<br>WR_2-BYTE                  | 1                   | 0   | 1          | 1         | X      | Χ      | Χ   | Χ         | X      | 0                   | Χ      | X             | 1   | Χ           | 0           | 1              | Data Phase Stall cycle half word write                      |

| DATA_STALL/<br>WR 3-BYTE                  | 1                   | 0   | 1          | 1         | X      | Χ      | χ   | X         | X      | 0                   | Χ      | Χ             | 1   | Χ           | 1           | 0              | Data Phase Stall cycle tribyte write                        |

| DATA_STALL/<br>WR_WORD                    | 1                   | 0   | 1          | 1         | X      | Χ      | χ   | Χ         | X      | 0                   | Χ      | χ             | 1   | Χ           | 1           | 1              | Data Phase Stall cycle word write                           |

| DATA_STALL/<br>WRITE                      | 1                   | 0   | 1          | 1         | X      | Χ      | Χ   | Χ         | X      | 0                   | Χ      | χ             | 1   | Χ           | Χ           | X              | Data Phase Stall cycle write                                |

| CP_STALL                                  | 1                   | 0   | 0          | Χ         | Χ      | Χ      | Χ   | Χ         | X      | Χ                   | Χ      | χ             | 1   | Χ           | Χ           | Χ              | Coprocessor Stall cycle                                     |

| MP_STALL_<br>READ                         | 1                   | 0   | 1          | 1         | X      | Χ      |     | Χ         | Χ      | 1                   | Χ      | χ             | 1   | Χ           | Χ           | Χ              | Multiprocessor Stall cycle read                             |

| MP_STALL_<br>INVALIDATE                   | 1                   | 0   | 1          | 1         | Χ      |        | χ   | 0         | X      | 1                   | Χ      | Χ             | 1   | Χ           | Χ           | Χ              | Multiprocessor Stall cycle write                            |

| DATA_STALL                                | 1                   | 0   | Χ          | Χ         | Χ      | X      | X   | Х         | Х      | χ                   | X      | Χ             | 1   | X           | Χ           | X              | Data Phase Stall cycle                                      |

(Cont.)

Table 2-1 (Cont.)

Control Group Symbol Table (R3000\_Ctrl)

|                            |     |     |            |           |      | (   | Con | trol G        | rou | p Va         | alue | !     |              |                |         |   |                                |

|----------------------------|-----|-----|------------|-----------|------|-----|-----|---------------|-----|--------------|------|-------|--------------|----------------|---------|---|--------------------------------|

| Symbol                     | Run | Pha | ase<br>Exc | •<br>XEn* | IRd⁴ | lWr | DRd | D <b>W</b> r* | Mer | y<br>VrBusy⁴ | Res  | AccTy | /p2<br>AccTy | rp1<br>AccTyp0 | Meaning |   |                                |

| MAIN_MEM_<br>DATA READ     | Х   | 0   | Х          | 0         | Χ    | Χ   | Х   | Х             | Х   | Х            | Χ    | Χ     | 1            | Х              | Χ       | Х | Main memory Data<br>Phase read |

| WRITE_<br>I CACHE_<br>ONLY | Х   | 0   | Х          | X         | Χ    | 0   | Χ   | Х             | Х   | 1            | Χ    | X     | 1            | X              | X       | X | Instruction cache write        |

| WRITE_<br>DCACHE_<br>ONLY  | Х   | 0   | X          | Χ         | Χ    | Χ   | Χ   | 0             | Χ   | 1            | Χ    | X     | 1            | Χ              | X       | X | Data cache write               |

| MAIN_MEM_<br>READ          | Х   | Χ   | Χ          | 0         | Χ    | Χ   | Χ   | Χ             | X   | χ            | Χ    | χ     | 1            | Χ              | Χ       | Χ | Main memory read               |

| MAIN_MEM_<br>WRITE         | Х   | 0   | Χ          | X         | X    | Χ   | X   | X             | X   | 0            | X    | 1     | 1            | X              | Χ       | Χ | Main memory write              |

| RESET_INST_<br>PHASE       | Х   | 1   | Χ          | Χ         | Χ    | X   | Х   | Χ             | X   | Χ            | Χ    | X     | 0            | X              | Χ       | Χ | Instruction Phase reset        |

| RESET_DATA_<br>PHASE       | Х   | 0   | Χ          | Χ         | Χ    | Χ   | X   | X             | χ   | Χ            | Χ    | Χ     | 0            | Χ              | Χ       | X | Data Phase reset               |

| RESET                      | Х   | Χ   | Χ          | Χ         | Χ    | χ   | Χ   | Χ             | Χ   | Χ            | Χ    | Χ     | 0            | Χ              | Χ       | Χ | Any reset                      |

<sup>†</sup> Exc1W\* and IntGr2M\* are Run cycles with Exception\* (Exc\*) asserted as defined by the MIPS R3000 Processor Interface.

<sup>‡</sup> These symbols may not display or trigger correctly at higher CPU clock rates due to the effects of the T<sub>SExc</sub> timing delay specification. Refer to Supplemental Timing Information for additional information on the timing specifications.

## **Section 3: INSTALLATION AND CONNECTIONS**

This section contains detailed descriptions of how to do the following:

- install the disassembler software

- view the demonstration reference memory

- set up the disassembler software

- connect the DAS 9200 to the system under test (SUT)

- configure the probe adapter

You must install the microprocessor support software prior to invoking and setting up the disassembler. It does not matter if you install the software before or after making the DAS 9200 connections and configuring the probe adapter.

You should configure the probe adapter before connecting the DAS 9200 to the R3000 system. Configuring the probe adapter consists of setting two jumpers and (if necessary) selecting the correct replaceable socket for the probe adapter. Details on configuring the probe adapter are give later in this section.

The probe adapter is shipped with a 145-pin replaceable protective socket installed in addition to a 175-pin socket. If your R3000 system uses the R3000A microprocessor, you need to replace the 145-pin socket with the 175-pin socket. Refer to Removing and Replacing Sockets in Appendix C for instructions on replacing the protective sockets.

#### INSTALLING SOFTWARE

The R3000 support software sets up the DAS 9200 to acquire, disassemble, and display data from an R3000 system. To install the support software, the support application files on the 5 1/4-inch floppy disk must be copied to the DAS 9200 hard disk.

To install the software, follow these steps:

- 1. Power on the DAS 9200 and press the Select Menu key.

- 2. Select the Disk Services menu in the Utilities column.

- 3. Press F6: MOVE TO UTILITY.

- 4. Select Install Applications in the Operation field.

- 5. Press F8: EXECUTE OPERATION and follow the on-screen prompts.

If there is inadequate disk free space available on the hard disk, you must use the Remove Application or Delete File function of the Disk Services menu to free up enough disk space to install the software. The approximate space required to install the software is listed on the label of the floppy disk.

You cannot execute the disassembler from the floppy disk.

After the DAS 9200 successfully copies the application files from the floppy disk to the hard disk, the message **Application** installation complete with no errors appears on your screen. Remove the floppy disk and store it in a safe place in case you need to reinstall the software.

If you would like to see an example of R3000 bus activity with mnemonic disassembly, read the next discussion and procedure.

### Viewing the Refmem Files

A reference memory file (called R3000\_Demo) is provided for you to familiarize yourself with the way the disassembler displays R3000 instruction mnemonics. A second reference memory (called R3K\_Timg\_96) is provide for you to view the R3000 timing bus forms as discussed in Section 5. You can select either reference memory file to see how R3000 data is displayed without making any DAS 9200 connections to your system under test.

Both reference memory files are automatically installed when the disassembler software is installed on the hard disk. All the figures in Section 4 showing acquired data are from the R3000\_Demo file. The data you acquire from your R3000 system will be different.

To view the reference memory files, use the following procedure:

- 1. Press the Select Menu key to return to the Menu Selection overlay.

- 2. Move the cursor to the Refmem column and select the reference memory you want to view.

- 3. Move the cursor to the Display column and select Disasm if you want to view the R3000\_Demo file, or select timing if you want to view the R3K\_Timg\_96 timing refmem file.

- 4. Press F5: MOVE TO DISPLAY or the Return key to view the reference memory that you selected.

You can change the format of disassembled data from the Disassembly Format Definition overlay, which you access through the Disassembly menu. Hardware disassembly is the default format in the Disassembly menu. Examples of the disassembly formats are found under *Displaying Disassembled Data* in Section 4.

If there is not enough free space left on the hard disk, you can delete the R3000\_Demo refmem file, the R3000\_Addr symbol table, or the R3K\_Timg\_96 timing refmem file from the hard disk. These files are presented strictly for viewing and are not necessary to the operation of the disassembler.

## **Setting Up Disassembler Software**

The microprocessor support package supplies the disassembler software and setup files for the data acquisition module to use to acquire and display instruction mnemonics. Setup files are supplied for the Channel, Clock, and Trigger menus. A Symbol file for the Control group is supplied for displaying data and to use in the Trigger menu. In addition, a Trigger library file, (called R3000\_Lib) is provided to help you trigger on selected disassembled data. A format file is also provided for the Timing menu when performing hardware analysis (described in Section 5).

Before selecting and setting up the disassembler, read the descriptions of *R3000 System Requirements and Restrictions* in Section 1.

The 92DM74 software is designed to work with a single 92A96 Module. If your DAS 9200 configuration contains more than one 92A96 card in adjacent slots, you must reconfigure your 92A96 Module to operate as a single-card module. If you do not have the correct 92A96 Module configuration, the DAS 9200 will display the following message when you attempt to select the R3000 Support in the Configuration menu: ERROR: Incompatible channel width detected. Restored the previous setup. Refer to the DAS 9200 System User's Manual for information on using the System Configuration menu to configure your 92A96 Module.

You can invoke the disassembler and its associated setup files from the module's Configuration menu. Move the cursor to the Software Support field and select R3000 Support. The microprocessor support software automatically sets up the various module menus as soon as you select R3000 Support.

A detailed description of the disassembler setup follows. You can select the Channel, Symbol Editor, Clock, and Trigger menus to view default setups and files.

If you have more than one data acquisition module in the DAS 9200, you should apply slot number labels to various parts of the DAS 9200 equipment before setting up the disassembler. Refer to the *Labels* discussion in this section for a description of where to apply the slot number labels. These slot numbers will help you identify which data acquisition module is connected to the probe adapter in a multimodule system.

### **Channel Groups and Assignments**

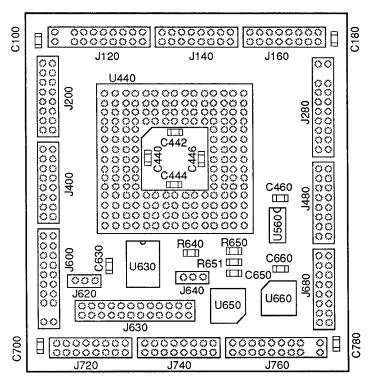

The disassembler relies on the presence of the signals and channel groups defined by the support software for the Address, Data, Jumper, and Control channel groups. The channel assignment table is located in Appendix C.

### What You Can Change During Setup

You can change part of the module setup without affecting disassembly. You can change the trigger program in the Trigger menu and the display radix for any channel group in the Channel menu or Disassembly Format definition overlay.

You cannot change the channel grouping or name for the Address, Data, Jumper, or Control groups, the threshold voltage, or polarity and expect the disassembler to function properly.

However, you can change the R3000 signal connections, the channel grouping, and group name for the channels not required for mnemonic disassembly. Refer to the discussions on signals in Appendix B for a list of these signal connections. Refer also to the discussion on *Alternate Connections* in this section for a description of how to make connections to other signals in your R3000 system.

## Symbol Tables

You can use symbol tables to display channel group information symbolically in the State and Disassembly menus and to control triggering. There is a symbol table file (named R3000\_Ctrl) supplied by the disassembler software that replaces specific Control channel group values. Refer to *Triggering* and *Displaying the Address Group Symbolically* in Section 4 for more information on displaying symbolic values.

A second symbol table (called R3000\_Addr) is provided with the 92DM74 software for use with the R3000\_Demo reference memory file to demonstrate the use of a symbol table with the address group. You can delete this symbol table if you need more disk space on the DAS 9200; it is provided for demonstration purposes only.

Table 3-1 shows the name, bit pattern, and meaning for the symbols in the file R3000\_Ctrl, the Control group symbol table.

Table 3-1

Control Group Symbol Table (R3000\_Ctrl)

|                                   |     |     |            |           |      | (  | Con | trol G    | rou | p Va                | alue  |              |     |              |              |                |                                                        |

|-----------------------------------|-----|-----|------------|-----------|------|----|-----|-----------|-----|---------------------|-------|--------------|-----|--------------|--------------|----------------|--------------------------------------------------------|

| Symbol                            | Run | Pha | ase<br>Exc | ·<br>XEn• | IRd* | Wr | DRd | •<br>DWr• | Mer | πRd*<br><b>M</b> em | RdBus | y<br>VrBusy* | Res | et*<br>AccTy | /p2<br>AccTy | /p1<br>AccTyp0 | Meaning                                                |

| INSTR                             | 0   | 1   | χ          | 0         | Х    | χ  | χ   | Х         | Χ   | χ                   | χ     | Х            | 1   | χ            | χ            | Χ              | Instruction fetched                                    |

| STREAMING<br>SWAPPED_<br>INST_RUN | 0   | 1   | X          | X         | χ    | X  | 0   | X         | X   | X                   | X     | X            | 1   | Χ            | X            | X              | during streaming<br>Swapped Instruction<br>run cycle   |

| INST_RUN/<br>EXC1W                | 0   | 1   | 0          | Χ         | χ    | X  | Χ   | Χ         | X   | X                   | χ     | Χ            | 1   | Χ            | Χ            | Χ              | Exception indication Exc1W†                            |

| INST_RUN                          | 0   | 1   | X          | X         | Χ    | Χ  | Χ   | Χ         | X   | Χ                   | χ     | X            | 1   | X            | χ            | X              | Instruction Phase of a run cycle                       |

| INST_STALL/<br>RETRY              | 1   | 1   | Χ          | 0         | X    | X  | Χ   | X         | X   | Χ                   | 1     | X            | 1   | Χ            | Χ            | X              | Instruction Phase of a Stall, read with Retry          |

| INST_FIXUP/<br>READ               | 1   | 1   | 0          | 0         | X    | X  | Χ   | X         | X   | X                   | X     | X            | 1   | X            | X            | X              | Instruction Read from main memory during a Fixup cycle |

| INST_REFILL                       | 1   | 1   | 1          | 0         | Χ    | X  | Χ   | X         | X   | Χ                   | Χ     | X            | 1   | X            | Χ            | X              | Instruction Phase of a<br>Refill cycle                 |

| INST_FIXUP                        | 1   | 1   | 0          | Χ         | Χ    | X  | Χ   | X         | X   | X                   | Χ     | X            | 1   | X            | χ            | X              | Instruction Phase of a Fixup cycle‡                    |

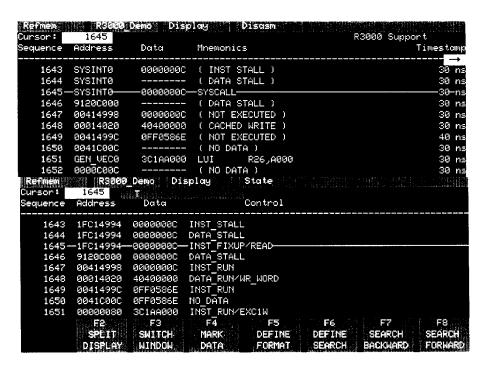

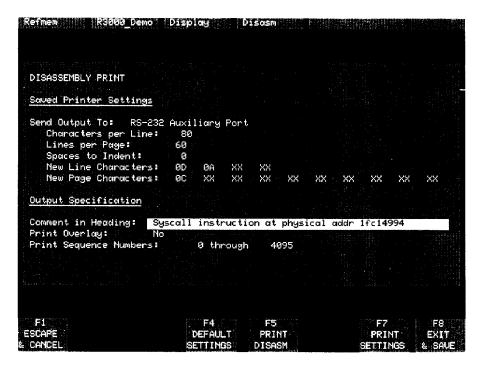

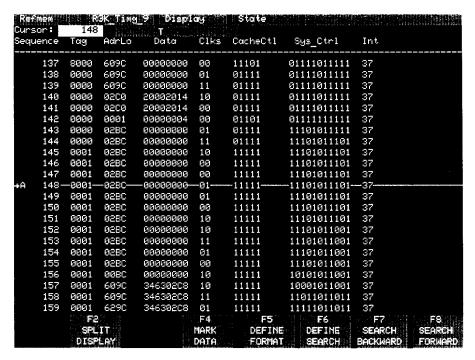

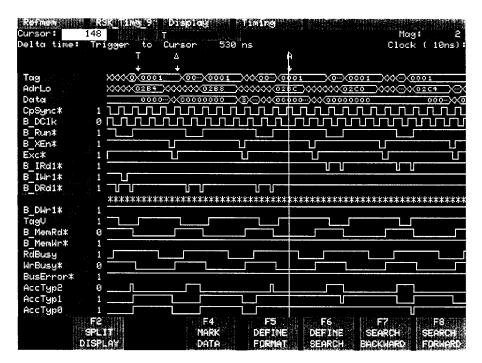

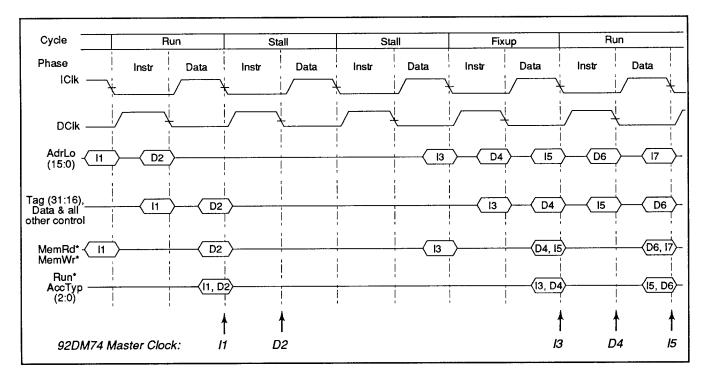

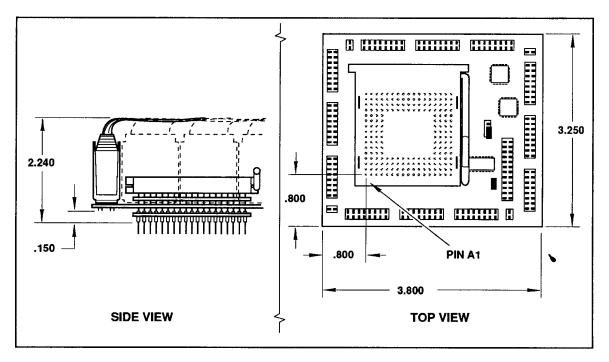

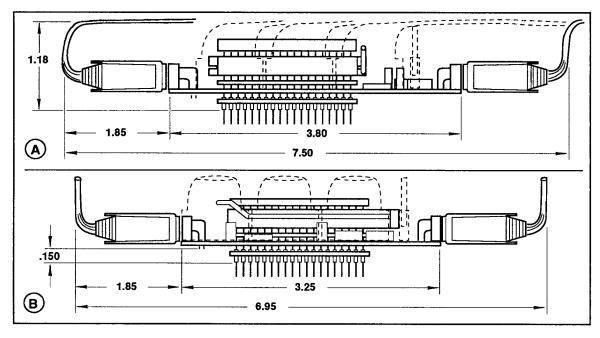

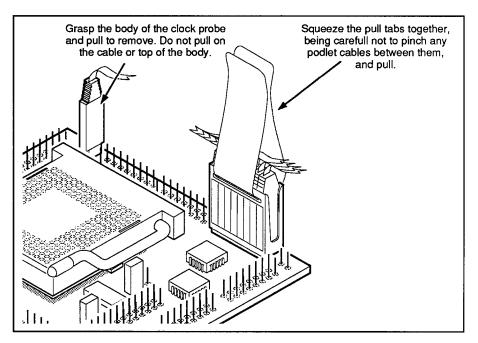

| INST_STALL                        | 1   | 1   | 1          | X         | X    | Χ  | X   | X         | X   | X                   | X     | Χ            | 1   | Χ            | X            | Χ              | Instruction Phase of a Stall cycle‡                    |