# Model 7022 Matrix-Digital I/O Card Instruction Manual

A GREATER MEASURE OF CONFIDENCE

# WARRANTY

Keithley Instruments, Inc. warrants this product to be free from defects in material and workmanship for a period of 1 year from date of shipment.

Keithley Instruments, Inc. warrants the following items for 90 days from the date of shipment: probes, cables, rechargeable batteries, diskettes, and documentation.

During the warranty period, we will, at our option, either repair or replace any product that proves to be defective.

To exercise this warranty, write or call your local Keithley representative, or contact Keithley headquarters in Cleveland, Ohio. You will be given prompt assistance and return instructions. Send the product, transportation prepaid, to the indicated service facility. Repairs will be made and the product returned, transportation prepaid. Repaired or replaced products are warranted for the balance of the original warranty period, or at least 90 days.

# LIMITATION OF WARRANTY

This warranty does not apply to defects resulting from product modification without Keithley's express written consent, or misuse of any product or part. This warranty also does not apply to fuses, software, non-rechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to follow instructions.

THIS WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR USE. THE REMEDIES PRO-VIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES.

NEITHER KEITHLEY INSTRUMENTS, INC. NOR ANY OF ITS EMPLOYEES SHALL BE LIABLE FOR ANY DIRECT. INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OF ITS INSTRUMENTS AND SOFTWARE EVEN IF KEITHLEY INSTRUMENTS, INC., HAS BEEN ADVISED IN ADVANCE OF THE POSSIBILITY OF SUCH DAMAGES. SUCH EXCLUDED DAMAGES SHALL INCLUDE, BUT ARE NOT LIM-ITED TO: COSTS OF REMOVAL AND INSTALLATION, LOSSES SUSTAINED AS THE RESULT OF INJURY TO ANY PERSON, OR DAMAGE TO PROPERTY.

Keithley Instruments, Inc. • 28775 Aurora Road • Cleveland, OH 44139 • 440-248-0400 • Fax: 440-248-6168 • http://www.keithley.com

| BELGIUM:       | Keithley Instruments B.V.   | Bergensesteenweg 709 • B-1600 Sint-Pieters-Leeuw • 02/363 00 40 • Fax: 02/363 00 64                                   |

|----------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| CHINA:         | Keithley Instruments China  | Yuan Chen Xin Building, Room 705 • 12 Yumin Road, Dewai, Madian • Beijing 100029 • 8610-62022886 • Fax: 8610-62022892 |

| FRANCE:        | Keithley Instruments Sarl   | 3, allée des Garays • 91127 Palaiseau Cedex • 01-64 53 20 20 • Fax: 01-60 11 77 26                                    |

| GERMANY:       | Keithley Instruments GmbH   | Landsberger Strasse 65 • 82110 Germering • 089/84 93 07-40 • Fax: 089/84 93 07-34                                     |

| GREAT BRITAIN: | Keithley Instruments Ltd    | The Minster • 58 Portman Road • Reading, Berkshire RG30 1EA • 0118-9 57 56 66 • Fax: 0118-9 59 64 69                  |

| INDIA:         | Keithley Instruments GmbH   | Flat 2B, WILOCRISSA • 14, Rest House Crescent • Bangalore 560 001 • 91-80-509-1320/21 • Fax: 91-80-509-1322           |

| ITALY:         | Keithley Instruments s.r.l. | Viale S. Gimignano, 38 • 20146 Milano • 02-48 39 16 01 • Fax: 02-48 30 22 74                                          |

| NETHERLANDS:   | Keithley Instruments B.V.   | Postbus 559 • 4200 AN Gorinchem • 0183-635333 • Fax: 0183-630821                                                      |

| SWITZERLAND:   | Keithley Instruments SA     | Kriesbachstrasse 4 • 8600 Dübendorf • 01-821 94 44 • Fax: 01-820 30 81                                                |

| TAIWAN:        | Keithley Instruments Taiwan | 1 Fl. 85 Po Ai Street • Hsinchu, Taiwan, R.O.C. • 886-3572-9077 • Fax: 886-3572-903 9/00                              |

# Model 7022 Matrix-Digital I/O Card Instruction Manual

©1997, Keithley Instruments, Inc. All rights reserved. Cleveland, Ohio, U.S.A. Second Printing, March 2001 Document Number: 7022-901-01 Rev. B

# **Manual Print History**

The print history shown below lists the printing dates of all Revisions and Addenda created for this manual. The Revision Level letter increases alphabetically as the manual undergoes subsequent updates. Addenda, which are released between Revisions, contain important change information that the user should incorporate immediately into the manual. Addenda are numbered sequentially. When a new Revision is created, all Addenda associated with the previous Revision of the manual are incorporated into the new Revision of the manual. Each new Revision includes a revised copy of this print history page.

| Revision A (Document Number 7022-901-01)  | April 1997  |

|-------------------------------------------|-------------|

| Addendum A (Document Number 7022-901-02)  | August 1998 |

| Revision B (Document Number 7022-901-01). |             |

# **Safety Precautions**

The following safety precautions should be observed before using this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read the operating information carefully before using the product.

The types of product users are:

**Responsible body** is the individual or group responsible for the use and maintenance of equipment, for ensuring that the equipment is operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

**Operators** use the product for its intended function. They must be trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with hazardous live circuits.

**Maintenance personnel** perform routine procedures on the product to keep it operating, for example, setting the line voltage or replacing consumable materials. Maintenance procedures are described in the manual. The procedures explicitly state if the operator may perform them. Otherwise, they should be performed only by service personnel.

Service personnel are trained to work on live circuits, and perform safe installations and repairs of products. Only properly trained service personnel may perform installation and service procedures.

Keithley products are designed for use with electrical signals that are rated Installation Category I and Installation Category II, as described in the International Electrotechnical Commission (IEC) Standard IEC 60664. Most measurement, control, and data I/O signals are Installation Category I and must not be directly connected to mains voltage or to voltage sources with high transient over-voltages. Installation Category II connections require protection for high transient over-voltages often associated with local AC mains connections. The user should assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise marked or described in the Manual. Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any unknown circuit before measuring.

Users of this product must be protected from electric shock at all times. The responsible body must ensure that users are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential human contact. Product users in these circumstances must be trained to protect themselves from the risk of electric shock. If the circuit is capable of operating at or above 1000 volts, **no conductive part of the circuit may be exposed**.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance limited sources. NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle. Inspect the connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input power disconnect device must be provided, in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured. The instrument and accessories must be used in accordance with its specifications and operating instructions or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a lid interlock.

If a  $(\pm)$  screw is present, connect it to safety earth ground using the wire recommended in the user documentation.

The  $\cancel{N}$  symbol on an instrument indicates that the user should refer to the operating instructions located in the manual.

The  $\cancel{1}$  symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of normal and common mode voltages. Use standard safety precautions to avoid personal contact with these voltages.

The **WARNING** heading in a manual explains dangers that might result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The **CAUTION** heading in a manual explains hazards that could damage the instrument. Such damage may invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits, including the power transformer, test leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses, with applicable national safety approvals, may be used if the rating and type are the same. Other components that are not safety related may be purchased from other suppliers as long as they are equivalent to the original component. (Note that selected parts should be purchased only through Keithley Instruments to maintain accuracy and functionality of the product.) If you are unsure about the applicability of a replacement component, call a Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water based cleaner. Clean the exterior of the instrument only. Do not apply cleaner directly to the instrument or allow liquids to enter or spill on the instrument. Products that consist of a circuit board with no case or chassis (e.g., data acquisition board for installation into a computer) should never require cleaning if handled according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the factory for proper cleaning/servicing.

# 7022 Matrix-Digital I/O Card

#### ANALOG MATRIX SPECIFICATIONS

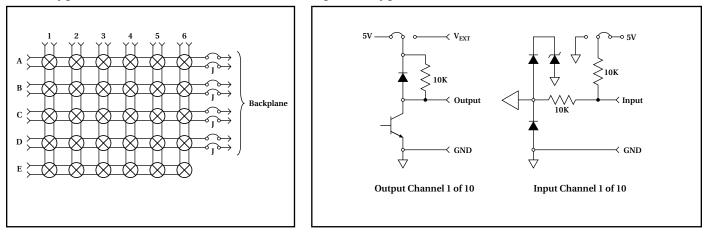

MATRIX CONFIGURATION: 5 rows×6 columns. Jumpers can be removed to isolate any row from the backplane. Rows A–D are connected to the backplane.

#### CONTACT CONFIGURATION: 2-pole Form A (HI, LO).

MAXIMUM SIGNAL: 110V DC, 110V rms, 155V peak between any two inputs or chassis, 1A switched, 30VA (resistive loads).

CONTACT LIFE:

Cold Switching: 108 closures.

Maximum Signal Levels: 10<sup>5</sup> closures.

CHANNEL RESISTANCE (per conductor): <1.25Ω.

#### CONTACT POTENTIAL:

<3µV per channel contact pair

<9µV per single contact

OFFSET CURRENT: <100pA.

ACTUATION TIME: <3ms.

Matrix Configuration

**Common Mode:** >10<sup>9</sup>Ω, <200pF.

$\textbf{CROSSTALK}^{1} \textbf{ (1MHz, 50} \Omega \textbf{ Load): } < -40 dB.$

INSERTION LOSS<sup>1</sup> (50 $\Omega$  Source, 50 $\Omega$  Load): <0.25dB below 1MHz, <3dB below 10MHz.

RELAY DRIVE CURRENT (per relay): 16mA.

<sup>1</sup> Specifications apply with no more than one crosspoint closed.

#### **DIGITAL I/O SPECIFICATIONS**

DIGITAL I/O CAPABILITY: 10 independent inputs. 10 independent outputs.

#### OUTPUT:

- Configuration: 10 open-collector drivers with factory installed  $10k\Omega$  pull-up resistors. Each driver has an internal flyback diode.

- **Pull-Up Voltage:** 5V internally supplied, external connection provided for user supplied voltage up to 42V max. Outputs short circuit protected up to 25V.

#### Maximum Sink Current: Per Channel: 250mA. Per Card: 1A.

**Logic:** Hardware user configurable for negative or positive true logic levels.

#### **INPUT:**

Configuration: 10 inputs with internal  $10k\Omega$  pull-up resistors provided. Input resistors can be set for pull-up or pull-down configuration.

MAXIMUM VOLTAGE LEVEL: 42V peak.

#### LOGIC: Positive true.

#### GENERAL

CONNECTOR TYPE: 96-pin male DIN connector (7011-KIT-R mating connector included).

ENVIRONMENT:

**Operating:** 0° to 50°C, up to 35°C <80% RH.

**Storage:** –25° to 65°C.

**EMC:** Conforms to European Union Directive 89/336/EEC. **SAFETY:** Conforms to European Union Directive 73/23/EEC (meets

EN61010-1/IEC 1010).

#### Digital I/O Configuration

# **Table of Contents**

# 1 General Information

| Introduction             | 1-1 |

|--------------------------|-----|

| Features                 | 1-1 |

| Warranty information     | 1-2 |

| Manual addenda           | 1-2 |

| Safety symbols and terms | 1-2 |

| Specifications           | 1-2 |

| Unpacking and inspection | 1-2 |

| Inspection for damage    | 1-2 |

| Shipping contents        |     |

| Instruction manual       | 1-2 |

| Repacking for shipment   | 1-3 |

| Optional accessories     | 1-3 |

|                          |     |

# 2 Matrix Configuration

| Introduction                       | 2-1 |

|------------------------------------|-----|

| Basic matrix configuration (5 × 6) | 2-1 |

| Typical matrix switching schemes   | 2-2 |

| Single-ended switching             | 2-3 |

| Differential switching             |     |

| Sensing                            |     |

| SMU connections                    |     |

| Matrix expansion                   | 2-5 |

| Two-card switching systems         |     |

| Mainframe matrix expansion         |     |

| 1                                  |     |

# 3 Digital I/O Configuration

| Introduction                                | . 3-1 |

|---------------------------------------------|-------|

| Digital outputs                             | . 3-1 |

| Controlling pull-up devices                 |       |

| Controlling devices using pull-up resistors |       |

| Digital inputs                              |       |

| 0 1                                         |       |

# 4 Card Connections and Installation

| Introduction                                     |      |

|--------------------------------------------------|------|

| Handling precautions                             | 4-1  |

| Matrix connections                               | 4-2  |

| Backplane row jumpers                            | 4-2  |

| Jumper removal                                   | 4-2  |

| Jumper installation                              | 4-2  |

| Digital I/O connections                          | 4-2  |

| Voltage source jumper                            | 4-2  |

| Pull-up resistors                                | 4-3  |

| Configuring digital I/O output logic             | 4-4  |

| Configuring digital I/O input pull-up resistance | 4-4  |

| Multi-pin (mass termination) connector card      | 4-5  |

| Typical matrix connection schemes                | 4-11 |

| Single-card system                               | 4-11 |

| Two-card system                                  | 4-12 |

| Two-mainframe system                             | 4-14 |

| Typical digital I/O connection schemes           | 4-16 |

| Output connection schemes                        | 4-16 |

| Input connection scheme                          |      |

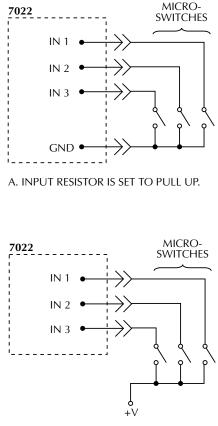

| Model 7022 installation and removal              | 4-18 |

| Card installation                                | 4-18 |

| Card removal                                     | 4-18 |

| Models 7022-D and 7022-DT                        | 4-19 |

| Internal connections                             | 4-19 |

| Input/output connections                         | 4-19 |

|                                                  |      |

# Operation

| Introduction                        | 5-1  |

|-------------------------------------|------|

| Power limits                        | 5-1  |

| Analog matrix maximum signal levels | 5-1  |

| Digital I/O maximum signal levels   | 5-1  |

| Mainframe control of the card       | 5-1  |

| Channel assignments                 | 5-2  |

| Closing and opening channels        | 5-4  |

| Scanning channels                   | 5-4  |

| Reading input channels              | 5-5  |

| IEEE-488 bus operation              | 5-5  |

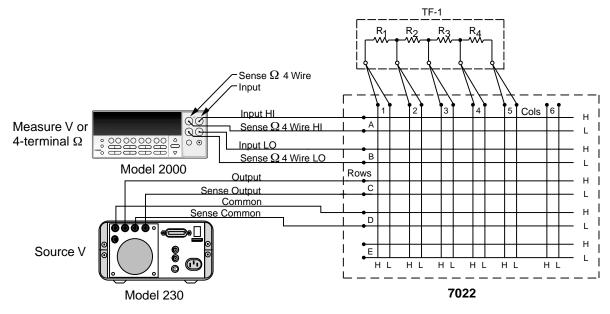

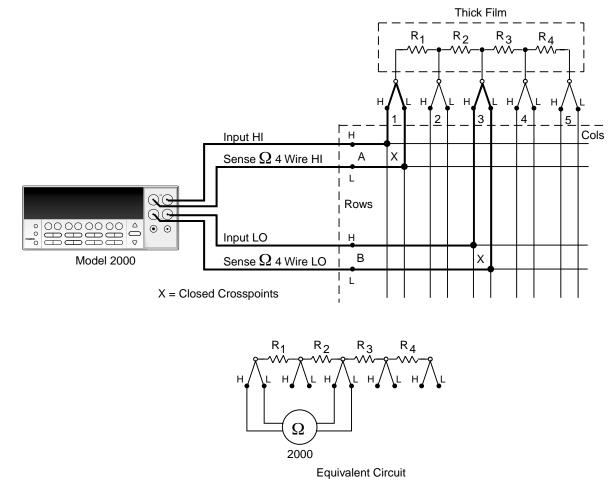

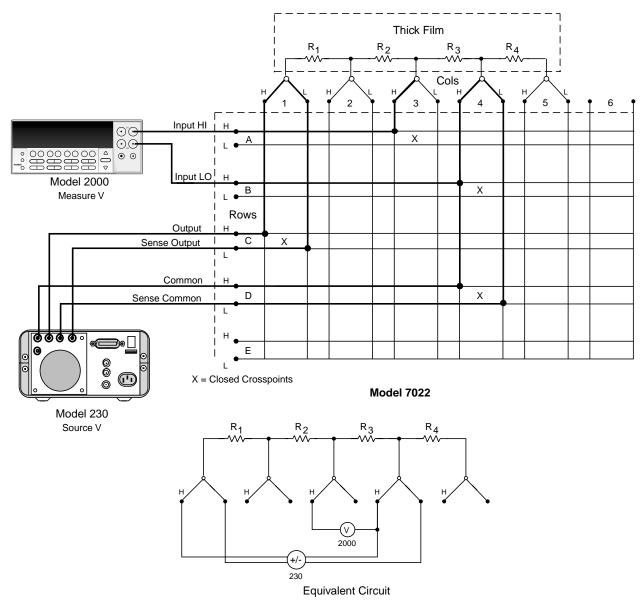

| Matrix switching examples           | 5-7  |

| Thick film resistor network testing |      |

| Transistor testing                  |      |

| Measurement considerations          | 5-12 |

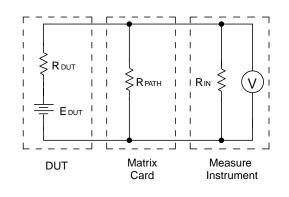

| Path isolation                      | 5-12 |

| Magnetic fields                     | 5-13 |

| Radio frequency interference        | 5-13 |

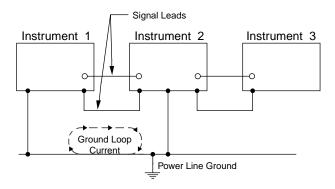

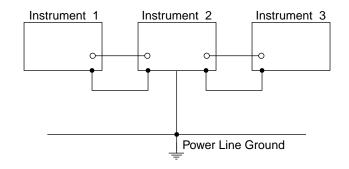

| Ground loops                        | 5-14 |

| Keeping connectors clean            |      |

| AC frequency response               | 5-14 |

#### Service Information 6

| Introduction                                 | 6-1  |

|----------------------------------------------|------|

| Handling and cleaning precautions            | 6-1  |

| Performance verification                     | 6-2  |

| Environmental conditions                     | 6-2  |

| Recommended equipment                        | 6-2  |

| Matrix connections                           | 6-2  |

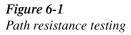

| Channel resistance tests                     | 6-3  |

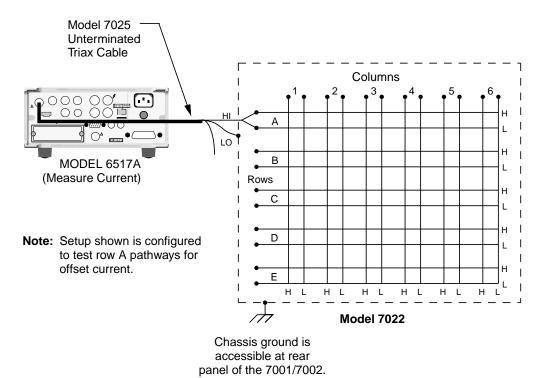

| Offset current tests                         | 6-4  |

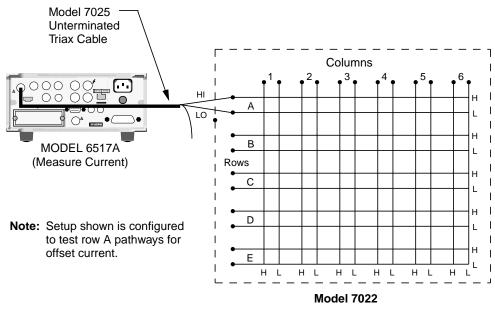

| Contact potential tests                      | 6-6  |

| Path isolation tests                         | 6-7  |

| Differential and common-mode isolation tests | 6-8  |

| Channel functionality test                   | 6-10 |

| Special handling of static-sensitive devices | 6-11 |

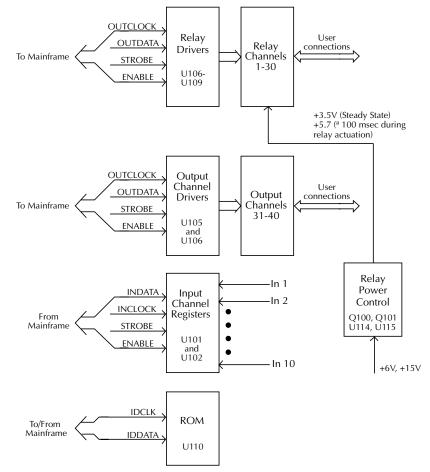

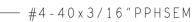

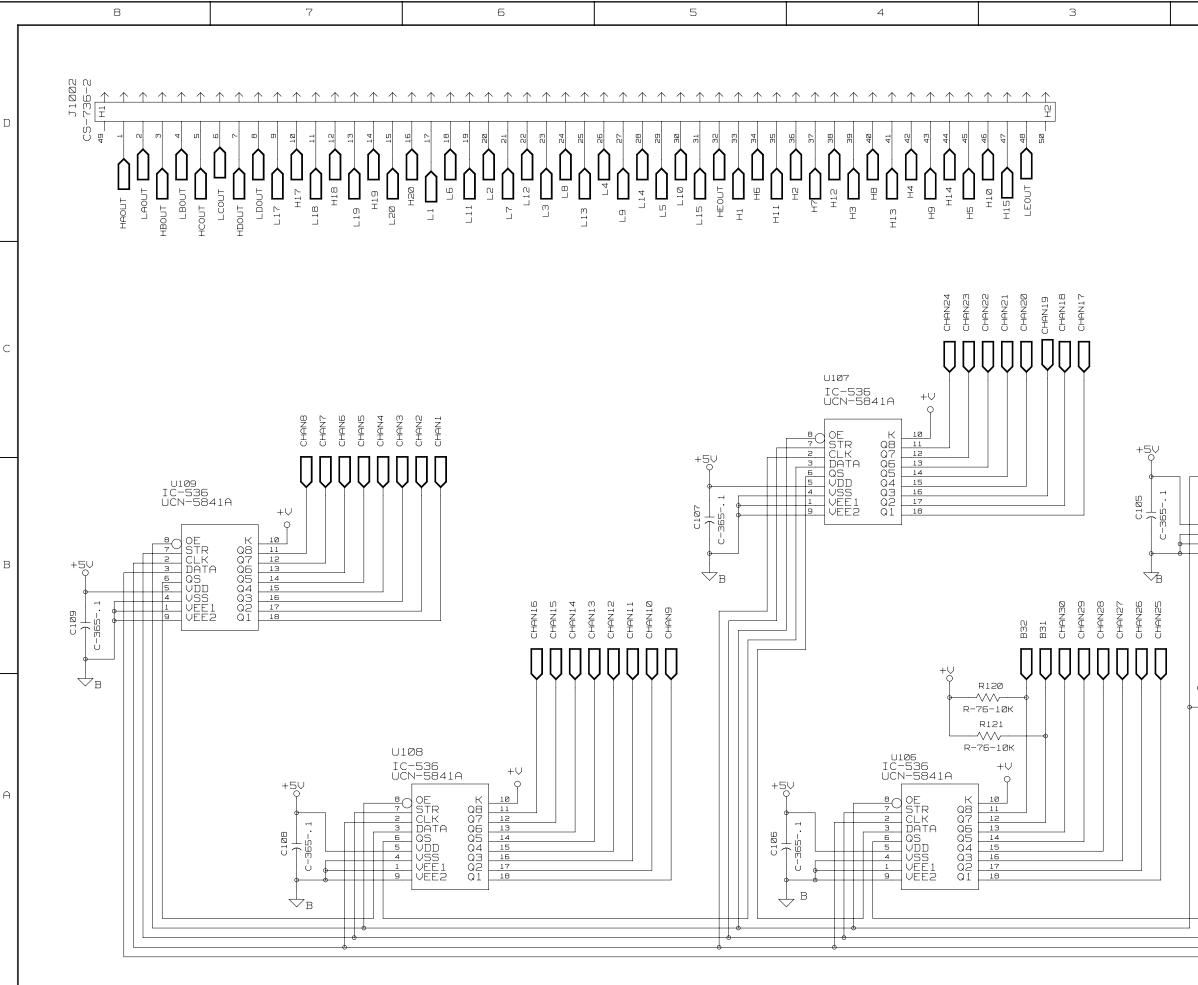

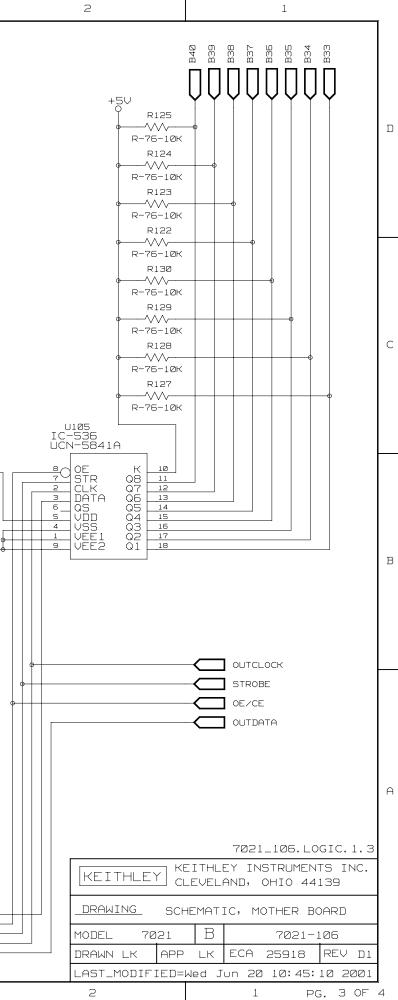

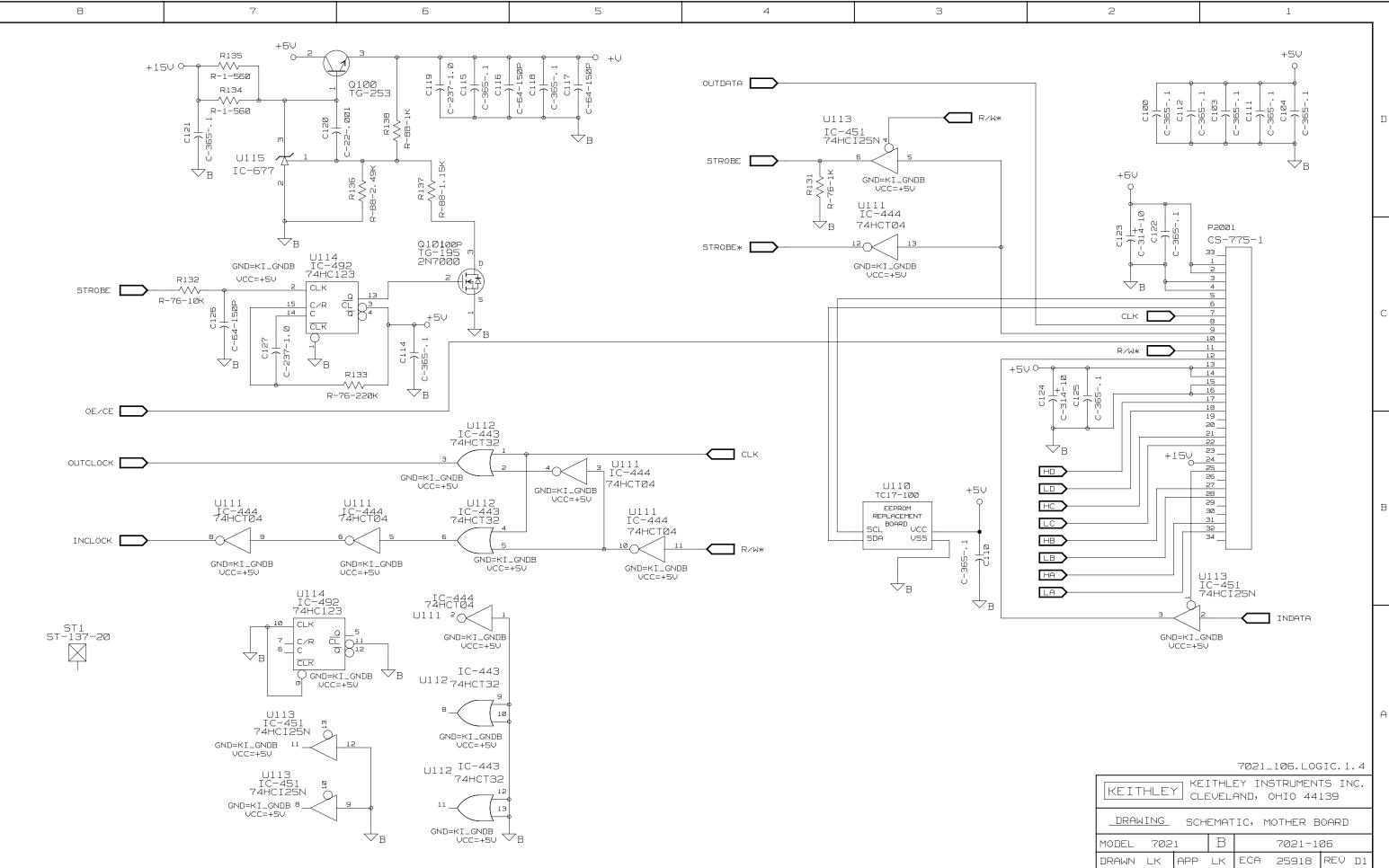

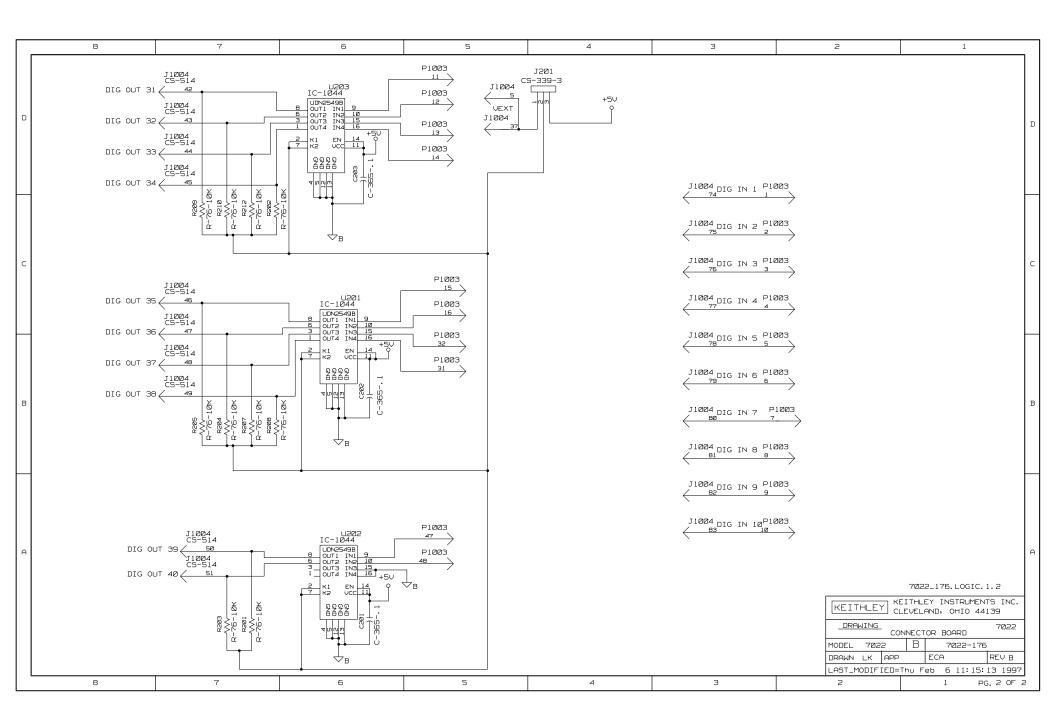

| Principles of operation                      | 6-11 |

| Block diagram                                | 6-11 |

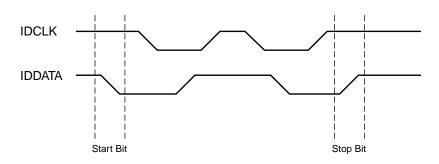

| ID data circuits                             | 6-12 |

| Matrix relay control                         | 6-13 |

| Matrix relay power control                   | 6-13 |

| Digital I/O output channel control           | 6-13 |

| Digital I/O input channel control            | 6-13 |

| Power-on safeguard                           | 6-13 |

| Troubleshooting                              | 6-14 |

| Troubleshooting equipment                    | 6-14 |

| Troubleshooting access                       |      |

| Troubleshooting procedure                    | 6-14 |

|                                              |      |

#### **Replaceable Parts** 7

| Introduction                             | 7-1 |

|------------------------------------------|-----|

| Parts lists                              | 7-1 |

| Ordering information                     | 7-1 |

| Factory service                          | 7-1 |

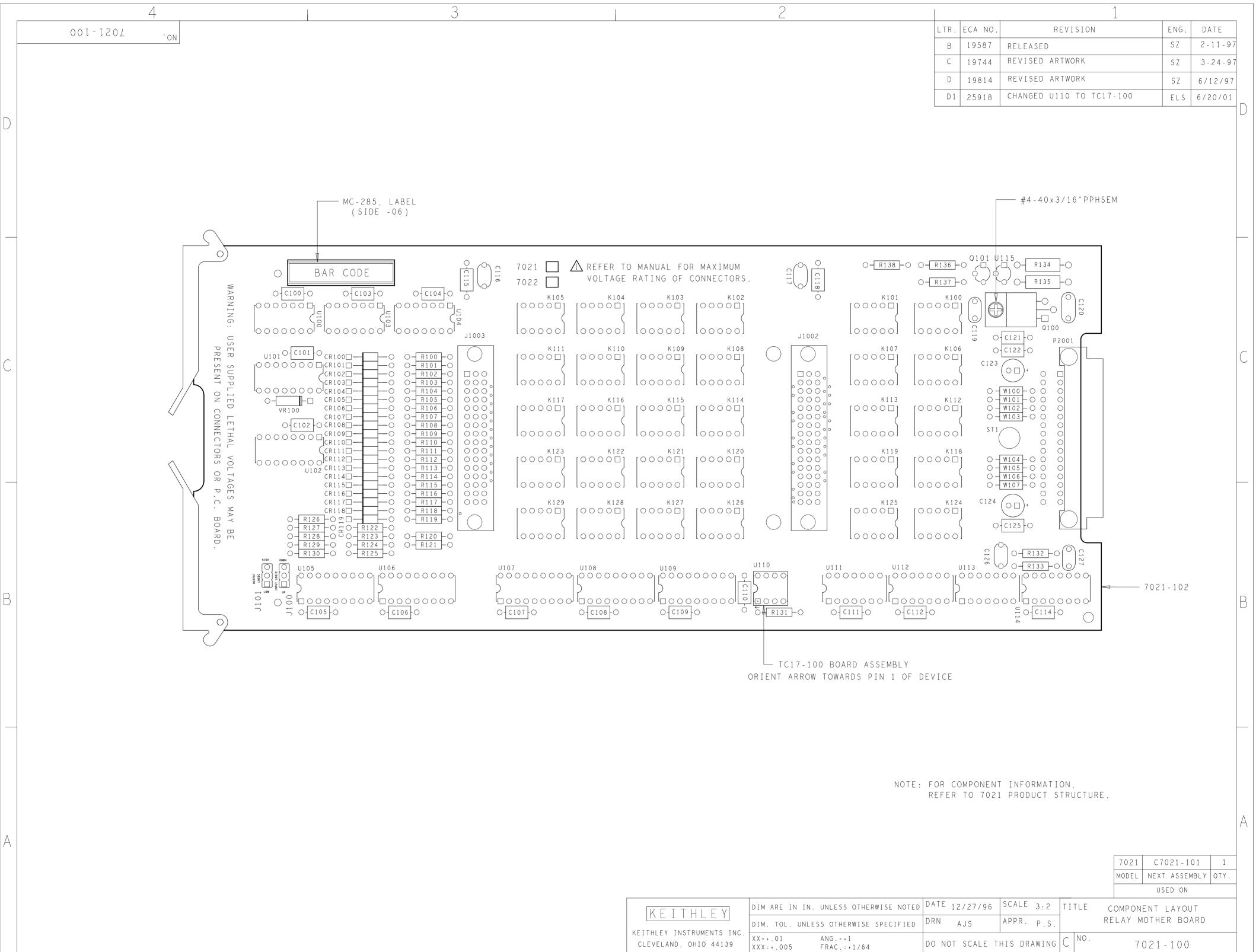

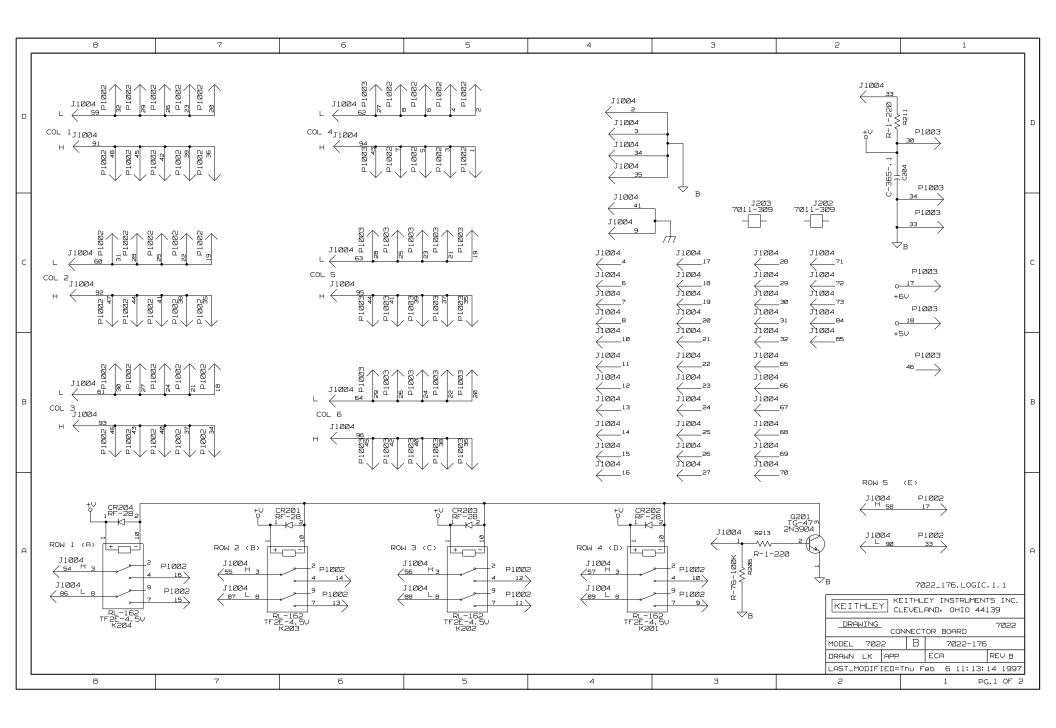

| Component layouts and schematic diagrams | 7-2 |

# Index

# **List of Illustrations**

# 2 Matrix Configuration

| Figure 2-1  | Model 7022 simplified schematic     | 2-1 |

|-------------|-------------------------------------|-----|

| Figure 2-2  | Model 7001/7002 analog backplane    |     |

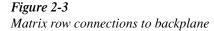

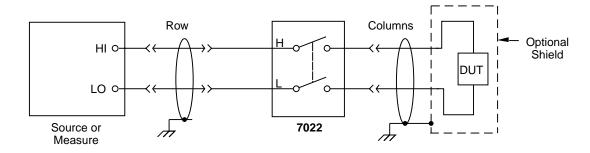

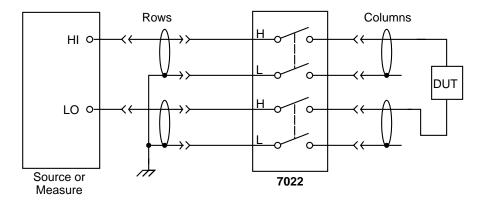

| Figure 2-3  | Matrix row connections to backplane | 2-2 |

| Figure 2-4  | Single-ended switching example      | 2-3 |

| Figure 2-5  | Differential switching example      | 2-3 |

| Figure 2-6  | Sensing example                     | 2-4 |

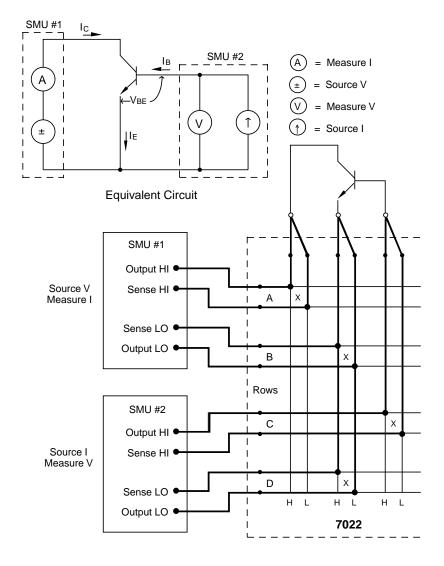

| Figure 2-7  | SMU connections                     | 2-4 |

| Figure 2-8  | Two separate 5 × 6 matrices         | 2-5 |

| Figure 2-9  | Narrow matrix example (4 × 12)      | 2-6 |

| Figure 2-10 | Wide matrix example $(10 \times 6)$ | 2-7 |

| Figure 2-11 | Mixed card type example             | 2-8 |

| Figure 2-12 | Partial matrix expansion (10 × 12)  | 2-9 |

# 3 Digital I/O Configuration

| Figure 3-1 | Output configuration for pull-up devices      | 3-1 | 1 |

|------------|-----------------------------------------------|-----|---|

| -          | Output configuration using pull-up resistance |     |   |

| Figure 3-3 | Input configuration                           | 3-2 | 2 |

# 4

# Card Connections and Installation

| Figure 4-1  | Backplane row jumpers                            | 4-2 |

|-------------|--------------------------------------------------|-----|

| Figure 4-2  | Voltage source jumper for output channels        | 4-3 |

| Figure 4-3  | Component locations - connector board            | 4-3 |

| Figure 4-4  | Voltage source jumper installation               | 4-3 |

| Figure 4-5  | Digital I/O output logic location                | 4-4 |

| Figure 4-6  | Digital I/O output logic selection               | 4-4 |

| Figure 4-7  | Digital I/O input pull-up resistance selection   | 4-5 |

| Figure 4-8  | Multi-pin connector card terminal identification |     |

| Figure 4-9  | Typical round cable connection techniques        | 4-9 |

| Figure 4-10 | Model 7011-MTR connector pinout                  | -10 |

| Figure 4-11 | Model 7011-KIT-R (with cable) assembly           | -10 |

| Figure 4-12 | Single-card system example                       |     |

| Figure 4-13 | Two-card system example                          | -13 |

| Figure 4-14 | Two-mainframe system example 4                   | -15 |

| Figure 4-15 | Digital output, solenoid control 4               |     |

| Figure 4-16 | Digital output, motor control                    | -16 |

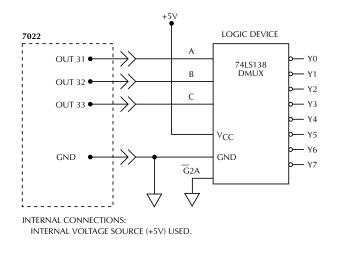

| Figure 4-17 | Digital output, logic device control 4           | -17 |

|             |                                                  |     |

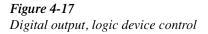

| Figure 4-18 | Digital input, monitoring micro-switches   | 4-17 |

|-------------|--------------------------------------------|------|

| Figure 4-19 | Model 7022 card installation in Model 7001 | 4-18 |

| Figure 4-20 | Mating the PC-boards                       | 4-19 |

| Figure 4-21 | Mating connector (solder-side view)        | 4-20 |

# 5 Operation

| Figure 5-1  | Model 7001 channel status display                           |  |

|-------------|-------------------------------------------------------------|--|

| Figure 5-2  | Model 7002 channel status display (slot 1)                  |  |

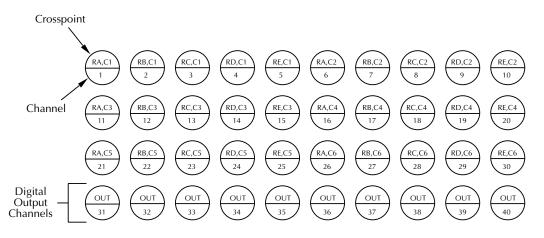

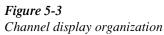

| Figure 5-3  | Channel display organization                                |  |

| Figure 5-4  | Model 7022 programming channel assignments                  |  |

| Figure 5-5  | Thick film resistor network testing                         |  |

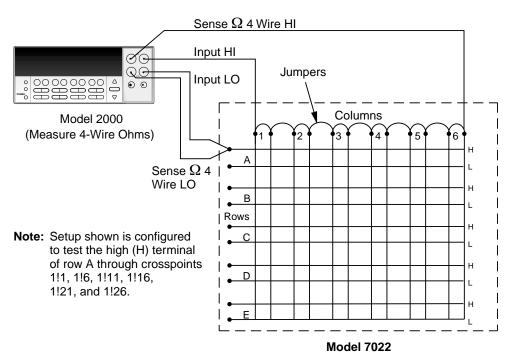

| Figure 5-6  | Four-terminal ohms measurements                             |  |

| Figure 5-7  | Voltage divider checks                                      |  |

| Figure 5-8  | Transistor testing                                          |  |

| Figure 5-9  | DC parameter checks                                         |  |

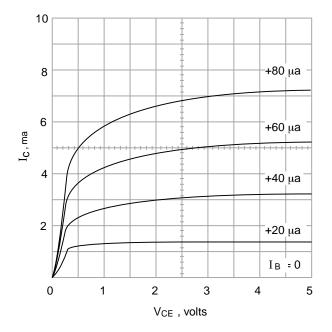

| Figure 5-10 | Common-emitter characteristics of an NPN silicon transistor |  |

| Figure 5-11 | Path isolation resistance                                   |  |

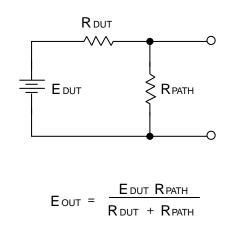

| Figure 5-12 | Voltage attenuation by path isolation resistance            |  |

| Figure 5-13 | Power line ground loops                                     |  |

| Figure 5-14 | Eliminating ground loops                                    |  |

# 6 Service Information

| Path resistance testing             | 6-3                                                                                                                                                                                                                                                                                                         |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common-mode offset current testing  | 6-4                                                                                                                                                                                                                                                                                                         |

| Differential offset current testing | 6-5                                                                                                                                                                                                                                                                                                         |

| Contact potential testing           | 6-6                                                                                                                                                                                                                                                                                                         |

| Path isolation testing (guarded)    | 6-7                                                                                                                                                                                                                                                                                                         |

| Differential isolation testing      |                                                                                                                                                                                                                                                                                                             |

| Common-mode isolation testing       | 6-10                                                                                                                                                                                                                                                                                                        |

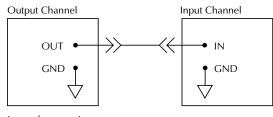

| Testing an input or output channel  | 6-10                                                                                                                                                                                                                                                                                                        |

| Model 7022 block diagram            | 6-11                                                                                                                                                                                                                                                                                                        |

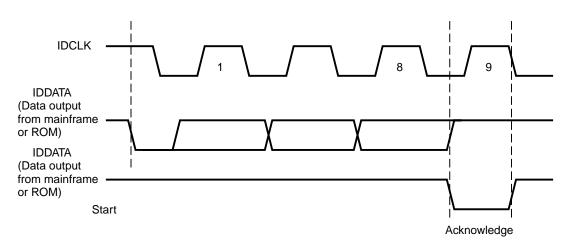

| Start and stop sequences            |                                                                                                                                                                                                                                                                                                             |

| Transmit and acknowledge sequence   | 6-12                                                                                                                                                                                                                                                                                                        |

|                                     | Common-mode offset current testing<br>Differential offset current testing<br>Contact potential testing<br>Path isolation testing (guarded)<br>Differential isolation testing<br>Common-mode isolation testing<br>Testing an input or output channel<br>Model 7022 block diagram<br>Start and stop sequences |

# **List of Tables**

# 4 Card Connections and Installation

| Table 4-1 | Mass termination accessories   | 4-: | 5 |

|-----------|--------------------------------|-----|---|

| Table 4-2 | Pin designation identification | 4-′ | 7 |

| Table 4-3 | Terminal identification        | -20 | 0 |

# 6 Service Information

| Table 6-1 | Verification equipment                         | . 6-2 |

|-----------|------------------------------------------------|-------|

| Table 6-2 | Path isolation tests                           | . 6-8 |

| Table 6-3 | Differential and common-mode isolation testing | . 6-9 |

| Table 6-4 | Recommended troubleshooting equipment.         | 6-14  |

| Table 6-5 | Troubleshooting procedure                      | 6-15  |

|           |                                                |       |

# 7 Replaceable Parts

| Table 7-1 | Relay card for Model 7022, parts list                        | 7-3 | 3 |

|-----------|--------------------------------------------------------------|-----|---|

| Table 7-2 | Mass terminated connector card for Model 7022, parts list    | 7-5 | 5 |

| Table 7-3 | Model 7011-KIT-R 96-pin female DIN connector kit, parts list | 7-7 | 1 |

# **1** General Information

# Introduction

This section contains general information about the Model 7022 matrix-digital I/O card.

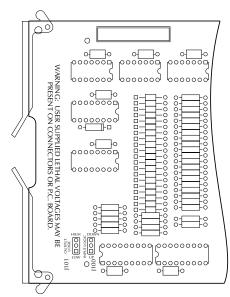

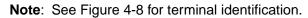

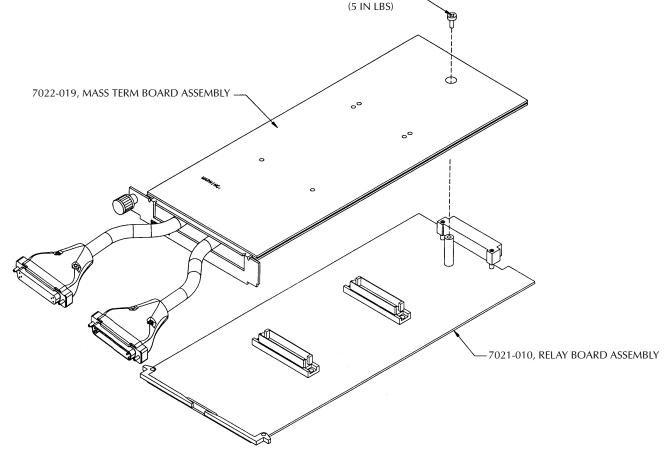

The Model 7022 consists of a multi-pin (mass termination) connector card and a relay card. External test circuit connections are made via the 96-pin male DIN connector on the connector card. Keithley offers a variety of optional accessories that can be used to make connections to the connector card. (See the available accessories at the end of this section.)

The rest of Section 1 is arranged in the following manner:

- Features

- Warranty information

- Manual addenda

- Safety symbols and terms

- Specifications

- Unpacking and inspection

- Repacking for shipment

- Optional accessories

# Features

The Model 7022 has a two-pole,  $5 \times 6$  (five rows by six columns) matrix. It also has ten independent inputs and outputs for digital I/O capabilities. Some of the key features include:

- Low contact potential and offset current for minimal effects on low-level signals.

- Backplane row jumpers. Cutting jumpers disconnects matrix rows from the Model 7001/7002 analog backplane.

- High density switching and control.

- High capacity digital output sink of 250mA.

- 1A pathway current carrying capacity.

- Model 7011-KIT-R connector kit that includes a 96-pin female DIN connector that will mate directly to the connector on the Model 7022 or to a standard 96-pin male DIN bulkhead connector (see Model 7011-MTR). This connector uses solder cups for connections to external circuitry and includes an adapter for a round cable and the housing.

# Warranty information

Warranty information is located on the inside front cover of this instruction manual. Should your Model 7022 require warranty service, contact the Keithley representative or authorized repair facility in your area for further information. When returning the card for repair, be sure to fill out and include the service form at the back of this manual in order to provide the repair facility with the necessary information.

# Manual addenda

Any improvements or changes concerning the card or manual will be explained in an addendum included with the card. Addenda are provided in a page replacement format. Replace the obsolete pages with the new pages.

# Safety symbols and terms

The following symbols and terms may be found on an instrument or used in this manual.

The  $\angle \mathbf{I}$  symbol on an instrument indicates that the user should refer to the operating instructions located in the instruction manual.

The symbol on an instrument shows that high voltage may be present on the terminal(s). Use standard safety precautions to avoid personal contact with these voltages.

The **WARNING** heading used in this manual explains dangers that might result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The **CAUTION** heading used in this manual explains hazards that could damage the card. Such damage may invalidate the warranty.

# **Specifications**

Model 7022 specifications are found at the front of this manual. These specifications are exclusive of the mainframe specifications.

# Unpacking and inspection

#### Inspection for damage

The Model 7022 is packaged in a resealable, anti-static bag to protect it from damage due to static discharge and from contamination that could degrade its performance. Before removing the card from the bag, observe the following precautions on handling.

#### Handling precautions

- 1. Always grasp the card by the side edges and shields. Do not touch the board surfaces or components.

- 2. When not installed in a Model 7001/7002 mainframe, keep the card in the anti-static bag and store it in the original packing carton.

After removing the card from its anti-static bag, inspect it for any obvious signs of physical damage. Report any such damage to the shipping agent immediately.

### Shipping contents

The following items are included with every Model 7022 order:

- Model 7022 Matrix-Digital I/O Card

- Model 7011-KIT-R 96-pin Female DIN Connector Kit

- Model 7022 Instruction Manual

- · Additional accessories as ordered

### Instruction manual

The Model 7022 Instruction Manual is three-hole drilled so it can be added to the three-ring binder of the Model 7001 or 7002 Instruction Manual. After removing the plastic wrapping, place the manual in the binder following the mainframe instruction manual. Note that a manual identification tab is included and should precede the Model 7022 Instruction Manual.

If an additional instruction manual is required, order the manual package, Keithley part number 7022-901-00. The manual package includes an instruction manual and any pertinent addenda.

# **Repacking for shipment**

Should it become necessary to return the Model 7022 for repair, carefully pack the unit in its original packing carton, or the equivalent, and include the following information:

- Advise as to the warranty status of the card.

- Write ATTENTION REPAIR DEPARTMENT on the shipping label.

- Fill out and include the service form located at the back of this manual.

# **Optional accessories**

The following accessories are available for use with the Model 7022:

**Model 7011-MTC-2** — This two-meter round cable assembly is terminated with a 96-pin female DIN connector on each end. It will mate directly to the connector on the Model 7022 and to a standard 96-pin male DIN bulkhead connector (see Model 7011-MTR).

**Model 7011-MTR** — This 96-pin male DIN bulkhead connector uses solder cups for connections to external circuitry. It will mate to the Model 7011-KIT-R connector and Model 7011-MTC-2 cable assembly.

General Information

# 2 Matrix Configuration

# Introduction

This section covers the basics for matrix switching and is arranged as follows:

- **Basic matrix configuration** (5 × 6) Covers the basic 5 × 6 matrix configuration. The significance of the backplane jumpers is also covered here.

- **Typical matrix switching schemes** Explains some of the basic ways a matrix can be used to source or measure. Covers single-ended switching, differential (floating) switching, and sensing.

- Matrix expansion Discusses the various matrix configurations possible using multiple cards.

# **Basic matrix configuration (5 × 6)**

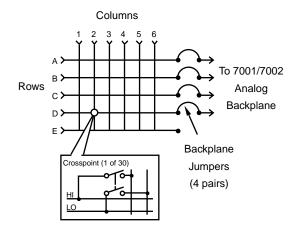

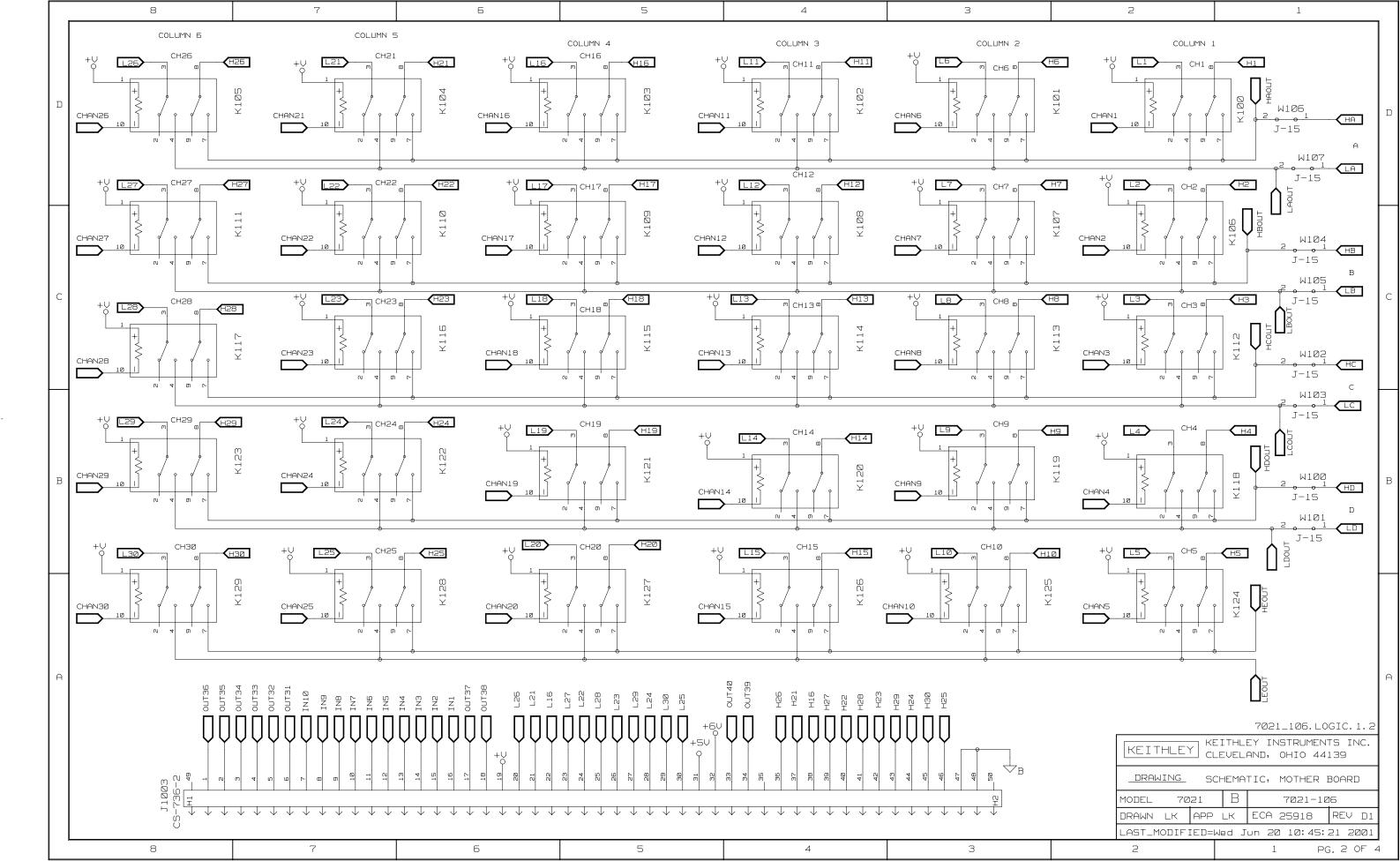

A simplified schematic of the Model 7022 matrix is shown in Figure 2-1. The card is configured as a  $5 \times 6$  matrix. Each of the 30 crosspoints is made up of a two-pole switch. By closing the appropriate crosspoint switch, any matrix row can be connected to any column in the matrix.

Figure 2-1 Model 7022 simplified schematic

#### **Backplane jumpers**

In Figure 2-1, the four pairs of backplane jumpers shown are located on the relay card. With the jumpers installed, the matrix is connected to the analog backplane of the Model 7001/7002 to allow matrix expansion with a second card installed in the mainframe. With the jumpers removed (cut), the matrix is isolated from an adjacent card installed in the mainframe. Note that row E does not connect to the analog backplane.

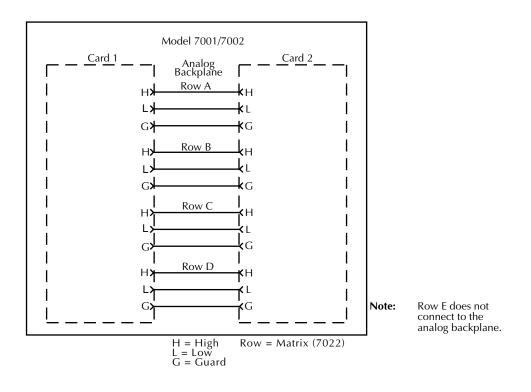

Figure 2-2 Model 7001/7002 analog backplane

The three-pole analog backplane of the mainframe is shown in Figure 2-2. It is through this analog backplane where the rows of a Model 7022 card installed in one slot can be connected to the rows (or banks) of a compatible card installed in the adjacent slot of the mainframe.

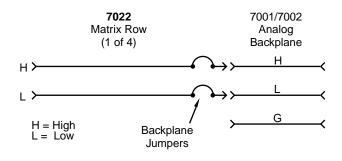

Figure 2-3 shows how each row of the Model 7022 is connected to the backplane. Since the Model 7022 is a two-pole card, it does not provide a connection to the Guard terminal of the backplane. The Model 7022 is shipped from the factory with the backplane row jumpers installed.

Removing (cutting) the backplane jumpers isolates the card from the backplane, and subsequently, any card installed in the adjacent slot. For information on removing the jumpers, refer to Section 4.

#### NOTE

The Model 7001/7002 does not provide an analog backplane for the non-701X/702X/703X series cards. As a result, any of these cards installed in one slot in the main-frame is electrically isolated from any card installed in the adjacent slot. The only way to connect a Model 7022 to one of these cards is to wire them together.

# Typical matrix switching schemes

The following paragraphs describe some basic switching schemes that are possible with a two-pole switching matrix. These switching schemes include some various shielding configurations to help minimize noise pickup in sensitive measurement applications. These shields are shown connected to chassis ground. For some test configurations, shielding may prove to be more effective connected to circuit common. Chassis ground is accessible at the rear panel of the Model 7001/7002.

# Single-ended switching

In the single-ended switching configuration, the source or measure instrument is connected to the DUT through a single pathway as shown in Figure 2-4.

# **Differential switching**

The differential or floating switching configuration is shown in Figure 2-5. The advantage of using this configuration is that the terminals of the source or measure instrument are not confined to the same matrix crosspoint. Each terminal of the instrument can be connected to any matrix crosspoint.

*Figure 2-4 Single-ended switching example*

*Figure 2-5 Differential switching example*

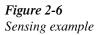

## Sensing

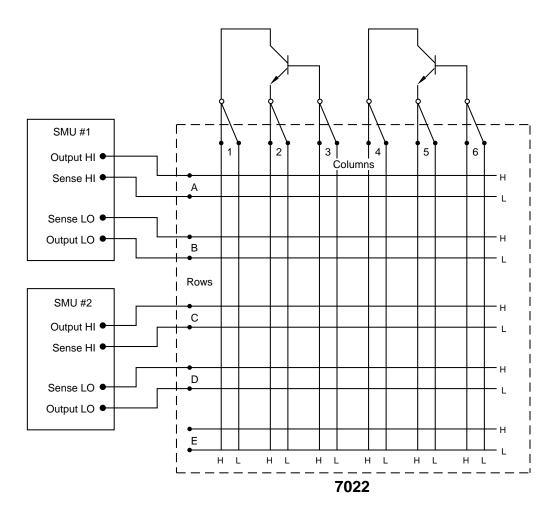

#### **SMU connections**

Figure 2-6 shows how the matrix can be configured to use instruments that have sensing capability. The main advantage of using sensing is to cancel the effects of matrix path resistance ( $<1.25\Omega$ ) and the resistance of external cabling. Whenever path resistance is a consideration, sensing should be used. Figure 2-7 shows how a Keithley Model 236, 237, or 238 Source Measure Unit could be connected to the matrix. By using triax cables that are unterminated at one end, the driven guard and chassis ground are physically extended all the way to the card.

WARNING: Hazardous voltages may be present on GUARD. Make sure all cable shields are properly insulated before applying power.

Figure 2-7 SMU connections

# **Matrix expansion**

With the use of additional cards and mainframes, larger matrices can be configured. Each Model 7001 Switch System mainframe can accommodate up to two cards, and up to six mainframes can be connected together to configure up to 12 cards. Each Model 7002 Switch System mainframe can accommodate up to ten cards. And, by connecting up to six Model 7002 mainframes, 60 cards can be configured. The limits on the number of cards in the Model 7001/7002 are due to triggering.

### **Two-card switching systems**

The Model 7001 and 7002 Switch System mainframes can accommodate two and ten cards, respectively. The following paragraphs use a two-card system to illustrate multiple-card switching configurations.

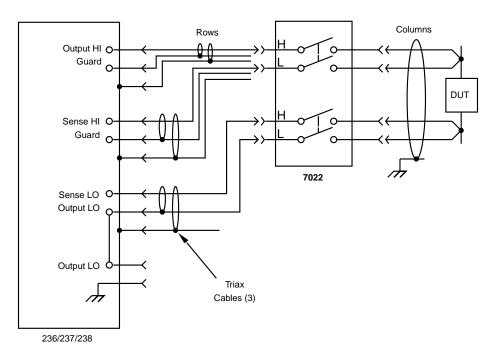

#### Separate switching systems

Two single-card systems can be configured by removing the backplane jumpers from one of the cards. The two cards will be controlled by the same mainframe, but they will be electrically isolated from each other. Figure 2-8 shows an example using two Model 7022 cards.

Figure 2-8

*Two separate*  $5 \times 6$  *matrices*

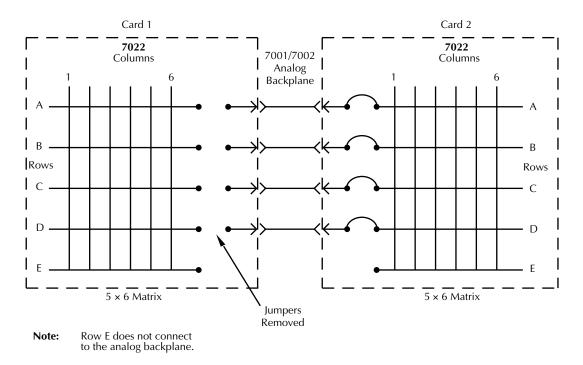

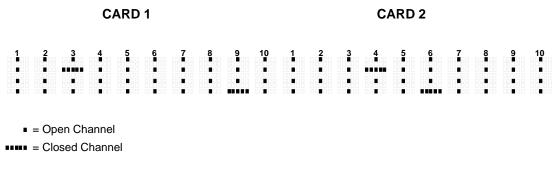

#### Narrow matrix expansion (4 × 12 matrix)

A narrow 4-row by 12-column matrix can be configured by installing two "as shipped" Model 7022s in the Model 7001/7002 mainframe. By leaving the backplane jumpers installed, matrix rows A through D of the card installed in

slot 1 (CARD 1) are automatically connected to matrix rows A through D of the card installed in slot 2 (CARD 2) through the analog backplane. Note that row E does not connect to the analog backplane. The  $4 \times 12$  matrix is shown in Figure 2-9.

Notes: 1. Backplane jumpers on both cards must be installed.2. Row E does not connect to the analog backplane.

*Figure 2-9 Narrow matrix example (4 × 12)*

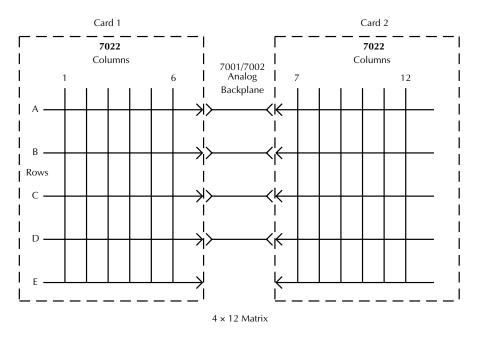

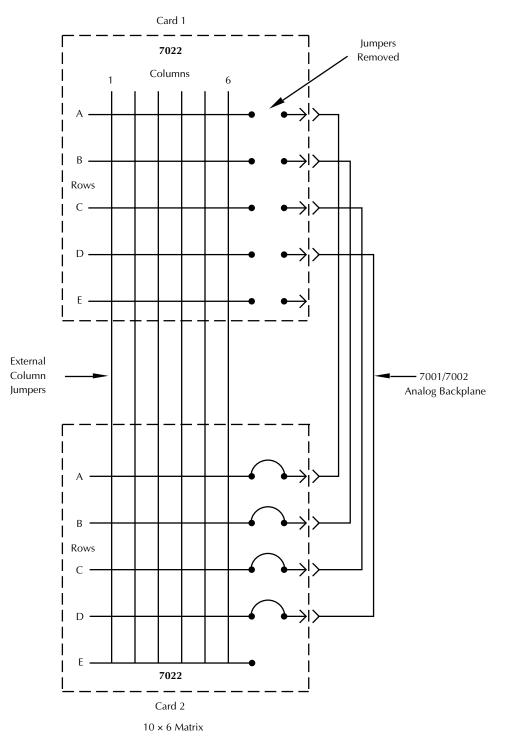

#### Wide matrix expansion $(10 \times 6 \text{ matrix})$

A wide ten-row by six-column matrix is shown in Figure 2-10. For this configuration, the six columns of the two matrices must be physically hard-wired together. Also

note that the backplane jumpers on one of the cards must be removed in order to isolate the rows of the two cards from each other.

*Figure 2-10 Wide matrix example (10 \times 6)*

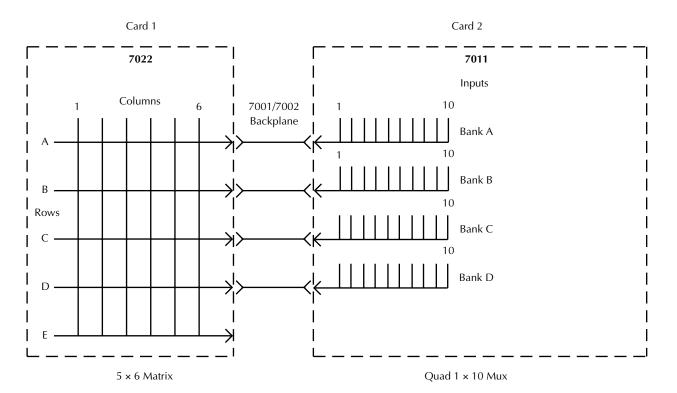

#### Mixing card types

Different types of cards can be used together to create some unique switching systems. For example, you could have a Model 7022 matrix-digital I/O card installed in one slot and a Model 7011 card installed in the adjacent slot.

Figure 2-11 shows a possible switching system using a Model 7011 and a Model 7022. The backplane jumpers for both cards must be installed. This allows matrix rows to be connected to multiplexer banks. On the Model 7011, the bank-to-bank jumpers must be removed to maintain isolation between matrix rows. See the instruction manual for the Model 7011 for complete multiplexer information.

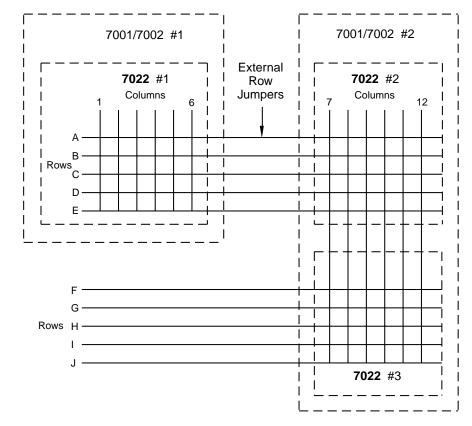

#### Mainframe matrix expansion

A 12-card matrix is possible by using six Model 7001 mainframes together, which provides 360 crosspoints. Also, a 60card matrix is possible by using six Model 7002 mainframes together, which provides 1800 crosspoints. The limits on the number of cards in the Model 7001/7002 switch system are due to triggering.

In general, connecting the rows of a card in one mainframe to the rows of a card in a second mainframe increases the column numbers of the matrix. For example, if the rows of a  $4 \times 12$  matrix in one mainframe are connected to the rows of a  $4 \times 12$  matrix in a second mainframe, the resulting matrix would be  $4 \times 24$ . Section 4 explains how to connect a test system using two mainframes.

Notes: 1. Models 7011 and 7022 backplane jumpers must be installed.2. Model 7011 bank-to-bank jumpers must be removed.

*Figure 2-11 Mixed card type example*

#### Partial matrix implementation

A fully implemented matrix provides a relay at each potential crosspoint. For example, a fully implemented  $10 \times 12$ matrix utilizing four  $5 \times 6$  cards contains 120 crosspoints. A partially implemented  $10 \times 12$  matrix would contain fewer crosspoints.

An example of a partially implemented  $10 \times 12$  matrix is shown in Figure 2-12. The partial matrix is still considered  $10 \times 12$  but contains only 90 crosspoints using three Model 7022 cards installed in two Model 7001/7002 mainframes.

Matrix card #1 (7022 #1) installed in one of the slots of the first mainframe (7001/7002 #1) provides a  $5 \times 6$  matrix. The other slot of the first mainframe should be left empty. If another switching card is left in that slot, it must be isolated from the analog backplane (i.e., backplane jumpers

removed). The two cards (7022 #2 and #3) installed in the second mainframe (7001/7002 #2) are configured as a  $10 \times 6$  matrix as explained in the wide matrix expansion ( $10 \times 6$ ) paragraph. Remember that the rows of card #2 must be isolated from the rows of card #3. This is accomplished by removing the jumpers on one of the two cards. Finally, the partially implemented  $10 \times 12$  matrix is realized by externally hard-wiring the rows of card #1 to the rows of card #2.

An obvious advantage of a partial matrix is that fewer cards are needed. Another reason to use a partial matrix is to keep specific devices from being connected directly to other devices. For example, a source connected to rows F, G, H, I, or J (Figure 2-12) cannot be connected to a column of Model 7022 #1 with one "accidental" crosspoint closure. Three specific crosspoints must be closed in order to route the source signal to a column of card #1.

*Figure 2-12 Partial matrix expansion (10 × 12)*

Matrix Configuration

# **3** Digital I/O Configuration

## Introduction

This section covers the basic digital input and output configurations for the Model 7022. Connection information for these configurations is provided in Section 4 of this manual, while operation (front panel and IEEE-488 bus) is explained in Section 5.

# **Digital outputs**

Output channels are user configurable for negative (low) or positive (high) true logic. That is, the output can be high or low when the channel is turned on (closed) depending upon user configuration. Conversely, the output can be high or low when the channel is turned off (open). Refer to Section 4 to configure the logic to your requirement.

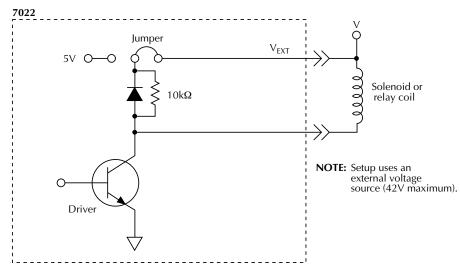

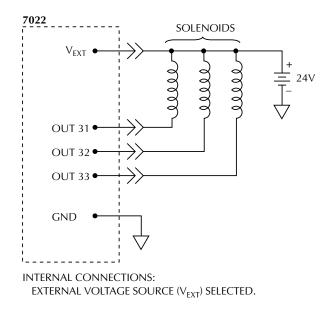

# Controlling pull-up devices

Typically, the digital outputs are used to provide drive for relatively high current devices such as solenoids, relays, and small motors. The configurations for these applications are shown in Figure 3-1. Figure 3-1 allows you to use an external voltage source (V) for devices that require a higher voltage (42V maximum). An internal jumper is used to select the internal pull-up voltage. At the factory, the internal 5V source is selected.

Each output channel uses a fly-back diode for protection when switching an inductive device, such as a solenoid coil. This diode diverts the potentially damaging fly-back voltage away from the driver.

*Figure 3-1 Output configuration for pull-up devices*

# Controlling devices using pull-up resistors

#### CAUTION

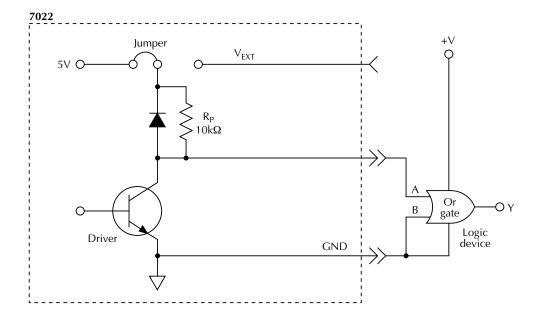

Failure to set J201 to the Vext position, when using external pull-up voltages, may result in damage to the output drivers. When interfacing outputs to high-impedance devices (i.e., logic devices), internal pull-up resistors are used to achieve the appropriate logic level. Figure 3-2 shows the output configuration using the  $10k\Omega$  pull-up resistor (Rp).

The configuration in Figure 3-2 uses the internal 5V source as the high logic level. If you need a higher logic level, you can place the jumper in the alternate position and apply an external voltage (via  $V_{EXT}$ ).

Output configuration using pull-up resistance

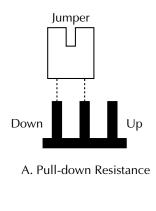

# **Digital inputs**

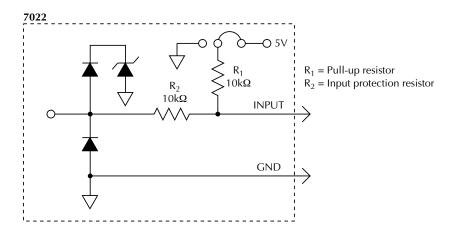

Input channels use positive true logic but can be pulled up or pulled down based on the configuration of the pull-up resistor. Each channel uses a  $10k\Omega$  pull-up resistor (R<sub>1</sub>). The pullup resistors can be pulled up to 5V or pulled down to ground depending on the positioning of the jumper on the input logic bank. Refer to Section 4 for more information. Figure 3-3 shows the resistor being pulled up to 5V.

When the resistor is connected to 5V, the channel is pulled high. Thus, with nothing connected to the channel, the input is pulled high to 5V which displays the channel as on.

When the resistor is connected to ground, the channel is pulled low. Thus, with nothing connected to the channel, the input is pulled low to ground which displays the channel as off.

The digital input is compatible with external TTL logic. Each built-in pull-up resistor provides level shifting so devices such as micro-switches can be monitored. Each input has a protection network that clamps the input at 5.7V. This allows logic levels up to 42V peak to be monitored.

Figure 3-3 Input configuration

Digital I/O Configuration

# **4** Card Connections and Installation

### Introduction

#### WARNING

The procedures in this section are intended only for qualified service personnel. Do not perform these procedures unless qualified to do so. Failure to recognize and observe normal safety precautions could result in personal injury or death.

The information in this section is arranged as follows:

- Handling precaution Explains precautions that must be followed to prevent contamination to the card. Contamination could degrade the performance of the card.

- Matrix connections Covers the basics for connecting external circuitry to the connector card.

- **Digital I/O connections** Explains the voltage source jumpers, pull-up resistors, output logic, and input resistance and how to configure them.

- Multi-pin (mass termination) connector card Covers the basic connections to the 96-pin DIN male connector and identifies each terminal.

- **Typical matrix connection schemes** Provides some typical connection schemes for single-card, two-card, and two-mainframe system configurations.

- **Typical digital I/O connection schemes** Provides some typical connection schemes for output solenoid, relay, motor, and logic device control and for input micro-switch monitoring.

- Model 7022 installation and removal Provides a procedure to install and remove the Model 7022 card from the Model 7001/7002 mainframe.

# Handling precautions

To maintain high impedance isolation, care should be taken when handling the relay and connector cards to avoid contamination from such foreign materials as body oils. Such contamination can substantially lower leakage resistances, thus degrading performance.

To avoid possible contamination, always grasp the relay and connector cards by the side edges or shields. Do not touch the board surfaces or components. On connectors, do not touch areas adjacent to the electrical contacts. Dirt build-up over a period of time is another possible source of contamination. To avoid this problem, operate the mainframe and card in a clean environment.

If a card becomes contaminated, it should be thoroughly cleaned as explained in Section 6.

# **Matrix connections**

The following paragraphs provide the basic information needed to connect your external test circuitry to the matrix. The removal/installation of the backplane row jumpers on the relay card and detailed information on the connector card is included.

#### WARNING

The following connection information is intended to be used by qualified service personnel. Failure to recognize and observe standard safety precautions could result in personal injury or death.

### **Backplane row jumpers**

The Model 7001/7002 mainframe has an analog backplane that allows the matrix rows of a Model 7022 to be internally connected to a compatible switching card installed in the adjacent slot. (See Section 2 for details.)

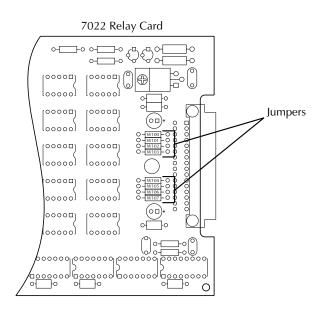

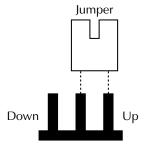

The backplane row jumpers for the card are located on the relay card as shown in Figure 4-1. The card is shipped from the factory with the jumpers installed.

# Jumper removal

Perform the following steps to remove the backplane row jumpers:

- 1. If mated together, separate the relay card from the connector card by removing the mounting screw and then pulling the two cards away from each other. Remember to only handle the cards by the edges and shields to avoid contamination.

- 2. Use Figure 4-1 to locate the jumper(s) to be removed.

- 3. It is not necessary to physically remove the jumpers from the PC board. Using a pair of wire cutters, cut one lead of each jumper.

# Jumper installation

Referring to Figure 4-1 for jumper locations, perform the following steps to install the backplane row jumpers:

- 1. If mated together, separate the relay card from the connector card by removing the mounting screw and then pulling the two cards away from each other. Remember to only handle the cards by the edges and shields to avoid contamination.

- 2. Physically remove a cut jumper by unsoldering it from the PC board.

- 3. Install a new #22 AWG jumper wire (Keithley P/N J-15) and solder it to the PC board.

- 4. Remove the solder flux from the PC board. The cleaning procedure is explained in Section 6.

# **Digital I/O connections**

# Voltage source jumper

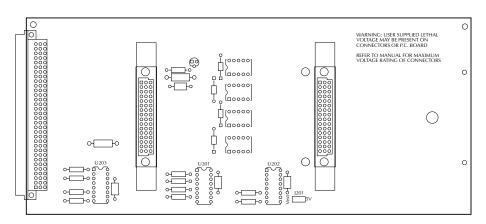

Digital output high uses the internal +5V source as the high logic level. If higher voltages are required, a user-supplied voltage can be used (42V maximum). At the factory, the internal jumper is set to use the internal +5V source.

#### CAUTION

Failure to set J201 to the Vext position, when using external pull-up voltages, may result in damage to the output drivers.

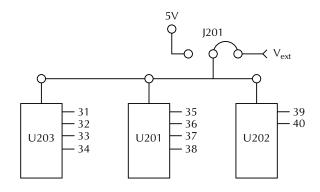

A plug-in jumper for the bank allows you to select the internal +5V source or an external source. In Figure 4-2, the banks are using the external voltage source.

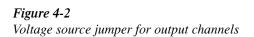

The voltage source jumper is located on the connector board as shown in Figure 4-3. Figure 4-4 shows how the plug-in jumper is installed on J201.

+5V

# **Pull-up resistors**

When interfacing outputs to high-impedance devices (i.e., logic devices), pull-up resistors are used to achieve the appropriate logic level. These resistors are installed at the factory.

#### Figure 4-3

Component locations - connector board

*Figure 4-4 Voltage source jumper installation*

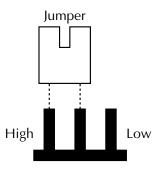

# Configuring digital I/O output logic

Referring to Figure 4-5 for the digital I/O output logic location, perform the following steps to configure J101:

- 1. If mated together, separate the relay card from the connector card by removing the mounting screw and then pulling the two cards away from each other. Remember to only handle the cards by the edges and shields to avoid contamination.

- 2. Locate J101 on the relay board. Refer to Figure 4-5.

- 3. Determine if you require positive (high) or negative (low) logic.

- 4. Install the plug-in jumper in the appropriate position as shown in Figure 4-6.

Figure 4-5 Digital I/O output logic location

A. High Selected

B. Low Selected

Figure 4-6 Digital I/O output logic selection

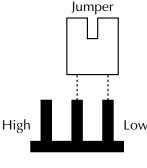

# Configuring digital I/O input pull-up resistance

Referring to Figure 4-5 for digital I/O input pull-up resistance location, perform the following steps to configure J100:

- 1. If mated together, separate the relay card from the connector card by removing the mounting screw and then pulling the two cards away from each other. Remember to only handle the cards by the edges and shields to avoid contamination.

- 2. Locate J100 on the relay board. Refer to Figure 4-5.

- 3. Determine if you require pull-up (5V) or pull-down (ground) input logic.

- 4. Install the plug-in jumper in the appropriate position as shown in Figure 4-7.

B. Pull-up Resistance Selected

#### Figure 4-7

Digital I/O input pull-up resistance selection

# Multi-pin (mass termination) connector card

Since connections to external circuitry are made at the 96-pin male DIN bulkhead connector, there is no need to separate the connector card from the relay card. If the connector card is separated from the relay card, carefully mate them together. Make sure to handle the cards by the edges and shields to avoid contamination.

Keithley has a variety of cable and connector accessories available to accommodate connections from the connector card to test instrumentation and DUT (devices under test). In general, these accessories, which are summarized in Table 4-1, utilize a round cable assembly for connections.

# Table 4-1

Mass termination accessories

| Model      | Description                                                                                          |

|------------|------------------------------------------------------------------------------------------------------|

| 7011-KIT-R | 96-pin female DIN connector and hous-<br>ing for round cable (provided with the<br>Model 7022 card). |

| 7011-MTC-2 | Two-meter round cable assembly termi-<br>nated with a 96-pin female DIN connec-<br>tor on each end.  |

| 7011-MTR   | 96-pin male DIN bulkhead connector.                                                                  |

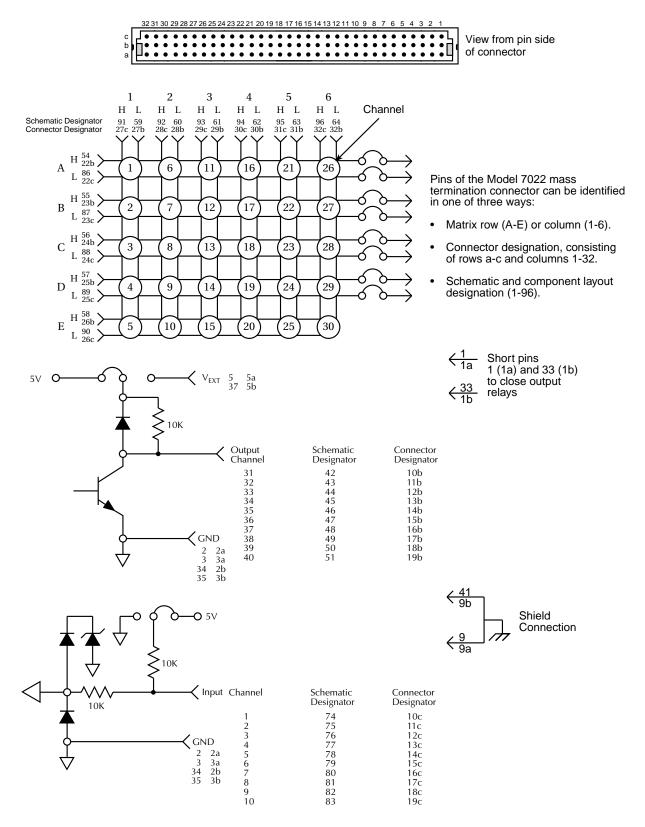

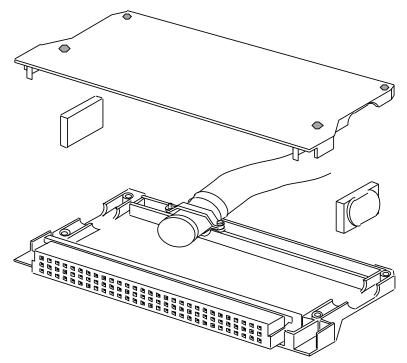

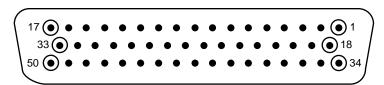

Terminal identification for the DIN connector of the multipin connector card is provided by Figure 4-8 and Table 4-2. This connector will mate to a 96-pin female DIN connector.

*Figure 4-8 Multi-pin connector card terminal identification*

Table 4-2Pin designation identification

| Matrix<br>terminal | Connector<br>designator<br>1a-32c | Schematic<br>designator<br>1-96 | Matrix<br>terminal | Connector<br>designator<br>1a-32c | Schematic<br>designator<br>1-96 | Matrix<br>terminal | Connector<br>designator<br>1a-32c | Schematic<br>designator<br>1-96 |

|--------------------|-----------------------------------|---------------------------------|--------------------|-----------------------------------|---------------------------------|--------------------|-----------------------------------|---------------------------------|

| row A, HI          | 22b                               | 54                              | IN 1               | 10c                               | 74                              | nc                 | 12a                               | 12                              |

| row A, LO          | 22c                               | 86                              | IN 2               | 11c                               | 75                              | nc                 | 13a                               | 13                              |

| row B, HI          | 23b                               | 55                              | IN 3               | 12c                               | 76                              | nc                 | 14a                               | 14                              |

| row B, LO          | 23c                               | 87                              | IN 4               | 13c                               | 77                              | nc                 | 15a                               | 15                              |

| row C, HI          | 24b                               | 56                              | IN 5               | 14c                               | 78                              | nc                 | 16a                               | 16                              |

| row C, LO          | 24c                               | 88                              | IN 6               | 15c                               | 79                              | nc                 | 17a                               | 17                              |

| row D, HI          | 25b                               | 57                              | IN 7               | 16c                               | 80                              | nc                 | 18a                               | 18                              |

| row D, LO          | 25c                               | 89                              | IN 8               | 17c                               | 81                              | nc                 | 19a                               | 19                              |

| row E, HI          | 26b                               | 58                              | IN 9               | 18c                               | 82                              | nc                 | 20a                               | 20                              |

| row E, LO          | 26c                               | 90                              | IN 10              | 19c                               | 83                              | nc                 | 21a                               | 21                              |

| col 1, HI          | 27c                               | 91                              | vext               | 5a                                | 5                               | nc                 | 22a                               | 22                              |

| col 1, LO          | 27b                               | 59                              | vext               | 5b                                | 37                              | nc                 | 23a                               | 23                              |

| col 2, HI          | 28c                               | 92                              | shield             | 9a                                | 9                               | nc                 | 24a                               | 24                              |

| col 2, LO          | 28b                               | 60                              | shield             | 9b                                | 41                              | nc                 | 25a                               | 25                              |

| col 3, HI          | 29c                               | 93                              | gnd                | 2a                                | 2                               | nc                 | 26a                               | 26                              |

| col 3, LO          | 29b                               | 61                              | gnd                | 3a                                | 3                               | nc                 | 27a                               | 27                              |

| col 4, HI          | 30c                               | 94                              | gnd                | 2b                                | 34                              | nc                 | 28a                               | 28                              |

| col 4, LO          | 30b                               | 62                              | gnd                | 3b                                | 35                              | nc                 | 29a                               | 29                              |

| col 5, HI          | 31c                               | 95                              | inter              | 1b                                | 33                              | nc                 | 30a                               | 30                              |

| col 5, LO          | 31b                               | 63                              | inter              | 1a                                | 1                               | nc                 | 31a                               | 31                              |

| col 6, HI          | 32c                               | 96                              | nc                 | 4b                                | 36                              | nc                 | 32a                               | 32                              |

| col 6, LO          | 32b                               | 64                              | nc                 | 6b                                | 38                              | nc                 | 1c                                | 65                              |

| OUT 31             | 10b                               | 42                              | nc                 | 7b                                | 39                              | nc                 | 2c                                | 66                              |

| OUT 32             | 11b                               | 43                              | nc                 | 8b                                | 40                              | nc                 | 3c                                | 67                              |

| OUT 33             | 12b                               | 44                              | nc                 | 20b                               | 52                              | nc                 | 4c                                | 68                              |

| OUT 34             | 13b                               | 45                              | nc                 | 21b                               | 53                              | nc                 | 5c                                | 69                              |

| OUT 35             | 14b                               | 46                              | nc                 | 4a                                | 4                               | nc                 | 6c                                | 70                              |

| OUT 36             | 15b                               | 47                              | nc                 | 6a                                | 6                               | nc                 | 7c                                | 71                              |

| OUT 37             | 16b                               | 48                              | nc                 | 7a                                | 7                               | nc                 | 8c                                | 72                              |

| OUT 38             | 17b                               | 49                              | nc                 | 8a                                | 8                               | nc                 | 9c                                | 73                              |

| OUT 39             | 18b                               | 50                              | nc                 | 10a                               | 10                              | nc                 | 20c                               | 84                              |

| OUT 40             | 19b                               | 51                              | nc                 | 11a                               | 11                              | nc                 | 21c                               | 85                              |

#### Typical connection techniques

All external circuitry, such as instrumentation and DUTs, that you want to connect to the card must be terminated with a single 96-pin female DIN connector. The following connection techniques provide some guidelines and suggestions for wiring your circuitry.

#### WARNING

Before beginning any wiring procedures, make sure all power is off and any stored energy in external circuitry is discharged.

#### WARNING

When wiring a connector, do not leave any exposed wires. No conductive part of the circuit may be exposed. Properly cover the conductive parts, or death by electric shock may occur.

#### NOTE

It is recommended that external circuitry be connected (plugged in) after the Model 7022 is installed in the Model 7001/7002 mainframe and with the mainframe power off. Installation is covered at the end of this section.

**Output relays** — The multi-pin connector card uses a relay for each of the four output banks. These output relays are normally open to prevent any hazardous voltages (via the mainframe backplane) from appearing on the pins of the male DIN connector. The output relays will only close when the Model 7011-MTC-2 cable assembly is connected to card. If building your own cable assembly, make sure it shorts pins 1a to 1b of the card connector (Figure 4-10) when it is mated to the card. Shorting pins 1a to 1b allows the output relays to close.

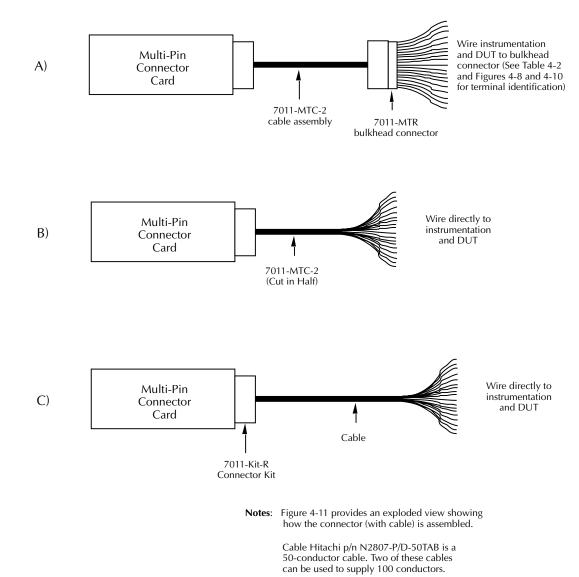

**Round cable assemblies** — Figure 4-9 shows typical round cable connection techniques using accessories available from Keithley.

*Figure 4-9 Typical round cable connection techniques*

.

In Figure 4-9A, connections are accomplished using a Model 7011-MTC-2 cable and a Model 7011-MTR bulkhead connector. The two-meter round cable is terminated with a 96-pin female DIN connector at each end. This cable mates directly to the multi-pin connector card and to the bulkhead connector. The bulkhead connector has solder cups to allow direct connection to instrumentation and DUT. Figure 4-10 provides pinout for the bulkhead connector. The view shown is from the solder cup end of the connector.

In Figure 4-9B, connections are accomplished using a Model 7011-MTC-2 cable assembly that is cut in half. The 96-pin female DIN connector on one end of the cable mates directly to the multi-pin connector card. The unterminated end of the cable is wired directly to instrumentation and DUT. The other half of the cable assembly could be used for a second switching card.

In Figure 4-9C, connections are accomplished using a custom-built cable assembly that consists of a Model 7011-KIT-R connector and a suitable round cable. Hitachi cable part number N2807-P/D-50TAB is a 50-conductor round cable. Two of these cables can be used to provide 100 conductors. The connector has solder cups to accommodate the individual wires of the unterminated cable. Figure 4-11 provides an exploded view of the connector assembly and shows how the cable is connected. For further Model 7011-KIT-R assembly information, refer to the packing list provided with the kit. The connector end of the resultant cable assembly mates directly to the multi-pin connector card. The unterminated end of the cable assembly is wired directly to instrumentation and DUT.

View from solder cup side of connector

#### *Figure 4-10 Model 7011-MTR connector pinout*

Figure 4-11 Model 7011-KIT-R (with cable) assembly

# Typical matrix connection schemes

The following information provides some typical connection schemes for single-card, two-card, and two-mainframe system configurations. Connection schemes for the multi-pin connector card use some of the techniques presented in this section. Keep in mind that these are only examples to demonstrate various ways to wire a test system.

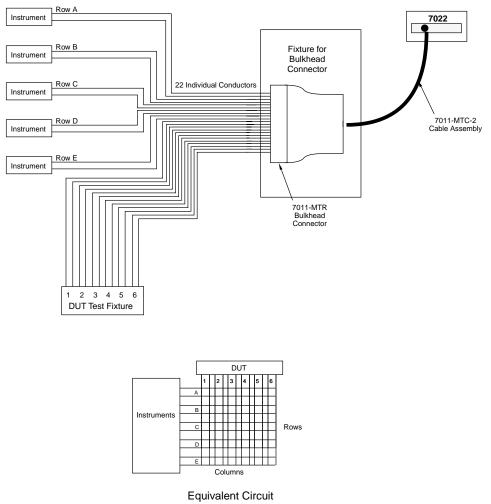

# Single-card system

Figure 4-12 shows how external connections can be made to a single-card system that uses the multi-pin connector card. Instrumentation and DUT are hard-wired to the Model 7011-MTR male bulkhead connector. This connector has solder cups that will accept wire size up to #24 AWG. The test system is connected to the matrix using the Model 7011-MTC-2 round cable assembly. This cable mates directly to both the external bulkhead connector and the Model 7022. Notice that the bulkhead connector is shown mounted to a fixture to help keep the cabling stable during the test.

When using a single-card system, make sure that the card remains electrically isolated from any other switching cards. There are several ways to ensure isolation for a single card in the Model 7001/7002 mainframe:

- 1. Vacate the adjacent slot in the mainframe. If there is a Model 70XX card installed in the other slot, remove it.

- 2. Remove the backplane jumpers on the card. This will disconnect the card from the analog backplane of the mainframe.

- 3. Remove the backplane jumpers from the switching card installed in the adjacent slot.

Figure 4-12 Single-card system example

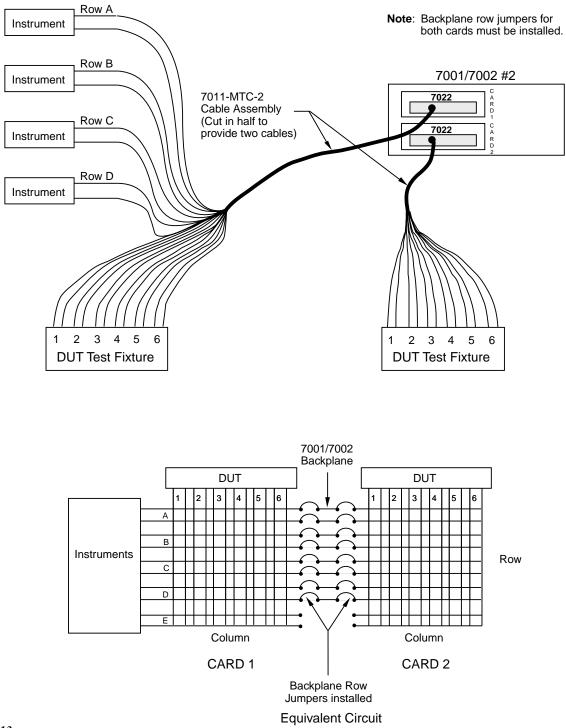

# Two-card system

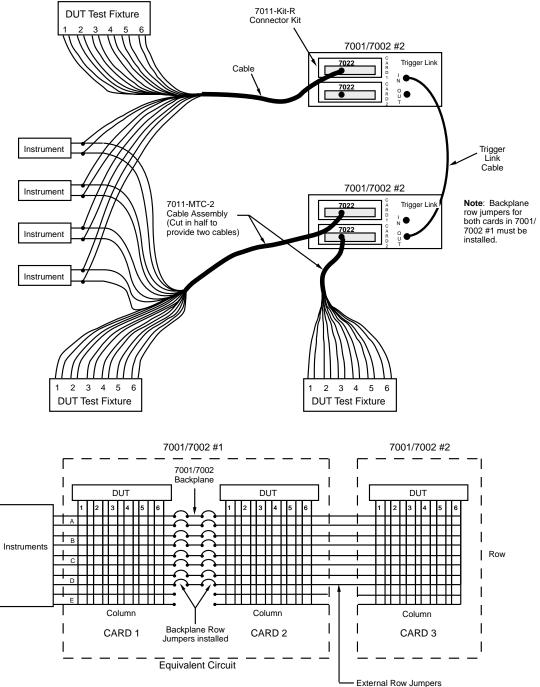

Figure 4-13 shows a system using two Model 7022 cards installed in one Model 7001/7002 mainframe to configure a  $4 \times 12$  test matrix. In this connection scheme, row connections of the two cards are accomplished internally through the backplane of the mainframe. To connect rows internally, the backplane row jumpers of both cards must be installed.

Figure 4-13 shows how external connections can be made for the multi-pin connector cards. In this example, a single Model 7011-MTC-2 round cable assembly is cut in half to provide two cables, each of which is unterminated at one end. The unterminated ends of the two cables are hard-wired to instrumentation and DUT as shown in the drawing. The other ends of these cables mate directly to the Model 7022 cards.

*Figure 4-13 Two-card system example*

# **Two-mainframe system**

Figure 4-14 shows a system using three cards in two Model 7001/7002 mainframes to configure a  $4 \times 18$  test matrix. This system is similar to the two-card system (see previous paragraph), except that a third card (installed in a second mainframe) is added.

Figure 4-14 shows the connection scheme for the multi-pin connector cards. External circuit connections to the Model

7001/7002 #1 mainframe are identical to the ones used for the two-card system. The third card (installed in Model 7001/7002 #2 mainframe) shows how a custom-built cable can be used to make connections to external circuitry. A suitable round cable can be terminated with a 96-pin female DIN connector (Model 7011-KIT-R) that will mate to the Model 7022. The unterminated end of the cable is connected directly to instrumentation and DUT. Notice that the row connections for the third card are made at the instruments.

*Figure 4-14 Two-mainframe system example*

# Typical digital I/O connection schemes

# **Output connection schemes**

The following examples show output connections from the card to external circuitry and summarizes the required internal connections on the card. Each example assumes negative true logic is used. To configure for positive true logic, refer to the Configuring digital I/O output logic paragraph.

**Solenoid control** — Figure 4-15 shows a digital output connection scheme to control solenoids. This example assumes that an external 24V source is being used. A solenoid is energized when the corresponding output channel is turned on (closed).

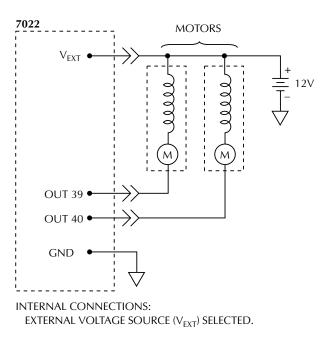

**Motor control** — Figure 4-16 shows a digital output connection scheme to control small 12V dc motors. An external 12V source is used to provide the necessary voltage level. A motor is turned on when the corresponding output channel is turned on (closed).

Figure 4-16 Digital output, motor control

**Logic device control** — Figure 4-17 shows a digital output connection scheme to control a logic device. This example assumes that an internal +5V voltage source is being used.

The logic device is a demultiplexer (DMUX). The binary pattern (value) seen at the input of the DMUX (lines A, B, and C) determines which DMUX output line (Y0 through Y7) is selected (pulled low). For example, with channels 1, 2, and 3 off (open), lines A, B and C are high. The binary 7 at the DMUX input (A = 1, B = 1 and C = 1) selects (pulls low) output Y7. If channel 2 is turned on (closed), line B goes low. The binary 5 seen at the DMUX input (1, 0, 1) selects (pulls low) Y5.

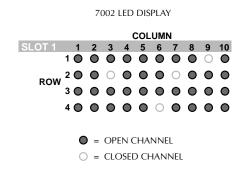

#### Input connection scheme

Figure 4-18 shows a digital input connection scheme to monitor the state of micro-switches. With a switch open and the input resistor configured for pull up as shown in Figure 4-18a, the corresponding input channel is pulled high by the internal input resistor. As a result, the input channel is high (appears as a bar on the Model 7001 display or a lit LED on the Model 7002). When a switch is closed, the corresponding input channel is pulled low to ground. As a result, the input channel is low (appears as a single dot on the Model 7001 display or an unlit LED on the Model 7002).

B. INPUT RESISTOR IS SET TO PULL DOWN.

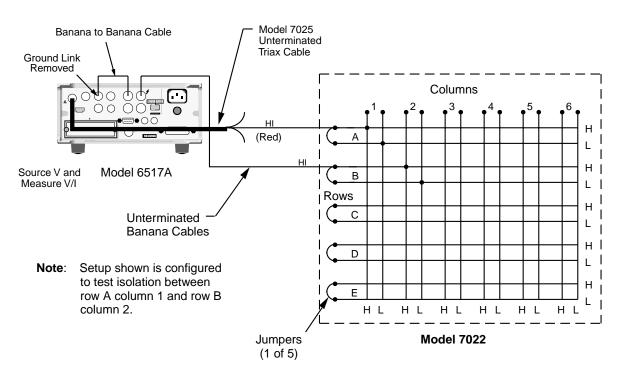

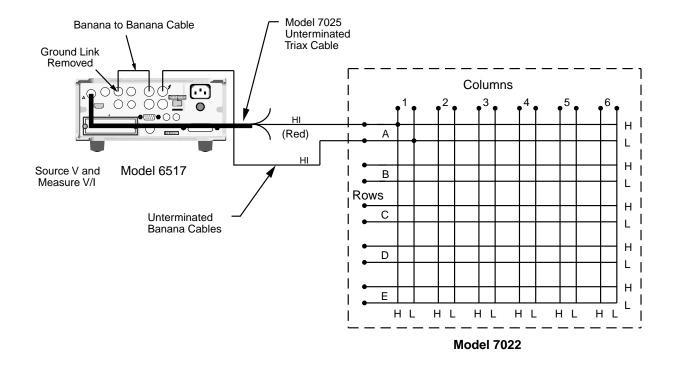

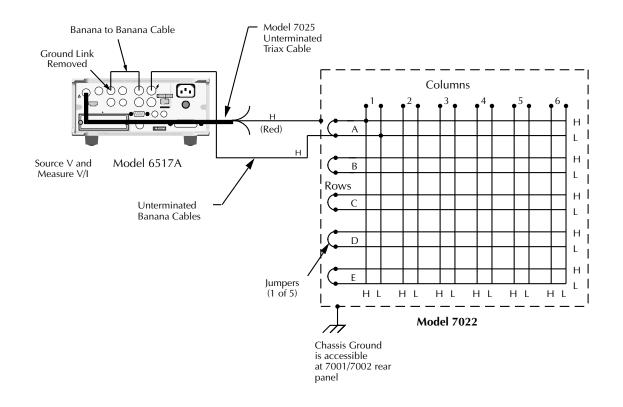

*Figure 4-18 Digital input, monitoring micro-switches*