# IMAGE SYSTEM CONTROLLER USER'S MANUAL

KEITHLEY/METRABYTE CORP.

# **CONTENTS**

| Section | 1                                    | Page |

|---------|--------------------------------------|------|

| 1       | Introduction                         | 1-1  |

| 1.1     | Features                             | 1-1  |

| 2       | Pinout and Signal Description        | 2-1  |

| 3       | Architecture                         | 3-1  |

| 3.1     | Host Interface                       | 3-1  |

| 3.2     | Arbiter                              | 3-1  |

| 3.3     | Address Generator                    | 3-2  |

| 3.4     | VRAM Controller                      | 3-2  |

| 3.5     | Display Timing Generator             | 3-4  |

| 3.6     | Display Update Generator             | 3-5  |

| 4       | Programmable Registers               | 4-1  |

| 4.1     | Register Values After Reset          | 4-2  |

| 4.2     | Host Interface Registers             | 4-2  |

| 4.3     | Display/Acquire Control Registers    | 4-8  |

| 4.4     | Video Timing Registers               | 4-9  |

| 4.5     | Address Generator Registers          | 4-11 |

| 5       | Host and Memory Interface Operations | 5-1  |

| 5.1     | Arbitration                          | 5-1  |

| 5.2     | Internal Register Access             | 5-1  |

| 5.3     | Display Update Cycle                 | 5-3  |

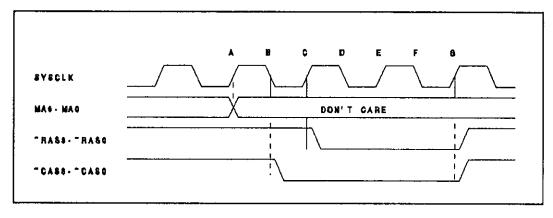

| 5.4     | CAS-before-RAS Refresh Cycle         | 5-4  |

| 5.5     | Host Direct Cycle                    | 5-5  |

| 5.6     | X-Y Indirect Cycle                   | 5-6  |

| 5.7     | Read/Write Transfer Cycle            | 5-6  |

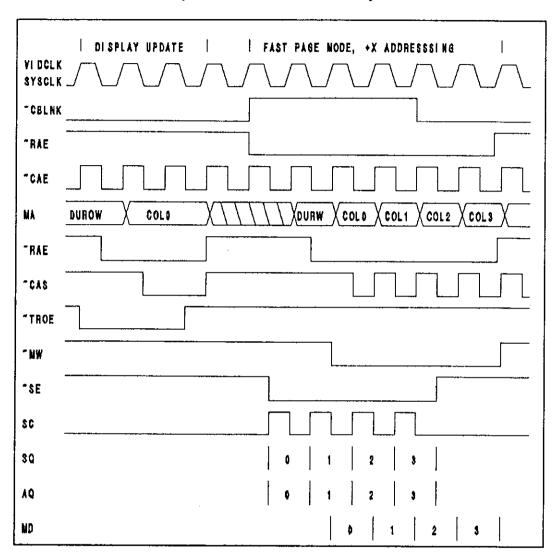

| 5.8     | Fast Page Mode                       | 5-7  |

| 5.9     | RDY interface                        | 5-8  |

| 5.10    | Reset and Initial Setup              | 5-9  |

| 6       | Display and Acquire Control          | 6-1  |

| 6.1     | Auto-Acquire                         | 6-1  |

| 6.2     | Internally Generated Video Signals   | 6-1  |

| 6.3     | External Sync Modes                  | 6-3  |

| 0.3     | Entertial Offic Haddes               |      |

| 7       | Specifications                       | 7-1  |

| Q       | Real-Time Processing with the ISC    | 8-1  |

# 1. INTRODUCTION

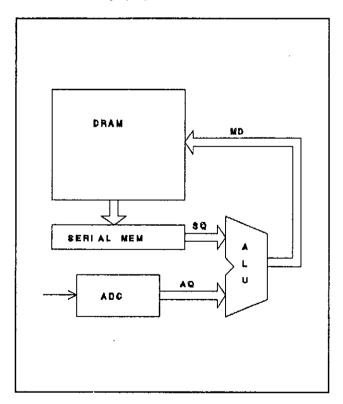

The Image System Controller (ISC) is designed in 1.5 micron CMOS. The primary function of the ISC is that of a VRAM controller. Unlike generic VRAM controllers for graphics applications, the ISC is optimized for both acquisition and display control. The ISC is designed to work with both 256K and 1 MEG VRAMs. In addition to providing all the necessary video timing and display update control, the ISC also provides flexible address generation to fit a variety of VRAM architectures. The ISC has a 16 MEG direct address space as well as a block address mode for a smaller 64K address space. Although designed as a VRAM controller, the ISC can be used as a DRAM controller as well. Two very important features of the chip are auto-acquisition which allows single or multiple acquires by simply toggling a pin and real-time processing mode which creates and coordinates all the timing signals necessary to perform frame rate pixel processing.

## 1.1 FEATURES

The ISC is highly programmable and supports a broad range of display resolutions and memory architectures. The following are the major ISC features:

- Generates all of the necessary VRAM/DRAM control signals for 256 K and 1 MEG devices.

- Synchronizes to external video sources as well as internally generates all video signals necessary for display including composite sync and blank.

- Supports interlaced and non-interlaced video with vertical wrap around for line scan applications.

- Automatically generates address and control signals for display/acquire update cycles.

- Addressing space of 16 MEG in either one-for-one direct, 64 K at a time block mode or X-Y addressing with a four bit code for registered mapped applications.

- Provides multiple step sizes for X-Y addressing for greater flexibility of memory architectures and the ability to move around an image by steps of more than one pixel at a time.

- Allows fast page mode cycles.

- CAS-before-RAS burst DRAM refresh.

- Automatically acquires one or many frames with a simple pulse(s) to a pin.

- Automatically generates all address and control signals for real-time processing at frame rates.

- Provides arbitration between internally generated memory cycles and host initiated cycles.

- Automatically reformats data when image is acquired via the serial access port of a bank-by-four memory architecture.

- Enables host controlled read and write transfers between DRAM and SAM.

- Automatically reformats data for images acquired via the serial access port with a bank-by-four memory architecture.

# 2. PINOUT and SIGNAL DESCRIPTION

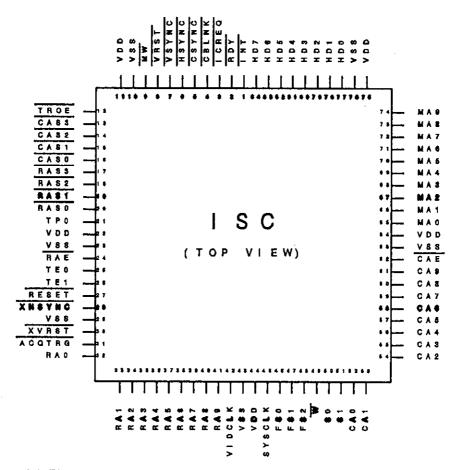

Figure 2.1 shows the signal names and pin numbers for the 84 pin package of the ISC. A description of the signals is given in Table 2.1.

Figure 2.1. Pin Assignment and Signal Names

The ISC is packaged in an 84 pin J-lead plastic chip carrier (PLCC).

| SIGNAL  | PIN   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA9-MA0 | 74-65 | 0   | Memory Address 9-0 These ten memory address outputs multiplex between ROW address at RAS time and COL address at CAS time. They are further multiplexed internally for display update address, X-Y address, host direct address or all 0's CAS-before-RAS refresh. These outputs are designed to drive VRAM/DRAM directly but a buffer is recommended for driving large or many banks of memory. |

| RA9-RA0 | 41-32 | I   | Row Address 9-0 These ten address pins are multiplexed to the memory address pins at RAS time during a host direct, read transfer or write transfer memory access. The Row address is latched on ~RAE going low.                                                                                                                                                                                 |

| CA9-CA0 | 61-52 | I   | Col Address 9-0  These ten address pins are multiplexed to the memory address pins at CAS time during a host direct, read transfer or write transfer memory access. The Col address is latched on ~CAE going low. During an X-Y address cycle, the four LSB's of these pins determine the X-Y function adjust.                                                                                   |

| S1,S0   | 51,50 | I   | Select RAS/CAS 1,0  These two select pins are user programmable to select either or both of Row address selects (RAS) and Col address selects (CAS) during a host direct, read transfer or write transfer memory access. Select is latched on ~CAE going low.                                                                                                                                    |

| ~RAE    | 24    | I   | Active Low Row Address Enable The high-to-low transition of RAE latches RA9-RA0 and FS2-FS0 and initiates a host access cycle. During an X-Y address cycle the Row address register is updated on the rising edge of RAE. RAE is synchronous with SYSCLK and must meet setup and hold requirements.                                                                                              |

| ~CAE    | 62    | I   | Active Low Col Address Enable The high-to-low transition of CAE latches CA9-CA0 and S1,S0. During an X-Y address cycle the Col address register is updated on the rising edge of CAE. CAE is synchronous with SYSCLK and must meet setup and hold requirements.                                                                                                                                  |

| ~W      | 49    | I   | Read/Write During non-SAM transfer host initiated memory cycles, ~W determines the direction of data transfer and the state of the memory write pin (~MW). Also, during an internal register access, ~W determines if data is to be read from or written to an internal register.                                                                                                                |

| ~INT    | 1     | O   | Active Low Interrupt Request This output indicates that a previously enabled interrupt condition has occurred. This signal will remain active until the internal status register has been read. Four independent conditions may trigger an                                                                                                                                                       |

interrupt, the end of an acquisition, a display update or refresh error or that a previously selected scan line has been reached.

| SIGNAL  | PIN   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

|---------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ~RDY    | 2     | 0   | Active Low Ready Under normal circumstances, this pin is at a high impedance state. At the beginning of a host access (~RAE>LOW), the ready pin goes high and remains high until the ISC recognizes the host initiated cycle AND the user defined wait state has been reached. At this point the ready pin will go low and remain low until ~RAE goes high. |

| ~ICREQ  | 3     | O   | Active Low Internal Cycle Request This output indicates that an internal cycle is pending (display update or refresh). This pin will remain LOW until the internal cycle has been serviced.                                                                                                                                                                 |

| HD7-HD0 | 84-77 | BI  | Host Data Bus 7-0 The internal registers of the ISC are accessed via these eight bi- directional data pins. Setup and hold times relative to ~CAE must be observed.                                                                                                                                                                                         |

| FS2-FS0 | 48-46 | I . | Function Select 2-0 These three bits form the function select code that determine the type of cycle requested by the host processor. These bits are latched on ~RAE going low and must meet the specified setup and hold times.                                                                                                                             |

| SYSCLK  | 45    | I   | System Clock The system clock is used to generate all memory timing signals. All host interface signals must be synchronous to SYSCLK.                                                                                                                                                                                                                      |

| ~RESET  | 27    | Ι   | Active Low Reset The Reset puts all of the ISC's internal registers and counters and output signals to a known state. Reset must be held low for a minimum of three SYSCLK periods. After Reset has been released, the ISC puts out a burst of eight CAS-before-RAS refresh cycles every 512 SYSCLK periods until the internal registers are reprogrammed.  |

| ~ACQTRG | 31    | I   | Active Low Acquire Trigger This pin is used to enable displays and acquires. When this signal is pulsed low, the ISC waits for the beginning of the next frame, acquires/displays the frame and then sets the End Acquire bit in the status register. If ~ACQTRG is held low, the ISC will continuously display/acquire.                                    |

| SIGNAL      | PIN   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ~RAS3-~RAS0 | 17-20 | O   | Active Low Row Address Strobe 3-0  These outputs drive the ~RAS inputs to VRAM/DRAM. The operation of these pins are controlled by the ISC control registers. If bit 13 of control register A is set, the source of control is the S1 and S0 input pins during a host direct, read transfer or write transfer memory cycle. If bit 15 of control register B is set, the source of control for these outputs is the block mode register for these cycles. If bit 11 of control register A is set, then all four RAS outputs will become active for all host initiated memory cycles. During an X-Y address cycle (if bit 11 of control register A is NOT set) the source of control for these outputs is the X-Y address register. During an internal display update cycle, the source of control is normally the display address register. If bit 11 of control register B is set, then all four RAS outputs become active during a display update cycle. During a CAS-before-RAS refresh cycle, all four RAS outputs become active. |

| ~CAS3-~CAS0 | 13-16 | Ο   | Active Low Col Address Strobe 3-0  These outputs drive the ~CAS inputs to VRAM/DRAM. The operation of these pins are controlled by the ISC control registers. If bit 12 of control register A is set, the source of control is the S1 and S0 input pins during a host direct, read transfer or write transfer memory cycle. If bit 15 of control register B is set, the source of control for these outputs is the block mode register for these cycles. If bit 10 of control register A is set, then all four CAS outputs will become active for all host initiated memory cycles. During an X-Y address cycle (if bit 10 of control register A is NOT set) the source of control for these outputs is the X-Y address register. During an internal display update cycle, the source of control is normally the display address register. If bit 10 of control register B is set, then all four CAS outputs become active during a display update cycle. During a CAS-before-RAS refresh cycle, all four CAS outputs become active. |

| ~MW         | 9     | 0   | Memory Write This output drives the Write Enable inputs to VRAM/DRAM. During a non-SAM transfer host initiated memory cycles, this output follows the ~W input pin. During a SAM transfer cycle, the state of this output is determined by the Function Select Codes. During an internal display update memory cycle, the state of this pin is determined by bit 12 of control register B. During a CAS-before-RAS refresh cycle, this output remains high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ~TROE       | 12    | O   | Active Low Shift Register Transfer and Output Enable This output drives the ~TROE input of VRAM or the ~OE input of DRAM. During a non-SAM transfer host initiated memory cycle,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

the state of this output is determined by the ~W input pin. During a SAM transfer memory cycle, the state of this pin is determined by the Function Select pins. During an internal display update memory cycle, the state of this pin is determined by bit 12 of control register B. During a CAS-before-RAS refresh cycle, this output remains high.

| SIGNAL  | PIN | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ~CBLNK  | 4   | 0   | Active Low Composite Blank This output controls the display blanking to a monitor. ~CBLNK is driven low during both horizontal and vertical blanking times. The duration of both horizontal and vertical blank is programmable. Setting bit 0 of control register B to a zero will cause the entire screen to be blanked.                                                                                                                                                                                  |

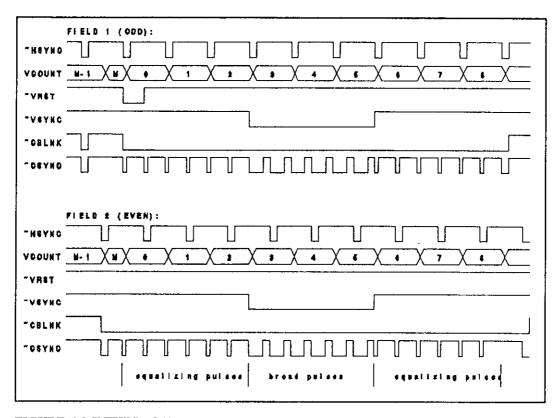

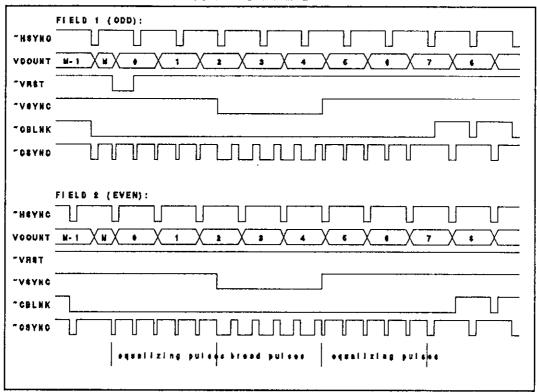

| ~CSYNC  | 5   | O   | Active Low Composite Sync In interlaced mode (control register B, bit 4 equals 1), this signal controls the vertical retrace of a monitor so that proper field alignment is obtained. Both American NTSC and European PAL standards are supported. The user can choose the standard by programming bit 3 of control register B to the appropriate value. When bit 4 of control register B is set to zero, the ISC is in NON-interlaced mode and the composite sync signal simply follows the HSYNC signal. |

| ~HSYNC  | 6   | 0   | Active Low Horizontal Sync  This signal is used to control the horizontal retrace of a monitor. The timing of this signal is user programmable.                                                                                                                                                                                                                                                                                                                                                            |

| ~VSYNC  | 7   | O   | Active Low Vertical Sync This signal is used to control the vertical retrace of a monitor with separate sync inputs. In interlaced mode, this signal will go low at the beginning of the Broad pulses of the composite sync signal. In NON-interlaced mode, this signal will go low at the same time that the internal vertical line counter is reset, at the end of a frame. In either case, the duration of this pulse is user programmable.                                                             |

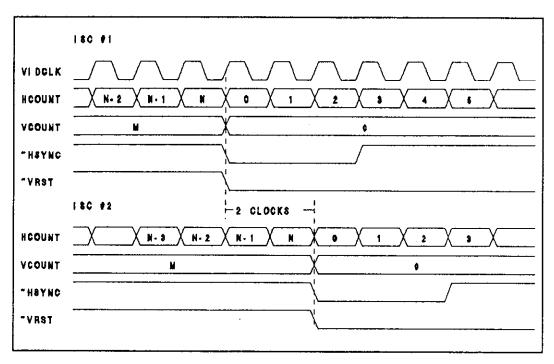

| ~VRST   | 8   | 0   | Active Low Vertical Reset This signal occurs once at the beginning of each frame. Its primary use is to frame sync one ISC to another.                                                                                                                                                                                                                                                                                                                                                                     |

| ~XHSYNC | 28  | I   | Active Low External Horizontal Sync This input is used to synchronize the horizontal timing of an ISC to an outside horizontal sync source. This input would normally be used with the external vertical reset input signal. Bit 2 of control register B determines whether the ISC generates HSYNC internally or uses this signal to slave to.                                                                                                                                                            |

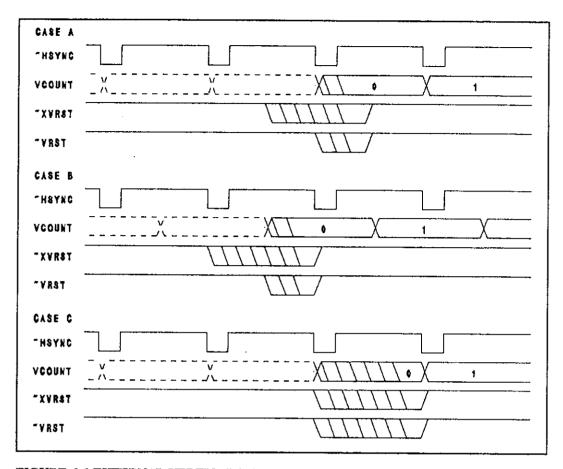

| ~XVRST  | 30  | I   | Active Low External Vertical Reset This signal is used to synchronize the vertical timing of an ISC to an outside frame sync signal. This signal must occur only once at the                                                                                                                                                                                                                                                                                                                               |

beginning of each frame. This signal would normally be used alone to genlock to an outside video source or together with the ~XHSYNC in a master/slave ISC configuration. Bit 1 of control register B determines whether the ISC generates vertical signals internally or uses this input signal to slave to.

| SIGNAL  | PIN               | I/O | DESCRIPTION                                                                                                                                                                      |

|---------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TE1,TE0 | 26,25             | I   | Internal Test Enable 1,0 These two test signals are used in the production of the ISC and are for internal use only. THESE TWO PINS MUST BE TIED TO GROUND FOR THE CHIP TO WORK. |

| TP0     | 21                | O   | Internal Test Point This test point is used in the production of the ISC and is for internal use only. THIS PIN MUST REMAIN UNCONNECTED.                                         |

| VDD     | 11,22,44<br>64    | +   | +5 volt supply                                                                                                                                                                   |

| VSS     | 10,23,29<br>43,63 | -   | Ground                                                                                                                                                                           |

# **ARCHITECTURE**

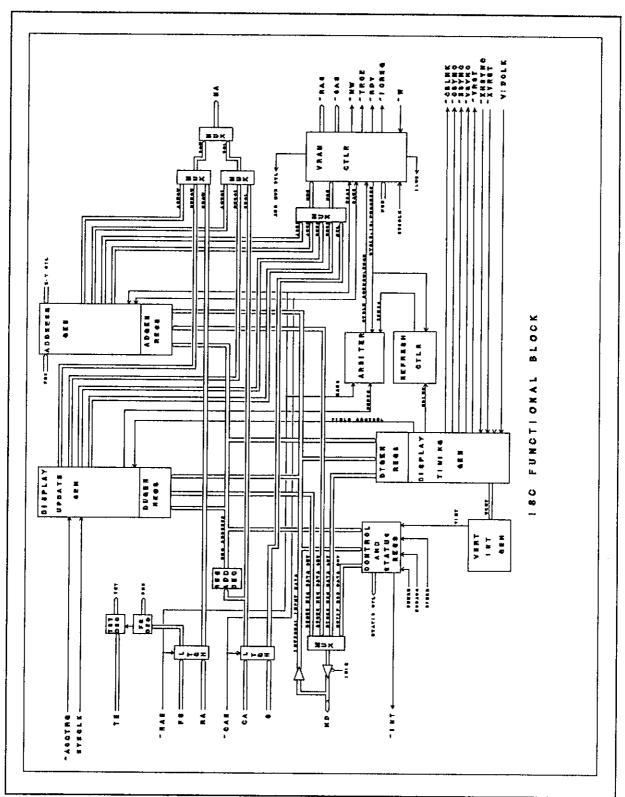

The Image System Controller consists of six functional blocks (Figure 3.1):

- Host Interface

- Control and Status Registers

- Address and Control Latches

- Arbiter

- Address Generator

- Address Registers

- VRAM Controller

- Refresh Controller

- Address Multiplexer

- Display Timing Generator

- Horizontal Timing Control

- Composite Sync Timing Control

- Vertical Timing Control

- Vertical Interrupt Control

- Display Update Generator

- Display Update Registers

#### 3.1 HOST INTERFACE

The host interface contains the two control registers, the status register, the address latches and the internal register address decoders.

Control registers A and B are 16 bit host programmable registers that dictate the ISC's mode of operation. Each register may be read from or written to by the host, See section 4. for detailed information.

The status register consists of four bits and is read only. After this register has been read from the host, the contents are automatically cleared. The four conditions that may set a bit in this register are: The end of an acquisition, a display update error, a refresh error or a vertical interrupt. An interrupt may be sent to the host on the ~INT pin by setting the appropriate interrupt enable bit in control register B.

There are two address latches. The first address latch latches RA9-RA0 and FS2-FS0 on the high-to-low transition of ~RAE. The second address latch latches CA9-CA0 and S1,S0 on the high-to-low transition of ~CAE.

## 3.2 ARBITER

The Arbiter determines whether a host initiated cycle, an internally generated display update cycle or an internally generated burst refresh cycle will be performed. Priority is granted as follows:

- Any cycle in progress

- A display update cycle (if enabled)

- A burst refresh cycle (if enabled)

- A host initiated cycle

When an internal cycle is in progress, a host initiated cycle is held-off with the ~RDY pin remaining

high until the internal cycle(s) is complete. The host may observe the request for an internal cycle by monitoring the ~ICREQ pin. This Internal Cycle Request pin will go low when the ISC would like to perform a display update or burst refresh and will remain low until the request has been serviced.

## 3.3 ADDRESS GENERATOR

The address generator consists of the X-Y ROW address register, The X-Y COL address register and the block address register. The address generator provides X-Y addressing for use in designs that may be register mapped, block mode direct addressing for use in designs that have an address space limited to 64K and fast page mode column addressing that is synchronized with the display update address generator for real-time processing or limited acquisition into DRAM. The address generator provides address linearization called Reformat. Address Reformat is necessary when interlaced data has been acquired into VRAM through SAM in a "bank-by-four" memory architecture. Reformat may be invoked by setting bit 14 of control register A.

X-Y addressing allows the user to move through DRAM using only a four bit code presented at CA3-CA0. The independent ROW and COL functions available are NOP, INCrement, DECrement and CLeaR. The user may step through memory by increments of more than one by programming the X-Y ROW STEPSIZE and X-Y COL STEPSIZE bits of control register A (bits 5 - 0). The ROW and COL STEPSIZE adjustments are also useful in mapping video lines and pixels to memory rows and columns for many different memory architectures. Fast page mode may be used with X-Y addressing by the user toggling ~CAE to create Column Address Strobes and holding ~RAE low for the duration of the cycle. The user must insure however, that a row boundary not be exceeded for the duration of the ~RAE cycle. NOTE that since the ROW portion of the X-Y address register is updated on the rising edge of ~RAE and the COL portion is updated on the rising edge of ~CAE, the two rising edges ~RAE and ~CAE must occur within the same SYSCLK cycle to insure that the ROW address adder recognizes a carry out from the COL address adder.

The Block Address Register (BAR) is a user programmable register that allows the user to directly address memory in 64K portions at a time. The BAR contains the two MSB's each of the row and column address registers and the two bits each that make up the row selects (RS1-RS0) and the column selects (CS1-CS0). NOTE that the contents of this register may be altered after an X-Y addressing operation. NOTE also that register values RA9 and CA9 are static and will not change with an X-Y address cycle.

When programmed for real-time mode, the address generator automatically creates the column portion of the DRAM address with the row portion of the address coming from the display update generator. The address generator is automatically CLEARED each time a display update is performed, thus resetting the pixel count to the beginning of a line. The column address is incremented each time ~CAE is toggled high. A gated version of the pixel clock may be used for ~CAE in this mode. The length of the cycle is determined by ~RAE and a delayed version of ~CBLNK may be used to create ~RAE. The direction of data to DRAM is determined by the ~W pin. In this mode, the system clock to the ISC must be replaced with the pixel clock.

## 3.4 VRAM CONTROLLER

The VRAM controller has no programmable registers but contains the address multiplexers, the burst refresh controller and the VRAM signal timing generator.

The address multiplexer provides the VRAM/DRAM array with row and column addresses at the proper time. Its input comes from the row, column and select pins, the X-Y address generator and the display update generator.

Figure 3.1 ISC Internal Architecture Block Diagram

The burst refresh controller initiates a burst of CAS-before-RAS refresh cycles at the beginning of composite blank by sending a refresh cycle request to the arbiter. After the arbiter acknowledges the refresh request, the burst refresh counter counts the number of refresh cycles until the programmed refresh burst length is reached (control register A, bits 8 and 9). When the beginning of the last refresh in a burst is reached, the refresh controller takes away the refresh request.

The VRAM signal timing generator creates the following VRAM/DRAM signals at the proper time: ~RAS(3-0), ~CAS(3-0), ~TROE and ~MW. The internal signals "Cycle-In-Progress" (CYIP) and "Busy" are also created by this circuit. The CYIP signal lets the arbiter know when a memory cycle is in progress. The Busy signal controls the external ~RDY signal and its duration is dependent on the value of the wait state limit of control register A, bits 7 and 6.

#### 3.5 DISPLAY TIMING GENERATOR

The Display Timing Generator consists of the Horizontal timing control, Composite Sync timing control, Vertical timing control and the Vertical interrupt control.

The Horizontal timing generator creates the Horizontal Sync signal and the Horizontal Blank portion of the Composite Blank signal. The Horizontal control consists of the following registers:

- Horizontal Total Latch

- Horizontal End Sync Latch

- Horizontal Start Blank Latch

- Horizontal End Blank Latch

- Horizontal Counter

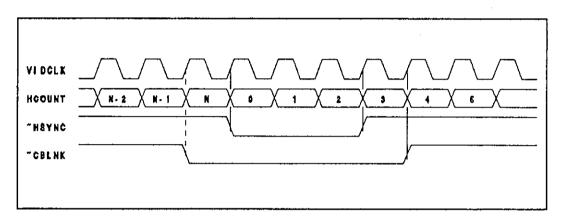

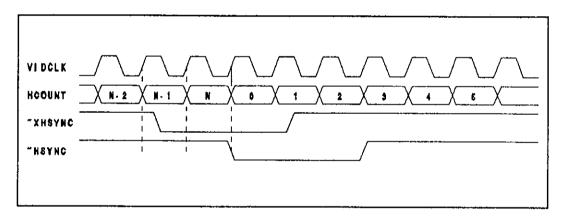

The Horizontal latches are user programmable and may also be read by the host. The Horizontal counter is read only. Reading the Horizontal counter is of little use since its value changes often and is asynchronous to the system. Its read-back use is mainly for manufacturing test. The first two Horizontal latches determine the scan line length and horizontal sync duration respectively. The second two latches determine the beginning and end of horizontal blank respectively. The Horizontal counter increments its value on every rising edge of VIDCLK and resets the clock cycle after HTOTAL is reached. The Horizontal Timing Controller also provides mid-line information to the Vertical Timing Generator for interlaced display and synchronizes the Horizontal timing signals to an external Horizontal sync signal.

The Composite timing controller creates the Composite Sync signal. The Composite Sync controller consists of the composite sync counter, the pulse width extraction circuit and the beginning of vertical count decoder. The composite sync counter counts out the equalizing and broad pulse widths of composite sync. This counter is read only to the host and its read-back capabilities are mainly intended for manufacturing test. The pulse width extraction circuit contains an arithmetic unit that automatically calculates the equalizing and broad pulse widths from the values in the HTOTAL and HENDSYNC latches. The beginning of vertical count decoder determines when to begin and end the equalizing and broad pulses.

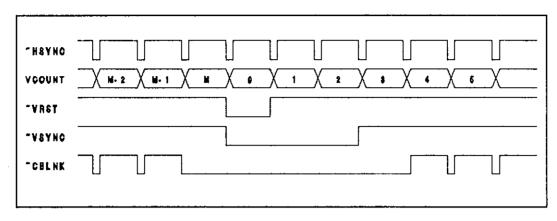

The Vertical timing generator creates the vertical reset signal, vertical Sync signal and the Vertical Blank portion of the Composite Blank signal. The Vertical control consists of the following registers:

- Vertical Total Latch

- Vertical End Sync Latch

- Vertical Start Blank Latch

- Vertical End Blank Latch

- Vertical Counter

The Vertical latches are user programmable and may also be read by the host. The Vertical total latch determine the number of scan lines per field in interlaced mode and the number of lines per frame in non-interlaced mode. The Vertical end sync latch determines which line Vertical sync will end. The vertical start and end blank latches determine where vertical blank will start and end. The start and end values may be set equal to each other in which case, vertical start blank will determine the start of display updates but ~CBLNK will contain NO vertical blanks. The Vertical counter counts the number of half lines in interlaced mode and the number of full lines in non-interlaced mode. This counter is read only by the host. Reading this counter may be useful but keep in mind that this counter runs asynchronous to SYSCLK and may need to be read several times in succession to guarantee the correct return value. The Vertical timing controller also synchronizes the Vertical timing signals to an external Vertical reset pulse.

The Vertical interrupt controller sets the vertical interrupt bit in the status register when the vertical counter reaches the line number value programmed into the Vertical interrupt latch. This latch is host programmable as well as readable by the host. NOTE that if the Vertical interrupt register is programmed with the value in the Vertical total register in interlaced mode, a Vertical interrupt will occur only once a FRAME at Vertical reset time.

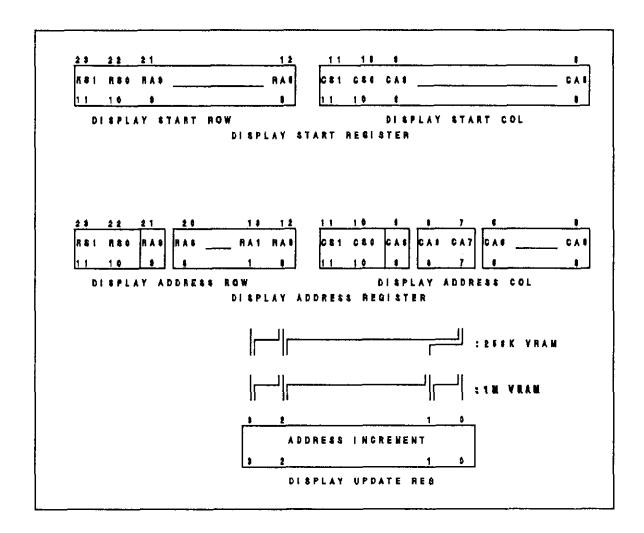

#### 3.6 DISPLAY UPDATE GENERATOR

The display update generator (DUGEN) is responsible for automatically creating memory read transfers in order to update a monitor with video information or automatically creating memory write transfers in order to acquire an image into video memory. The display update generator also contains the auto-acquire circuitry for host independent frame acquisitions. When the ~ACQTRG pin is toggled low, the auto-acquire state machine waits for the beginning of a new frame, allows the DUGEN to acquire/display that frame, disables the DUGEN and sets the end-acquire bit in the status register. The ~ACQTRG pin must remain low for continuous display to a monitor. The DUGEN may also be shut off by setting bit 13 of control register B. When the DUGEN is turned off in this manner, display updates immediately terminate and the DUGEN remains in its current state. The DUGEN may be programmed for display or acquire by programming bit 12 of control register B with the correct value. Display updates may be programmed to occur after every display line, every other, every fourth or every eight display line by programming the Line Count Limit bits 8 and 9 of control register B with the correct value. One of four each of the row and column address strobes may be selected by the display update address register (DAR) or all four of each of the row and/or column strobes may be selected by programming the display update RAS/CAS OVerride bits 10 and 11 of control register B. NOTE that the row and column select bits of the DAR as well as row and column address bits 9 of the DAR are static i.e. not part of the display update address generation. The DUGEN provides address linearization called Reformat. Display update address reformat is necessary when interlaced data has been acquired into VRAM through SAM in a "bank-by-four" memory architecture and is to be displayed NON-interlaced. Display update reformat may be invoked by setting bit 14 of control register B.

The DUGEN creates updates differently for acquire vs. display. At the beginning of an acquire, the DUGEN updates the DAR at vertical start blank of a new frame but does not perform a write transform cycle. After the end of vertical blank and at the beginning of each horizontal blank time determined by the line count limit, the DUGEN performs a write transfer cycle (after the arbiter acknowledges the internal display update request) followed by DAR update. At the beginning of vertical blank of the end of the frame, the DUGEN completes one last write transfer cycle without a DAR update. The case for display is similar but performs both a DAR update and a read transfer cycle (in that order) at the beginning of a frame and for each successive line count limit reached.

# The DUGEN contains three host accessible registers:

DSR- The twenty four bit Display Start Register consists of a twelve bit ROW address portion and a twelve bit COL address portion. This register determines where in memory the displayed (acquired) image will start. Adjusting the ROW portion of this register allows the user to SCROLL the image. Adjusting the COL portion of this register allows the user to PAN the image.

DAR- The twenty four bit Display Address Register is loaded with the contents of the DSR at the beginning of a frame. After each successive Line Count Limit has been reached, the contents of the Display Update Register (DUR) is added to the DAR. If the display is interlaced, one half of the value in the DUR is added to the DSR and the sum is placed in the DAR at the beginning of the second field.

DUR- The four bit Display Update Register determines the display update increment size and is intended to be programmed with the values of 1, 2, 4 or 8.

# 4. PROGRAMMABLE REGISTERS

This section describes the use of the ISC's programmable registers. The ISC contains eighteen programmable registers, one read only status register and three read only counters. The length of these registers vary in size from four to sixteen bits and are all host accessible through an eight bit data path a byte at a time.

The host processor accesses these registers via the internal register read/write cycles. These cycles are designed to look very much like memory cycles to the host. An internal register access is not allowed when the ISC is busy with an internally generated memory cycle. A function select code of 0 or 2 along with ~RAE going low starts an internal register access. The ~W signal determines the direction of the access and column address input pins 0 through 5 determine the register address. Column address bit 0 determines whether the high or low byte of the register is accessed. The input signal ~CAE latches the register address. During a register write cycle, register data is accepted on Host Data (HD) pins 0 through 7. Since there is no data latch, setup and hold times must be observed.

In the following register descriptions, the following conventions are observed: The LSB of a register is the right most bit and conversely, the MSB of a register is the left most bit. Active bits in a register are represented with a capital 'A' and bits not implemented in a register are represented with a capital 'X'.

| INPUT PIN VALUE |          |          | REGISTER NAME            |

|-----------------|----------|----------|--------------------------|

| CCCCC           | UPPER    | LOWER    |                          |

| AAAA            | BYTE     | BYTE     |                          |

| 5 4 3 2 1       | CAO=1    | CAO=0    |                          |

| 00000           | XXXXAAAA | AAAAAAA  | HORIZONTAL TOTAL         |

| 00001           | XXXXAAAA | AAAAAAA  | HORIZONTAL END SYNC      |

| 00010           | XXXXAAAA | AAAAAAA  | HORIZONTAL START BLANK   |

| 00011           | XXXXAAAA | AAAAAAA  | HORIZONTAL END BLANK     |

| 00100           | XXXXAAAA | AAAAAAA  | VERTICAL TOTAL           |

| 00101           | XXXXAAAA | AAAAAAA  | VERTICAL END SYNC        |

| 0 0 1 1 0       | XXXXAAAA | AAAAAAA  | VERTICAL START BLANK     |

| 0 0 1 1 1       | XXXXAAAA | AAAAAAA  | VERTICAL END BLANK       |

| 0 1 0 0 0       | XXXXAAAA | AAAAAAA  | HORIZONTAL COUNTER *     |

| 0 1 0 0 1       | XXXXAAAA | AAAAAAA  | CSYNC COUNTER *          |

| 0 1 0 1 0       | XXXXAAAA | AAAAAAA  | VERTICAL COUNTER *       |

| 0 1 0 1 1       | XXXXAAAA | AAAAAAA  | VERTICAL INTERUPT        |

| 0 1 1 0 0       | AAAAAAA  | AAAAAAA  | CONTROL REGISTER A       |

| 0 1 1 0 1       | AAAAAAA  | AAAAAAA  | CONTROL REGISTER B       |

| 0 1 1 1 0       | AAAAAAA  | AAAAAAA  | X-Y ADDRESS REGISTER     |

| 0 1 1 1 1       | XXXXXXX  | AAAAAAA  | BLOCK ADDRESS REGISTER   |

| 10000           | XXXXAAAA | AAAAAAA  | DISPLAY START REG -COL   |

| 10001           | XXXXAAAA | AAAAAAA  | DISPLAY START REG -ROW   |

| 10010           | XXXXAAAA | ΑΑΑΑΑΑΑ  | DISPLAY ADDRESS REG -COL |

| 1 0 0 1 1       | XXXXAAAA | AAAAAAA  | DISPLAY ADDRESS REG -ROW |

| 10100           | XXXXXXXX | XXXXAAAA | DISPLAY UPDATE REGISTER  |

| 1 0 1 0 1       | XXXXXXXX | XXXXAAAA | STATUS REGISTER          |

TABLE 4-1 REGISTER ADDRESS MAP

<sup>\* =</sup> READ ONLY REGISTER

# 4.1 REGISTER VALUES AFTER RESET

At reset, the internal registers are set to values indicated in Table 4-2.

| REGISTER NAME            | VALUE AFTER RESET   |

|--------------------------|---------------------|

| HORIZONTAL TOTAL         | XXXX 0010 0000 0000 |

| HORIZONTAL END SYNC      | XXXX 0000 1000 0000 |

| HORIZONTAL START BLANK   | XXXX 0010 0000 0000 |

| HORIZONTAL END BLANK     | XXXX 0000 1000 0000 |

| VERTICAL TOTAL           | XXXX 0010 0000 0000 |

| VERTICAL END SYNC        | XXXX 0000 1000 0000 |

| VERTICAL START BLANK     | XXXX 0010 0000 0000 |

| VERTICAL END BLANK       | XXXX 0000 1000 0000 |

| HORIZONTAL COUNTER       | XXXX 0000 0000 0000 |

| CSYNC COUNTER            | xxxx 0000 0000 0000 |

| VERTICAL COUNTER         | XXXX 0000 0000 0000 |

| VERTICAL INTERRUPT       | XXXX 0000 1000 0000 |

| CONTROL REGISTER A       | 0000 0011 0000 0000 |

| CONTROL REGISTER B       | 0000 0011 0000 0000 |

| X-Y ADDRESS REGISTER     | 0000 0000 0000 0000 |

| BLOCK ADDRESS REGISTER   | XXXX XXXX 0000 0000 |

| DISPLAY START REG -COL   | XXXX 0000 0000 0000 |

| DISPLAY START REG -ROW   | XXXX 0000 0000 0000 |

| DISPLAY ADDRESS REG -COL | XXXX 0000 0000 0000 |

| DISPLAY ADDRESS REG -ROW | XXXX 0000 0000 0000 |

| DISPLAY UPDATE REGISTER  | XXXX XXXX XXXX 0000 |

| STATUS REGISTER          | XXXX XXXX XXXX 0000 |

TABLE 4-2 INTERNAL REGISTER VALUES AFTER RESET

Note that the default refresh burst length is eight, the default number of wait states is zero, the default line count limit is eight and the default memory size is 256K. Also, the screen is disabled by default.

## 4.2 HOST INTERFACE REGISTERS

The ISC contains two, host programmable, sixteen bit control registers that determine the behavior of display timing, display update addressing, X-Y addressing, host interface signals, memory control and interface signals, DRAM refresh and interrupt control. There is also a four bit read-only status register that the host may access.

## 4.2.1 CONTROL REGISTER A

| B15         | B14               | B13          | B12          | B11               | B10               | B9-B8                    | B7-B6                  | B5-B3               | B2-B0               |

|-------------|-------------------|--------------|--------------|-------------------|-------------------|--------------------------|------------------------|---------------------|---------------------|

| MEM<br>SIZE | AG<br>RE-<br>FRMT | XRAS<br>MODE | XCAS<br>MODE | AG<br>RAS<br>OVRD | AG<br>CAS<br>OVRD | REFRSH<br>BURST<br>LNGTH | WAIT<br>STATE<br>LIMIT | X-Y<br>ROW<br>STPSZ | X-Y<br>COL<br>STPSZ |

FIGURE 4-1

# BITS FUNCTION

#### B2-B0 X-Y COLUMN STEP SIZE

These three bits control how much the column address counter will be incremented or decremented during X-Y addressing mode. The column address counter is architected such that the two LSBs of the column address register control the four column address strobes. With bit B2=0, bits B1-B0 set the column address register step size to 1, 2, 4 or 8. With bit B2=1, bits B1-B0 set the column address register step size to 4, 8, 16 or 32 (ie the column address strobes will not be affected).

#### B5-B3 X-Y ROW STEP SIZE

These three bits control how much the row address counter will be incremented or decremented during X-Y addressing mode. The row address counter is architected such that the two LSBs of the row address register control the four row address strobes. With bit B5=0, bits B4-B3 set the row address register step size to 1, 2, 4 or 8. With bit B5=1, bits B4-B3 set the row address register step size to 4, 8, 16 or 32 (ie the row address strobes will not be affected).

| B2 | B1 | 80 | STARTING ADDRESS BIT AFFECTED | B5 | B4 | В3  | STARTING ADDRESS BIT AFFECTED |

|----|----|----|-------------------------------|----|----|-----|-------------------------------|

| 0  | 0  | 0  | CSO -COL SEL BIT O            | 0  | 0  | 0   | RSO -ROW SEL BIT O            |

| 0  | 0  | 1  | CS1 -COL SEL BIT 1            | 0  | 0  | 1   | RS1 -ROW SEL BIT 1            |

| 0  | 1  | 0  | CAO -COL ADD BIT 0            | 0  | 1  | . 0 | RAO -ROW ADD BIT O            |

| 0  | 1  | 1  | CA1 -COL ADD BIT 1            | 0  | 1  | 1   | RA1 -ROW ADD BIT 1            |

| 1  | 0  | 0  | CAO -COL ADD BIT O            | 1  | 0  | 0   | CA8/7 -COL ADD MSB            |

| 1  | 0  | 1  | CA1 -COL ADD BIT 1            | 1  | 0  | 1   | RAO -ROW ADD BIT O            |

| 1  | 1  | 0  | CA2 -COL ADD BIT 2            | 1  | 1  | 0   | RA1 -ROW ADD BIT 1            |

| 1  | 1  | 1  | CA3 -COL ADD BIT 3            | 1  | 1  | 1   | RA2 -ROW ADD BIT 2            |

TABLE 4-3 STEPSIZE CONTROL

# **B7-B6 WAIT STATE LIMIT**

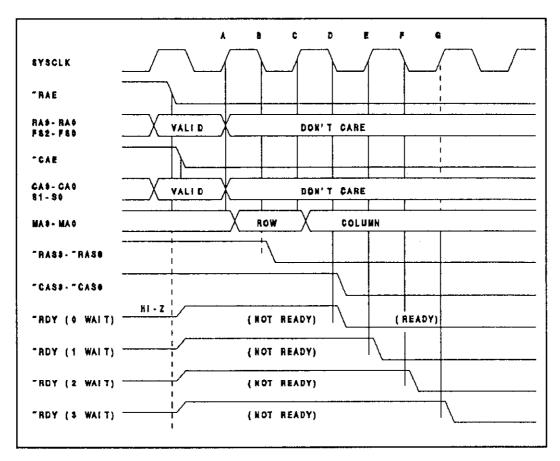

These two bits determine the number of wait states inserted into host initiated cycles. A wait state is a delay of one-half of a SYSCLK period inserted into a cycle to increase its duration. Zero through three wait states are available.

| В7 | В6 | # OF WAIT STATES |

|----|----|------------------|

| 0  | 0  | O WAIT STATES    |

| 0  | 1  | 1 WAIT STATE     |

| 1  | 0  | 2 WAIT STATES    |

| 1  | 1  | 3 WAIT STATES    |

TABLE 4-4 WAIT STATE LIMIT

# B9-B8 REFRESH BURST LENGTH

Bits B9-B8 contain a two bit encoded number specifying the number of DRAM refresh cycles to be generated per horizontal scan line. The number of refresh cycles per scan line allowed are 0, 2, 4 or 8.

| B9 | 88 | REFRESH BURST LENGTH |

|----|----|----------------------|

| 0  | 0  | NO REFRESH CYCLES    |

| 0  | 1  | 2 REFRESH CYCLES     |

| 1  | 0  | 4 REFRESH CYCLES     |

| 1  | 1  | 8 REFRESH CYCLES     |

TABLE 4-5 REFRESH BURST LENGTH

#### B10 ADDRESS GENERATOR CAS OVERRIDE

When this bit is set to a one, all four ~CAS lines are forced to their active-low level during the following types of cycles: HOST DIRECT, X-Y INDIRECT, REAL-TIME and HOST INITIATED SHIFT-REGISTER TRANSFER.

\* WARNING: Depending on the memory architecture, CAS override during a READ cycle could result in data collision.

## B11 ADDRESS GENERATOR RAS OVERRIDE

When this bit is set to a one, all four ~RAS lines are forced to their active-low level during the following types of cycles: HOST DIRECT, X-Y INDIRECT, REAL-TIME and HOST INITIATED SHIFT-REGISTER TRANSFER.

\* WARNING: Depending on the memory architecture, RAS override during a READ cycle could result in data collision.

# B12 EXTERNAL CAS MODE

When this bit is set to a one, the input value at pins S1 and S0 replace the two-bit value at locations B1-B0 of the BLOCK address register and determine which of the four ~CAS outputs is driven low during a non block-mode host-direct or shift-register transfer cycle.

# B13 EXTERNAL RAS MODE

When this bit is set to a one, the input value at pins S1 and S0 replace the two-bit value at locations B5-B4 of the BLOCK address register and determine which of the four ~RAS outputs is driven low during a non block-mode host-direct or shift-register transfer cycle.

\* NOTE: S1-S0 are latched on ~CAE

#### B14 ADDRESS GENERATOR REFORMAT

When this bit is set to one, an interlaced image that was captured as two video lines per memory row will appear to be in non-interlaced format during host initiated memory cycles. REFORMAT is memory size sensitive so B15 of control register A must be set to the correct value. REFORMAT works by swapping ROW bit 0 with COL bit 7 using 256K VRAM or with COL bit 8 using 1M VRAM.

\* NOTE: Be careful when using fast page mode with REFORMAT!

#### B15 MEMORY SIZE

This bit sets the memory size for correct display updates and reformat control. B15=0 sets the memory size for 256K VRAM, B15=1 sets the memory size for 1M VRAM.

#### CONTROL REGISTER B

| B15 | B14    | B13         | B12 | B11               | B10 | B9-B8 | B7                      | B6  | B5  | В4             | В3 | B2 | B1    | ВО               |

|-----|--------|-------------|-----|-------------------|-----|-------|-------------------------|-----|-----|----------------|----|----|-------|------------------|

| 11  | REFRMT | DU<br>INHBT | DIR | DU<br>Ras<br>Ovrd |     | COUNT | ENDACQ<br>INT<br>ENABLE | INT | INT | INTL<br>ENABLE | TD |    | VSYNC | SCREEN<br>ENABLE |

#### FIGURE 4-2

#### BITS FUNCTION

#### B0 SCREEN ENABLE

When this bit is zero, the ~CBLANK pin is driven low continuously. When B0 is set to one, the ~CBLANK pin is driven low only during horizontal and vertical blanking times.

#### B1 EXTERNAL VSYNC ENABLE

When B1=0, the ISC generates the vertical sync and vertical reset signals internally (~VSYNC and ~VRST pins respectively) and ignores any signal present at the ~XVRST input pin. When B1=1, the external VRST mode is enabled and the ISC locks onto the externally-generated vertical reset signal (~XVRST pin). The signals at the ~VSYNC and ~VRST output pins in external VRST mode are essentially delayed versions of there externally generated counterparts except for the duration of VSYNC which is still dependent on the programmed value of the VESYNC register.

\* NOTE: When external VRST is enabled, serrated pulses are not generated and ~CSYNC simply becomes another ~HSYNC.

# B2 EXTERNAL HSYNC ENABLE

When B2=0, the ISC generates the horizontal sync signal internally (~HSYNC pin) and ignores any signal present at the ~XHSYNC input pin. When B2=1 the external HSYNC mode is enabled and the ISC locks on to the externally-generated horizontal sync signal (~XHSYNC pin). The signal at the ~HSYNC output pin in external HSYNC mode is essentially a delayed version of its externally generated counterpart except for the duration of HSYNC which is still dependent on the programmed value of the HESYNC register.

# B3 VIDEO STANDARD

When B3=0, the composite sync signal follows the NTSC TV standard and when B3=1, the composite sync signal follows the PAL TV standard, if interlaced is enabled.

# **B4** INTERLACE ENABLE

When B4=0, the ISC is configured for non-interlaced scan and ~CSYNC becomes another ~HSYNC. When B4=1, the ISC is configured for interlaced scan and composite sync is generated according to the

TV standard selected.

#### B5 VERTICAL INTERRUPT ENABLE

When B5=0, the setting of the vertical interrupt flag in the status register does not cause an interupt to the host processor. When B5=1, the interrupt request is enabled.

## B6 ERROR INTERRUPT ENABLE

When B6=0, the setting of an error interrupt flag in the status register does not cause an interrupt to the host processor. When B6=1, the setting of either an display or refresh error interrupt flag causes an interrupt request.

# B7 END-ACQUIRE INTERRUPT ENABLE

When B7=0, the setting of the end-of-acquire interrupt flag in the status register does not cause an interrupt to the host processor. When B7=1, the interrupt is enabled.

## **B9-B8 LINE COUNT LIMIT**

The Line Count Limit determines the number of horizontal lines that are counted by the scan line counter before a display update cycle is granted. Possible limits are: every line, every other line, every forth line and every eighth line. The scan line counter repeatedly counts from zero to the scan line limit, incrementing at the beginning of every COMPOSITE blank interval. The scan line counter is reset at the beginning of every vertical blank period and remains inactive during vertical blank. When the scan line limit is reached and an internal display update is requested. When the arbiter grants a display update acknowledge, the display update request is removed and the scan line counter is reset. The display address register is updated BEFORE the display update cycle in DISPLAY mode and AFTER the display update cycle in ACQUIRE mode. When the line scan limit is set to zero, display updates occur on every scan line.

| B9 | В8 | LINE COUNT LIMIT      |

|----|----|-----------------------|

|    |    | CINC COONT CIPIT      |

| 0  | 0  | AFTER EACH SCAN LINE  |

| 0  | 1  | EVERY OTHER SCAN LINE |

| 1  | o  | EVERY 4TH SCAN LINE   |

| 1  | 1  | EVERY 8TH SCAN LINE   |

TABLE 4-6 DISPLAY UPDATE CONTROL

# B10 DISPLAY UPDATE CAS OVERRIDE

When B10=1, all four COL address strobe pins are active during a display update cycle. When B10=0, only one of four strobes is active during a display update cycle and the active strobe is selected by the value contained in bits B11-B10 of the display address register.

#### B11 DISPLAY UPDATE RAS OVERRIDE

When B11=1, all four ROW address strobe pins are active during a display update cycle. When B11=0, only one of four strobes is active during a display update cycle and the active strobe is selected by the value contained in bits B23-B22 of the display address register.

# B12 DISPLAY UPDATE DIRECTION

When B12=0, the ISC is in Display mode and display update cycles transfer data from the memory cell array to the shift register. When B12=1, the ISC is in Acquire mode and "display" update cycles transfer data from the shift register to the memory cell array.

#### B13 DISPLAY UPDATE INHIBIT

When this bit is set to a one, display update cycles are inhibited.

## B14 DISPLAY UPDATE REFORMAT

When this bit is set to one, an interlaced image that was captured as two video lines per memory row will be addressed in non-interlaced format during display update cycles. REFORMAT is memory size sensitive so B15 of control register A must be set to the correct value. REFORMAT works by swapping ROW bit 0 with COL bit 7 using 256K VRAM or with COL bit 8 using 1M VRAM.

## B15 BLOCK MODE

Block Mode addressing is available when the ISC is used in systems with limited address space. By setting B15=1 and programming the block address register with the two MSBs of each of the ROW and COLUMN addresses and the two bits each of the ROW and COLUMN select bits, memory can be accessed in 64K blocks using the eight LSBs of each of the ROW and COLUMN address pins.

\* NOTE: The Block Address register is part of the ROW and COLUMN

address registers in the address generator and is subject to change value during X-Y addressing mode.

#### STATUS REGISTER

| B3 | B2               | B1               | 80                    |

|----|------------------|------------------|-----------------------|

|    | REFRESH<br>Error | DISPLAY<br>ERROR | VERTICAL<br>INTERRUPT |

FIGURE 4-3

The status register contains four bits, each representing a particular internal condition. When one of the bits is set and the corresponding interrupt-enable bit in Control Register B is set to one, the ISC sends an interrupt request to the host processor by driving the ~INT pin to its active low level. The status register can be read, but not written to, by the host processor. A read of the status register by the host will cause all of the bits to be reset to zero, thereby clearing the interupt request.

#### BITS FUNCTION

# B0 VERTICAL INTERRUPT

A one in this bit indicates that the vertical counter has reached the value programmed in the Vertical Interrupt Register.

# B1 DISPLAY ERROR

A one in this bit indicates that a display update cycle was unable to be performed during the composite blanking period.

#### B2 REFRESH ERROR

A one in this bit indicates that the ISC was unable to execute the designated number of cycles before the end of the horizontal blanking period.

# B3 END ACQUIRE INTERRUPT

A one in this bit indicates the end of a frame(s) of acquiring (or displaying) data if the ~ACQTRG pin was triggered.

# 4.3 ACQUIRE/DISPLAY CONTROL REGISTERS

#### 4.3.1 DISPLAY ADDRESS REGISTER

The twenty four bit display address register (DAR) consists of a twelve bit ROW portion and a twelve bit COL address portion. This register contains the address to be output during the next automatic display update cycle. In general, this register is updated once at the beginning of each vertical blank and at the beginning of a horizontal blank period when the line scan limit has been reached. During a frame ACQUIRE, the DAR is updated once at the beginning of vertical blank at the beginning of a frame then, a memory transfer cycle with a DAR update occur at every scheduled update time. For the last update of a frame at vertical blank time, only a memory transfer occurs to acquire the very last line of data. During a frame DISPLAY, the DAR is updated then a memory transfer cycle occurs at the beginning of a frame at vertical blank time and at every scheduled display update cycle. No update is performed for the last vertical blank of a single frame. The DAR also provides the ROW portion of the address for REAL-TIME processing mode. Display address bits RA9, CA9, RS1, RS0, CS1, CS0 and CA0 through CA8 of are not part of the normal update cycles. These bits merely mimic what's in the display start register at these locations.

The host may access this register in two ways. One is by performing successive read cycles to insure the integrity of the returned data. The other is by using the vertical interrupt register to get you to the end of a line, then wait through the horizontal blank time before performing an access.

#### 4.3.2 DISPLAY START REGISTER

The twenty four display start register (DSR) consists of a twelve bit ROW address portion and a twelve bit COL address portion. This register determines where in memory the displayed (acquired) image will start. The contents of this register are loaded into the DAR at the beginning of VERTICAL blank when in non-interlaced mode and at the beginning of VERTICAL blank at the beginning of a frame when in interlaced mode. Adjusting the ROW portion of this register allows the user to SCROLL the image. Adjusting the COL portion of this register allows the user to PAN the image. This register may be both written to and read from by the host.

#### 4.3.3 DISPLAY UPDATE REGISTER

The four bit display update register (DUR) contains the value by which the display address is incremented. Valid increment values are 0, 1, 2, 4 and 8. This register may be written to or read by the host.

## NON-INTERLACED MODE OPERATION

During a scheduled DAR update at the beginning of HORIZONTAL blank, the contents of the display update register (DUR) are added to the display address register (DAR).

## INTERLACED MODE OF OPERATION

During a scheduled DAR update at the beginning of HORIZONTAL blank, the contents of the display update register (DUR) are added to the display address register (DAR). At the start of VERTICAL blank preceding an EVEN field (ie mid-frame), one-half the value contained in the DUR is added with the value from the DSR and the result stored in the DAR. This allows the offset needed to display/acquire two video fields.

#### **4.4 VIDEO TIMING REGISTERS**

The Display Timing Generator (DTGEN) creates all of the signals necessary to operate a CRT display in either non-interlaced or interlaced NTSC or PAL standards. In addition, the DTGEN can sync to an external video timing source such as external video or another ISC. When synchronized to external VRST, the DTGEN provides HSYNC to be phase lock looped to an external HSYNC to create a stable video clock for a tightly coupled system. The DTGEN also creates a vertical interupt signal at a user programmed interval.

# NAME DESCRIPTION

HCNTR The horizontal counter is a 12 bit counter that counts video clocks until reset by the horizontal total strobe that is internally generated when the HCNTR reaches the value stored in the horizontal total register. The HCNTR is used in the creation of HSYNC, HBLANK and the internally generated half line strobe.

CCNTR The composite counter is a 12 bit counter that counts video clocks until reset by either the horizontal total strobe or the half line strobe and is used in the creation of the equalizing and broad pulses for composite sync.

VCNTR

The vertical counter is a 13 bit counter that counts horizontal lines in non-interlaced mode and half lines in interlaced mode until reset by the vertical total strobe that is internally generated when the VCNTR reaches the value programmed in the VTOTAL register. It is used in the creation of VSYNC, VBLANK and CSYNC.

HTOTAL The horizontal total register is a 12 bit user programmable register and determines the length of a horizontal line (in video clock units).

HESYNC The horizontal end sync register is a 12 bit user programmable register and determines the width of the horizontal sync pulse (in video clock units).

HSBLANK The horizontal start blank register is a 12 bit user programmable register and determines where in a line horizontal blank begins (in video clock units).

HEBLANK The horizontal end blank register is a 12 bit user programmable register and determines the width of the horizontal blank pulse (in video clock units).

VTOTAL The vertical total register is a 12 bit user programmable register and determines the length of a field/frame (in horizontal lines).

VESYNC The vertical end sync register is a 12 bit user programmable register and determines the width of the vertical sync pulse (in horizontal lines).

VSBLANK The vertical start blank register is 12 bit user programmable register and determines where the vertical blank begins (in horizontal lines).

VEBLANK The vertical end blank register is a 12 bit user programmable register and determines the width of vertical blank (in horizontal lines).

VINT

The vertical interrupt register is a 12 bit user programmable register and determines where in a field/frame a vertical interrupt will occur (in horizontal lines). An interrupt will occur once a FRAME in non-interlaced mode and once a FIELD in interlaced mode with the exception of when the value in the VINT register is set equal to the value in the VTOTAL register. In this case, an interrupt will occur once each FRAME.

## 4.4.1 VIDEO TIMING RELATIONSHIPS TO DTGEN REGISTERS

# DTGEN REGISTERS

HTOTAL = [Horizontal line time / VCLK period]-1

HESYNC = [Horizontal sync time / VCLK period]-1

HSBLANK = HTOTAL-[Hfront porch / VCLK period]

HEBLANK = [(Hsync time + Hback porch) / VCLK period]-1

VTOTAL(non-interlaced) = #Hlines per frame-1

VTOTAL(interlaced) = [#Hlines per frame-1] / 2

VESYNC = Vsync width-1 (in # Hlines)

VSBLANK = VTOTAL-Vfront porch width (in #Hlines)

VEBLANK = Vsync width + Vback porch-1 (in #Hlines)

VINT = line # interrupt is to occur

\*NOTE: The following restrictions apply when programming the internal DTGEN registers for video use:

HTOTAL>HESYNC

HTOTAL = > HSBLANK

HTOTAL = > HEBLANK

HSBLANK <> HEBLANK

VTOTAL> VESYNC

VTOTAL = > VSBLANK (non-int)

VTOTAL = > VEBLANK

VTOTAL> VSBLANK (int)

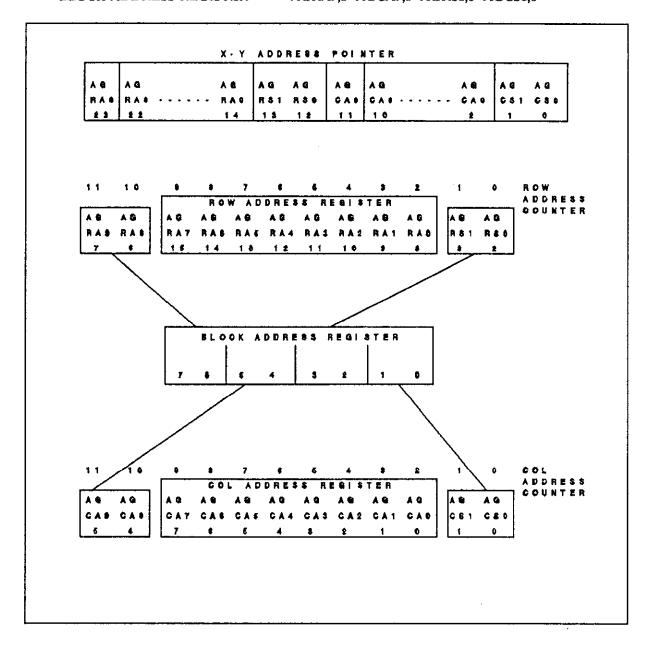

#### 4.5 ADDRESS GENERATOR

The X-Y addressing mode allows access to all of DRAM with only a four bit code. This is a very useful feature for systems that are register mapped or have limited memory address space. A memory read or write access that utilizes the contents of the X-Y address pointer for the memory address is called an X-Y indirect cycle.

The X-Y addressing mode is enabled with a Function Select code of one (FS2-FS0 = 001). The 4-bit adjustment code on input CA3 - CA0 during an X-Y indirect cycle determines the manner in which the contents of the ROW and COL address counters are updated following the completion of the X-Y indirect cycle, as indicated in Table 4-7. The X-Y adjustment code is latched on the falling edge of ~CAE. The COL address counter performs an address update on the rising edge of ~CAE and the ROW address counter performs an update on the rising edge of ~RAE. At the end of an X-Y indirect cycle, both ~CAE and ~RAE must go high within the same SYSCLK period. This is to insure that a COL-to-ROW carry is recognized if one had been generated. The X-Y adjustment size is determined by the ROW STEPSIZE (control register A, bits 5-3) and the COL STEPSIZE (control register A, bits 2-0) as in Table 4-3.

| CA3 | CA2 | CA1 | CAO | X-Y FUNC | CTION ADJUST |

|-----|-----|-----|-----|----------|--------------|

| 0   | 0   | 0   | 0   | NOP      | NOP          |

| ō   | ō   | ō   | 1   | +X       | NOP          |

| ō   | Ō   | 1   | ō   | -x       | NOP          |

| 0   | 0   | 1   | 1   | CLRX     | NOP          |

| 0   | 1   | 0   | 0   | NOP      | +Y           |

| 0   | 1   | 0   | 1   | +X       | +Y           |

| 0   | 1   | 1   | 0   | -x       | ÷Y           |

| 0   | 1   | 1   | 1   | CLRX     | +Y           |

| 1   | ٥   | 0   | 0   | NOP      | -Y           |

| 1   | 0   | 0   | 1   | +X       | - <b>Y</b>   |

| 1   | 0   | 1   | 0   | -x       | -Y           |

| 1   | 0   | 1   | 1   | CLRX     | -Y           |

| 1   | 1   | 0   | 0   | NOP      | CLRY         |

| 1   | 1   | 0   | 1   | +X       | CLRY         |

| 1   | 1   | 1   | 0   | -X       | CLRY         |

| 1   | 1   | 1   | 1   | CLRX     | CLRY         |

The address generator consists of a 24 bit address pointer which consists of a 12 bit ROW address counter and a 12 bit COLumn address counter. These counters are accessed by the host via 3, 8 bit register locations.

TABLE 4-7

- COL ADDRESS REGISTER

- ROW ADDRESS REGISTER

- BLOCK ADDRESS REGISTER

AGCA7 - AGCA0 AGRA7 - AGRA0 AGRA9,8 AGCA9,8 AGRS1,0 AGCS1,0

The X-Y address pointer is arranged such that the COL address counter creates the lower half of the pointer address and the ROW address counter creates the upper half of the pointer address. The column select bits make up the two LSB's of the COL address counter. The row select bits make up the two LSB's of the ROW address counter. Both ROW address bit 9 and COL address bit 9 are static and do not participate in the address count. These two bit are programmable, however, and are sent to Memory Address bit 9 during the appropriate RAS/CAS cycle times. The MSB of the COL address counter is either column address bit 7 (when the memory size bit is set to 0, control register A bit 15) or column address bit 8 (when the memory size bit is set to 1). When column bit 7 is the MSB of the COL address counter, then column address bit 8 becomes static

and does not participate in the address count. The MSB of the COL address counter carries over to the LSB of the ROW address counter. The ROW address counter carry-in position is determined by the MSB of ROW STEPSIZE (control register A, bit 5). When the ROW STEPSIZE MSB equals 0, the carry is to ROW address counter bit 0 (ie. row select bit 0). When the ROW STEPSIZE MSB equals 1, the carry is to ROW address counter bit 2 (ie. row address bit 0). For memory architectures that store two video lines per row of memory, the COL address register MSB can be used as the row address LSB. A ROW STEPSIZE = 4 (control register bits 5,4 and 3 = 100) will cause the column MSB to change on the rising edge of ~CAE during an X-Y address cycle.

Programming the address pointer for an initial value is merely a matter of writing to the 3 address registers. The COL address register is simply the 8 LSB's of the column address. The ROW address register consists of the 8 LSB's of the row address. The BLOCK address register consists of the two MSB's each of the row address and the column address as well as the two row select bits and two column select bits. The BLOCK address register has a second function. In systems with limited address space, this register allows the user to move through memory in 64K blocks. By setting control register B, bit 15 to 1, the user may use address input pins CA7 - CA0 and RA7 - RA0 to move within a 64K block determined by the contents of the BLOCK address register. Note that since the BLOCK address register is part of the X-Y address pointer, its contents are subject to change after an X-Y cycle is performed.

For memory architectures that store two video lines of data per row of memory in interlaced format (ie. data is in memory as Line# 1,3,2,4,5,7,6,8,etc.) the ISC can linearize a memory access by setting the AGREFORMAT bit to 1 (control register A bit 4). Data will then be accessed from memory as Line# 1,2,3,4,5,6,7,8,etc. The ISC performs this function by swapping the column MSB with row bit 0 during memory addressing time. Remember, the column MSB selection is memory size dependent.

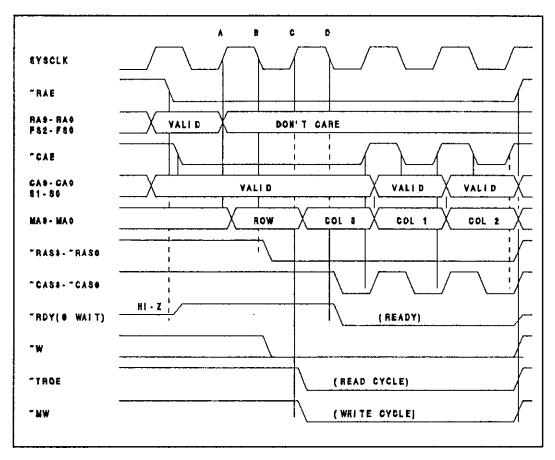

The chip also provides the ability for fast page mode memory access. The chip provides this feature by allowing the ~CAE input pin a direct path to ~CAS outputs once the initial setup of the memory is complete. The user must hold ~RAE low for the duration of the cycle and toggle ~CAE for each new column update. The user must obey memory precharge requirements and all other memory specific timing associated with this mode. The ISC does not detect row changes and so the user must provide this function so that row boundaries are not crossed during a fast page mode access. Fast page mode may be used with both memory direct and memory indirect cycles.

# 5. HOST AND MEMORY INTERFACE OPERATION

The ISC performs two types of access cycles; host initiated cycles and internally generated cycles. The five host initiated cycles include: Host Direct, X-Y Indirect, Shift-Register Transfer, Internal Register access and Real-Time access. These host initiated cycles are selected with the function select pins (FS2-FS0) and are initiated when ~RAE goes low. The function select code is latched on the falling edge of ~RAE. The two internally generated cycles are: Display/Acquire Update and Burst Refresh.

| FS2 | F\$1 | FS0 | CYCLE              |  |

|-----|------|-----|--------------------|--|

| 0   | 0    | 0   | Register-access    |  |

| 0   | 0    | 1   | X-Y Indirect       |  |

| 0   | 1    | 0   | Register-access    |  |

| 0   | 1    | 1   | Host-direct access |  |

| 1   | 0    | 0   | Write Transfer     |  |

| 1   | 0    | 1   | Read Transfer      |  |

| 1   | 1    | 0   | Real-Time access   |  |

| 1   | 1    | 1   | Reserved           |  |

TABLE 5-1 FUNCTION SELECT DECODE

#### **5.1 ARBITRATION**

The arbiter that is built into the ISC controls the scheduling of the automatic display update cycle, the automatic burst refresh cycle and any host initiated cycle. When faced with a conflict, the arbiter grants requests according to the following priority:

- 1) Any cycle already in progress

- 2) A display/acquire update cycle (if enabled)

- 3) A DRAM burst refresh cycle(s) (if enabled)

- 4) A host initiated cycle (including internal register access)

Both display/acquire updates and DRAM refresh are requested at the beginning of horizontal blank. When both display/acquire updates and DRAM refresh are enabled, the arbiter allows the display/acquire update to occur first and then allows the DRAM burst refresh to proceed immediately following. If a display update was not allowed to occur by the end of horizontal blank, a display update error is generated in the status register. If a DRAM burst refresh was not allowed to occur or finish by the end of horizontal blank, a refresh error is generated in the status register.

# **5.2 INTERNAL REGISTER ACCESS**

There are 22, 16 bit register locations in the ISC that are host accessible. Since the ISC's host data bus interface is only 8 bits wide, the internal registers are accessed as lower and higher bytes. An internal register access cycle is initiated with a function select code of 0 or 2 and the falling edge of ~RAE. The direction of the transfer is determined by the ~W input pin. Column address input pin 0 determines whether the lower or higher byte of the 16 bit register is accessed. Column address bits 1 through 5 selects one of the 22 register locations.

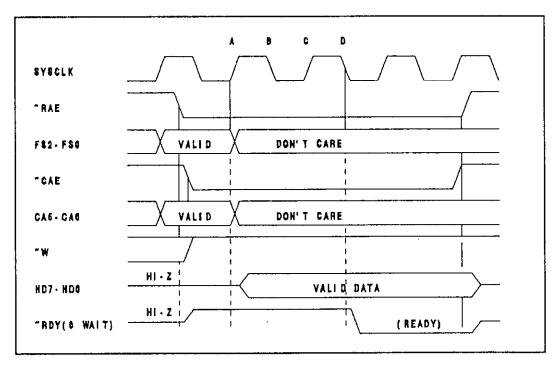

FIGURE 5-1 INTERNAL REGISTER READ ACCESS

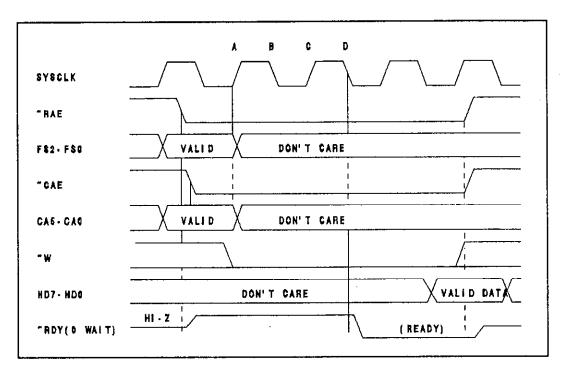

FIGURE 5-2 INTERNAL REGISTER WRITE ACCESS

Data bus pins HD7-HD0 are bidirectional and ~W must be valid prior to clock edge 'A' of the register cycle or the enabling of external data buffers to prevent buffer conflict, which could damage the ISC. Since the ISC does not latch host input data, the user must ensure that host data remains valid past the rising edge of ~CAE or ~W at the end of a register write cycle. During a register read cycle, the ~W input must remain valid for the duration of the cycle.

The timing of a register read cycle is shown in figure 5-1. By driving ~RAE low, the host processor signals the start of a cycle. The FS2-FS0 signal inputs are latched on this edge of ~RAE. The CA5-CA0 inputs are latched on the falling edge of ~CAE. The ~RDY pin transitions from the high impedance state to the active high "not ready" state. After the appropriate number of wait states have been counted out, the ~RDY pin transitions to the active low "ready" state. At the end of the cycle, when ~RAE transitions high, the ~RDY pin goes back to the high impedance state. The ISC detects ~RAE going low and begins the cycle on SYSCLK edge 'A' (assuming there are no conflicts with an internally generated cycle). Valid data is available just after clock edge 'A' and a 0 wait state, active low ready signal is asserted on clock edge 'D'.

The register write cycle of Figure 5-2 is similar to the register read cycle. Data to the ISC on pins HD7-HD0 must be valid before either ~CAE or ~W go high and must remain valid just after these signals going high.

## **5.3 DISPLAY UPDATE CYCLE**

A display (acquire) update is performed automatically by the ISC. A display update is basically an automatically generated VRAM read transfer cycle in which the contents of a row of memory is transferred to the Serial Access Memory (SAM) register. An acquire update is similarly an automatically generated VRAM write transfer cycle in which the contents of SAM is transferred to a row of memory.

The contents of the row portion of the display address register determines which row in memory the transfer will occur. The contents of the column portion of the display address register determines the tap point for the transfer.

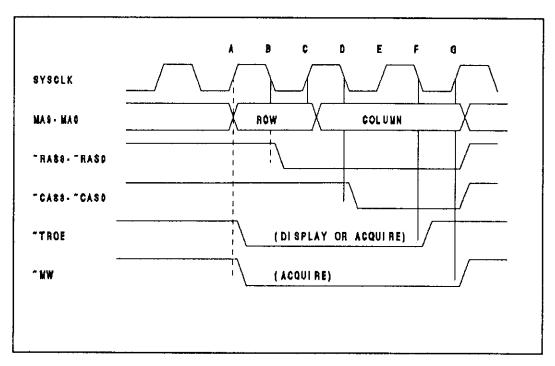

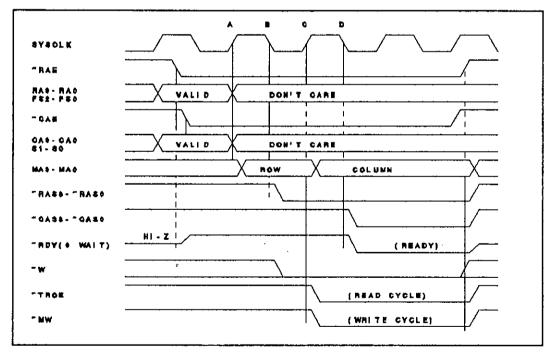

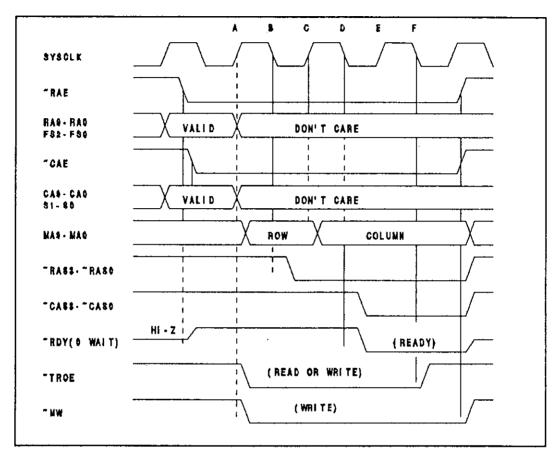

The ISC first creates an internal display update request. The arbiter determines if any other cycle is inprogress. If all is clear, the arbiter creates an acknowledge to this request. The VRAM controller inside the ISC then begins the cycle on the rising SYSCLK edge 'A' by pointing to the row portion of the display address register and assertion ~TROE low (also ~MW low during an acquire). At clock edge 'B' ~RAS is asserted. At clock edge 'C', the memory address points to the column portion of the display address register. At clock edge 'D', ~CAS is asserted. At clock edge 'F', ~TROE is brought back high. The cycle ends on clock edge 'G'. Once a display update cycle begins it takes three SYSCLK cycles to complete the cycle.

FIGURE 5-3 DISPLAY OR ACQUIRE UPDATE CYCLE