### **Physical Layer Validation of Storage Systems**

- Advanced Tools for Validation, Debug and Characterization of SAS and SATA Designs

John Calvin Tektronix Storage Portfolio Product Manager Chairman of SATA-IO Logo and Interoperability Working group

#### **Presenter Biography**

#### John Calvin, Logo Work Group Chair

- John Calvin currently is the chairman of the Serial ATA International Organization's Interoperability working group. John is a Product Manager at Tektronix where he has worked for the last 15 years, with a focus on high speed serial measurements solutions for industry standards. He has worked as a contributor to SATA testing since 2000. John holds a Bachelors Degree in Electrical Engineering from Washington State University and has been awarded 6 patents in measurement-related technology.

- <u>http://www.serialata.org/about/work\_group\_chairs.asp</u>

### SATA Logo/Interoperability mission

- The Storage industry and SATA in particularly has shipped over One Billion disk drives. The cost sensitivity of the consumer market has made storage systems a commodity item. The lowest cost item usually emerges as the most attractive from a OEM/Supplier arrangment.

- The interchangeability of SATA storage demands a high degree of assured interoperability between devices at the principal electrical interfaces.

- The SATA Logo/Interoperability organization's charter is to develop test techniques and methods which ensure this industries interoperability objectives are being met, for all SATA Certified products.

Tektronix Innovation Forum 2010

Tektronix<sup>\*</sup>

### Agenda

- Introduction

- SAS

- Physical Layer Testing Overview

- Measurements

- Challenges in SSC

- Test Reporting

- SATA

- UTD 1.4 (6 Gb/s) Measurements

- New Measurements

- Receiver Testing

- Summary

- Serial Advanced Technology Attachment (SATA)

- Tektronix has the only comprehensive and <u>fully automated SATA physical</u> layer test automation package in the industry today, enabling the broad community of expert users, industrial automation and technical users since the beginning of SATA over a decade ago.

- Well established 20 Ghz scope performance has been utilized at industry interoperability events and test labs for 2 years and provides unparalleled trigger, capture and analysis capabilities.

- In the field of Receiver testing, Tektronix has introduced the concept of full digital synthesis of waveform impairments as well as integrated methods of logical state control with high performance (24Gs/sec) Arbitrary Waveform Generators.

- Serial Attached SCSI (SAS)

- Tektronix is currently recognized as one of the two valid tool providers for the UNH IOL <u>SAS Consortium's Physical Layer test suite</u>. These are the tests performed for SAS conformance at a recent Plugfest.

- Best in class, proven real time instrumentation platform along with industry recognized 70GHz sampling scopes provides users flexibility and latitude with either advanced debug or higher bit rates.

- The first and only tool provider to provide comprehensive Noise decomposition, as well as Jitter decomposition along BER contour calculations.

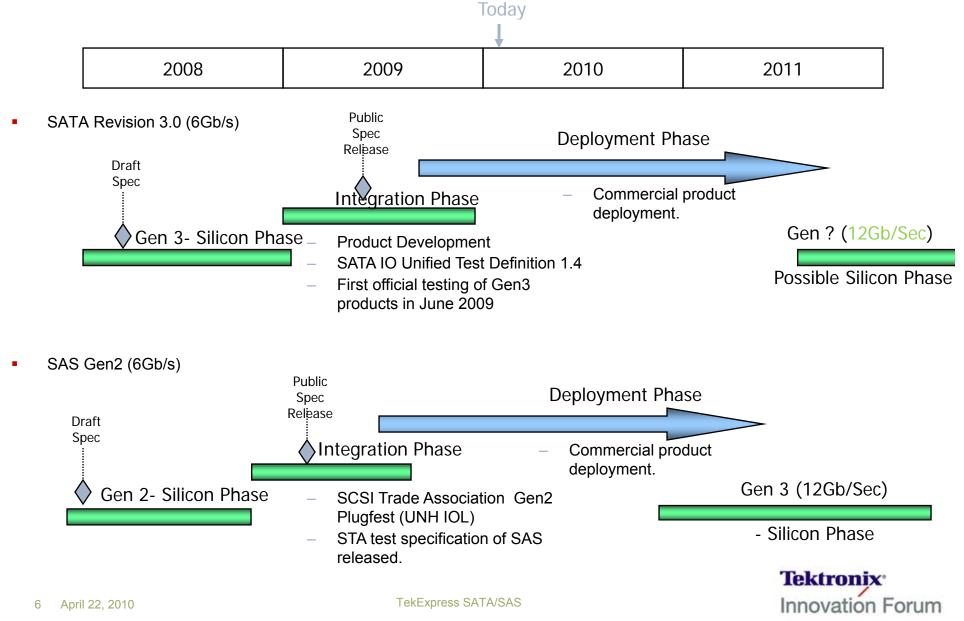

### Storage Timelines and Solutions Development

#### Industry Productivity

### Compliance Testing – An Industry Productivity Issue

Greater speed means greater design challenges, with implications...

- 1. Greater test complexity

- More instruments, configurations, and setup time

- Breadth of tests demands highly experienced, senior equipment users to perform and interpret results.

- 3. Text complexity is high

- Highly specialized e.g., SSC modulation analysis, advanced receiver testing, Frequency domain S-Parameter measurements.

- 4. Days to perform effective, repeatable and reliable product validation tests

"Banner specs are no longer the gating issue. The latest equipment provides ample raw performance. What's needed is greater ease of use, setup and automation."

- Customer feedback

## SAS Physical Layer Testing

#### STA: PHY informative measurements

- SAS GROUP 1: COUPLING & OOB REQUIREMENTS

- TEST 5.1.1 AC COUPLING REQUIREMENTS

- TEST 5.1.2 TX MAXIMUM NOISE DURING OOB IDLE

- TEST 5.1.3 TX OOB BURST AMPLITUDE

- TEST 5.1.4 TX OOB OFFSET DELTA

- TEST 5.1.5 TX OOB COMMON MODE DELTA

- SAS GROUP 2: TX SPREAD SPECTRUM CLOCKING (SSC) REQUIREMENTS

- TEST 5.2.1 TX SSC MODULATION TYPE

- TEST 5.2.2 TX SSC MODULATION FREQUENCY

- TEST 5.2.3 TX SSC MODULATION DEVIATION AND BALANCE

- TEST 5.2.4 TX SSC DFDT (INFORMATIVE)

- GROUP 3: TX NRZ DATA SIGNALING REQUIREMENTS

- TEST 5.3.1 TX PHYSICAL LINK RATE LONG TERM STABILITY

- TEST 5.3.2 TX COMMON MODE RMS VOLTAGE LIMIT

- TEST 5.3.3 TX COMMON MODE SPECTRUM

- TEST 5.3.4 TX PEAK-TO-PEAK VOLTAGE

- TEST 5.3.5 TX VMA AND EQ (INFORMATIVE)

- TEST 5.3.6 TX RISE AND FALL TIMES

- TEST 5.3.7 TX RANDOM JITTER (RJ)

- TEST 5.3.8 TX TOTAL JITTER (TJ)

9

The SAS consortium and the testing programs sponsored by the SCSI Trade Association (STA) perform these measurements on an <u>informative</u> basis.

There are no sanctioned SAS <u>compliance</u> measurements.

**GROUP 4: S-PARAMETER REQUIREMENTS**

- TEST 5.4.1 RX DIFFERENTIAL RETURN LOSS (SDD11)

- TEST 5.4.2 RX COMMON-MODE RETURN LOSS (SCC11)

- TEST 5.4.3 RX DIFFERENTIAL IMPEDANCE IMBALANCE (SCD11)

- TEST 5.4.4 TX DIFFERENTIAL RETURN LOSS (SDD22)

- TEST 5.4.5 TX COMMON-MODE RETURN LOSS (SCC22)

- TEST 5.4.6 TX DIFFERENTIAL IMPEDANCE IMBALANCE (SCD22)

Tektronix<sup>•</sup> Innovation Forum

TEST 5.3.9 - TX WAVEFORM DISTORTION PENALTY (WDP)

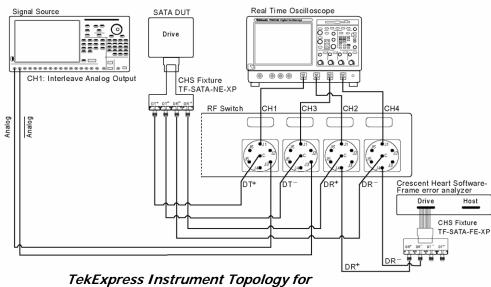

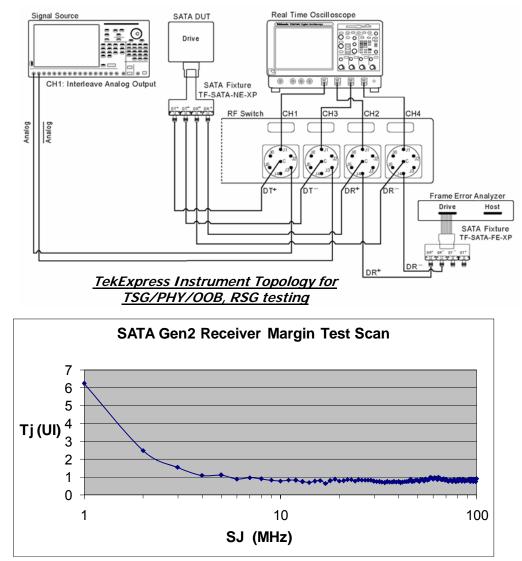

#### Integrated and Automated Test Control TekExpress<sup>™</sup> Test Automation Framework

TSG/PHY/OOB, RSG testing

- •Simplifies Complex Measurements

- Improves Engineering Productivity

- •Repeatable and Consistent results

- •Automatic with no user intervention

- Arbitrary Waveform Generator (AWG)

- DUT state control

- Digitally synthesizes test signal impairments (Direct Synthesis)

- Complete offering includes:

- Leading portfolio of Tektronix test instruments

- Oscilloscopes

- Signal generators

- 3<sup>rd</sup> party integration with RF switch (Keithley), fixtures, API (NI), cabling, deskew, etc.

- Auto discovery of instruments using GPIB, USB, and LAN

- 1GbE networking is used for data/waveform transport.

- GPIB/488.2 is used for RF Switch and Power supply communications

- Test sequence automation

- One button control

- Reporting

### TekExpress: SAS TSB/PHY/OOB

|                                         | Select Standard                                             | Select Device           | Select Test Suite                                  |          | Version         |

|-----------------------------------------|-------------------------------------------------------------|-------------------------|----------------------------------------------------|----------|-----------------|

| <ul><li>○ Seria</li><li>⊙ SAS</li></ul> | IATA                                                        | ⊙ Drive                 | <ul> <li>● PHY-TSG-00B</li> <li>● Rx-Tx</li> </ul> | SAS 2.0  | 0               |

|                                         |                                                             | Drive : PHY-TSG-OOB S   | AS 2.0                                             |          | Configure       |

| Select                                  | TestName                                                    |                         |                                                    | <u>^</u> |                 |

|                                         | Test 5.2.4 - TX SSC DFDT (<br>Test 5.3.1 - TX Physical Link | •                       |                                                    | _        | Show MOI        |

|                                         | Test 5.3.2 - TX Common Mo                                   |                         |                                                    | _        |                 |

|                                         | Test 5.3.3 - TX Common Mo                                   | -                       |                                                    | _        | Show Schematic  |

|                                         | Test 5.3.4 - TX Peak-to-Peak                                |                         |                                                    |          |                 |

|                                         | Test 5.3.5 - TX VMA and EQ                                  | -                       |                                                    |          | Select All      |

|                                         | Test 5.3.6 - TX Rise and Fall                               |                         |                                                    | =        |                 |

|                                         | Test 5.3.7 - TX Random Jitte                                | r (RJ)                  |                                                    |          | Select Required |

|                                         | Test 5.3.8 - TX Total Jitter (T                             | J)                      |                                                    |          |                 |

|                                         | Test 5.3.9 - TX Waveform D                                  | istortion Penalty (WDP) |                                                    | ~        | Deselect All    |

• Example SAS Report:

<u>ftp://ftp.tektronix.com/outgoing/Sample\_SAS\_Report.mht</u>

Tektronix<sup>•</sup> Innovation Forum

### TekExpress: SAS TSB/PHY/OOB

|                                     |                                    | Drive        | : PHY-TSG-OOB SAS 2.0              |            |                                     | Show Pass / Fail   |

|-------------------------------------|------------------------------------|--------------|------------------------------------|------------|-------------------------------------|--------------------|

| TestName                            | Status                             | Low Limit    | Measured Value                     | High Limit | Low limit margin, High limit margin | Pass/Fail Status ^ |

| Test 5.1.2 - TX Maximum Noise Duri  | Completed Test 5.1.2 - TX Maximum  | 120 mV       | 104                                | -NA-       | 16 - Passed                         | 🗸 Pass             |

|                                     |                                    | 2400 mV      | Maximum peak-to-peak burst amplitu | -NA-       | 1796 - Passed                       |                    |

| Task E 1 0 TV OOD Durch Association | Completed Test 5.1.3 - TX OOB Burs | 2400 mV      | Minimum peak-to-peak burst amplitu | -NA-       | 2119.8 - Passed                     | ✓ Pass             |

| Test 5.1.3 - TX OOB Burst Amplitude | Completed Lest 2.1.3 • 1X OOB Burs | 240 mV       | Minimum peak-to-peak burst amplitu | -NA-       | 364 - Passed                        |                    |

|                                     |                                    | 240 mV       | Minimum peak-to-peak burst amplitu | -NA-       | 40.2 - Passed                       |                    |

| Test 5.1.4 - TX OOB Offset Delta    | Completed Test 5.1.4 - TX OOB Offs | 25 mV        | -3.09832                           | -NA-       | 28.0983 - Passed                    | ✓ Pass             |

| Test 5.1.5 - TX OOB Common Mode     | Completed Test 5.1.5 - TX OOB Com  | 50 mV        | -3.47364                           | -NA-       | 53.4736 - Passed                    | 🗸 Pass             |

| Test 5.2.1 - TX SSC Modulation Type | Completed Test 5.2.1 - TX SSC Mod  | •            | Down-spread SATA                   |            | •                                   | 🗸 Pass             |

|                                     |                                    |              | Modulation frequency: 30           |            | 0,3-Failed                          |                    |

| Test 5.2.2 - TX SSC Modulation Freq | Completed Test 5.2.2 - TX SSC Mod  | 30 KHz       | Min Modulation frequency: 29.9976  | 33 KHz     | Informative                         | 🗙 Fail             |

|                                     |                                    |              | Max Modulation frequency: 30 0017  | _          | Informative                         |                    |

| Test 5.2.3 - TX SSC Modulation Devi | Completed Test 5.2.3 - TX SSC Mod  | -5000 ppm    | Max deviation: -2200.53            | 0 ppm      | Informative                         | × Fail             |

| TESCO.2.3 * TA SSC MODULATION DEVI  |                                    | -5000 ppm    | Min deviation: -0.4482             | 0 ppm      | Informative                         |                    |

| Test 5.2.4 - TX SSC DFDT (Informati | Completed Test 5.2.4 - TX SSC DFD  | -5350 ppm/us | -327.7502                          | 350 ppm/us | 5022.2498, 677.7502 - Passed        | 🗸 Pass 🛛 👻         |

| <                                   |                                    |              | Ш                                  |            |                                     | >                  |

- Test Results are detailed in the analysis panel, showing measurement results, user or standard specified test limits and high and low margin values.

- The Pass/Fail criteria defaults to the SAS Standards limits, however users can relax or make them more stringent if needed.

#### Advanced Noise Decomposition and Jitter Analysis

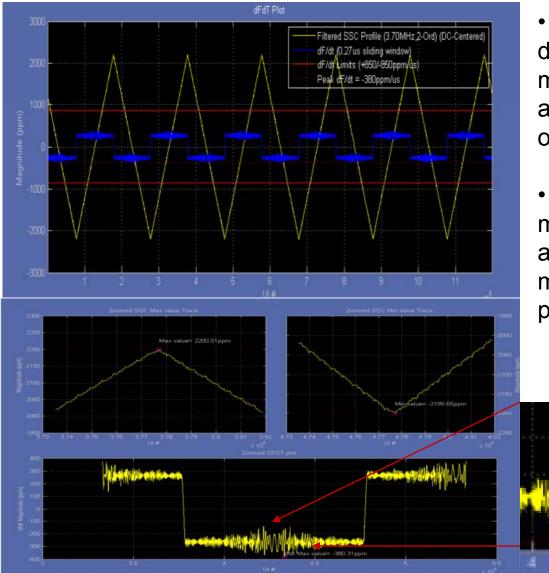

#### SAS/SATA SSC Analysis

Advanced tools required to provide detailed insights into SSC modulation problems and to automatically identify and zoom in on problem areas

In this example, the regions of maximum and minimum modulation as well as the dF/dT absolute maximum are magnified and presented for scrutiny

Tektronix Innovation Forum 2010

## SAS: Comprehensive Report: 29 fully automated tests

|                                                      |              |                    | Test Details                                              |            | Measured                 |            |                    | Units Test Re: |                        |

|------------------------------------------------------|--------------|--------------------|-----------------------------------------------------------|------------|--------------------------|------------|--------------------|----------------|------------------------|

| Test Name                                            | Pattern Name | Interface<br>Speed | Measurement Details                                       | Low Limit  | Value                    | High Limit | Margin             | Units          | Test Resi              |

| Test 5.2.1-TX SSC Modulation Type                    | HFTP         | 6.0Gb/s            | Center-spread SAS                                         | -NA-       | SSC ON                   | -NA-       | -NA-               | -NA-           | Pass                   |

|                                                      | HFTP         | 6.0Gb/s            | SSC Modulation Frequency                                  | >= 30      | 30.0000                  | <= 33      | 0,3                |                | Pass                   |

| Test 5.2.2-TX SSC Modulation Frequency               | HFTP         | 6.0Gb/s            | Min SSC Modulation Frequency                              | >= 30      | 29.9992                  | <= 33      | Informative        |                |                        |

|                                                      | HFTP         | 6.0Gb/s            | Max SSC Modulation Frequency                              | >= 30      | 30.0011                  | <= 33      | Informative        |                | Informati<br>Informati |

|                                                      |              |                    |                                                           |            |                          |            |                    | I              |                        |

|                                                      | HFTP         | 6.0Gb/s            | Max Deviation                                             | -NA-       | -2199.6500               | -NA-       | -NA-               | -              | Informat               |

| est 5.2.3-TX SSC Modulation Deviation and Balance    | HFTP         | 6.0Gb/s            | Min Deviation                                             | -NA-       | 2200.0074                | -NA-       | -NA-               | ppm            | Informati              |

| Corolizio IX Coo Modulaton Donaton and Dalance       | HFTP         | 6.0Gb/s            | Avg Deviation                                             | >= -350    | 0.1787                   | <= 350     | 350.1787, 349.8213 | ppin           | Pass                   |

|                                                      | HFTP         | 6.0Gb/s            | Deviation asymmetry                                       | -          | - 0.3574 <= 288 287.6426 |            |                    | Pass           |                        |

| Test 5 2 4-TX SSC DEDT (Informative)                 | HFTP         | 6 0Gb/s            | df/dt                                                     | >= -850    | -380 3082                | <= 850     | Informative        | ppm/us         | Informat               |

|                                                      | HFTP         | 6.0Gb/s            | Mean Period                                               | > -100     | -2.1050                  | < 100      | Informative        |                | Informat               |

| Test 5.2.1 TV Dhusiaal Link Data Lang Term Stability | HFTP         | 6.0Gb/s            | Min Period                                                | > -100     |                          | < 100      |                    |                |                        |

| Test 5.3.1-TX Physical Link Rate Long Term Stability |              |                    |                                                           | > -100     | 2200.0074                |            | Informative        | ppm            | Informat               |

|                                                      | HFTP         | 6.0Gb/s            | 0Gb/s Max Period                                          |            | -2199.6501               | < 100      | Informative        |                | Informat               |

| Test 5.3.2-TX Common Mode RMS Voltage Limit          | CJTPat-Gen 2 | 6.0Gb/s            | Common-mode RMS voltage at IT (mV)-<br>SAS 2.0            | -          | 42.9927                  | < 30       | 12.9927            | mV             | Fail                   |

|                                                      |              | 1                  |                                                           |            |                          |            | 1                  |                |                        |

|                                                      | CJTPat-Gen 2 | 6.0Gb/s            | Common-mode spectrum (dBmV) at<br>100MHz-SAS 2.0          | -          | -33.5589                 | < 12.7     | 46.2589            |                | Pass                   |

| Test 5.3.3-TX Common Mode Spectrum                   | CJTPat-Gen 2 | 6.0Gb/s            | Common-mode spectrum (dBmV) at first<br>harmonic-SAS 2.0  | -          | 16.7701                  | < 26       | 9.2299             | mV             | Pass                   |

|                                                      | CJTPat-Gen 2 | 6.0Gb/s            | Common-mode spectrum (dBmV) at<br>second harmonic-SAS 2.0 | -          | -9.8586                  | < 30       | 39.8586            |                | Pass                   |

| Test 5.3.4-TX Peak-to-Peak Voltage                   | D30.3-Gen 2  | 6.0Gb/s            | Peak to Peak voltage (mVppd)-SAS 2.0                      | > 850      | 1240.0000                | < 1200     | 390 , 40           | mV             | Fail                   |

|                                                      | I            |                    |                                                           |            |                          |            |                    | I              |                        |

| Test 5.3.5-TX VMA and EQ                             | D30.3-Gen 2  | 6.0Gb/s            | Transmitter equalization (dB)-SAS 2.0                     | > 2        | 2.0684                   | < 4        | Informative        | dB             | Pass                   |

|                                                      | D10.2        | 6.0 Gb/s           | Rise time in ps                                           | >= 41.6    | 55.7616                  | -          | 14.1616            |                | Pass                   |

| Test 5.3.6-TX Rise and Fall Times                    | D10.2        | 6.0 Gb/s           | Fall time in ps                                           | >= 41.6    | 55.3999                  | -          | 13.7999            | ps             | Pass                   |

|                                                      | I            |                    | 1                                                         | <br>       |                          |            | 1                  | I              |                        |

| Test 5.3.7-TX Random Jitter (RJ)                     | D24.3-Gen 2  | 6.0Gb/s            | Rj before CIC                                             | -          | 0.7069                   | <= 25      | 24.2931            | ps             | Pass                   |

|                                                      | D24.3-Gen 2  | 6.0Gb/s            | Rj after CIC                                              | -          | 0.5321                   | <= 25      | 24.4679            |                | Pass                   |

|                                                      | •            |                    | Tektronix Innov                                           | ation Form | m 2010                   | -          |                    |                |                        |

Tektronix Innovation Forum 2010

## SATA Physical Layer Testing

It's the measurements ...

### SATA UTD 1.4 Test Requirements

| Phy Transmit Signal Requirements                                   | SI General Requirements                                              |

|--------------------------------------------------------------------|----------------------------------------------------------------------|

| TSG-01 : Differential Output Voltage<br>TSG-02 : Rise/Fall Time    | SI-1:8 : Cable Characterization<br>SI-09 : Inter-Symbol Interference |

| TSG-03 : Differential Skew                                         | Phy General Requirements                                             |

| TSG-04 : AC Common Mode Voltage                                    | PHY-01 : Unit Interval                                               |

| TSG-05 : Rise/Fall Imbalance                                       | PHY-02 : Frequency Long Term Stability                               |

| TSG-06 : Amplitude Imbalance                                       | PHY-03 : Spread-Spectrum Modulation Frequency                        |

| TSG-07 : Gen1 (1.5Gb/s) TJ at Connector, Clock to Data, fBAUD/10   | PHY-04 : Spread-Spectrum Modulation Deviation                        |

| TSG-08: Gen1 (1.5Gb/s) DJ at Connector, Clock to Data, fBAUD/10    | Phy OOB Requirements                                                 |

| TSG-09 : Gen1 (1.5Gb/s) TJ at Connector, Clock to Data, fBAUD/500  | OOB-01 : OOB Signal Detection Threshold                              |

| TSG-10 : Gen1 (1.5Gb/s) DJ at Connector, Clock to Data, fBAUD/500  | OOB-02 : UI During OOB Signaling                                     |

| TSG-11 : Gen2 (3Gb/s) TJ at Connector, Clock to Data, fBAUD/500    | OOB-03 : COMINIT/RESET and COMWAKE Transmit Burst Length             |

| TSG-12 : Gen2 (3Gb/s) DJ at Connector, Clock to Data, fBAUD/500    | OOB-04 : COMINIT/RESET Transmit Gap Length                           |

| TSG-13: Gen3 (6Gb/s) Transmit Jitter w/wo CIC                      | OOB-05 : COMWAKE Transmit Gap Length                                 |

| TSG-14 : Gen3 (6Gb/s)TX Maximum Differential Voltage Amplitude     | Phy Receiver/Transmitter Channel Reqs                                |

| TSG-15 : Gen3 (6Gb/s) TX Minimum Differential Voltage Amplitude    | RX/TX-01 : Pair Differential Impedance                               |

| TSG-16 : Gen3 (6Gb/s) Tx AC Common Mode Voltage                    | RX/TX-02 : Single-Ended Impedance (Obsolete)                         |

| Phy Receive Signal Requirement                                     | RX/TX-03 : Gen2 (3Gb/s) Differential Mode Return Loss                |

| RSG-01 : Gen1 (1.5Gb/s) Receiver Jitter Tolerance Test (Normative) | RX/TX-04 : Gen2 (3Gb/s) Common Mode Return Loss                      |

| RSG-02 : Gen2 (3Gb/s) Receiver Jitter Tolerance Test (Normative)   | RX/TX-05 : Gen2 (3Gb/s) Impedance Balance                            |

| RSG-03 : Gen3 (6Gb/s) Receiver Jitter Tolerance Test               | RX/TX-06 : Gen1 (1.5Gb/s) Differential Mode Return Loss              |

| RSG-05 : Gen1 Asynchronous Receiver Stress Test at +350ppm         | RX/TX-07 : Gen3 (6Gb/s) Differential Mode Return Loss                |

| RSG-06 : Gen1 Asynchronous Receiver Stress Test With SSC           | RX/TX-08 : Gen3 (6Gb/s) Impedance Balance                            |

#### **SATA Measurement Legends:**

No change from previous UTD 1.3 spec version Revised methodology from UTD1.3 to UTD 1.4 New test definitions in UTD 1.4 Obsolete

Full SATA Logo Test Specification available at.. http://www.serialata.org/documents/Interop\_UnifiedTe st\_Rev1\_4\_v1\_00\_083109.pdf Tektronix<sup>•</sup>

Tektronix Innovation Forum 2010

#### SATA UTD 1.4 TSG/PHY/OOB Measurements

Drive : PHY-TSG-00B SATA Gen 3-UTD 1.4-All

| Select   | TestName                                              |

|----------|-------------------------------------------------------|

|          | Informative-df/dt Measurement                         |

|          | Informative-Eye diagrams                              |

|          | 00B01-00B Signal Detection Threshold                  |

|          | 00B02-UI During 00B Signaling                         |

|          | OOB03-COMINIT_RESET and COMWAKE Transmit Burst Langth |

|          | OOB04-COMINIT_RESET Transmit Gap Length               |

|          | 00B05-COMWAKE Transmit Gap Length                     |

|          | 00B06-COMWAKE Gap Detection Windows                   |

|          | 00B07-COMINIT Gap Detection Windows                   |

|          | PHY01-Unit Interval                                   |

|          | PHY02-Frequency Long Term Stability                   |

|          | PHY03-Spread-Spectrum Modulation Frequency            |

|          | PHY04-Spread-Spectrum Modulation Deviation            |

|          | TSG01-Differential Output Voltage-Option 1            |

|          | TSG01-Differential Output Voltage-Option 2            |

|          | TSG02-Rise-Fall Time                                  |

|          | TSG03-Differential Skew                               |

|          | TSG04-AC Common Mode Voltage                          |

|          | TSG05-Rise-Fall Imbalance                             |

|          | TSG06-Amplitude Imbalance                             |

|          | TSG09-TJ at Connector, Clock to Data, fBAUD-500       |

|          | TSG10-DJ at Connector, Clock to Data, fBAUD-500       |

|          | TSG11-TJ at Connector, Clock to Data, fBAUD-500       |

|          | TSG12-DJ at Connector, Clock to Data, fBAUD-500       |

|          | TSG13-Transmit Jitter                                 |

|          | TSG14-TX Maximum Differential Voltage Amplitude       |

|          | TSG15-TX Minimum Differential Voltage Amplitude       |

| 8 🔽      | TSG16-Tx AC Common Mode Voltage                       |

| <i>r</i> |                                                       |

| SATA Gen 3-UTD 1.4-All                       | ~ |

|----------------------------------------------|---|

| SATA Gen 2-UTD 1.2                           | ^ |

| SATA Gen 2-UTD 1.2-All<br>SATA Gen 2-UTD 1.3 |   |

| SATA Gen 2-UTD 1.3-All                       |   |

| SATA Gen 2-UTD 1.4                           |   |

| SATA Gen 2-UTD 1.4-All<br>SATA Gen 3-UTD 1.4 |   |

| SATA Gen 3-UTD 1.4-All                       | ~ |

Different Test program and degrees of regression testing now user selectable. UTD 1.2 and 1.3 tests use JIT3 and run on TDS and DPO class instruments. UTD 1.4 tests (Gen3) only operate on DPOJET.

Debug and Diagnostic tools (Informative measurements)

New SATA Gen3 measurements **Tektronix** Innovation Forum

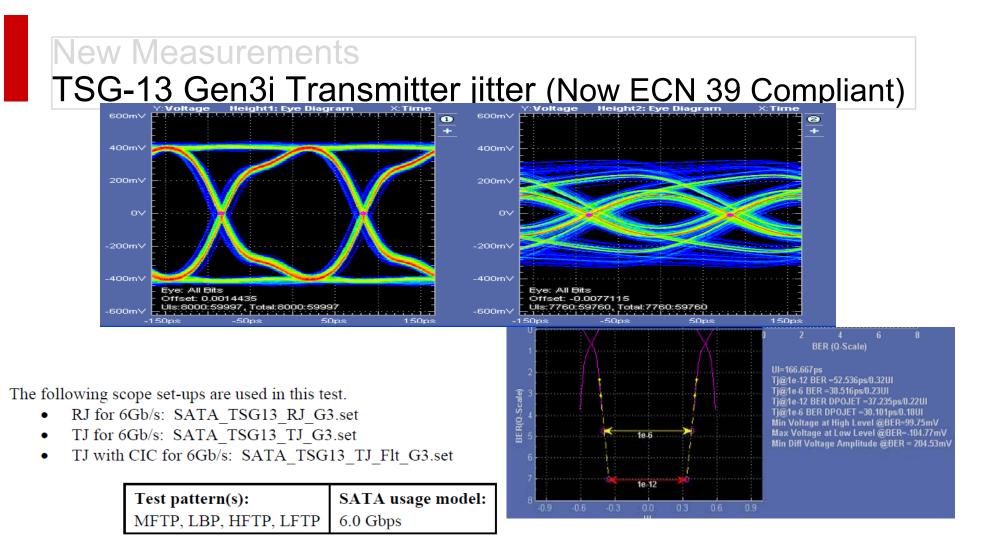

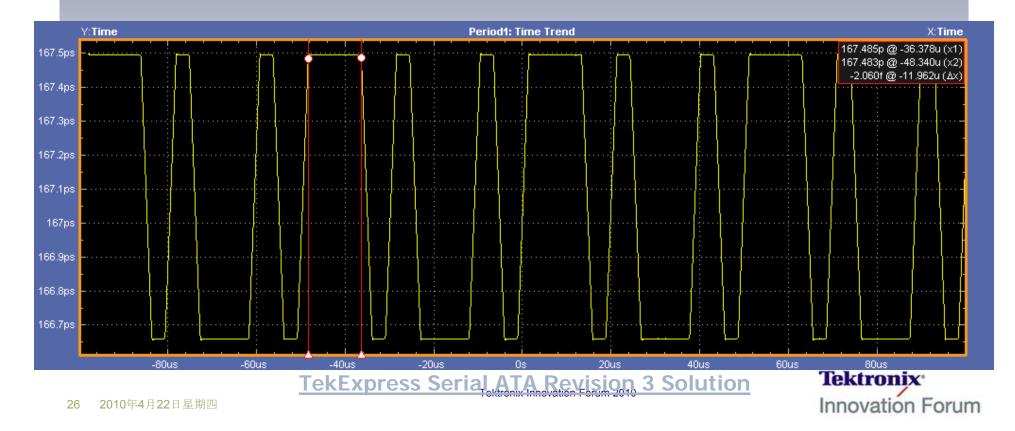

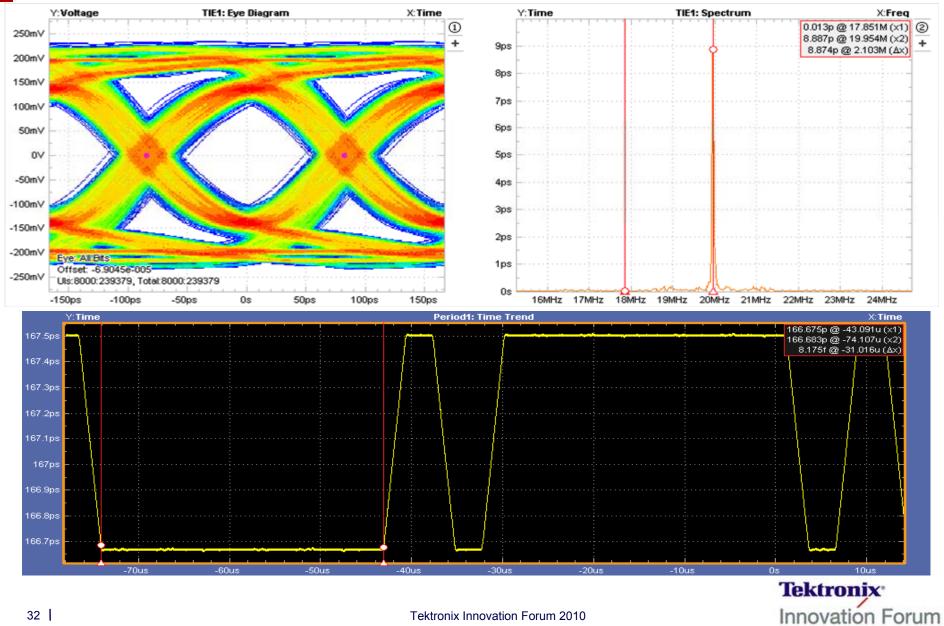

SATA 6Gbps: 10 us/div, 20 ps/pt (>100,000 UI).

Horizontal resolution will vary depending on the data rate and oscilloscope model

#### **Observable Results:**

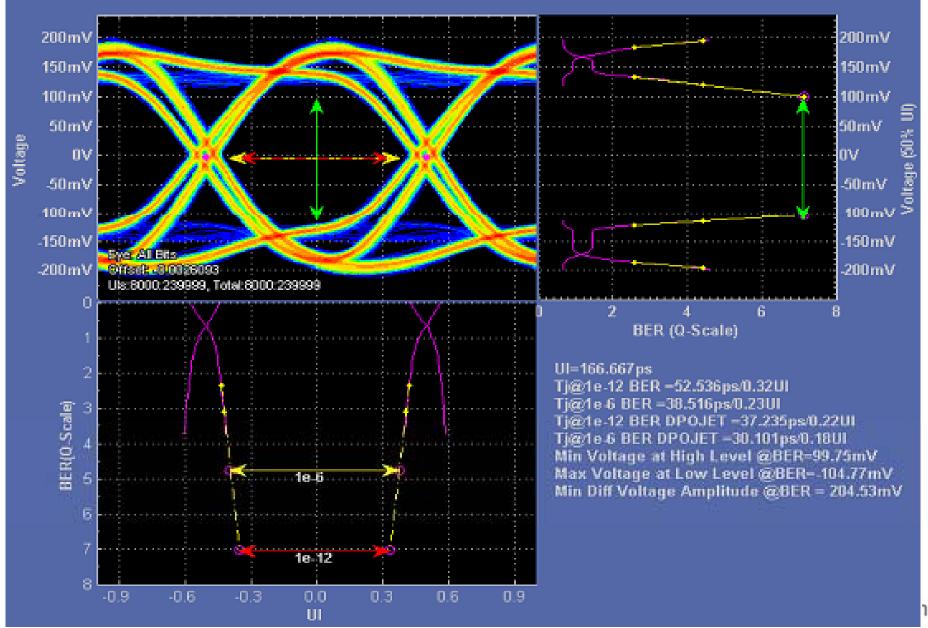

• RJ measured (RJmeas) at a maximum of 0.18 UI into a Laboratory Load before the Compliance Interconnect Channel (CIC) when measured using the specified JTF for products running at 6.0 Gb/s

• TJ measured at a maximum of (RJmeas) + 0.34 UI into a Laboratory Load before the CIC when measured using the specified JTF (for products running at 6.0 Gb/s)

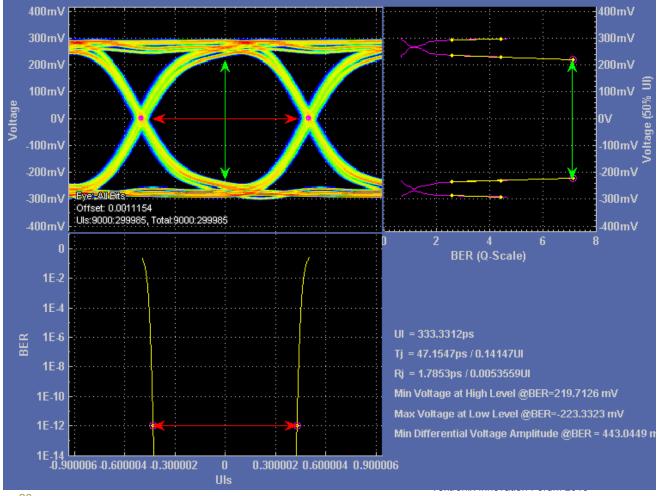

#### New Measurements TSG-15 Tx Minimum Differential Amplitude @ BER.

- One of the most significant advancements in SATA PHY testing for Gen3 is the new minimum amplitude technique

- Analyzes signal noise content and projects eye closure down to 10E-12 BER.

Goal of this measurement is the horizontal bathtub curve . This is similar to the WDP measurement in SAS

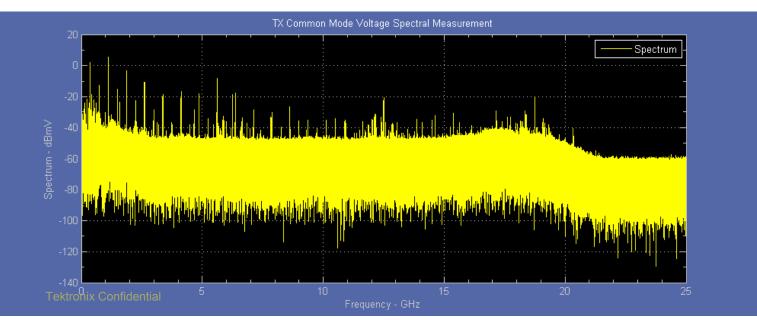

#### New Measurements TSG-16 Tx AC Common Mode Signal Analysis

- 1st/2nd harmonics provide insight into common mode and time domain waveform asymmetry problems which results in EMI problems.

- Real-time waveform capture is absolutely vital if SSC is present. The constant movement of the spectral peaks and the determination of a nominal period cannot be performed on any other system.

- Spectral peaks are constantly moving

- Continuous multi-cycle analysis

**Tektronix**

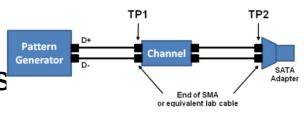

#### SATA: Receiver Signaling Tests

- The jitter composition for receiver testing is a precise mix of Random, Sinusoidal and Pattern Jitter.

- Additionally, the signal amplitude is lowered to the spec limit, and under these conditions a receiver is required to operate for 10, 5, and 2.5 minutes error free (for Gen1, 2, and 3 resp.)

- Sinusoidal (Sj) jitter frequencies

- 5, 10, 33, 62 and recently piloted125MHz

- Why these frequencies?

- High 62 and 33 MHz noise levels inside PC's known to create PLL peaking phenomenon at 5 and 10MHz, 125MHz is a high noise spectral location in PC architectures.

- SATA specifications require the error detection be made at a frame level

**RSG/RMT** testing with TekExpress

#### 7.4.1.2 Frame Error Rate Measurements

The Frame Error Rate (FER) shall be measured and computed to be no greater than 8.200\*10<sup>-8</sup> at a 95% confidence level when tested with any given 8b/10b pattern, including the Frame Error Rate reference patterns cited in section 7.4.1.1. The Serial ATA CRC error detection mechanism is used to measure FER.

The Frame Error Rate is calculated based on the maximum size of a Data FIS, plus overhead for the FIS header and CRC Dwords. The Frame Error Rate assumes a target bit error rate of 10<sup>-12</sup>.

$$FER = (8192 + 8) \times 10 \times 10^{-12} = 8.200 \times 10^{-8}$$

4/22/2010

Innovation Forum

### SATA Receiver Test Jitter Specifications

| Step               | Test<br>Point | Calibration<br>Pattern                                 | Method                                                                                                                                                                                                                                                                                                                                                           | Gen1i                                                                                              | Gen1m                                                    | Gen2i                                                                                           | Gen2m                                                      | Gen3                                                                                                                                                                                                         |

|--------------------|---------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rise/ Fall<br>Time | TP1           | LFTP                                                   | Section 7.4.4 in SATA 3.0<br>Specification                                                                                                                                                                                                                                                                                                                       | 100 ps (20/                                                                                        | 80%)                                                     | 100 ps (20                                                                                      | /80%)                                                      | 62 ps to 75 ps (20/80%)                                                                                                                                                                                      |

| Rj                 | TP1           | MFTP                                                   | Section 7.4.12 of SATA 3.0<br>Specification, Rj method also<br>applied to Gen1i/m and<br>Gen2i/m                                                                                                                                                                                                                                                                 | 8.57 ps RM<br>for a 7 sign<br>projection)                                                          |                                                          | 4.285 ps R<br>sigma for a<br>0.18 UI pro                                                        | a 7 sigma                                                  | 2.14 ps RMS (1 sigma for a<br>7 sigma 0.18 UI projection)                                                                                                                                                    |

| Sj                 | TP1           | MFTP                                                   | Using Rj method defined in<br>section 7.4.12 of SATA 3.0<br>Specification for all data rates                                                                                                                                                                                                                                                                     | Sj=270mUI                                                                                          |                                                          | Sj=270mU                                                                                        | I                                                          | Sj=192mUI                                                                                                                                                                                                    |

| Tj                 | TP2           | Framed COMP<br>with 2 Aligns<br>and new LBP<br>section | See UTD section 2.17.1.1                                                                                                                                                                                                                                                                                                                                         | Tj(min)=50<br>Tj(max)=51<br>Using a cha<br>introduces<br>6ps (i.e. mi<br>max 46ps)<br>the given so | 9mUI<br>annel that<br>40 ps ±<br>n 34ps and<br>of ISI in | Tj(min)=55<br>Tj(max)=54<br>Using a ch<br>introduces<br>6ps (i.e. m<br>max 46ps)<br>the given s | 88mUI<br>annel that<br>40 ps ±<br>in 34ps and<br>of IS( in | Tj(min)=498mUI<br>Tj(max)=570 mUI<br>Using a CIC that introduces<br>a min 21ps and max 33ps<br>of ISI in the given setup and<br>that follows the definition in<br>section 7.2.7 of SATA 3.0<br>Specification |

| Amplitude          | TP2           | Framed COMP<br>with 2 Aligns<br>and new LBP<br>section | For this test the amplitude<br>distribution will be either<br>measured or projected to a 1E-<br>12 BER contour at the 50%<br>location of the bit interval using<br>previously calibrated edge<br>rates and jitter. It is required to<br>ensure that the maximum<br>allowed voltage is not<br>exceeded. Sections 7.4.3 and<br>7.4.12 of SATA 3.0<br>Specification |                                                                                                    | 240 mV                                                   | 275 mV                                                                                          | 240 mV                                                     | 240 mV                                                                                                                                                                                                       |

#### SerialXpress<sup>™</sup> for Serial ATA Pattern Generation

| Ba | se Pattern | Transmitter  | Channel/C       | able      |               |          |                  |       |         |               |             |                    |                   |                   |                     |                   |        |

|----|------------|--------------|-----------------|-----------|---------------|----------|------------------|-------|---------|---------------|-------------|--------------------|-------------------|-------------------|---------------------|-------------------|--------|

|    | Periodic   | Jitter (Pk-I | <sup>2</sup> k) |           |               |          |                  |       |         |               |             | 1                  |                   |                   |                     |                   |        |

|    |            | Mag          | initude:        |           |               |          | Frequency (Hz):  |       | Pha     | se ("):       |             |                    |                   |                   |                     |                   |        |

|    | 🗹 Sine1    | 0.100        |                 | <b>\$</b> | UI            | •        | 10.000000 M      | *     | 0.00    |               | *           |                    |                   |                   |                     |                   |        |

|    | 🗖 Sine2    | 0.070        |                 | •         | UI            | <b>T</b> | 33.000000 M      | Basel | Pattern | Transmitter   | Channel/C   | able               |                   |                   |                     |                   |        |

|    | 🗖 Sine3    | 0.000        |                 | •         | UI            | -        | 10.000000 M      | ~     | [ISI: ] | 0.100         |             | 😌 UI               | -                 |                   |                     |                   |        |

|    | 🗌 Sine4    | 0.000        |                 | •         | UI            | -        | 10.000000 M      |       | 181.    | 10.100        |             |                    | · _               |                   |                     |                   |        |

|    |            | ,            |                 |           |               |          | ,                | 0     | S-Par   | ameter Filte  | er:         |                    |                   |                   |                     |                   |        |

|    | Random     | Jitter (RMS  | •               |           |               |          |                  |       |         |               |             |                    |                   |                   |                     | _                 |        |

|    |            |              | itude:          |           |               |          | quency-Low (Hz): |       | Read    | from File:    | C:\Pro      | )gram Files\Tektro | nix(Serial        | Xpress\S          | 3amples\T           | 01 E              | Irowse |

|    | 🗹 Rj1:     | 0.010        | *               | U         | •             | 10       | 0.000 K          |       | _       |               |             |                    |                   |                   |                     | _                 |        |

|    | 🗖 Rj2:     | 0.000        | *               | UI        | -             | 10       | 0.000 K 🔣        |       | l Inv   | /erse Filter: |             |                    |                   |                   |                     |                   | irowse |

|    | SSC -      |              |                 |           |               |          |                  |       | ISI Sc  | aling:        | 1.000       |                    | *                 |                   |                     |                   |        |

|    |            |              |                 |           |               |          | Frequency -      |       | - Tou   | ichstone 4-I  | Port Data T | vne                |                   |                   |                     |                   |        |

|    | Shape:     |              | Triangle        | e         | <b>-</b>      |          | Deviation:       |       | 100     |               |             | ype                |                   |                   |                     |                   |        |

|    | Spread:    |              | Down            |           | •             |          | Modulation:      |       |         |               | Single      | -ended             | € D               | ifferentia        | I                   |                   |        |

|    | Unequal (  | Spread:      | 0.00            |           | <b>3</b> %    |          | 🗖 Noise:         |       | To      | uchstone 4    | -Port Layou | ut                 |                   |                   |                     |                   |        |

|    | df/dt:     |              | 0.000           |           | 😂 pp          | m/us     |                  |       |         |               |             |                    | _                 |                   |                     | _                 | ,      |

|    | awat.      |              | 1               |           | - 44 <b>-</b> |          |                  |       | 6       | DC12 (mo      | ost commo   | n)                 | S <sub>dd11</sub> | S <sub>dd12</sub> | S <sub>doll</sub> S | S <sub>dc12</sub> |        |

|    | 🗆 Noise    | :            | 0.0             | 000       | 😂 Vo          | lt (RM   | IS) Add Noise    |       | 0       | CD12          |             |                    | S <sub>dd21</sub> | S <sub>dd22</sub> | S <sub>dc21</sub> S | S <sub>dc22</sub> |        |

|    | Pre/D      | e-emphasi:   | 4.0             | 000       | 🛟 di          | 8 🔻      | ·                |       | 0       | 12DC          |             |                    |                   |                   |                     |                   |        |

|    |            |              |                 |           |               |          | _                |       |         |               |             |                    | S <sub>cd11</sub> | S <sub>cd12</sub> | S <sub>cc11</sub> S | Scc12             |        |

|    |            |              |                 |           |               |          |                  |       |         | 12CD          |             |                    | S <sub>cd21</sub> | S <sub>cd22</sub> | S <sub>cc21</sub> S | S <sub>cc22</sub> |        |

|    |            |              |                 |           |               |          |                  |       |         |               |             |                    | L                 |                   |                     | -                 | 1      |

|    |            |              |                 |           |               |          |                  |       |         |               |             |                    |                   |                   |                     |                   |        |

|    |            |              |                 |           |               |          |                  |       |         |               |             |                    |                   |                   |                     |                   |        |

**Tektronix**<sup>®</sup>

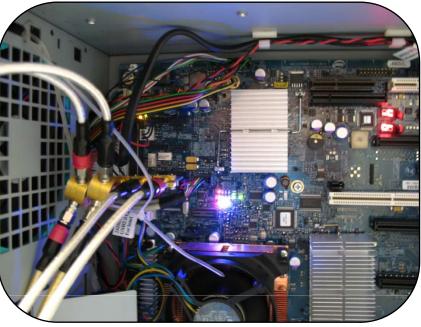

#### Serial ATA Revision 3.0 Receiver Testing

- Leading portfolio of Tektronix test instruments

- Oscilloscopes with advanced jitter and link analysis software

- Signal generators with stressed pattern generation software

- Tektronix Arbitrary Waveform Generator (6 Gb/s AWG)

- Integrated DUT state control for disconnect-free solution

- Digital Synthesis of CIC receiver ISI components with variable control.

- Simplified SSC generation of complex dF/dT impairments or other modulation modeling needs

- High Sinusoidal Jitter generation ability (0-100+UI, from *DC to Nyquist*!)

- PHY Receive Signal Requirements

- **RSG-01:** Gen1(1.5 Gb/s) Receiver Jitter Tolerance Test (Normative)

- RSG-02: Gen2(3.0 Gb/s) Receiver Jitter Tolerance Test (Normative)

- **RSG-03:** Gen3(6.0 Gb/s) Receiver Jitter Tolerance Test (Informative)

- **RSG-05:** Asynchronous Receiver Stress Test at +350 ppm (Informative)

TekExpress Serial ATA Revision 3 Solution

Tektronix<sup>®</sup> Innovation Forum

#### Serial ATA Logo test futures

- dFdT (Phase modulation slew rate) has been approved in SATA through TP-03 for Tx testing. A reciprocal test for the Receiver is currently being piloted at the SATA IW#8 event in April 2010.

- The Tektronix AWG with it's digital waveform synthesis capability is leading the field of advanced modulation analysis. These tests expand the scope of conventional Receiver testing, while providing many insights into capabilities of the Phy's tracking architectures and how well it's is tuned for operating in a system environment where SSC noise and modulation issues can be significant.

## Complete Tektronix SATA/SAS Portfolio

| TekExpress Software                                                                                                                                                                               | Comprehensive System level                                                                                                            | Gen1-3 Instrument Automation |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| <b>RSG/RMT Tests</b><br>RSG/RMT- Receiver jitter and amplitude sensitivity compliance<br>and margin test.                                                                                         | AWG7122B with Opt.1, 6 and 8<br>SerialXpress Digital Signal Generation                                                                |                              |

| Rx/Tx Channel Tests         •Rx/Tx - Device and Host electrical channel performance,<br>Impedance and return loss         SI Cable Tests         •SI - Cable crosstalk, skew and frequency domain | DSA8200<br>80E08 TDR Sampling Module for DSA8200 Sampling<br>Scope<br>S-Parameter Analysis Software 80SICON Software for<br>DSA8200   |                              |

| PHY, TSG, and OOB Tests PHY – Signal timing stability and SSC analysis.                                                                                                                           | 80E08 TDR Sampling Module for DSA8200 Sampling<br>Scope                                                                               |                              |

| <ul> <li>PFY – Signal timing stability and SSC analysis.</li> <li>TSG – Transmitter AC parametric, Jitter, Amplitude.</li> <li>OOB- Out Of Band signal validation</li> </ul>                      | <b>DSA72004B</b><br>DPOJET Jitter Analysis software<br>SMA Adapters TCA-SMA 2 per scope<br>Differential SMA Probe P7313SMA (optional) |                              |

#### Resources

- What equipment do I need to test SATA and SAS?

- SATA:

www.tek.com/applications/serial\_data/sata/sata\_tests.html

– SAS:

www.tek.com/applications/serial\_data/sas/recommended\_equipment.html

- How can I learn more about SATA/SAS testing?

- Tektronix SATA Knowledge Center: www.tektronix.com/SATA

- Tektronix SAS Knowledge Center: www.tektronix.com/SAS

- SATA International Organization: www.serialata.org

- SCSI Trade Association: www.scsita.org

- T10 Technical Committee: www.t10.org

- University of New Hampshire Interoperability Lab: www.iol.unh.edu/services/testing/sas

## Enabling Innovation in the Digital Age

#### **Accelerating Performance**

Enabled by High-speed Serial Technologies

#### Integrated Instrument BERT

- Tektronix DPO/DSA/MSO 72004B/71604B/71254B Oscilloscopes offer a variable rate Frame Error and Bit Error Detector integated into the base instrument trigger system which can operate from 1.5G to 6.25G. This is an instrument setup used in conjunction with the High Speed Serial Trigger (STU) option.

- Released to SATA-IO in Tek RSG MOI on January 15, 2010. Certified by SATA-IO on April 8 2010.

|         | lit ∣ Vert        | tical           | Horiz/Acq                                | Trig      | Display | Cursors | Measure     | Mask     | Math   | MyScope                 | Analyze        |

|---------|-------------------|-----------------|------------------------------------------|-----------|---------|---------|-------------|----------|--------|-------------------------|----------------|

| E Sta   | tus: C            | our             | nting/Sig                                | nal/L     | ocked/  | maxAP   | _0K '       | -  <br>: | 1 1    |                         |                |

| E FE    | ors: U<br>Rate: ( | ın 1<br>0.00    | 509ॅ103ॅ6<br> 0000e+0                    | 0<br>00 m | axAPs   | :2      |             |          |        |                         |                |

| E Cha   | aracte            | er Er           | rors: 0                                  |           |         |         |             |          |        |                         |                |

| E-Dis   | parity            | ' Err           | rors: 0                                  |           |         |         |             |          |        | · · +                   |                |

| E- ·    |                   |                 |                                          |           |         |         |             |          |        | · · ‡                   |                |

| ₽~      |                   | <b>⊢</b> †<br>∶ |                                          | -+        |         | + + +   |             | +        |        | -+-+ <del>+</del><br>   |                |

| E ·     |                   |                 |                                          |           |         |         |             |          |        | · · ‡                   |                |

| E ·     |                   |                 |                                          |           |         |         |             |          |        | · · ‡                   |                |

| Ē.      |                   |                 |                                          |           |         |         |             |          |        | · · ‡                   |                |

| Ē.      |                   |                 |                                          |           |         |         |             |          |        | · · +                   |                |

| Ē.      |                   | i İ             |                                          | , i       | 1 1     | i i İ   |             | , i      | 1 1    | <u>, , ‡</u>            |                |

| C1      | <b>) 100m</b>     | ∩V/di           | v t                                      | 50Ω B     | w:16.0G |         |             |          |        |                         |                |

|         |                   |                 |                                          |           |         |         |             |          |        |                         |                |

|         |                   |                 |                                          |           |         |         |             |          |        |                         |                |

|         |                   |                 |                                          |           |         |         |             |          |        |                         |                |

|         |                   |                 |                                          |           |         |         |             |          |        |                         |                |

| 8°      |                   | Т               | rigger - S                               | Serial    | Patterr | 1       |             |          |        |                         |                |

| 2°<br>  | Event             | Т               |                                          |           |         |         |             | )ata Sr  | c.     | Stan                    | dard           |

|         | Event<br>>B Seq   |                 | Trigger - S<br>Trigger T<br>Serial       |           |         | Clk Src | [<br>▼ Ch 1 | )ata Sr  | c<br>V | Stan<br>Custom          | dard           |

| Δ-      |                   |                 | Trigger T                                |           |         | Clk Src | ▼ Ch 1      |          | ۲      |                         |                |

| A-<br>B | >B Seq<br>Event   |                 | Trigger T                                | ype<br>▼  |         | Clk Src | ▼ Ch 1      | Coding   | ۲      | Custom                  | Rate           |

| A-<br>B | >B Seq            |                 | Trigger T<br>Serial                      | ype<br>▼  |         | Clk Src | ▼ Ch 1      | Coding   | ▼<br>  | Custom<br>Bit F         | Rate           |

| A-<br>B | >B Seq<br>Event   |                 | Trigger T<br>Serial                      | ype<br>V  |         | Clk Src | ▼ Ch 1      | Coding   | ▼<br>  | Custom<br>Bit F         | Rate           |

| A-<br>B | >B Seq<br>Event   |                 | Trigger T<br>Serial<br>Select            | ype<br>V  |         | Clk Src | ▼ Ch 1      | Coding   | ▼<br>  | Custom<br>Bit F<br>5.00 | Rate           |

| A-<br>B | >B Seq<br>Event   |                 | Trigger T<br>Serial<br>Select<br>Setting | ype<br>V  |         | Clk Src | ▼ Ch 1      | Coding   | ▼<br>  | Custom<br>Bit F<br>5.00 | Rate<br>ib/s ( |

| A-<br>B | >B Seq<br>Event   |                 | Trigger T<br>Serial<br>Select<br>Setting | ype<br>V  |         | Clk Src | ▼ Ch 1      | Coding   | ▼<br>  | Custom<br>Bit F<br>5.00 | Rate<br>ib/s ( |

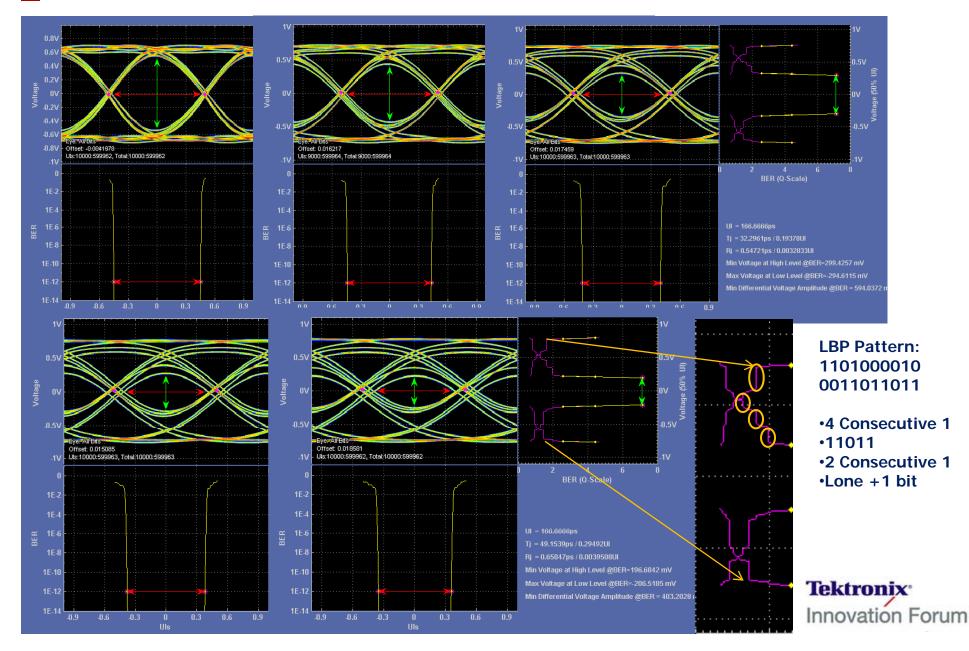

#### Eye Waveform Synthesis Fidelity Progressive Impairment of a SATA Gen3 (6Gb/s) Lone Bit Pattern

#### **Additional Material**

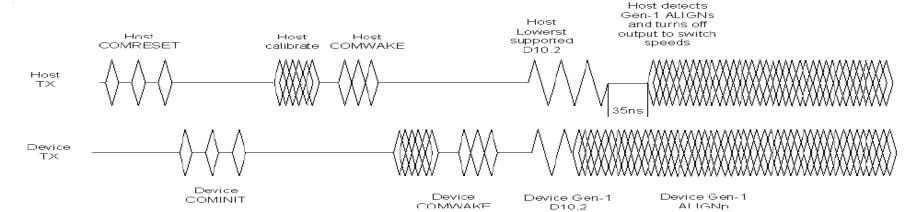

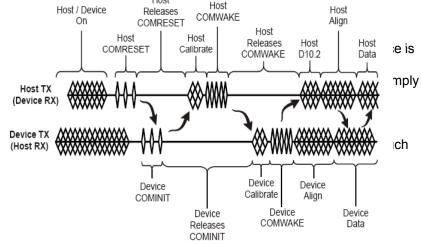

AWG based sequences referred to as BIST-L initiators are used to negotiate the devices and hosts LSTM.

|              | P6                | DP6:     |      | Davias        |                    | and an all a |

|--------------|-------------------|----------|------|---------------|--------------------|--------------|

| Go To        | Event Jump To     | Repeat   | Wait | Ch 2 Waveform | Ch 1 Waveform      | Index No     |

|              |                   | 10       |      | Empty         | IDLE-12x           | 1            |

|              |                   |          |      | Empty         | crs01+_16x-24Gs    | 2            |

|              |                   | 10       |      | Empty         | IDLE-12x           | 3            |

|              |                   |          |      | Empty         | cwke01+_x16_24Gs   | 4            |

|              |                   | 5        |      | Empty         | IDLE-12x           | 5            |

|              |                   | 20       |      | Empty         | D10_2710_24Gs      | 6            |

|              |                   | 400      |      | Empty         | -align_32_24Gs     | 7            |

|              |                   | 65000    |      | Empty         | -sync_256_al2_24Gs | 8            |

|              | Comm-Reset        | 65000    |      | Empty         | -sync_256_al2_24Gs | 9            |

| ck) Activate | Speed Negotiation | 65000    |      | Empty         | -sync 256 al2 24Gs | 10           |

|              | BIST-FIS (LOOPDA  | 100      |      | Empty         | -r rdy32 24Gs      | 11           |

|              |                   |          |      | Empty         | -align_32_24Gs     | 12           |

|              |                   | 10       |      | Empty         | -r_rdy32_24Gs      | 13           |

|              |                   | 2        |      | Empty         | -r ip32 24Gs       | 14           |

|              |                   | 2        |      | Empty         | -r ok32 24Gs       | 15           |

|              |                   | 10       |      | Empty         | -align 32 24Gs     | 16           |

|              |                   | 10       |      | Empty         | -sync 256 al2 24Gs | 17           |

|              |                   | 20       |      | Empty         | -x rdy32-24Gs      | 18           |

|              |                   |          |      | Empty         | -SOF 24Gs          | 19           |

|              | Next              | Infinite |      | Empty         | -HF-32Dword 24Gs   | 24           |

| atterns      | Next Test pa      | Infinite |      | Empty         | Gen3-FCP-2A-Clean  | 25           |

| 25           |                   |          |      | Empty         | Gen3-FCP-2A-1Err   | 26           |

|              | lektron           |          |      |               |                    |              |

## Serial ATA Compliance Test Solution

Advanced Technical FAQ

#### Training: BIST-T –vs- BIST-L

BIST-T (Built In Self Test) – Transmit: Optional capability (not supported on all devices) which allows an 80 bit sequence to be broadcast from a phy's transmitter channel.

Advantages: Ultra low cost method of getting simple patterns out of a device (HFTP, MFTP, LBP etc).

No Align primitives inserted into data stream

Disadvantages: Not all silicon supports this mode of operation.

Pattern is very short. No crosstalk Can only test Phy/TSG/RxTx with this mode of operation. Hosts typically require proprietary SW tools to enable this mode.

BIST-L (Built In Self Test) –Loopback: Required capability (devices are non SATA spec compliant without this) which accepts a signal on it's receiver, retimes it to the local device clock domain, and transmits the received signal out the transmitter.

Advantages: All devices are required to support this mode of operation.

Allows devices to broadcast complex patterns with easy external control. We send it the pattern we want the device to broadcast and it copies the received signal on it's transmitter.

This test mode is fundamental to testing receivers.

Disadvantages: Requires additional equipment cost for an external generator

Sometimes loopback modes include ALIGN primitives in the returned signal stream.

TekExpress Position:

By using the "Manual BIST" mode of operation and pausing the system on the DUT power-cycle Drive-Master or Intel's NAZBist can be used today, to issue a BIST-T command and have the DUT broadcast the required pattern. BIST-T mode of operation is supported today for the PHY/TSG and RxTx tests today provided that user intervention is acceptable to the user.

# Serial ATA Compliance Test Solution ASR

Advanced Technical FAQ

ASR (Asynchronous Recovery): This is a silicon based feature which detects a number of error conditions and resets the link based on these conditions.

- 1. Disconnect detected

- a. Loss of Data Sync condition

- b. ComReset (DC input signal for more than 20mSec).

This is an important architectural feature designed to allow devices to automatically reestablish a link condition should it be dropped for any reason.

The down side of this feature is that it makes testing nearly impossible (unless you use an AWG7102 or AWG7122B) it this capability is enabled.

30-40% of the silicon in industry today has this feature turned on.

Why does ASR interfere with testing?

ASR interferes with testing when one is required to use an external BIST initiation tool such as Drive Master or Intel's NAZ-Bist tools to set the test state. At which point you need to disconnect from the device and attach a test stimulus system (BERT, pattern generator etc). This disconnect triggers ASR and resets the device.

The AWG seamlessly initiates the BIST-L state and proceeds to testing with the required test pattern, without ever triggering the ASR circuitry. Competitors use power splitters, or solid state switches to get around this problem, but you now have additional hardware between the Tx source and the DUT.

#### Serial ATA Compliance Test Solution OOB Channel Calibration

The OOB (Out of Band signaling) phase:

The OOB sequence is a multi stage sequence designed to put a SATA Phy into a suitable starting state. It negotiates line rate (Gen1-Gen3) between a host and a drive or port-multiplier. There is a critical step here called "Power-On Calibration" where the source impedance is adjusted once during startup to adapt to the line conditions presented by that host, cable and device pairing (adaptive equalization). Once OOB competes, no further line conditioning is performed. If ones uses a bus analyzer or PC to put the DUT into a test state, and then disconnects and attaches a BERT (what is commonly done) the line conditions change radically. The internal adapted source impedance settings are not meant for a BERT configuration yielding different results than if the AWG initiates the OOB and BIST-L test states and not detached through the course of the

#### measurements..

SATA 2.6G Spec page 2 7.4.21 OOB Signaling Te: OOB signaling is used to in an active mode, a low i This section specifies the to the OOB signaling seq 7.4.21.1 Power-On Seque 7.4.21.1.1 Calibration When the host controller that the electrical requirer

Advanced Technical FAQ