## **Explore BERTScope's Benefit In High Speed Serial Data**

### Agenda

- BERTScope In High Speed Serial Data

- USB 3.0 Compliance Testing

- SATA Compliance Testing

- PCIE Rx & PLL Loop bandwidth Testing

- One Stop Shopping for HSSD from Tektronix

## BERTScope's Applications In High Speed Serial Data

**USB 3.0 Rx Compliance Testing**

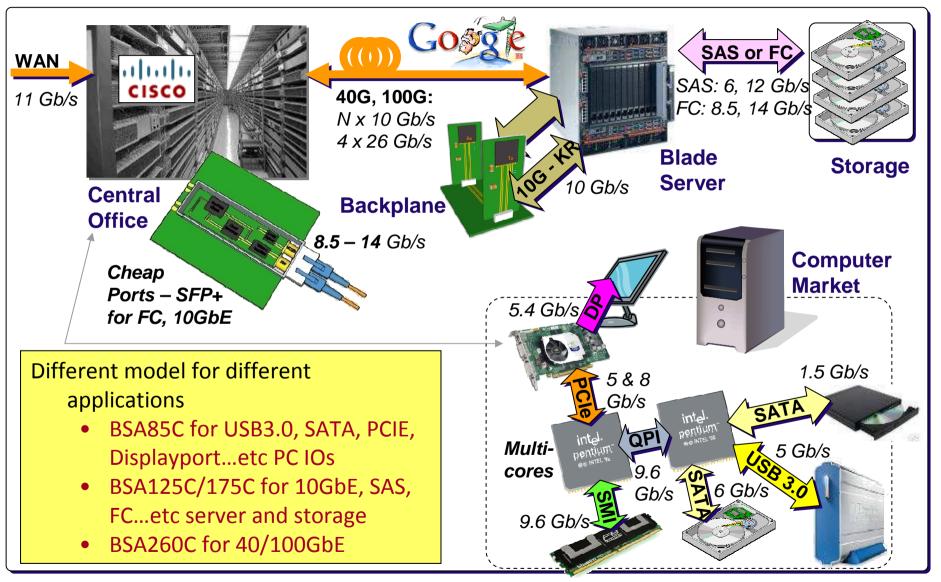

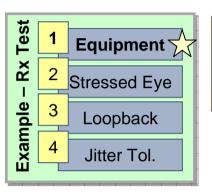

### USB 3.0 Receiver Test Flowchart

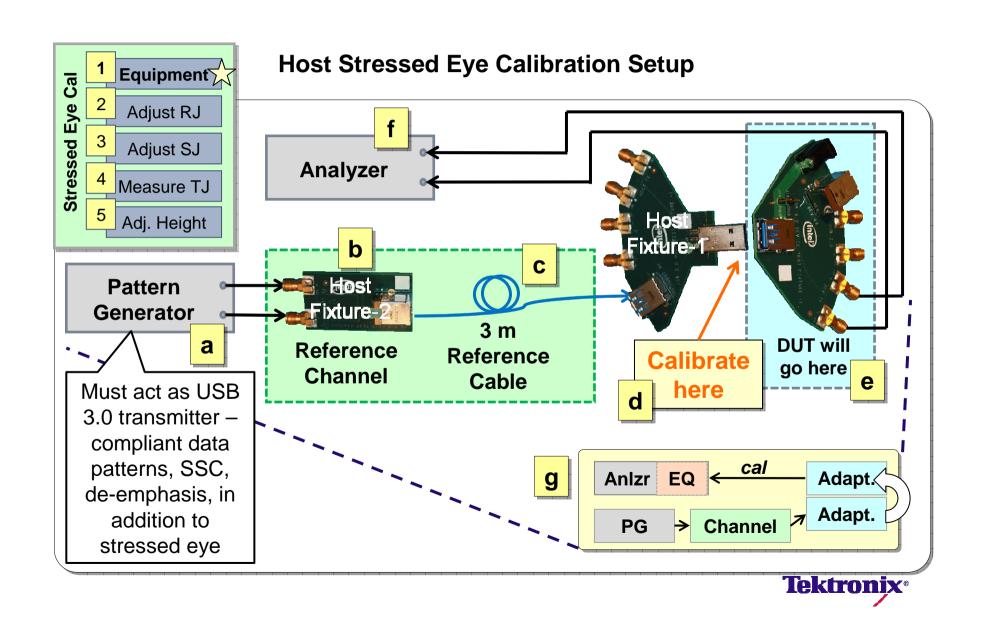

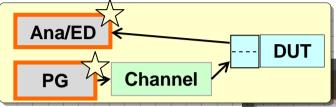

## USB 3.0 Stressed Eye Calibration Equipment Setup

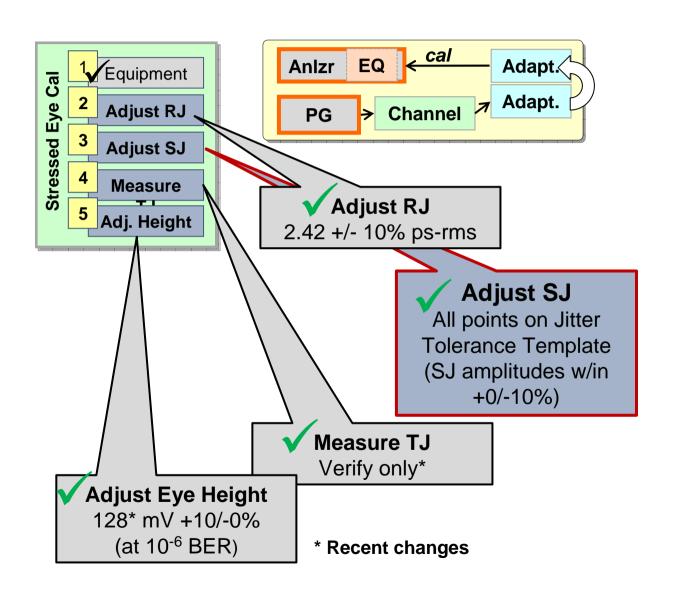

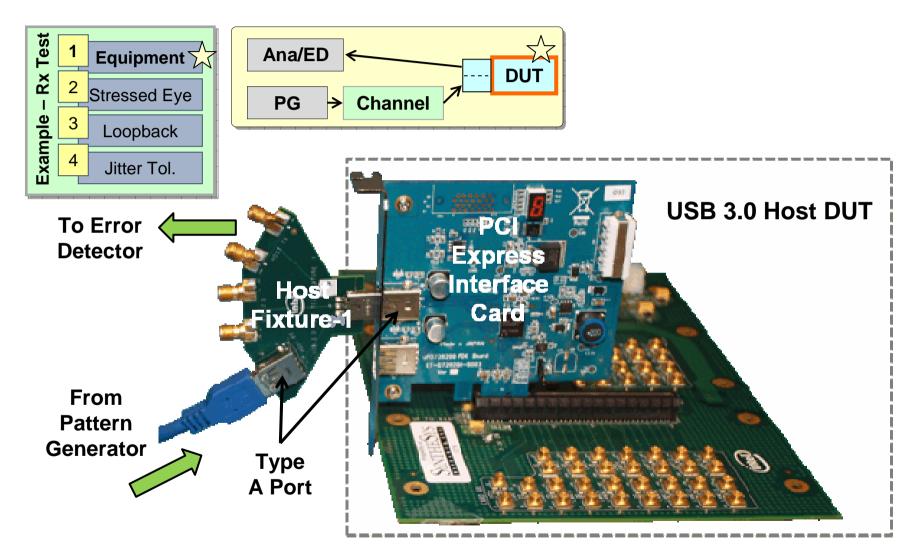

## USB 3.0 Stressed Eye Calibration Jitter and Eye Height

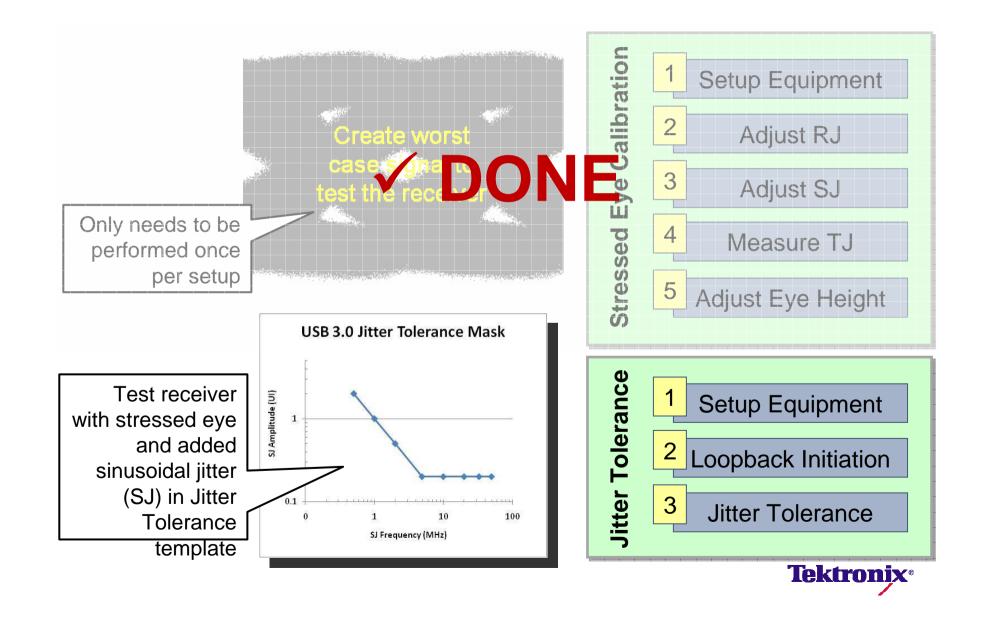

### USB 3.0 Receiver Test Flowchart

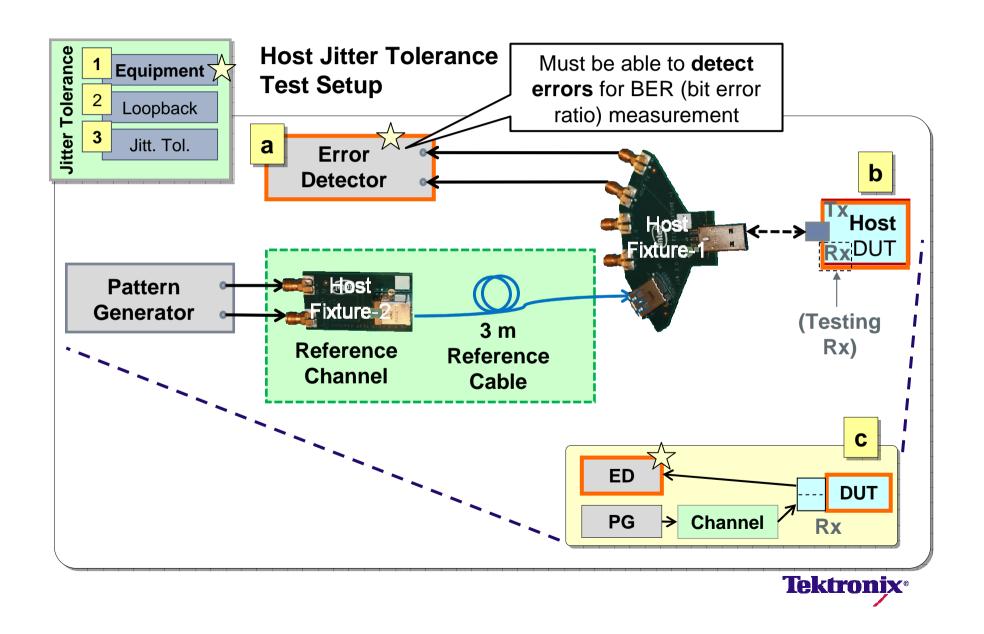

# USB 3.0 Jitter Tolerance Testing Equipment Setup

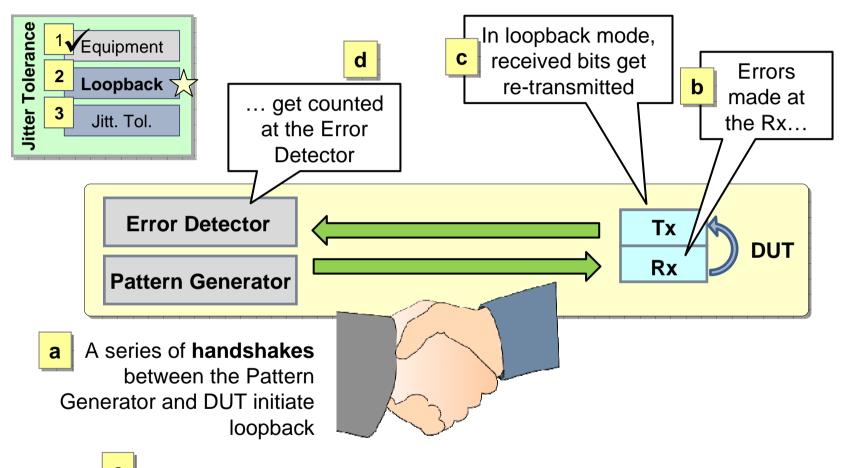

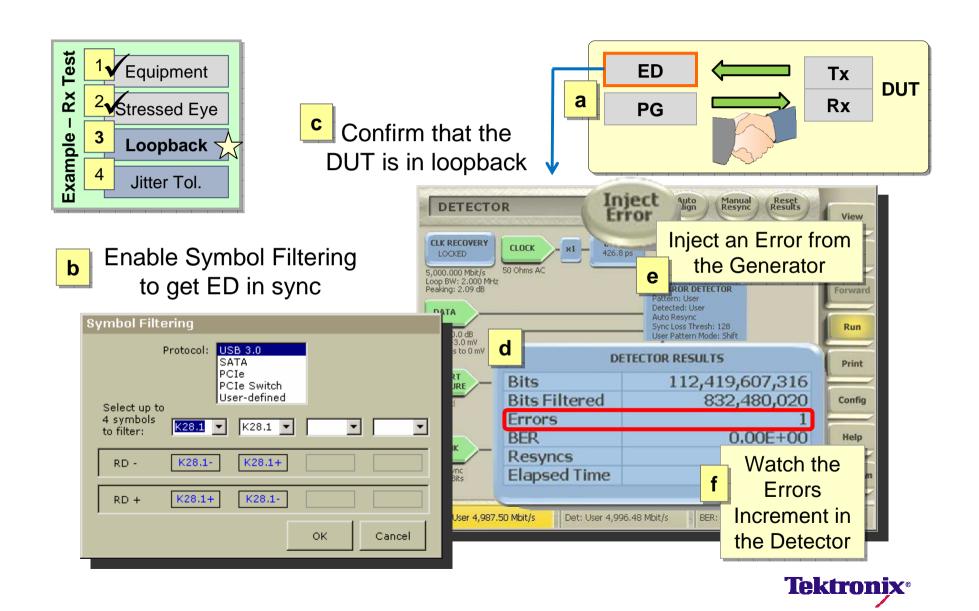

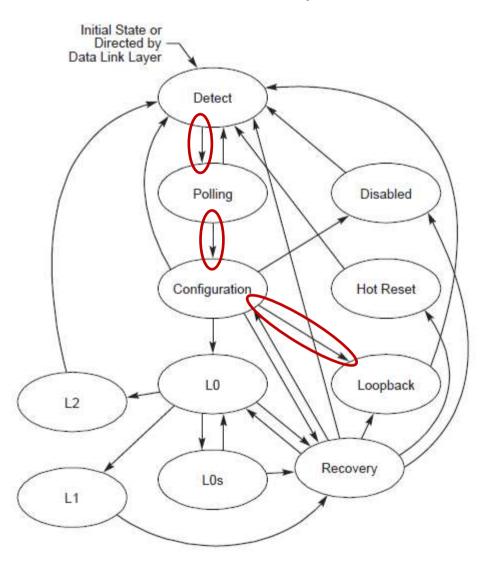

## USB 3.0 Jitter Tolerance Testing Loopback Initiation

Notes:

1. Once in loopback, the DUT should not exit loopback unless directed

2. "Loopback BER", where the DUT keeps track of its own BER, is not required for compliance testing

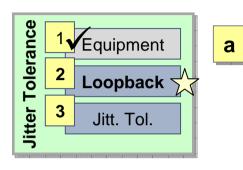

## USB 3.0 Jitter Tolerance Testing Asynchronous BER Testing

Clock compensation symbols (SKPs) are used to adjust for the differing clock frequencies in the received data vs. the transmitter (common in 8b/10b systems)

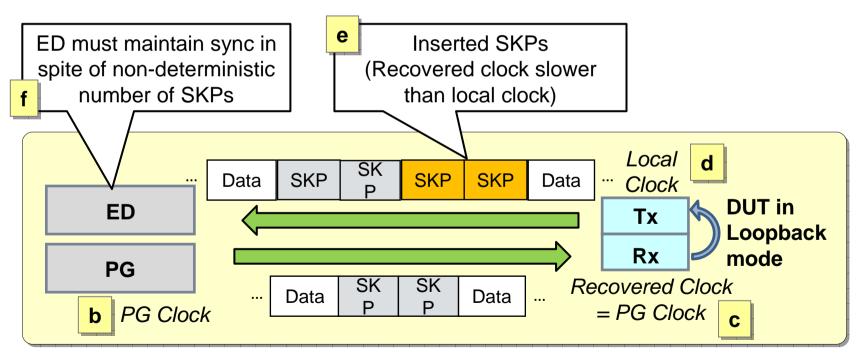

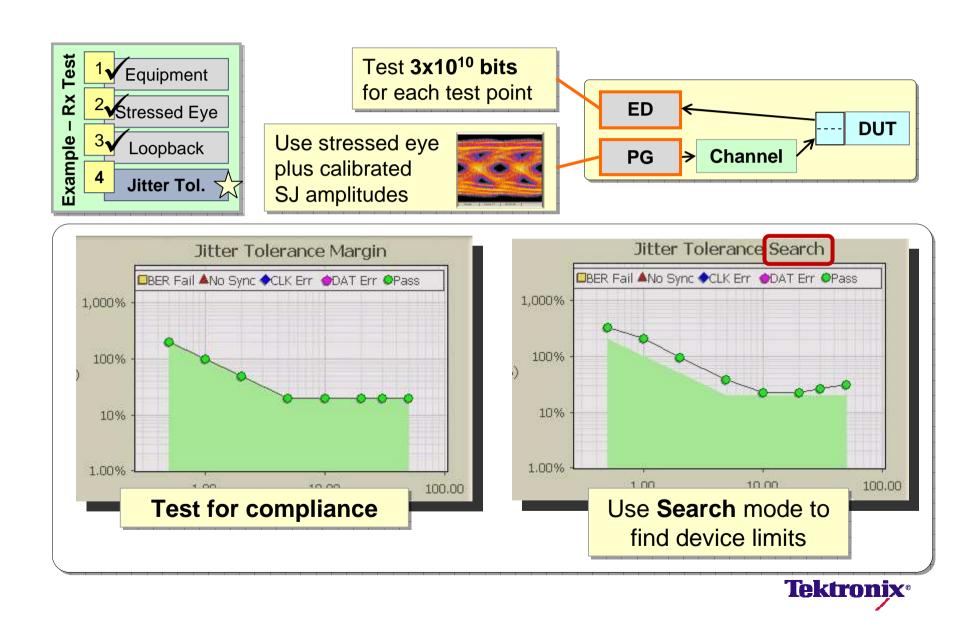

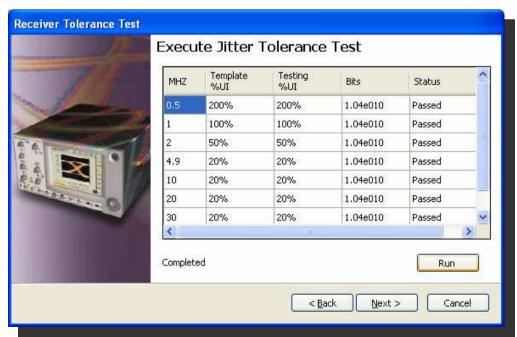

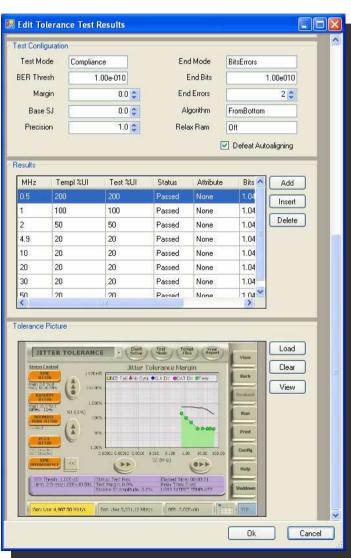

### USB 3.0 Run Jitter Tolerance

## USB 3.0 BERTScope Instrumentation

**BERTScope DPP** (3 and 4 tap) for compliant 3 dB de-emphasis

**BERTScope CR 125A** with Extended Loop Bandwidth Option for **compliant JTF**

pattern generation (RJ, SJ, and SSC) and BER analysis including jitter, eye height, CTLE emulation, asynchronous BER testing and automated Jitter Tolerance testing.

## USB 3.0 Host DUT

### USB 3.0 Stressed Eye Calibration Jitter

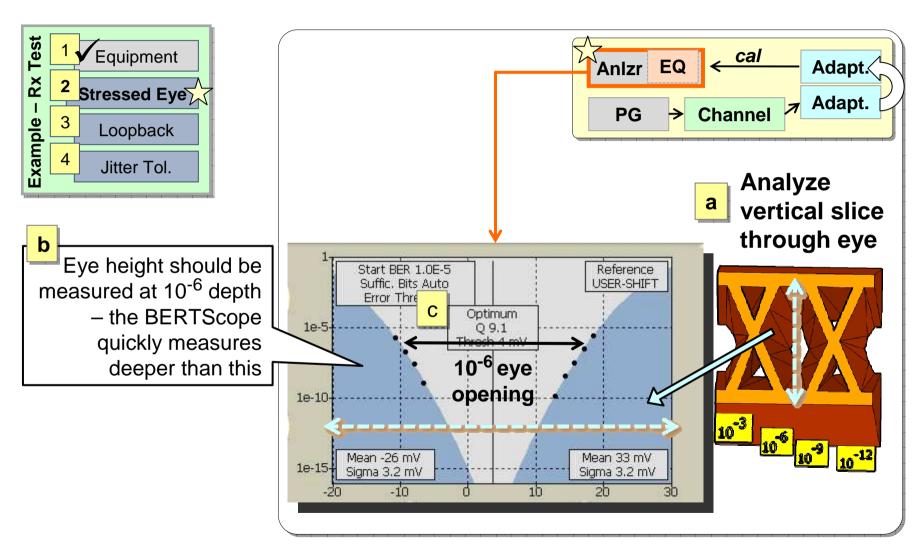

## USB 3.0 Stressed Eye Calibration Eye Height

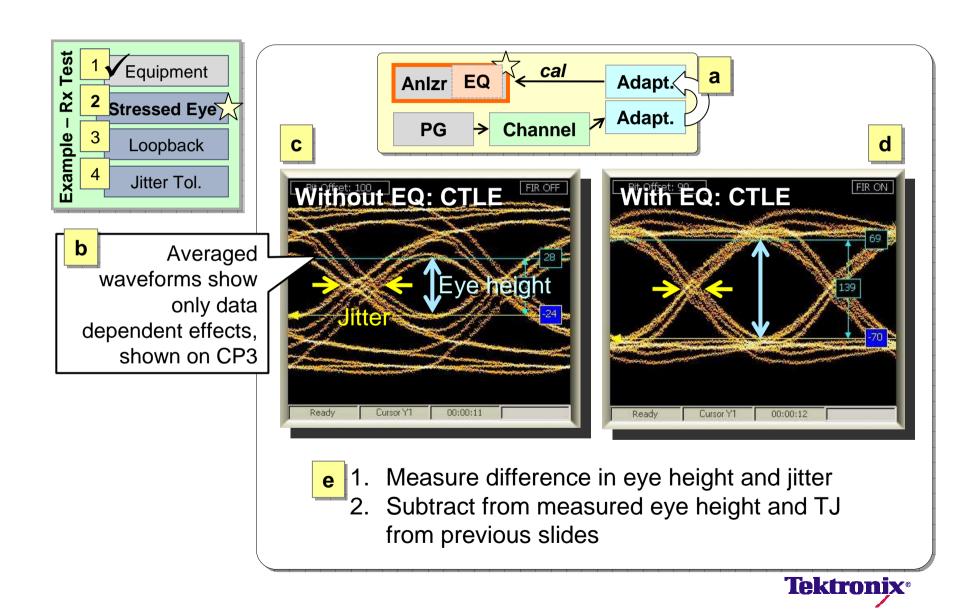

## USB 3.0 Stressed Eye CTLE Equalization Emulation

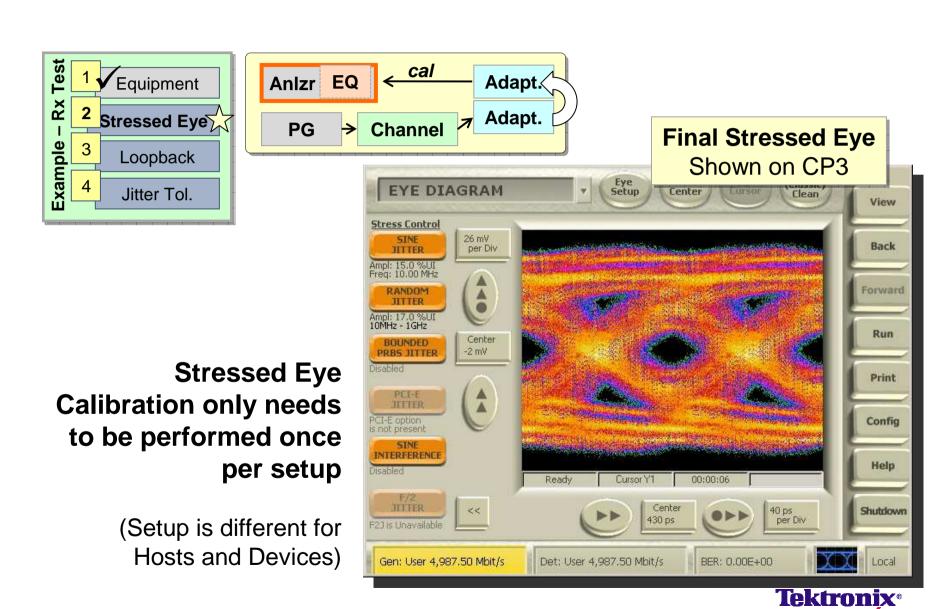

## USB 3.0 Final Stressed Eye

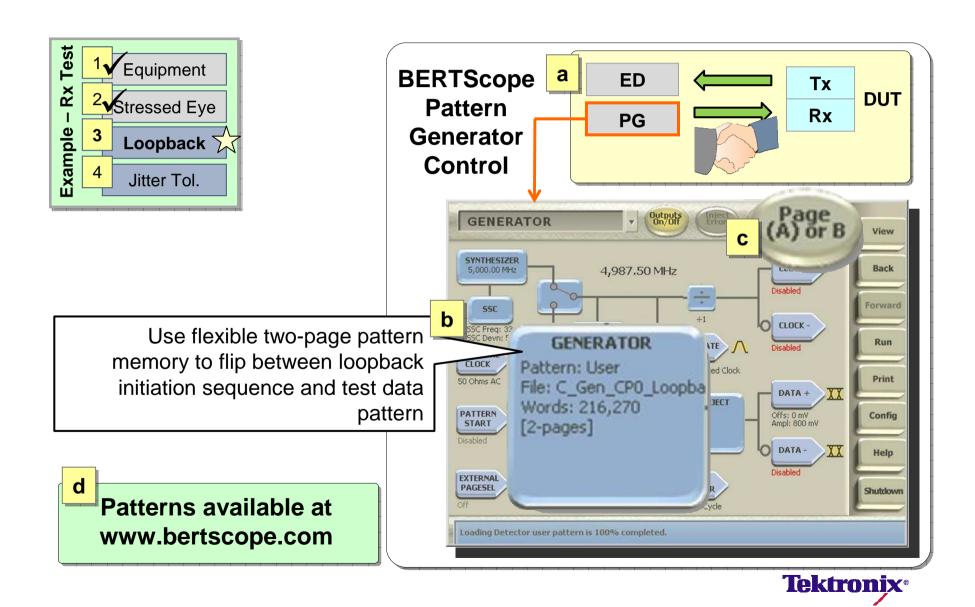

## USB 3.0 Loopback Initiation

## USB 3.0 Loopback Confirmation

### USB 3.0 Jitter Tolerance Test

## USB 3.0 Automation software (Coming Soon)

#### **USB 3.0 Automation Software**

- Automated stressed eye calibration

- •Fast automated receiver testing

- Easy loopback initiation

- Database back-end for fast report generation

## SATA Rx Compliance Testing

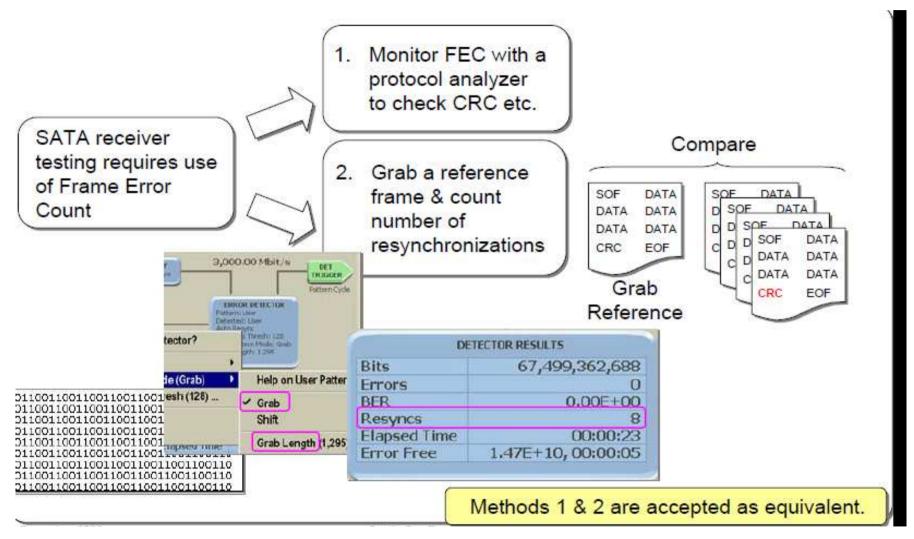

### SATA Frame Error Count

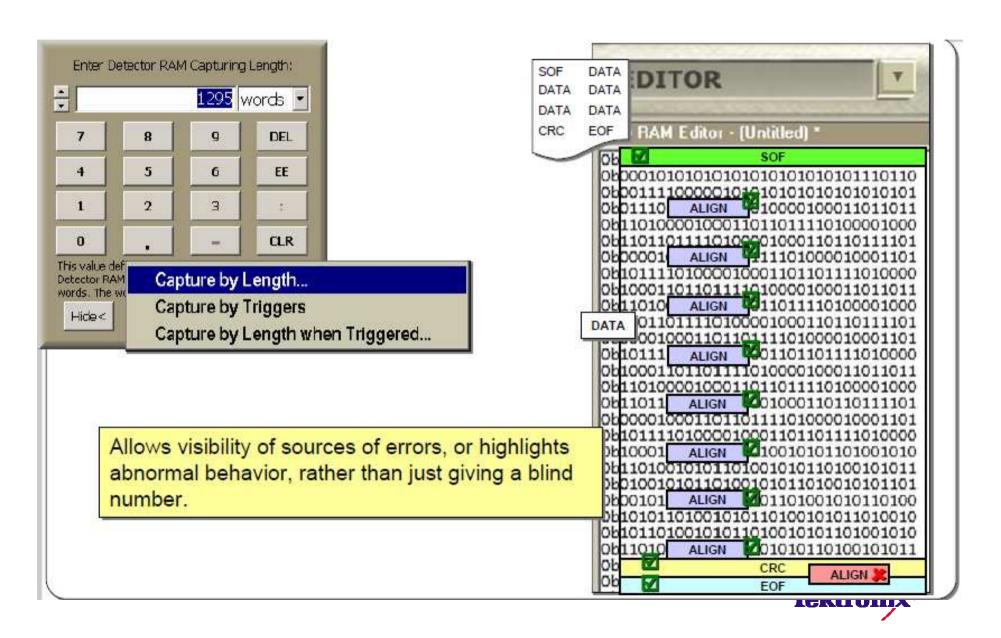

## SATA Grab Mode (Running Disparity)

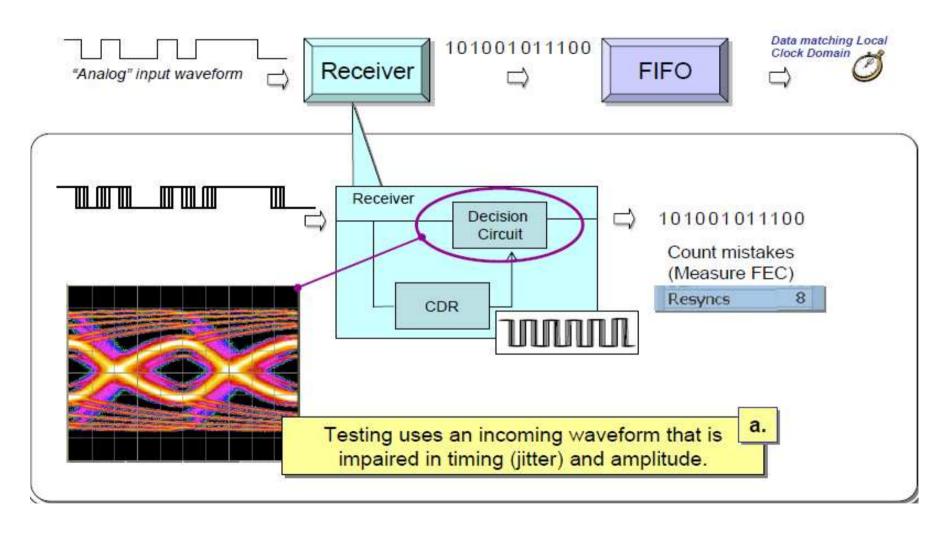

# SATA Testing Decision Circuit

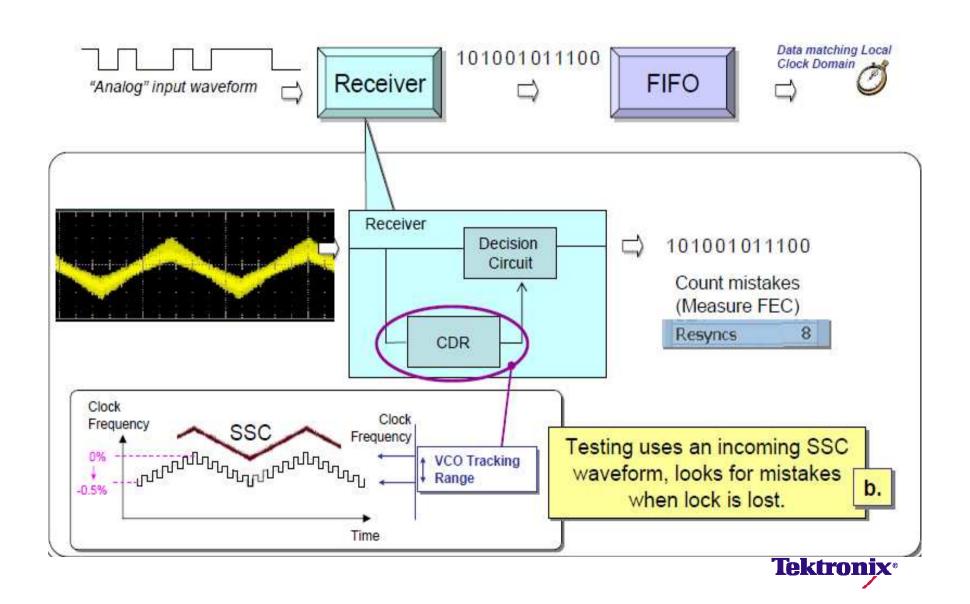

## SATA Testing CDR

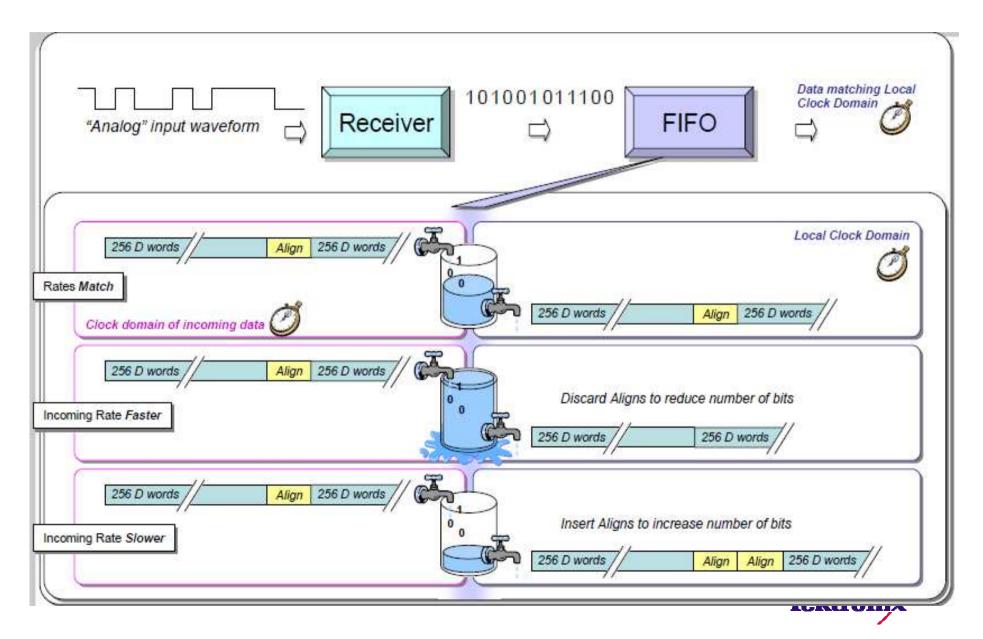

# SATA Testing FIFO (+-350ppm timing offset)

## SATA Compliance and beyond

#### Receiver Testing:

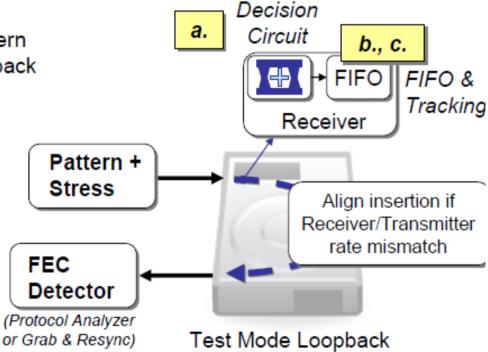

- 1. Generate stressed framed COMP pattern

- Received pattern retimed and looped back to output of transmitter

- If clock domains differ between received signal and system clock, aligns inserted.

- Increase impairments, mistakes detected in CRC etc. at FEC detector

- 5. Gives basic **Compliance**No information about where failures occurred, or individual margins

#### **Rx Impairments**

Test a. Added Jitter

Added Amplitude Closure

Test b., c. Frequency Offset (350ppm)

SSC Profile

#### Beyond Compliance – margin testing

- By keeping clock domains the same, can stop aligns being added and see the effect of different stress types.

- Can analyze margin in different parts of the receiver.

## PCIE Rx Compliance testing

All information in these slides are based on the PCI-Express draft 0.71

## PCI Express Agenda

- PCIe Gen3 Receiver Testing

- Stressed Voltage Eye

- Stressed Jitter Eye

- Speed and Equalization Auto-Negotiation

- PLL Loop Bandwidth Testing

## PCIe Gen3 Receiver Testing

- Split up into testing with two types of stressed eye

- 1. Stressed Voltage Eye

2. Stressed Jitter Eye

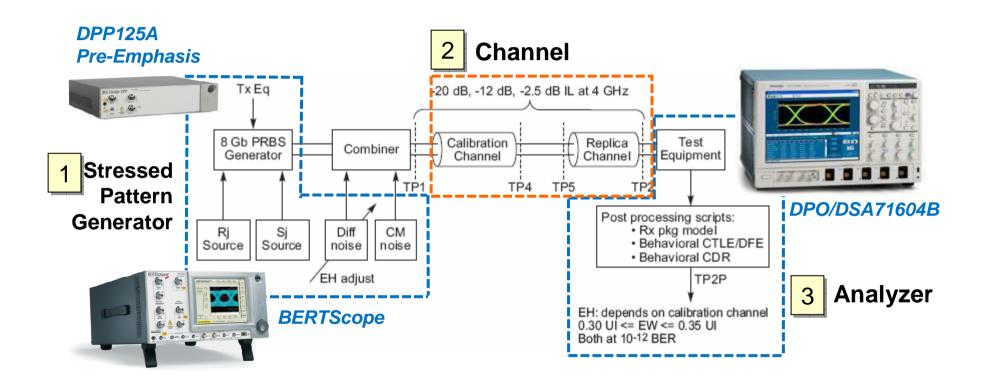

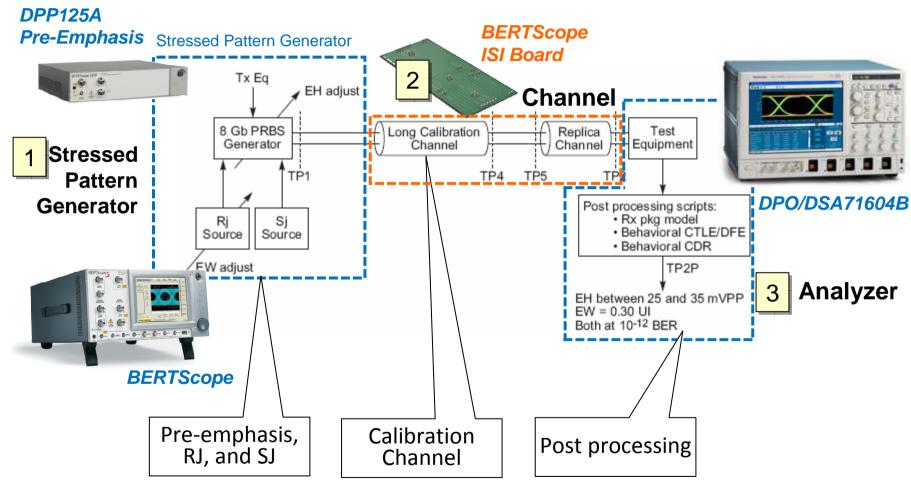

## PCIE Gen3 Stressed Voltage Eye Calibration

## PCIE Gen3 Stressed Voltage Eye Stressed Pattern Generation

## PCIE Gen3 Stressed Voltage Eye Analyzer

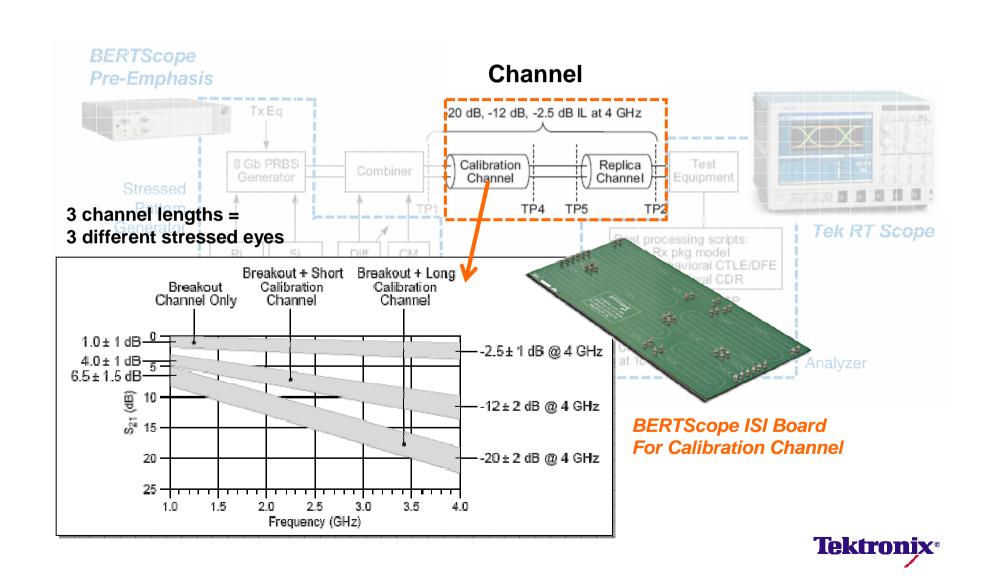

## PCIE Gen3 Stressed Voltage Eye Channel

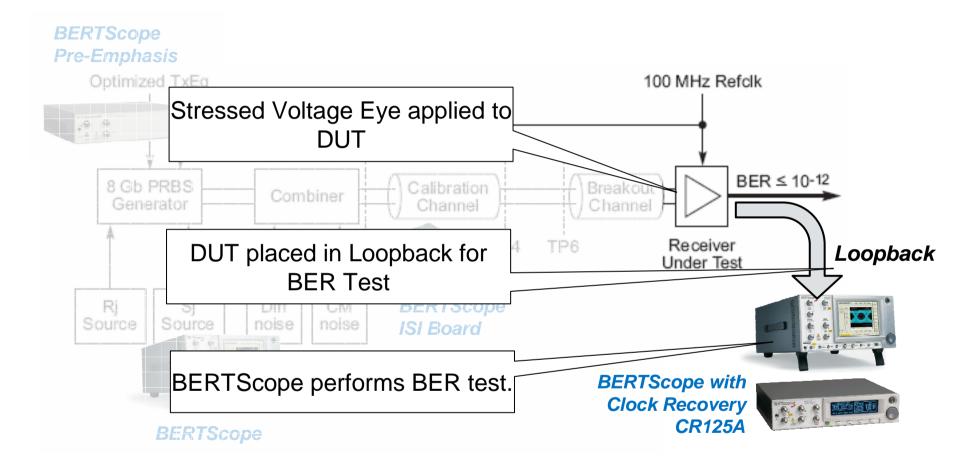

## PCIE Gen3 Stressed Voltage <u>Test</u>

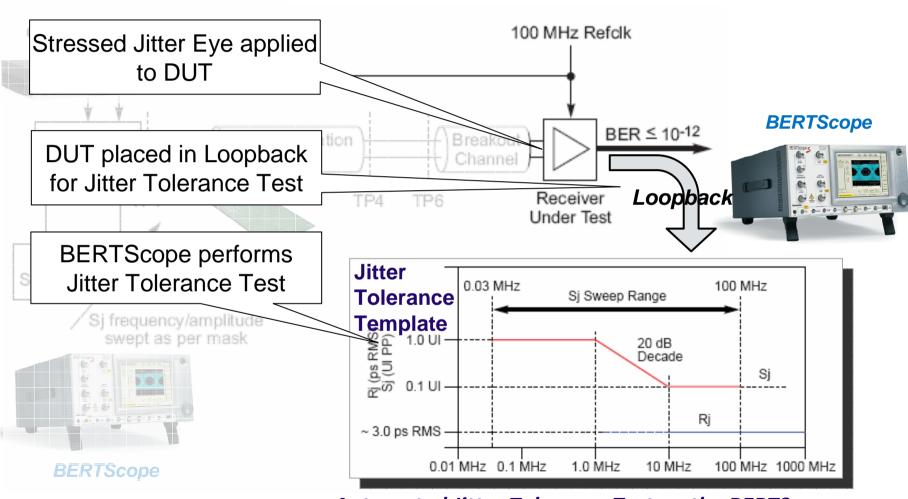

## PCIE Gen3 Stressed <u>Jitter</u> Eye Calibration

Similar requirements as the Stressed Voltage Eye

# PCIE Gen3 Stressed Jitter <u>Test</u> *Jitter Tolerance*

Automated Jitter Tolerance Test on the BERTScope, with Search Mode to find device limits

**Tektronix**®

## Summary of BERTScope Rx Test Capabilities for PCle Gen3

BERTscope Stressed Pattern Generation

- ✓ Random Jitter

- ✓ Sinusoidal Jitter

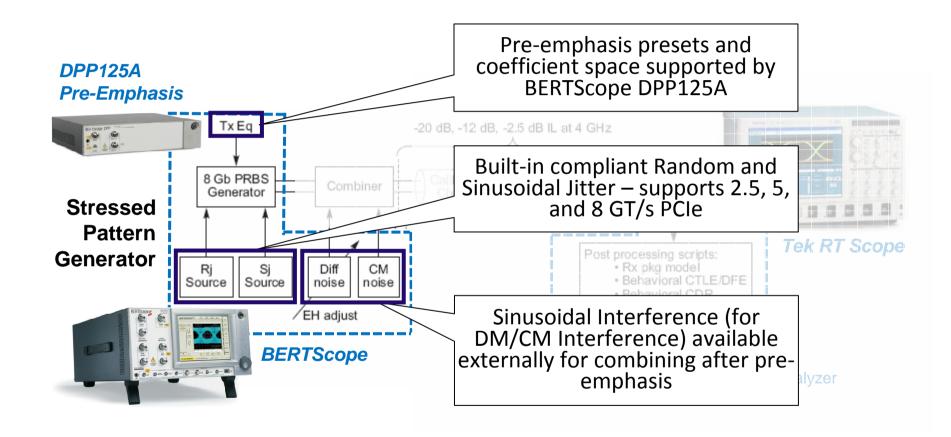

- ✓ Pre-emphasis (DPP125A)

- ✓ Differential Mode Interference

- ✓ Common Mode Interference

- ✓ Calibration Channel (ISI Board)

- BERTScope Error Detection

- ✓ Clock Recovery (CR125A)

- ✓ Automated Jitter Tolerance Test

- ✓ BER testing

- The BERTScope Family of Products provides the stresses needed for PCle Gen3 with unrivaled ease of use, so engineers can quickly debug issues and find device margins

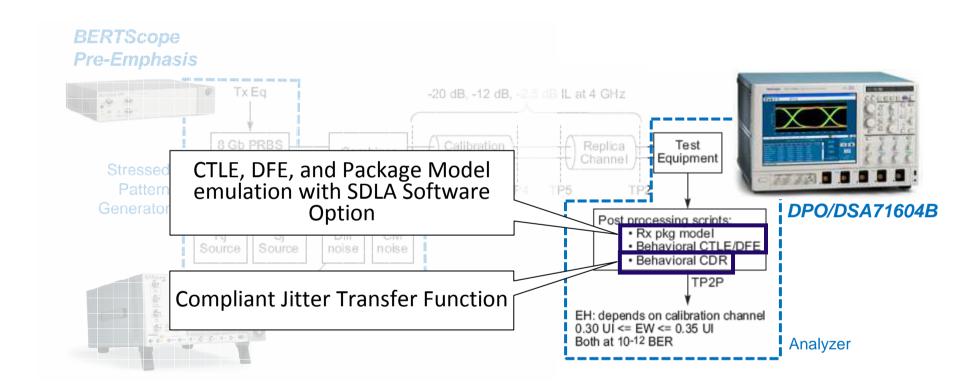

# Summary of BERTScope Rx Test Capabilities for PCle Gen3 (Continued)

- Oscilloscope (for Stressed Eye Calibration)

- ✓ CTLE

- ✓ DFE

- ✓ Behavioral package emulation

- ✓ Clock Recovery for Compliant Jitter Transfer Function

**DPO/DSA71604B**

The Tektonix DPO/DSA71604B provides compliant embedding of the Receiver equalization for accurate measurements as would be seen at the latch of the Receiver, providing the right feedback to the BERTScope Stressed Pattern Generator during Stressed Eye Calibration

## PCIE Gen3 Agenda

- PCIe Gen3 Receiver Testing

- Stressed Voltage Eye

- Stressed Jitter Eye

- Speed and Equalization Auto-Negotiation

- PLL Loop Bandwidth Testing

## PCIE Gen3 Speed and Equalization Auto-Negotiation

- Devices must start up at 2.5 GT/s and negotiate up to 8 GT/s

- In PCIe Gen3, Receivers are expected to:

- 1. Optimize their own equalization

- 2. Adjust the Transmitter's pre-emphasis settings via back-channel communication

- Device equalization optimization algorithm will be key to PCI-Express Gen3 success, and we are here to help you test

#### PCIE Gen3

#### Speed and Equalization Auto-Negotiation with the BERTScope

- Use the BERTScope for R&D testing of new Gen3 devices

- Fixed data patterns can perform the speed negotiation to 8 GT/s and allow the user to check (manually) their DUT's equalization optimization routine

- With a fixed pattern, can get devices into Loopback for Receiver testing of early R&D Silicon

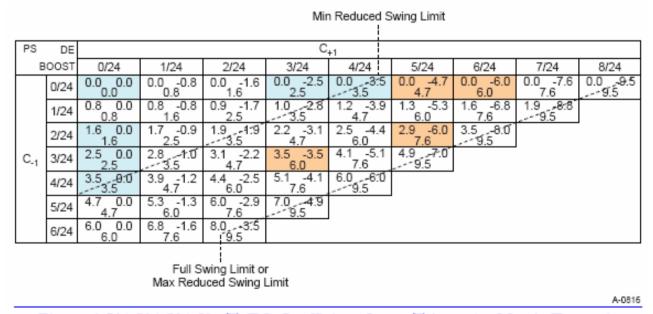

### PCIE Gen3 Transmitter Pre-emphasis

The DPP125A supports the allowable pre-emphasis settings (table below from draft 0.71)

The colored fields in the table are the "pre-sets" which are easily loaded from factory created configuration files

DPP125A

Figure 4-514-504-50: TxEQ Coefficient Space Triangular Matrix Example

## PCIE Gen3 Agenda

- PCIe Gen3 Receiver Testing

- Stressed Voltage Eye

- Stressed Jitter Eye

- Speed and Equalization Auto-Negotiation

- PLL Loop Bandwidth Testing

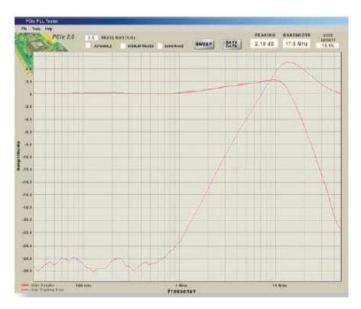

## PCIE Gen3 PLL Loop Bandwidth Test

- The BERTScope CR125A-PCIE is the test instrument used for PCI-Express Gen2 PLL Loop Bandwidth testing (2.5 and 5 GT/s) at the Compliance Workshops

- Clock recovery capability at 8 GT/s facilitates testing of Gen3 devices

- Higher speed models support 16 GT/s for future PCIe Gen4

## PCIE Gen3 Summary

- Receiver testing is expected to be mandatory and will include testing with a Stressed Voltage and Stressed Jitter Eye

- Equalization auto-negotiation controlled by the Receiver is new for Gen3

- Tektronix can provide solutions for many aspects of receiver testing to PCIe Gen3 today

- Tektonix, including the BERTScope, has a strong history providing test solutions for PCI-Express – one that we plan to continue

- The BERTScope supports data rates to 8.5G, 12.5G, and 17.5G for current and future PCIe projects

- Contact us for further details on our plans for Gen3 support

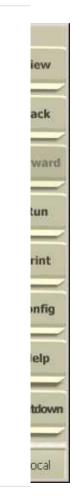

## One Stop Shopping For HSSD From Tektronix

| Transmitter Tests Transmitter jitter and timing measurements.                                                                                              | DSA/DPO/MSO 71254B / MSO71254 or higher bandwidth  Opt. USB-TX (TekExpress Automation and DPOJET Measurements)  Opt. DPOJET Jitter and Eye Diagram Analysis Tool  TF-USB3-AB-KIT (Host and Device Test) or TF-USB3-A-P (Host Test) or TF-USB3-A-R (Device Test) Test Fixture | Many 2012 (Alles and 1922) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Receiver Tests: Signal Generation / Error Detection  Receiver Jitter Tolerance Tests for Customers working with HDMI, DP, MIPI  Flexible channel Emulation | AWG7122B w/ Opt. 6 and Opt. 8 and DSA/DPO/MSO 71254B / MSO71254 or higher bandwidth w/ Opt. STU and ERRDT  SerialXpress SDX100 opt. ISI and SSC TEKEXP USB-RMT for Full Automation TF-USB3-AB-KIT Test Fixture Kit                                                           |                            |

| Receiver Tests: Error Detection Receiver Jitter Tolerance Test and Debug and Analysis Tools                                                                | BERTScope BSA85C w/Opt. STR&PVU DPP125 CR125A with Opt XLBW & Opt CR125ACBL (Precision delay-matched cable set for use with BSA & CR in SSC applications)                                                                                                                    |                            |

| Interconnect/Cable Tests  Cable skew, Far End Noise, Near End Noise, cable and connector impedance, Insertion loss, and return loss measurements.          | DSA8200 80E08 TDR Sampling Module for DSA8200 2 per scope IConnect TDR and S-Parameter measurement software (80SSPAR) TF-USB3-AB-KIT Test Fixture Kit for Cable Test                                                                                                         |                            |