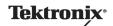

## Test Setup and Configuration

- All the tests are logically grouped based on the input source requirement

- WRITE

- CLOCK - ADDR/CMD

- Quickly set up the test configuration by selecting a complete group or individual tests

- Flexible input source requirement, inputs are not hardwired to a particular Oscilloscope channel.

Tektronix<sup>e</sup>

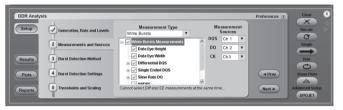

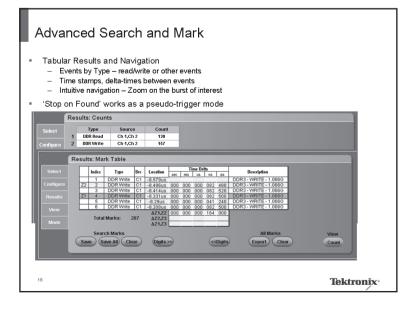

### **Burst Detection**

- Read / Write bursts are automatically detected for analysis purposes

- Several different techniques are used for Read/Write Burst Separation

- irst Separation

DQ/DQS phase alignment: DQ and DQS have different phase relationship in Read and Write bursts

CS, Latency + DQ/DQS Phase Alignment: CS is used to quality the occurrence of a burst, followed by DQ/DS phase relationship to distinguish between ReadWrite

Logic State + Burst latency: The command bus probed using the digital channels on the MSO is used to identify. Boat Multiple propagated by the command business.

- identify Read/Write commands on the command bus are quality and distinguish Read and Write bursts

- Options are provided to adjust the levels to improve burst detection in systems with lower signal integrity

Tektronix

### **Burst Detection**

- Easily Identify, Mark & Measure all Read / Write bursts

- Scroll through marked reads / writes across the entire waveform record

- Measurements performed on ALL Reads/writes within an acquisition

Tektronix<sup>\*</sup>

##

## Memory Probing

- Computer Systems use standardized DIMM's for which several probing solutions are available

- Memory in Embedded Designs is usually directly mounted on the PCB.

- Memory Components use BGA or PoP Packages

- Reduces the parasitics, enabling performance at higher speeds

- Mandate from JEDEC

- Probing a BGA or PoP package is Difficult

- Unable to probe at the Balls of the Device

- Probing at a connector, trace, or a via is not the same as probing at the device

- Not a true representation of the signal

Tektronix<sup>e</sup>

## TriMode Probing

- TriMode, with a single probe-DUT connection, allows:

- Traditional differential measurements: V+ to V-

- Independent single ended measurements on either input

- V+ with respect to ground

- V- with respect to ground

- Direct common mode measurements: ((V+) + (V-))/2 with respect to

- Many standards require both differential and single-ended voltage limit measurements. Requires two separate probes - Until Now!

Tektronix<sup>\*</sup>

### Before and After

#### Before TriMode Probing

- 1 Probe for Differential 2 Probes for SE and Common Mode

- 1 Probe Soldered and Re-soldered 3 times 2 Probes for Common Mode

After TriMode Probing

1 Probe and 1 setup for Differential, SE and Common Mode

Tektronix

# Memory Component Interposers Provide easy access to signals of Interest Controller Impedance path with embedded resistor for good signal Integrity De-embed filters to remove effects of interposer tap trace SPICE model available upon request for simulation and analysis

| -  | SPICE Induel available upon request for simulation and ana |                           |                                                                                                      |

|----|------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|

|    | Memory<br>Standard                                         | Supported<br>Form Factors | Interposer Types                                                                                     |

|    | DDR2                                                       | - BGA                     | - Socketed Interposer<br>- Direct Attach Interposer                                                  |

|    | DDR3                                                       | - BGA                     | - Socketed Interposer - Direct Attach Interposer - MSO DIMM Interposer - Instrumented DIMM           |

|    | DDR4                                                       | - BGA                     | - Socketed Interposer - Direct Attach Perimeter Interposer - MSO DIMM Interposer - Instrumented DIMM |

|    | LPDDR2                                                     | - BGA<br>- PoP            | - Socketed Interposer<br>- PoP Interposer                                                            |

|    | LPDDR3                                                     | - BGA<br>- PoP            | - Socketed Interposer<br>- PoP Interposer                                                            |

|    | GDDR5                                                      | - BGA                     | - Socketed Interposer<br>- Direct Attach Interposer                                                  |

| 22 |                                                            |                           |                                                                                                      |

**Tektronix**

## De-embedding

- In order to remove the effects on the Interposer, probe tips and probes de-embedding must be considered.

- De-embedding filters will available for the interposers upon request.

These de-embedding filters are developed assuming nominal values

- For more accurate characterization for a particular setup SDLA visualizer for Real time scopes can be used

Tektronix

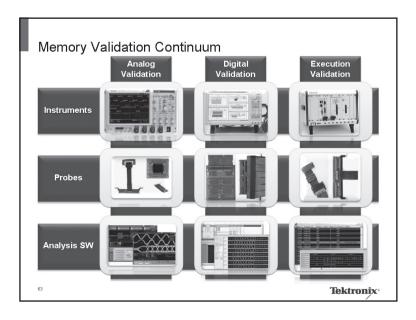

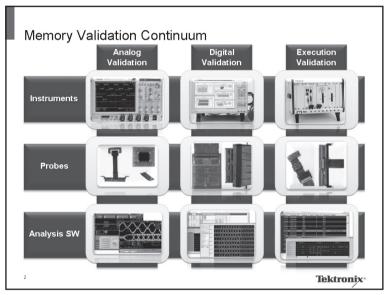

## Memory Interface Digital Validation

Measure the digital logic state and cycle based timing characteristics for diagnostic and troubleshooting purposes

**Tektronix**°

24

## **DDR4 Memory Component Interposers**

- MCI's are used for probing signals from individual Memory Components

- Comes with a Custom Socket that needs to be soldered to Target system

- Quickly swap TLA & oscilloscope interposers on the same target. Quickly move interposers to different target.

- No special footprints or special routing requirements

- Memory Component Interposer Types

- Logic Analyzer and Oscilloscope

- Direct Attach or Socketed interposers

- x4/x8 and x16 Memory Component types

Tektronix<sup>,</sup>

## DDR4 ACC Interposers

- Protocol / Execution Validation

- DIMM and SODIMM Interposers

- Targeted for protocol compliance analysis

- Automated Setup

- Use with Nexus Compliance Analysis S/W

- Compatible with P6960HCD or NEX-PRB1XL

Sales University 2012 - Tektronix Confidential Course Title vx.x (Edit in View/Insert > Header and Footer)

Tektronix •

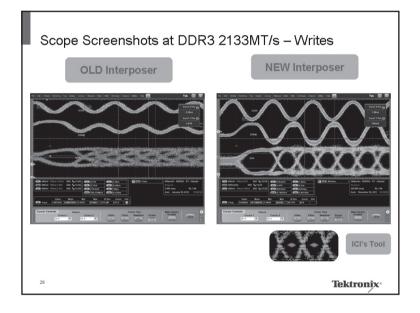

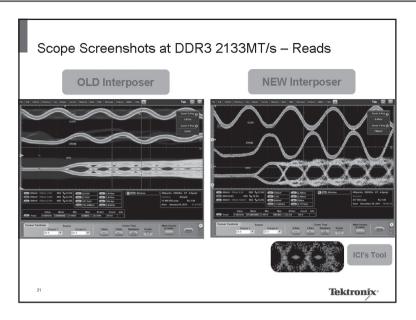

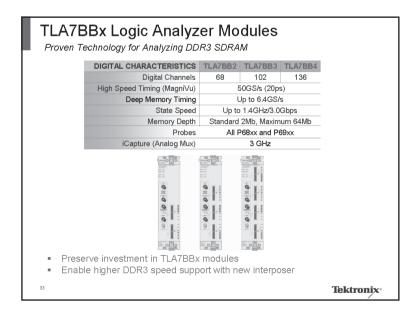

## Introducing New DDR3/4 High Speed Interposer

Next Generation DDR3/4 Probing Technology

## Gain Unprecedented Visibility Into Your DDR3/4 Signal Activity

DIMM Interposer

SODIMM Interposer

Collaborative design combining years of Logic Analyzer acquisition and DDR3 probing experience between Tektronix and Nexus Technology

2

Tektronix<sup>\*</sup>

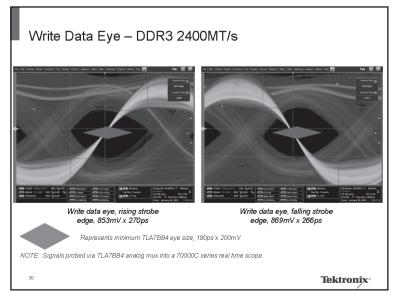

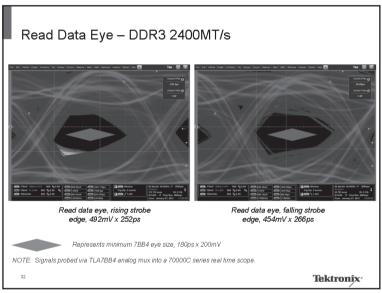

## New DDR3/4 High Speed Interposer

Next Generation DDR3/4 Probing Technology

- Provides significant performance improvements to DDR3 probing

- Integrates Tektronix ultra-high performance SiGe Hybrid ASIC technology

- Compensation for platform trace loss on writes

- Improved interposer input impedance (5.2k to 0.73V)

- Reduces load on target with minimal effect on bus

- Provides an accurate representation of the signal on the target

- Enables probing DDR3/4 speeds at 2400MT/s and beyond

- Enables probing lower voltage signals on LVDDR3/4

- Interposers compatible with UDIMM, RDIMM, LRDIMM

Tektronix

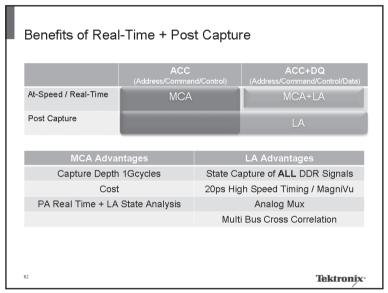

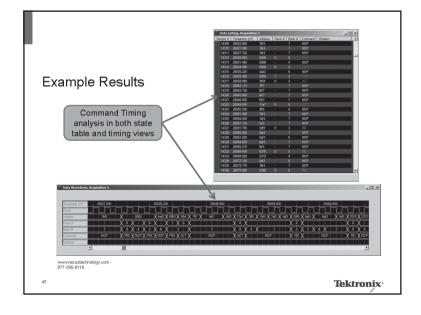

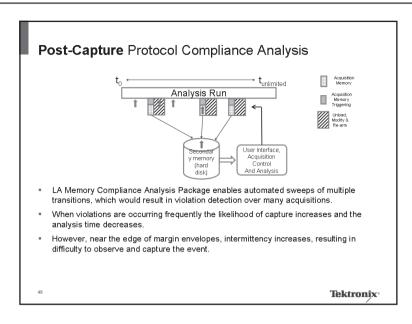

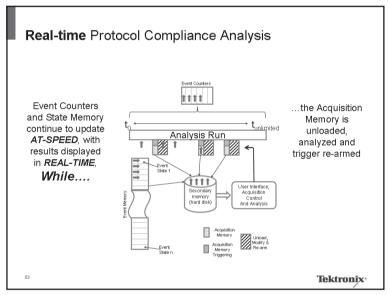

What's unique about Execution Validation

Typical instrument use a post-capture model

TRIGGER → ACQUIRE → ANALYZE

Execution Validation use model

t<sub>0</sub> ← → t<sub>unlimited</sub>

Analysis Run

Two equipment options

1. Logic Analyzer - S/W automates acquisitions

2. Memory Compliance Analyzer - Real-time Analysis

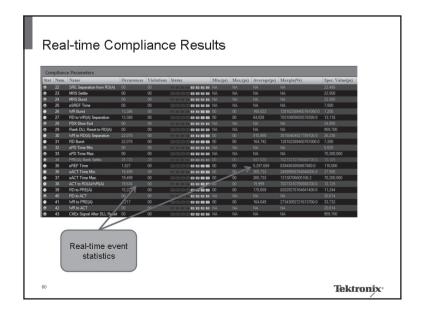

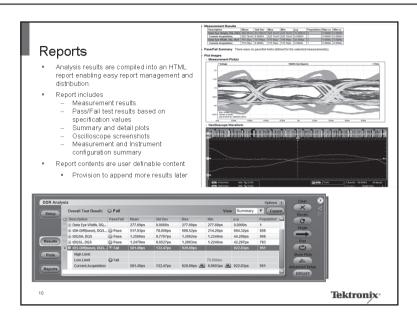

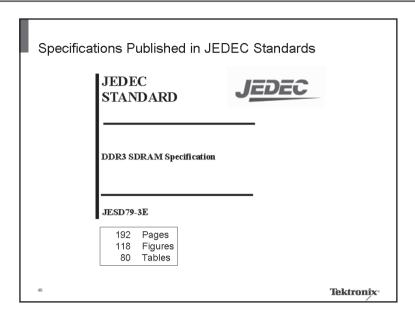

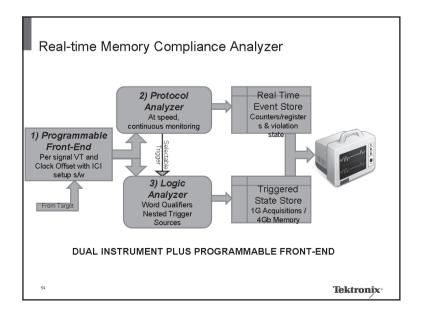

## Memory Compliance Analyzer

#### **REAL-TIME PROTOCOL COMPLIANCE ANALYSIS**

- Analysis 160+ categories of JEDEC spec parameters

- Includes Power up/down, self-refresh and autoprecharge (RDA/WRA) analysis

- Timing and State analysis

- HTML reports / XML exporting

Real-time AND Post Capture Compliance Analysis

Command/Address

Tektronix<sup>\*</sup>

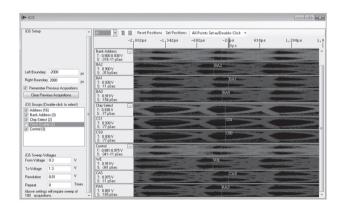

## Programmable Front-End / High Speed Eye Diagrams

Tektronix<sup>\*</sup>

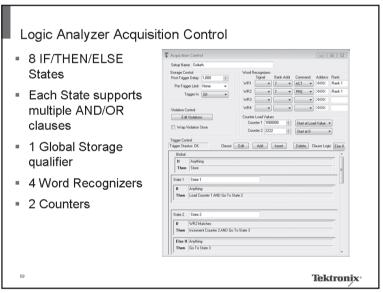

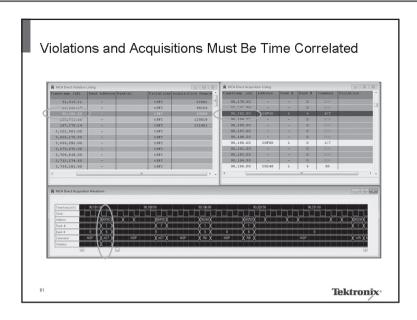

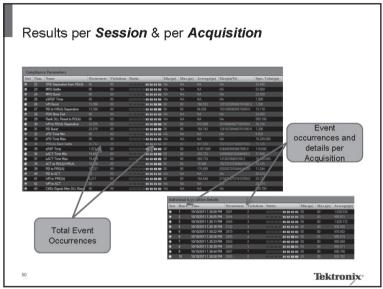

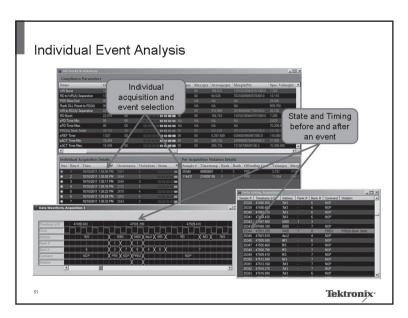

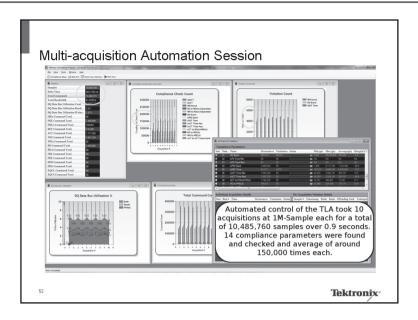

## Automated Analysis Sessions

- One or Many Acquisitions / One or Both Analyzers

- Protocol Analysis Session

- Protocol Analyzer runs until stopped

- Violations and statistics are reported

- Single Acquisition Session

- Protocol Analyzer runs until the state analyzer is triggered

- Violations and statistics are reported.

- State/Timing data is acquired and available for analysis

- Multi-Acquisition Session

- Protocol Analyzer runs until the state analyzer is triggered

- Results are stored in disk memory and analysis is restarted

- Trigger conditions can be modified mid-session.

57

Tektronix<sup>\*</sup>