## **Storage PHY Test Solutions**

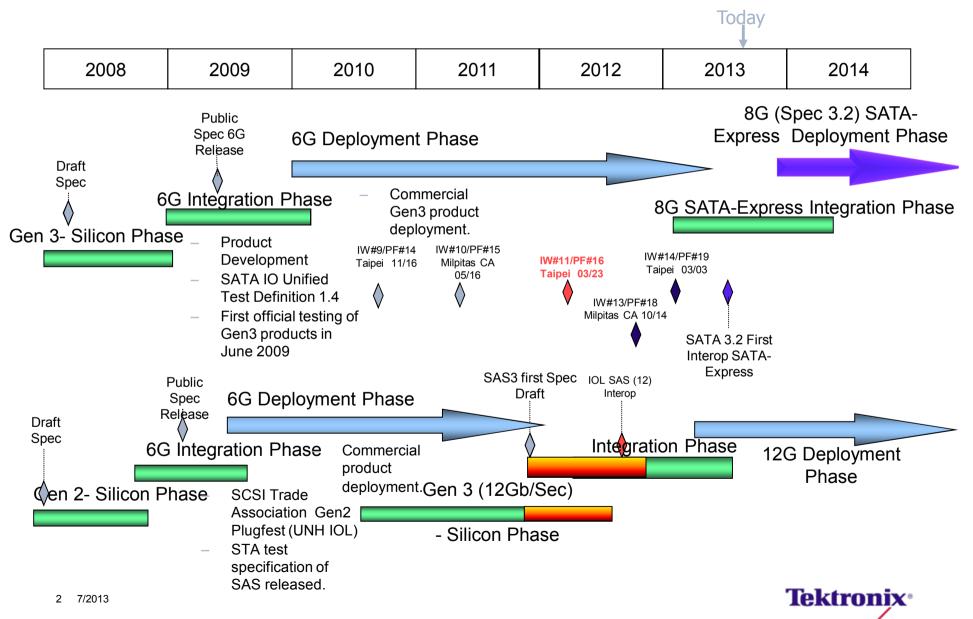

#### Storage Timelines and Solutions Development

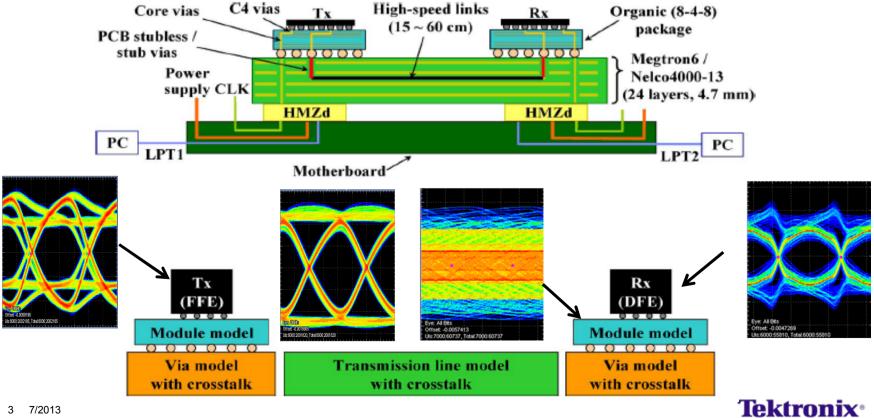

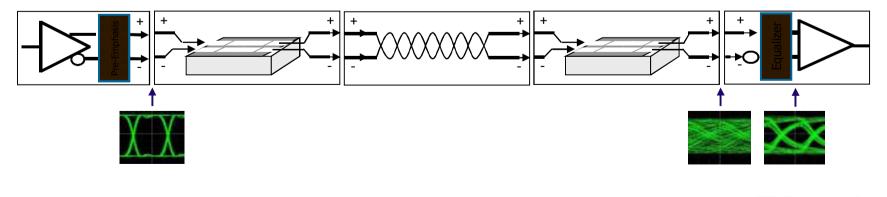

### 12G+ Design Problem: 1000mV, FFE, Crosstalk, DFE, 50mV

- Crosstalk and signal loss problems are the largest design challenge today.

- Significant advances in high tap count Decision Feedback Equalization are key to operating at 12G+.

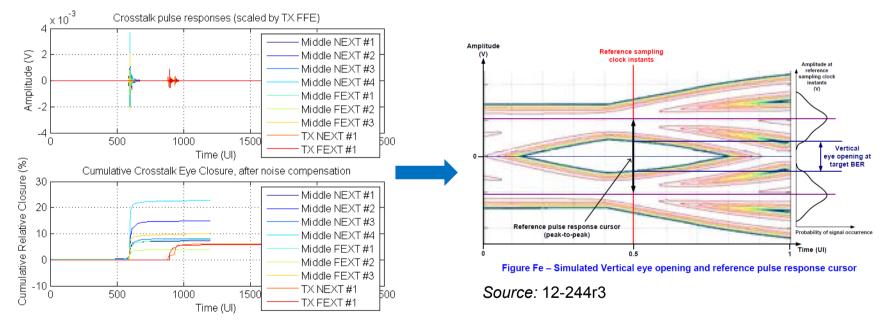

### NEW Measurement for Crosstalk/ISI Evaluation

- SAS3\_EYEOPENING\* Measurement for accurate analysis of ISI and crosstalk effects

- Provides measure of relative vertical eye opening after reference equalization

\*Note, this measurement is similar to the SAS-2 Waveform Distortion Penalty (WDP) measurement but also includes Tx EQ in addition to DFE. The code was provided and distributed through the T10 Technical Committee and permission has been granted for Tektronix to reuse.

### SAS3\_EYEOPENING Provides 4 Different Metrics

- 1. Relative Vertical Eye Opening: A direct indication of how much margin there is after equalization

- Takes into account un-compensable ISI and crosstalk

- ISI and crosstalk broken down in report

- 2. Main Cursor Amplitude: A direct indication of the amplitude after equalization

– Assumes 800 mVppd max. TX launch amplitude, unless data is captured

- **3. Maximal FFE correction**: A direct indication of how much FFE correction is required by the transmitter

- Max(abs(Cpre/Ccntr,Cpost/Ccntr))

- **4. Maximal DFE correction:** A direct indication of how much DFE correction is required by the receiver

- Max(abs(DFE/Main))

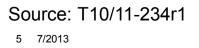

#### SAS-3 PHY Transmitter Solution – Option SAS3

#### Group 1 – OOB Signaling

| 5.1.1  | Maximum Noise During OOB Idle                     |

|--------|---------------------------------------------------|

| 5.1.2  | OOB Burst Amplitude                               |

| 5.1.3  | OOB Offset Delta                                  |

| 5.1.4  | OOB Common Mode Delta                             |

| Grou   | o 2 – Spread Spectrum Clocking (SSC) Requirements |

| 5.2.1  | SSC Modulation Type                               |

| 5.2.2  | SSC Modulation Frequency                          |

| 5.2.3  | SSC Modulation Deviation                          |

| 5.2.4  | SSC Balance                                       |

| 5.2.5  | SSC DFDT                                          |

| Grou   | o 3 – NRZ Data Signaling Requirements             |

| 5.3.1  | Physical Link Rate Long Term Stability            |

| 5.3.2  | Common Mode RMS Voltage Limit                     |

| 5.3.3  | Common Mode Spectrum                              |

| 5.3.4  | Peak to Peak Voltage                              |

| 5.3.5  | Voltage Modulation Amplitude (VMA)                |

| 5.3.6  | Equalization                                      |

| 5.3.7  | Rise Time                                         |

| 5.3.8  | Fall Time                                         |

| 5.3.9  | Random Jitter (RJ)                                |

| 5.3.10 | Total Jitter (TJ)                                 |

| 5.3.11 | Waveform Distortion Penalty (WDP)                 |

| 5.3.12 | SAS3_EYEOPENING                                   |

| 5.3.13 | Pre Cursor Equalization Ratio                     |

| 5.3.14 | Post Cursor Equalization Ratio                    |

| 5.3.15 | Transition Bit Voltage PK-PK (VHL)                |

| 5.3.16 | Unit Interval                                     |

|        |                                                   |

#### SAS-3 1.5/3/6/12 Gb/s Tx Test Software

#### TekExpress SAS3-TSG Automation Software

| 🖇 TekExp | ress  | s SAS - (Untitled | I)*               |                                                      |     |                                  | Options • | ۲     |

|----------|-------|-------------------|-------------------|------------------------------------------------------|-----|----------------------------------|-----------|-------|

|          |       |                   |                   |                                                      |     |                                  |           | Start |

| Setup    | 1     | DUT               |                   | DUT001                                               |     | <b>Ø</b>                         |           |       |

| Status   | 2     | Test Selection    | • Acq<br>View     | uire live wavefo<br>Compliance                       | rms | OUse pre-recorded waveform files |           |       |

| Results  | 3     | Acquisitions      | Device            | Drive                                                | ¥   |                                  |           | Pause |

| Reports  | 4     | Preferences       | Suite             | Transmitter                                          | •   |                                  |           |       |

|          |       |                   | ✓ 3<br>✓ 6<br>✓ 1 | .5 Gb/s<br>.0 Gb/s<br>.0 Gb/s<br>2 Gb/s<br>utomation |     |                                  |           |       |

|          | Statu | us Ready          |                   |                                                      |     |                                  |           |       |

Tektronix<sup>•</sup>

#### SAS-3 PHY Transmitter Solution – Option SAS3-TSG

- Automated transmitter validation for 1.5, 3, 6 and 12 Gb/s SAS physical layer specification

- Integrated SAS3\_EYEOPENING and WDP measurements for accurate analysis of ISI and crosstalk effects and relative vertical eye opening after reference equalization

- Easily reconfigure existing measurements to create user-specified test parameters or test limits

- Multiple plots and measurement configurations provides a quick comparison of the same acquired data with different settings

- Simultaneous two lane testing of primary and secondary ports

- Detailed test reports with screenshots, setup details, and pass/fail limits

#### **Beyond Compliance**

- How much margin is there in my design?

- How many DFE/FFE taps are needed to meet the system budget?

- What is longest channel (cable/backplane) the system can tolerate?

- How does process/voltage/temperature affect device performance?

#### Flexible Link Analysis Tools – option SDLA

- DFE/FFE modeling

- Reference equalizer vs. vendor-specific

- Equalizer implementation for PHYs

- Enhanced de-embedding

- Full four-port network characterization

- Channel emulation for margin analysis

**Tektronix**<sup>®</sup>

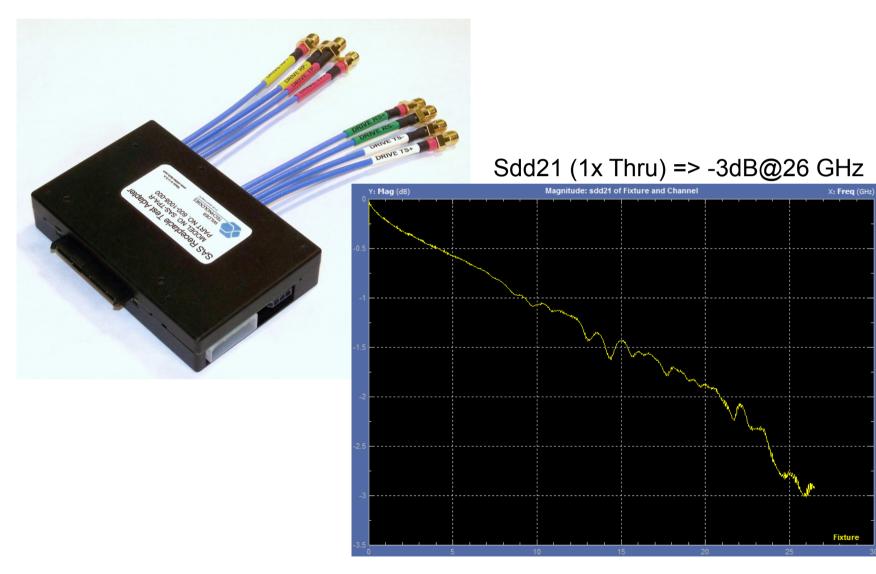

### SAS Receptacle Test Adapter

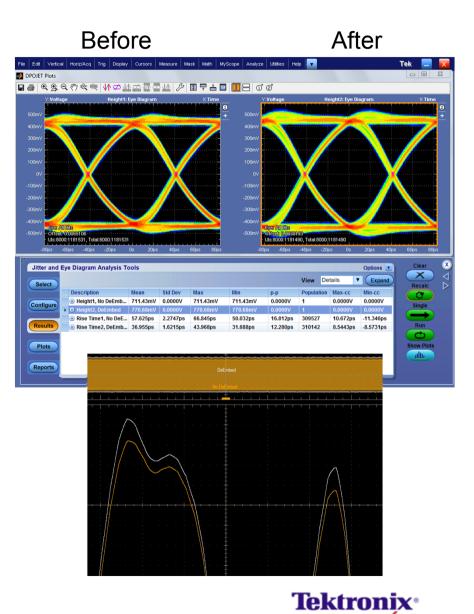

#### **Test Fixture De-embedding**

- Why de-embed?

- Tx measurements referenced to die (ET)

- Improve margin with removal of fixture effects

- S-Parameters acquired from calibration fixture or model extraction

- Use inverse response to compensate for loss

|               | Before<br>De-Embed | After<br>De-Embed |

|---------------|--------------------|-------------------|

| Eye<br>Height | 711 mV             | 770 mV            |

| Rise Time     | 57                 | 37                |

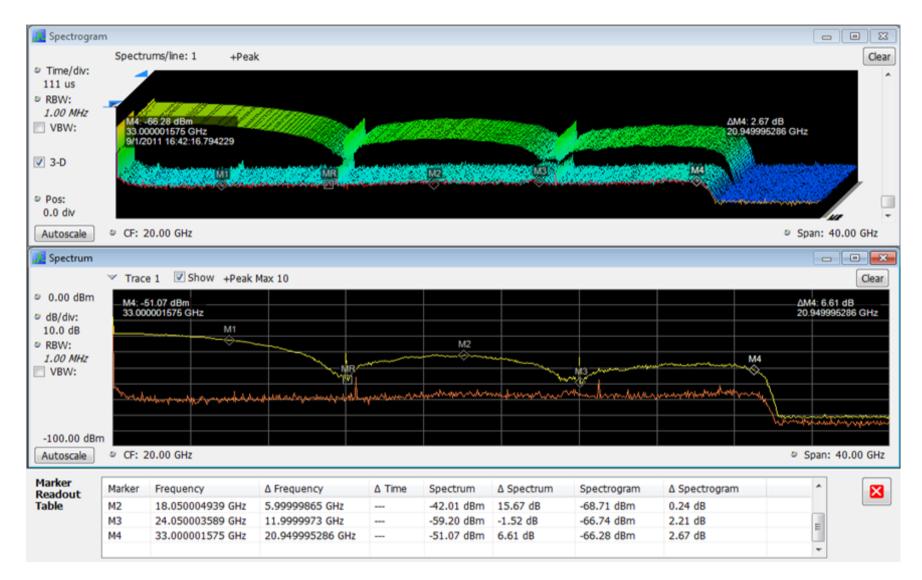

#### Bandwidth Considerations SAS PRBS11 12G NRZ Power Spectrum

### Recommended Equipment

The following components are required for performing SAS12 Tx measurements

- DSA/DPO/MSO70K(C/D) Series Oscilloscope with Opt. 2XL or higher

- 12.5 GHz or higher recommended for 1.5, 3, or 6 Gb/s

- 20 GHz or higher recommended for 12 Gb/s

- DPOJET Advanced (DJA) Prerequisite

- Option SAS3-TSG & SAS3-TSGW (required for WDP measurements)

- Test Fixtures:

- TF-SAS-TPA-R SAS Gen3 Receptacle Adapter (drive form factor) or

- <u>TF-SASHD-TPA-R</u> miniSASHD 12G SAS Receptacle (mini SAS HD 4i/x cables) or

- Set of <u>TF-SASHD-TPAR-P</u> miniSASHD 12G SAS (Right Side) Plug and <u>TF-SASHD-TPAL-P</u> miniSASHD 12G SAS (Left Side) Plug (x8)

- PMCABLE1M or equivalent Phase Matched Cable Set (qty: 2)

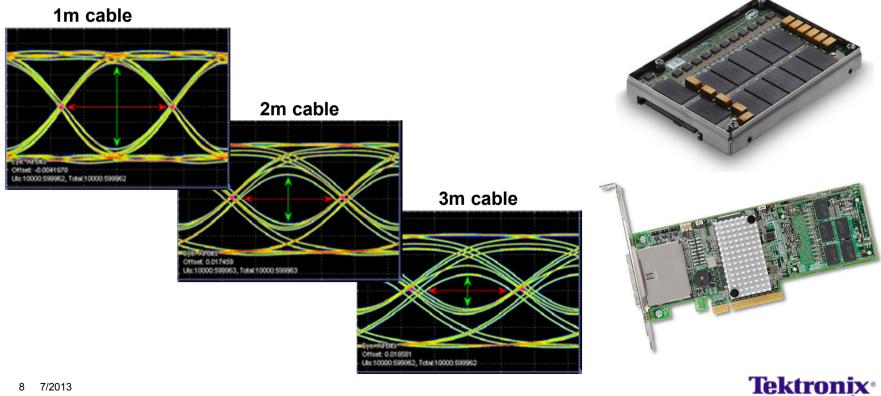

#### SAS Implications for Receiver Testing

- System margins are decreasing, testing the transmitter only does not imply interoperability

- Receiver test requirements are expanding and will include testing with a crosstalk, ISI and Tx/Rx EQ

- Transmitter Equalization requires pre/post-cursor control

- Receiver Equalization is more sophisticated

- Behavior equalizers (Continuous Time Linear and 5-tap Decision Feedback Equalization) must be used to compensate for channel loss

- Transmitters must support back channel negotiation to auto-negotiate with Receivers to determine optimal equalization settings for testing

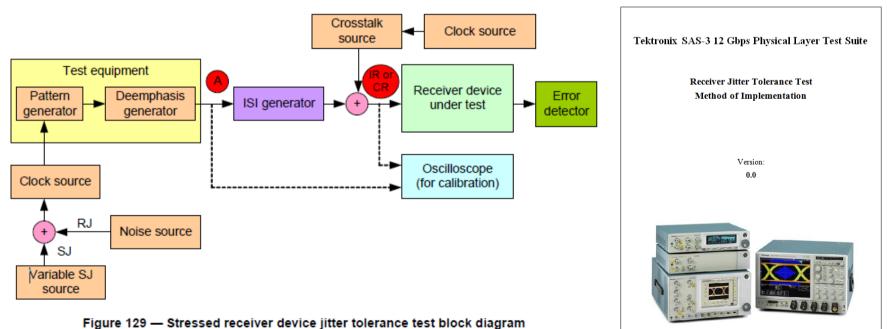

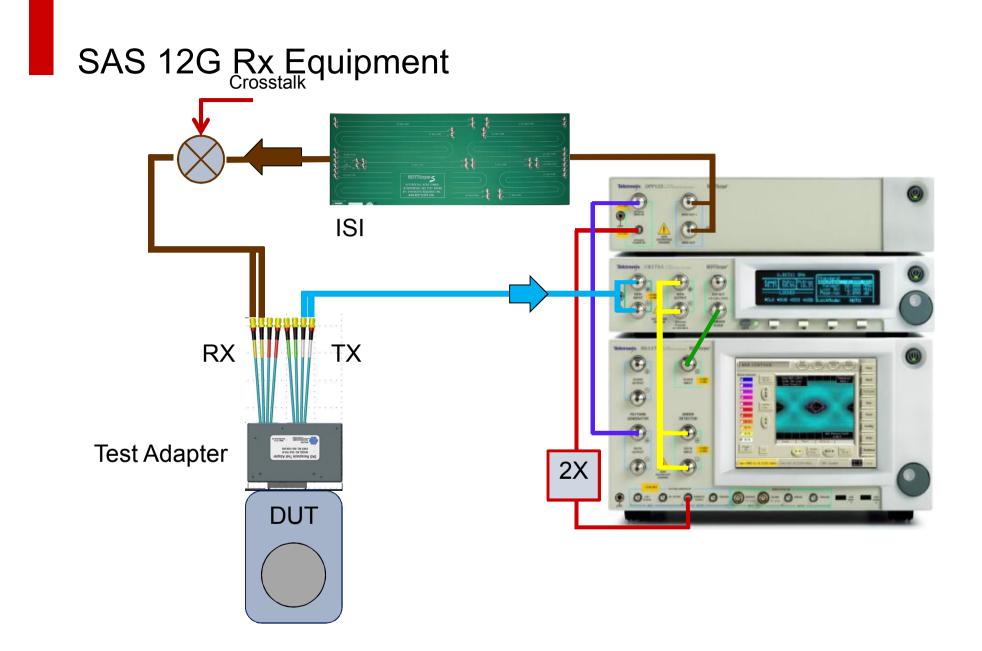

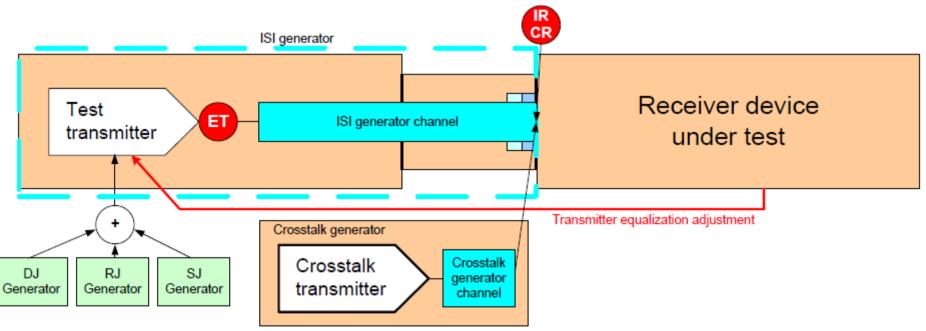

#### SAS 12 Gb/s Rx Test Setup

- Similar to SAS 6 Gb/s Rx configuration

- Rx calibration -> CJTPAT -> BER test

- Tektronix Method of Implementation (MOI) provides complete Rx Test procedure

#### SAS 12 Gb/s Rx MOI

Source: sas3r03\_18Oct2012

**Tektronix**.

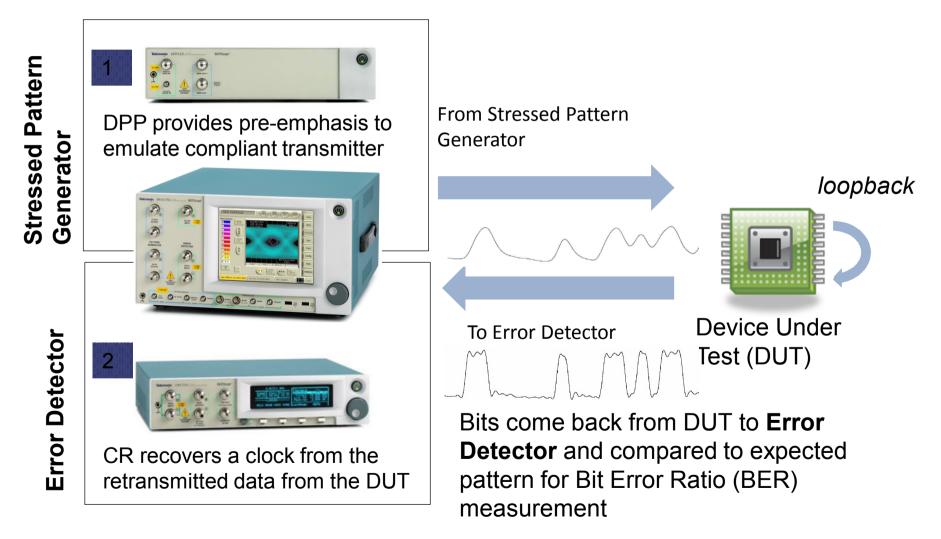

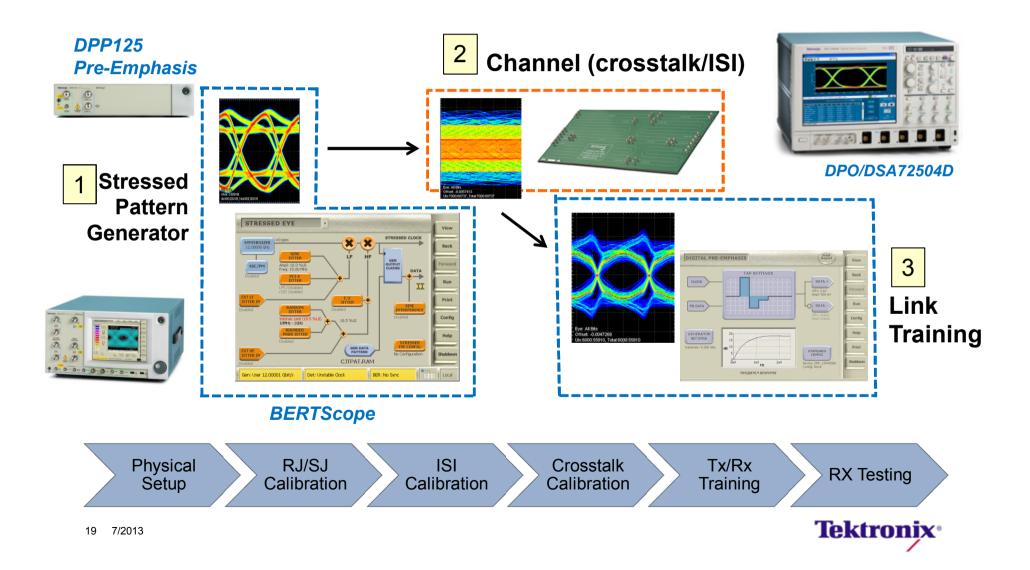

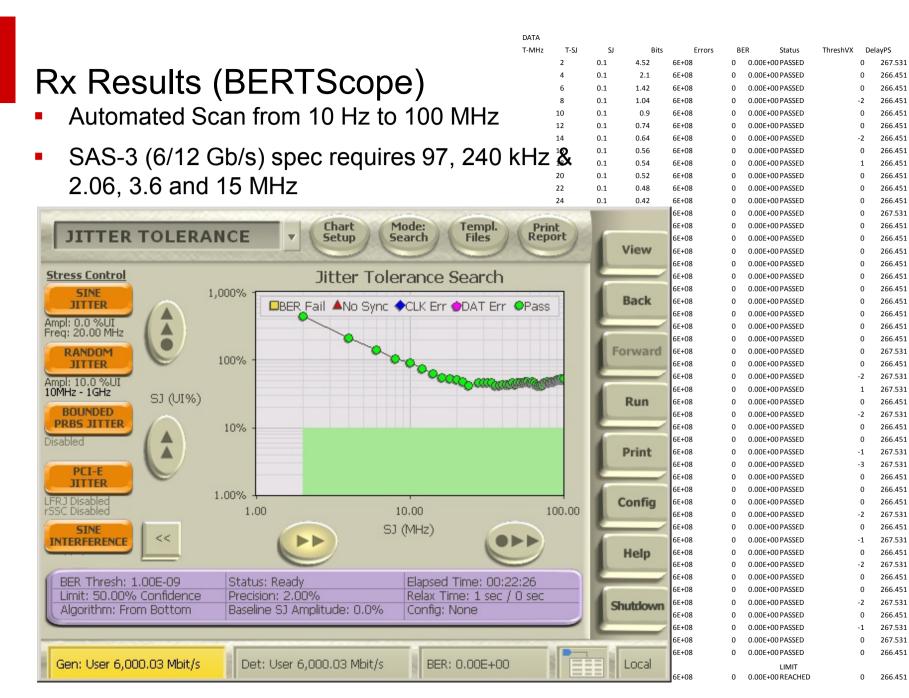

#### Receiver Test Made Easy with the BERTScope

#### Trained Link for Jitter Tolerance Test

- Complete Rx test exercises both CDR and Tx/Rx EQ capabilities

- Link optimization options

- Iterate possible Tx/Rx EQ states and apply from 'best' optimized eye

- Directly apply Preset based on typical configuration for worst case channel

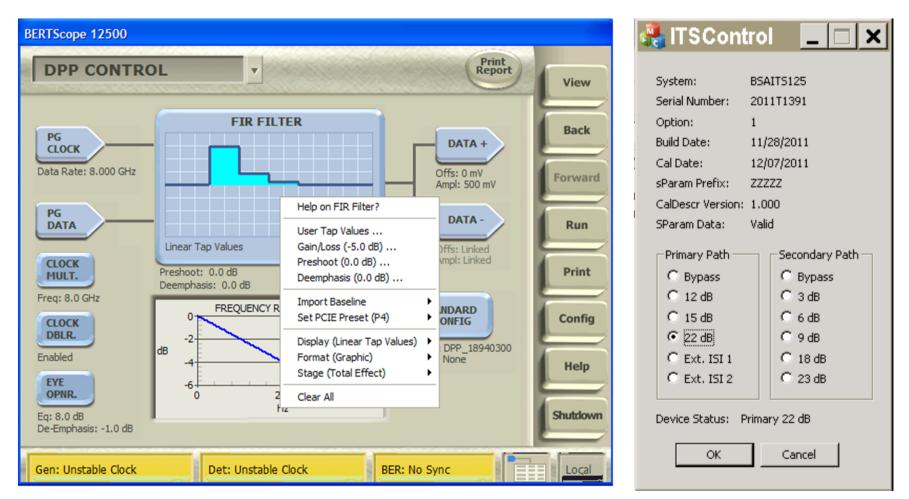

Figure Fh – Stressed receiver transmitter equalization adjustment

#### Stressed Pattern Calibration – Putting it Together

#### Need for Precise ISI generation

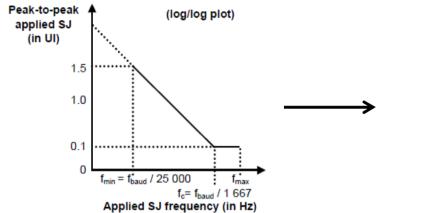

Device margin testing against variable magnitude sinusoidal test vectors has been foundation of receiver characterization.

Current PHY designs use sophisticated CTLE and/or DFE architectures, where tolerance and margining against DDJ is more important than SJ.

#### **NEW SAS 12 Gb/s Receiver Test Solutions**

#### **DPP125C Digital Pre-emphasis Processor**

- Integrated eye opener functionality for testing DUTs with long channels

- Integrated clock doubler that enables full rate stress for 12 Gb/s

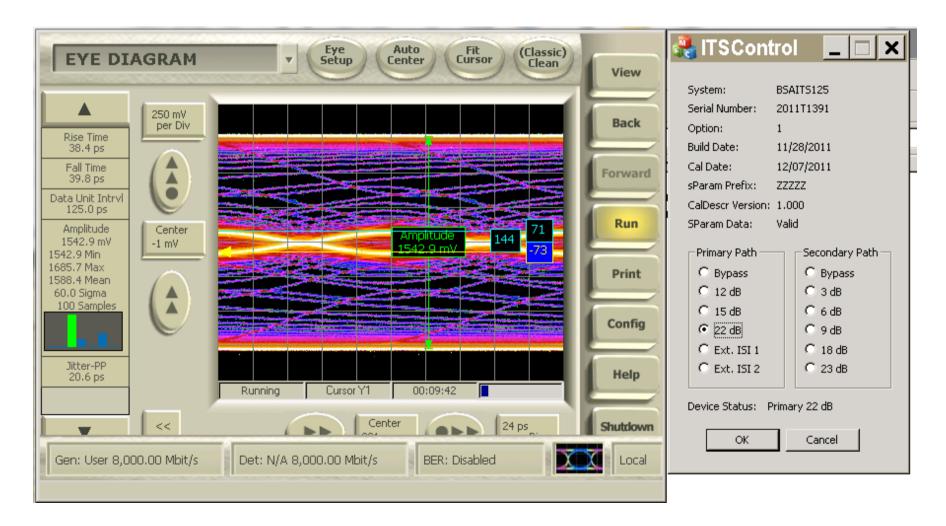

#### **BSAITS125** Interference Test Set

- Programmable variable ISI for automated testing and precision setting

- Integrated CM and DM interference combiner

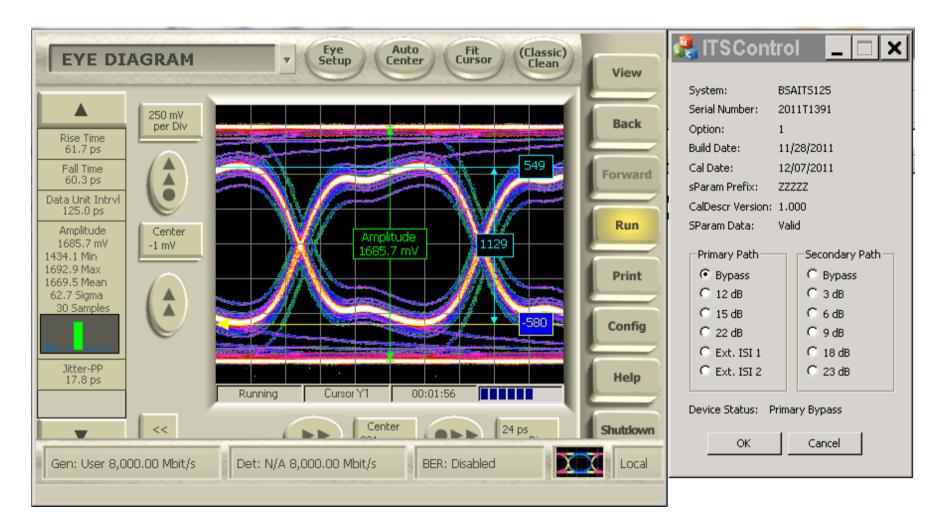

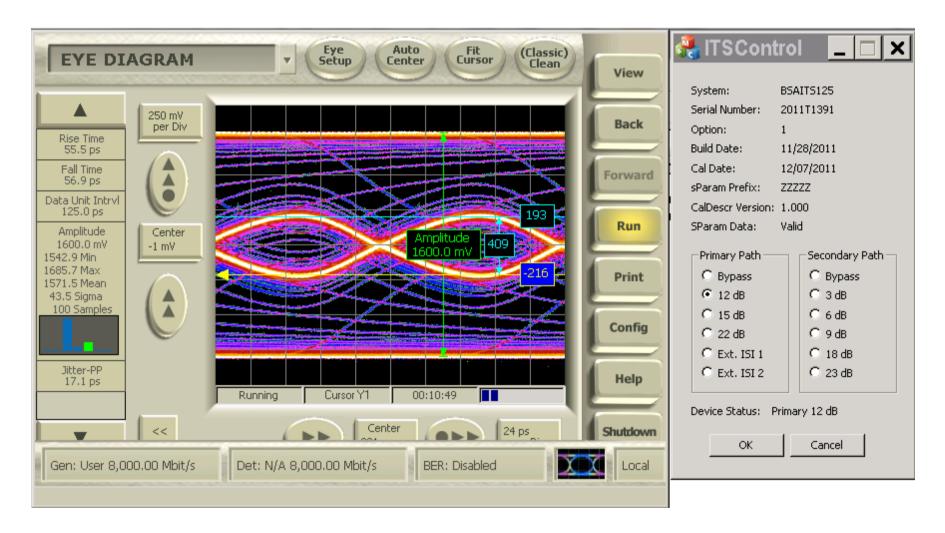

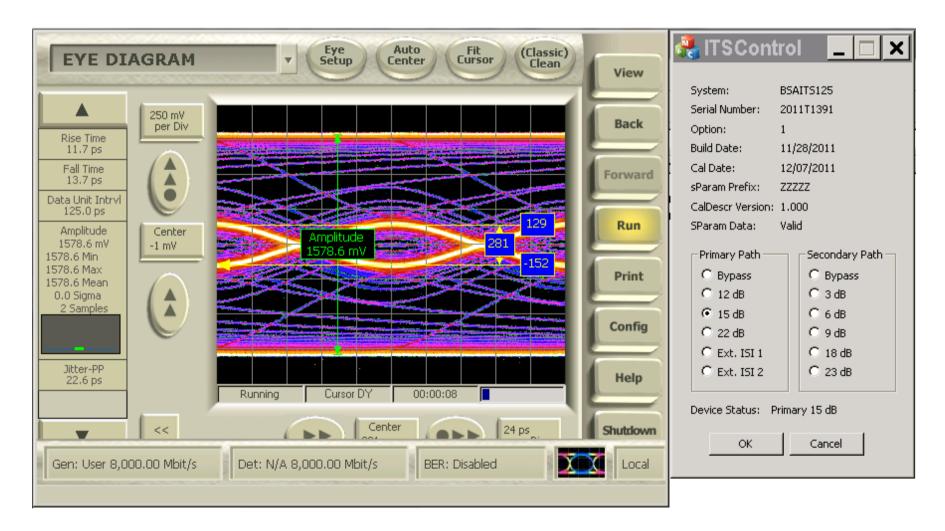

### Data Dependent Jitter Variability with BSAITS

BSAITS automates selection of fixed ISI traces with fine (mdB) controls with the DPP FIR filter for a continuously variable high precision ISI source.

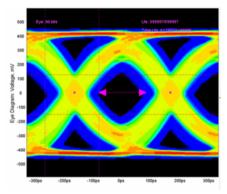

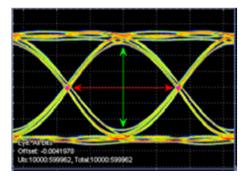

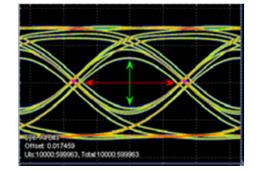

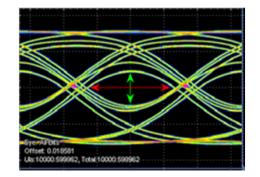

#### **BSAITS Bypass mode**

#### BSAITS 12dB mode

#### BSAITS 15dB mode

#### BSAITS 22dB mode

# Complete Tektronix SAS Testing

| <b>Receiver Tests/Active Cable Tests</b><br><b>RSG/RMT</b> - Receiver Silicon, Active cable<br>characterization and Compliance testing<br>capability to 26 Gb/s                                                                                                    | BSA125C with option JMAP, STR & SF<br>DPP125C, CR125A and BSAITS for<br>Digital Emphasis, Clock recovery and<br>ISI generation              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Channel Tests<br>ICR: Insertion Loss/Crosstalk analysis.<br>Rx/Tx - Device and Host electrical channel<br>performance, Crosstalk, Impedance and<br>return loss<br>Passive Cable Tests<br>Cable crosstalk, skew and frequency<br>domain measurements, sdd21, sdd11. | DSA8300 Sampling Oscilloscope<br>80E10 TDR Sampling Module for<br>DSA8300 Sampling Oscilloscope<br>80SICON S-Parameter Analysis<br>software |  |

| <ul> <li>PHY, TSG, and OOB Tests</li> <li>PHY – Signal timing stability and SSC analysis.</li> <li>TSG – Transmitter AC parametric, Jitter, Amplitude.</li> <li>OOB- Out Of Band signal validation</li> </ul>                                                      | DSA72504D Real-Time Oscilloscope<br>Option SAS3-TSG, SAS3-TSGW, and<br>SAS3 12 Gbps Tx Test Software<br>DPOJET Jitter/Eye Analysis software |  |