## Introduction

With the full power of digital computing arriving in the wireless world, we are seeing the development of a range of intelligent, low cost RF devices. This explosion of digital RF is fuelling the development of highly integrated communication devices. Mobile phones are at the forefront of this trend, with each new generation offering more capabilities and functionality than the last.

These developments are creating a highly complex, highly integrated design environment. The underlying trend in this space is the drive towards more use of software and digital baseband than traditional analog components. In short, the digital to RF interface is moving closer to the antenna.

The benefits of using more digital baseband technology are higher performance, lower power consumption and faster time to market. Engineers from all industries, communications to radar to consumer, are all taking advantage of this move towards more "software defined" RF devices.

Technical Brief

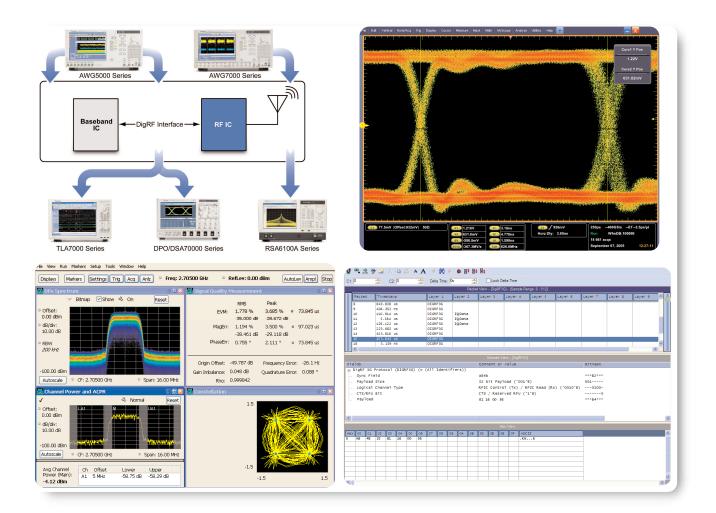

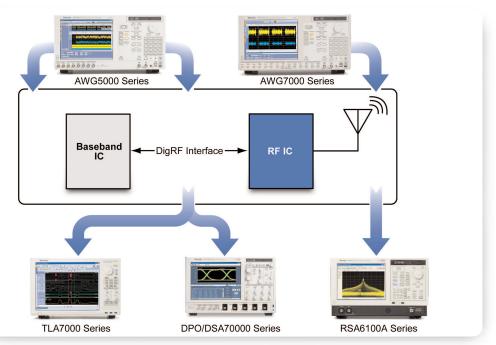

Figure 1. Baseband IC and RF IC interaction.

With both the baseband and RF sections becoming more complex, the interface between them is becoming more important. With many designs, such as 3G mobile phones, being commonly implemented with two highly integrated ICs, one for baseband and one for RF, the interface between them is critical.

In many industries there is no clear standard for the digital to RF interface as different designs rely on different levels of integration and design methodologies. This can cause added problems during the design integration process because not only are engineers trying to troubleshoot and debug functional issues, they can also be dealing with issues caused by the interface. To overcome some of these issues and to enable more interoperability between ICs from different vendors, the mobile phone industry has developed the DigRF standard.

The DigRF 3G standard aims to simplify this interface by providing an open interface that all IC manufacturers can implement. By complying with the standard, IC designers do not have to worry about interoperability issues when their designs are used in conjunction with ICs from different vendors. For phone designers, this standard removes the constraint of proprietary interfaces, leaving them free to select ICs from a wide range of vendors, safe in the knowledge that the interface and communication between the ICs has already been taken care of.

#### Testing

What DigRF does not remove is the need to functionally verify the interaction between the ICs. Both the baseband and RF ICs, see Figure 1, need to be tested to ensure that they are correctly responding to input and control signals. This has to be done during the initial power on and verification stage, as well as the final integration process.

With these DigRF devices, the design environment is likely to contain digital, analog and RF signals, as well as both parallel and serial interfaces, so the functional validation and debug is a challenging task. What compounds this challenge is that designs have not just to be functionally tested, they have to be tested under multiple conditions: ideal; stressed; and real-world. This is the only way to ensure reliability of the design in all operating environments.

Tektronix offers DigRF specific application software that extends the capabilities of its standard test equipment, enabling DigRF devices to be tested without the need for expensive, specialized accessories.

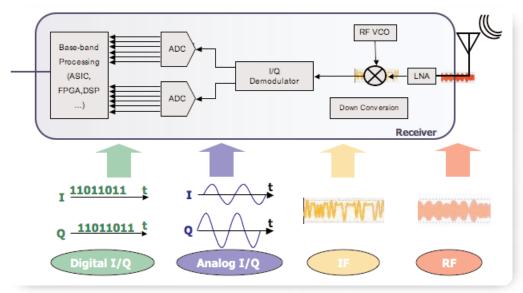

Figure 2. Complexity of a mixed signal environment.

#### Stimulation

In a mixed signal environment of a Digital RF device, there obviously is the need to test many different scenarios, so there is the need to generate the different analog, digital and mixed signals.

The design needs to be tested under ideal, as well as stress test conditions. Engineers need to be able to generate signals that simulate conditions such as I/Q impairments, carrier leakage, sideband suppression, I/Q imbalance, quadrature offset, frequency responses and so on. The Tektronix AWG5000 series of Arbitrary Waveform Generators can cover all these signal generation needs. It is a single instrument that can generate Digital I/Q, Analog I/Q as well as IF signals.

Typically, it takes several instruments to generate the various signals required for thorough testing of the digital RF interface. These include a logic source with enough performance to generate Digital I/Q data and an arbitrary waveform generator with high enough vertical resolution or an I/Q Vector Signal Generator to generate Analog I/Q data. The AWG5000 offers all of these capabilities in a single instrument, Figure 3.

This approach dramatically simplifies the setup and testing of complex mixed signal designs. It enables a

Figure 3. AWG5000 Series arbitrary waveform generator mixed signal capability.

correlation of the different signals and reduces the space needed on the test bench, as well as the investment required.

The AWG5000 not only allows the generation of all the different signals needed to validate the functional performance of ICs, it enables the testing of how the IC handles and responds to DigRF signals. Ideal, non-ideal, and real world DigRF signals can be sent into the IC so that design engineers can have complete faith in their design's ability to operate in any environment.

Technical Brief

| 1: 0        |                                      |                                     | ÷                          |                  |           |      | ÷     | Delta |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

|-------------|--------------------------------------|-------------------------------------|----------------------------|------------------|-----------|------|-------|-------|--------|-------|--------------|-------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------------|---------------------|----------|---------|-------------------------------|---------|-------|-----|

|             |                                      |                                     |                            |                  |           |      |       |       |        |       | Pack         | et View                             | r - [DigF                             | RF3G] -                               | - [Sample F                                     | Range: 0 - 512]     |          |         |                               |         |       |     |

| P           | acke                                 | t                                   | Time                       | estamp           | •         |      |       | Layer | - 1    | Lay   | ren 2        | Lay                                 | er 3                                  | L                                     | ayer 4                                          | Layer 5             | Laye     | er 6    | Layer 7                       | Layer 8 | Layer | 9 ^ |

| 8           |                                      |                                     | 843.                       | 838 us           | 5         |      |       | DIGRF | 3G     |       |              | 1                                   |                                       |                                       |                                                 |                     |          |         |                               | 1       |       |     |

| 9           |                                      |                                     |                            | 252 ms           |           |      |       | DIGRF |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 10          |                                      |                                     |                            | 914 us           |           |      |       | DIGRF |        |       | Data         |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 11          |                                      |                                     |                            | 384 us           |           |      |       | DIGRF |        |       | Data         |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 12          |                                      |                                     |                            | 122 US           |           |      |       | DIGRF |        | IQI   | Data         |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 13          |                                      |                                     |                            | 002 us           |           |      |       | DIGRF |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 14          |                                      |                                     |                            | 816 us<br>842 us |           |      |       | DIGRF |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| 19          |                                      |                                     |                            | 842 US<br>159 ms |           |      |       | DIGRF |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       |     |

| <           |                                      |                                     | >.                         | 122, 102         | >         |      |       | DIGKP | 50     |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         |       | >   |

| 1           |                                      |                                     |                            |                  |           |      |       |       |        |       |              |                                     |                                       |                                       |                                                 |                     |          |         |                               |         | )     |     |

|             |                                      |                                     |                            |                  |           |      |       |       |        |       |              |                                     | Decode                                | e View                                | / - [DigRF3                                     | G]                  |          |         |                               |         |       |     |

| e1          | ds                                   |                                     |                            |                  |           |      |       |       |        |       |              | Com                                 | ment (                                | 00.1/7                                | 1.00                                            |                     |          |         | and an owned by               |         |       |     |

|             |                                      |                                     |                            |                  |           |      |       |       |        |       |              | COIIII                              | incrite 1                             | UI Ve                                 | anue                                            |                     |          |         | Bitmask                       |         |       |     |

| D           | igRF                                 | 3G F                                | Proto                      | co1 (            | DIGR      | F3G) | (= (  | A11 I | denti  | fiers | 5))          | COM                                 | ilence i                              |                                       | ilue                                            |                     |          |         | BITMASK                       |         |       |     |

|             | -                                    | 3G F                                |                            | col (            | DIGR      | F3G) | (= (  | A11 I | denti  | fiers | 5))          | a84b                                |                                       | 01 12                                 | liue                                            |                     |          |         | ***B2***                      |         |       |     |

| -           | Sync                                 | : Fie                               | eld                        | col (            | DIGR      | F3G) | (= (  | A]] I | denti  | fiers | 5))          | a84b                                | 5                                     |                                       |                                                 | 18)                 |          |         | ***B2***                      |         |       |     |

| -           | Sync<br>Pay1                         | Fie<br>oad                          | eld<br>Size                |                  |           | F3G) | (= (  | A11 I | denti  | fiers | 5))          | a84b<br>32 b                        | o<br>Dit Pa                           | ayloa                                 | ud ('001                                        |                     | (Bx) ('0 | 2010'8) | ***B2***<br>001               |         |       |     |

| -           | Sync<br>Pay1<br>Logi                 | Fie<br>oad<br>cal                   | eld<br>Size<br>Chan        | col (<br>nel Tj  |           | F3G) | (= (  | A11 I | denti  | fiers | 5))          | a84b<br>32 b<br>RFIC                | b<br>bit Pa<br>Cont                   | ayloa<br>trol                         | ud ('001<br>(Tx) /                              | RFIC Read           | (Rx) ('0 | D010'B) | ***B2***<br>001<br>0100-      |         |       |     |

| -           | Sync<br>Payl<br>Logi<br>CTS/         | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (  | A11 I | denti  | fier  | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve                | ud ('001                                        | RFIC Read           | (Rx) ('0 | D010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

| -           | Sync<br>Pay1<br>Logi                 | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (, | A11 I | denti  | fiers | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont                   | ayloa<br>trol<br>serve                | ud ('001<br>(Tx) /                              | RFIC Read           | (Rx) ('C | 0010'B) | ***B2***<br>001<br>0100-      |         |       |     |

| -           | Sync<br>Payl<br>Logi<br>CTS/         | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (  | All I | denti  | fiers | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve                | ud ('001<br>(Tx) /                              | RFIC Read           | (RX) ('C | 0010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

| -           | Sync<br>Payl<br>Logi<br>CTS/         | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (  | A]] I | denti  | fiers | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve                | ud ('001<br>(Tx) /                              | RFIC Read           | (RX) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

|             | Sync<br>Payl<br>Logi<br>CTS/         | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (/ | A]] I | denti  | fiers | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve                | ud ('001<br>(Tx) /                              | RFIC Read           | (Rx) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

|             | Sync<br>Payl<br>Logi<br>CTS/         | Fie<br>oad<br>cal<br>RFU            | eld<br>Size<br>Chan<br>Bit |                  |           | F3G) | (= (, | All I | dent i | fiers | 5))          | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve<br>36          | ud ('001<br>(Tx) /<br>ed RFU (                  | RFIC Read           | (Rx) ('C | 0010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

|             | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | : Fie<br>oad<br>cal<br>'RFU<br>load | eld<br>Size<br>Chan<br>Bit | nel Tj           | ype       |      |       |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | nd ("001<br>(Tx) /<br>nd RFU (<br>/iew          | RFIC Read<br>('1'B) | (RX) ('C | 0010'B) | ***B2***<br>001<br>0100-<br>0 |         |       |     |

| -           | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       | 5))<br>DA 08 | a84b<br>32 b<br>RFIC<br>CTS         | b<br>bit Pa<br>Cont<br>/ Res          | ayloa<br>trol<br>serve<br>36          | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | 0010'B) | ***B2***<br>001<br>0100-<br>0 |         |       | _   |

| -           | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | : Fie<br>oad<br>cal<br>'RFU<br>load | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   |       |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 |         |       | _   |

| -<br>-<br>- | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 | _       |       |     |

| -<br>-<br>- | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('c | 0010'B) | ***B2***<br>001<br>0100-<br>0 | _       |       |     |

| -<br>-<br>- | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('t | D010'B) | ***B2***<br>001<br>0100-<br>0 | _       |       |     |

| ×           | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 | _       |       |     |

| ×           | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | D010'B) | ***B2***<br>001<br>0100-<br>0 | _       | _     | _   |

| -<br>-<br>- | Sync<br>Payl<br>Logi<br>CTS/<br>Payl | Fie<br>oad<br>cal<br>RFU<br>load    | eld<br>Size<br>Chan<br>Bit | nel Ty           | ype<br>04 | 05   | 06    |       | :      |       |              | a84b<br>32 b<br>RFIC<br>CTS<br>81 1 | b<br>bit Pa<br>Cont<br>/ Res<br>L6 00 | ayloa<br>trol<br>serve<br>36<br>Hex \ | ld ('001<br>(Tx) /<br>cd RFU (<br>/iew<br>0F AS | RFIC Read<br>('1'B) | (Rx) ('C | 0010'B) | ***B2***<br>001<br>0100-<br>0 | _       |       |     |

Figure 4. Logic Analyzer ability to acquire the data into memory, recognize the message packet structures, and format them for display in multiple formats.

## **Digital Test**

When it comes to analyzing the DigRF serial interface between baseband and RF, the logic analyzer is the tool of choice. The Tektronix TLA7012 logic analyzer with the TLA7AAx logic analyzer module has the ability to acquire the data into memory, recognize the message packet structures, and format them for display in multiple formats: a field-by-field listing of packet content; a hexadecimal listing of each packet; and an overview of data transmissions showing the time between packets. This is shown in Figure 4. With this capability, the TLA can verify the performance of the physical layer and the functionality of the DigRF device without relying on specialized external hardware. However there is more to testing a DigRF device than checking that it conforms to the standard. For a start, what if a designer is implementing a proprietary extension of DigRF? How does he or she verify that it is working properly? The DigRF solution from Tektronix has the flexibility to be customized so that it will recognize and handle proprietary extensions of the standard. By entering information about one's own protocol and packet structure, the Tektronix DigRF solution will be reconfigured to acquire and analyze a designer's own proprietary portions within the standard. What about debugging anomalies or errors within the DigRF transmission? With the use of filtering, long records of acquired DigRF data can be quickly sorted several different ways so that any series of events, or even individual events, can be analyzed. The advantage of this approach is that there is no need to reacquire the data. Everything needed is stored in memory, allowing designers to perform the complete analysis on a single set of data, thus removing the uncertainty that occurs when they have to make comparisons between different sets of acquired data.

Moving past the task of verifying that the device conforms to the standard, an important attribute of the logic analyzer is its ability to debug these devices. In these DigRF ICs, debugging is not a straightforward task. It can be a complex, time consuming process. Thankfully, the TLA7000 Series offers features and capabilities that simplify this task allowing, for quick debugging of designs.

With iCapture<sup>™</sup> multiplexing capabilities, the TLA7012 with a TLA7AA module can simultaneously make both digital and analog acquisitions through a single logic analyzer probe, enabling design engineers to analyze both digital and analog signal characteristics in order to effectively debug and verify their systems. Once the data is acquired, the logic analyzer display screen presents digital information as well as the analog waveform. The two waveforms are time-aligned so that the digital waveform can be examined with its analog waveform. Because of this time alignment and the high resolution acquisition of the TLA7000 Series, analysis of problems can be performed easily and quickly. Additionally, since this acquisition can be made with a single low capacitance logic analyzer probe, the signal under test is preserved and the engineer is provided with maximum signal fidelity and measurement accuracy.

Given the complex and transient nature of DigRF systems, the only way to trace challenging timing and glitch problems is with a logic analyzer with high resolution acquisition. The TLA7012 with MagniVu<sup>™</sup> provides simultaneous 125ps high resolution timing and state data with single probe, ensuring that glitches and other issues can be easily pinpointed.

With this leading acquisition technology and flexible DigRF analysis, the Tektronix TLA7000 Series offers engineers a complete solution for debugging and verifying their DigRF designs.

## Analog Test

The oscilloscope is another key component of the DigRF test bench. Although these designs tend not to use extremely high clock speeds, they are not immune to signal integrity issues, especially given their low power levels. Issues such as jitter, rise and fall time, cross talk, and others are all important parameters in DigRF devices. Problems in any of these parameters will affect the performance of the system.

Technical Brief

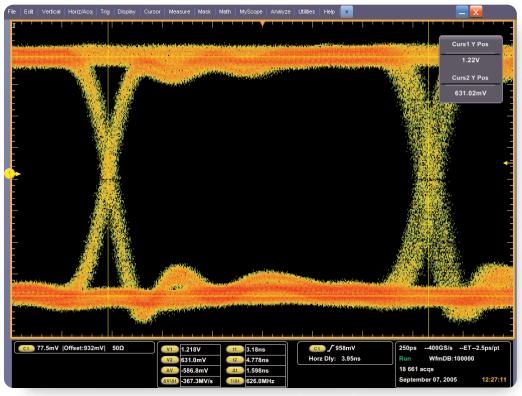

#### Figure 5. Real-time oscilloscope jitter and timing analysis.

Because it is one of the most common measurement tools used in electronic research, development, and engineering, the real-time oscilloscope is likely to be the first line of defense when jitter issues need to be investigated. But the Tektronix DPO7000 Series of real-time oscilloscopes is more than just an expedient choice. It is the ideal solution for many jitter applications and can address almost every kind of jitter measurement within reach of its bandwidth and resolution. Figure 5.

The DPO7000 owes its jitter measurement versatility to the fact that it can capture the entire signal waveform, every detail, for many operational cycles of the DUT. Because a long history of waveform activity is preserved in the oscilloscope's sample memory, attributes as varied as rise time, pulse width and jitter of all kinds can be studied.

#### RF

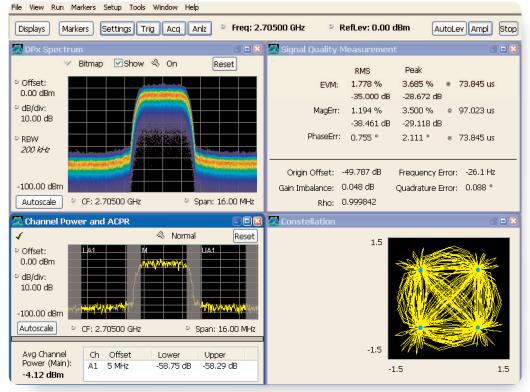

When it comes to testing the RF section, the instrument needs to be capable of verifying the frequency and modulation performance of the device, but also needed is something that is able to quickly troubleshoot the tough transient problems that exist in these modern Digital RF radios.

If the need is to find low-level signals, characterize a fast-moving transient, or understand how an RF signal changes over time, the unique Digital Phosphor<sup>™</sup> Technology (DPX<sup>™</sup>) is of value. This feature, standard in the Tektronix RSA6100A Series of real-time spectrum analyzers, reveals signal details that would otherwise be missed. The full-motion DPX Spectrum's live RF display delivers instant insight that accelerates discovery and diagnosis.

Figure 6. The RSA6100A Series captures signals that other analyzers miss with the unique frequency mask trigger.

The building of Digital RF systems increases the need to work with a real-time analysis tool. The Tektronix RSA6100A Series captures signals that other analyzers miss with the unique frequency mask trigger, which enables the capturing of complex signals into memory for complete analysis in all domains, shown in Figure 6. This capability, coupled with flexible modulation analysis, makes the Tektronix RSA6100A the tool of choice for characterizing and troubleshooting the RF section of a DigRF device.

## Summary

No matter what stage of the development you are involved in, when it comes to test equipment, flexibility is the key. Test equipment needs to be flexible enough to go beyond just verifying that the device under test is complying to the standard. Can the test equipment handle proprietary variation of the DigRF standard? Can it create real world inputs? What about non-compliant input signals? The answer to these questions should always be yes, because without these capabilities, the full capabilities of the design cannot be understood.

The DigRF solutions from Tektronix provide the flexibility and performance required to quickly bring products to market with the confidence of knowing that they will perform in any environment.

#### **Contact Tektronix:**

ASEAN / Australasia (65) 6356 3900 Austria +41 52 675 3777 Balkan, Israel, South Africa and other ISE Countries +41 52 675 3777 Belgium 07 81 60166 Brazil & South America (11) 40669400 Canada 1 (800) 661-5625 Central East Europe, Ukraine and the Baltics +41 52 675 3777 Central Europe & Greece +41 52 675 3777 Denmark +45 80 88 1401 Finland +41 52 675 3777 France +33 (0) 1 69 86 81 81 Germany +49 (221) 94 77 400 Hong Kong (852) 2585-6688 India (91) 80-22275577 Italy +39 (02) 25086 1 Japan 81 (3) 6714-3010 Luxembourg +44 (0) 1344 392400 Mexico, Central America & Caribbean 52 (55) 5424700 Middle East, Asia and North Africa +41 52 675 3777 The Netherlands 090 02 021797 Norway 800 16098 People's Republic of China 86 (10) 6235 1230 Poland +41 52 675 3777 Portugal 80 08 12370 Republic of Korea 82 (2) 528-5299 Russia & CIS +7 (495) 7484900 South Africa +27 11 254 8360 Spain (+34) 901 988 054 Sweden 020 08 80371 Switzerland +41 52 675 3777 Taiwan 886 (2) 2722-9622 United Kingdom & Eire +44 (0) 1344 392400 USA 1 (800) 426-2200 For other areas contact Tektronix, Inc. at: 1 (503) 627-7111 Updated 15 September 2006

Our most up-to-date product information is available at: www.tektronix.com

\$

Copyright © 2007, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.

4/07 FLG/WOW

52W-20776-0