| TekE    | press USB - (Untitled)*                                                    |           |            | Doptions •                 |

|---------|----------------------------------------------------------------------------|-----------|------------|----------------------------|

|         | Overall Test Result                                                        |           |            | Preferences •              |

| Setup   | Test Name                                                                  | PassFall  | Value      | Margin                     |

| Setup   | <ul> <li>UI-Unit Interval</li> </ul>                                       | Pass      | 200.433 ps | 492.963 fs & 627.037 fs    |

| -       | High Limit                                                                 | Pass      | 201.06 ps  |                            |

| Status  | Low Limit                                                                  | Pass      | 199.94 ps  |                            |

| tesults | <ul> <li>VTx-Diff-PP-Differentia</li> <li>I PP Tx voltage swing</li> </ul> | 📀 Pass    | 283.475 mV | 183.475 mV & 916.525<br>mV |

| _       | High Limit                                                                 | Pass      | 1.2 V      |                            |

| Reports | Low Limit                                                                  | O Pass    | 100.0 mV   |                            |

|         | TCOR_Slew_Max-Maximum Slew Rate                                            | Pass      | 3.663 ms/s | 6.337 ms/s                 |

|         | High Limit                                                                 | O Pass    | 10.0 ms/s  |                            |

|         | Low Limit                                                                  | N.A.      | NA         |                            |

|         | <ul> <li>Mask Hits</li> </ul>                                              | Pass      | 0.000      | 0.000                      |

|         | <ul> <li>DJ-Tx deterministic<br/>Jitter-Dual Dirac</li> </ul>              | Pass      | 39.710 ps  | 46.290 ps                  |

|         | <ul> <li>Eye Height -<br/>Transmitter Eye Mask</li> </ul>                  | 📀 Pass    | 171.099 mV | 71.099 mV & 1.029 V        |

|         | High Limit                                                                 | Pass Pass | 1.2 V      |                            |

|         | Low Limit                                                                  | O Pass    | 100.0 mV   |                            |

|         | WidthgütR                                                                  | 🥑 Pass    | 111.861 ps | 43.861 ps                  |

|         | High Limit                                                                 | R.A.      | NA         |                            |

|         | Low Limit                                                                  | O Pass    | 68.0 ps    |                            |

|         | Rj-Tx random                                                               | 🕗 Pass    | 1.290 ps   | 2.000 ps                   |

# Simplifying Validation and Debug of USB 3.0 Designs

# Application Note

#### Introduction

This application note will explain the evolution of the Universal Serial Bus (USB) standard and testing approaches that have been developed to accommodate the increasing speed and complexity of this popular communications standard.

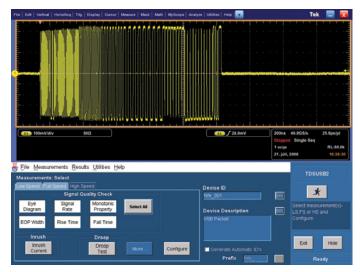

Figure 1. TDSUSB2 High speed compliance software.

#### History of USB 2.0

Universal Serial Bus has become known as the de facto standard for connecting personal computers and other peripheral devices. USB 2.0 was introduced in 2000 with 40x speed improvement over the legacy USB 1.1 specification. This specification opened the door for a more data-intensive applications and an improved user experience. While the

low speed (1.5 Mb/s) and full speed (12 Mb/s) rates were sufficient for devices like keyboards or mice the high speed rate (480 Mb/s) supported developments in the area of multimedia, data storage and transfer, and other high speed i/o applications.

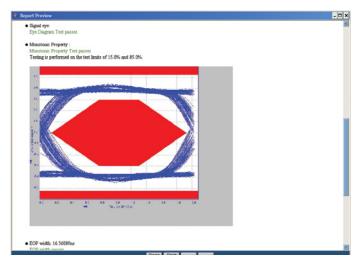

Figure 2. TDSUSB2 test report.

# USB 2.0 Architecture, Test Strategy and Solutions

USB 2.0 is a serial bus that utilizes a 4-wire system — VBUS, D-, D+ and Ground. D and D+ are the prime carriers of the information. There are three main groups of USB implementations: a host, device, and hub. USB 2.0 devices can be either self-powered (having their own power supply) or bus-powered (drawing power through the host).

The USB Implementers Forum (USB-IF) has outlined a set of required compliance tests for product certification which ensures robustness and interoperability. Products that meet the minimum performance levels for the USB-IF Compliance Program are added to the Integrators List. The scope of this application note focuses on performing electrical tests and providing guidance for debugging and resolving test issues.

Figure 1 shows the operation of the option USB compliance test package on a DPO7254 oscilloscope. This test package fully automates the signal quality test process, allowing designers to easily test their designs. A user must select the measurements to be performed for a particular signal speed (low, full or high speed). The test package eliminates manual, time consuming oscilloscope set-ups, cursor placements and can automatically compare test results with USB 2.0 specifications. Results are automatically displayed as part of a detail report and summary, as illustrated in Figure 2.

|                                   | USB 3.0                                                         | USB 2.0                                                                                |

|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Data Rate                         | 5.0 Gb/s                                                        | 480 Mb/s                                                                               |

| Signaling                         | 8b/10b encoding, AC coupling, Spread<br>Spectrum Clocking (SSC) | NRZI encoding, DC coupling, No SSC                                                     |

| Bus Power                         | 150mA for un-configured power and 900 mA for configured power   | 100 mA for un-configured and suspended devices and up to 500 mA for configured devices |

| Plug and Play/<br>Hot Swapping    | Asynchronous event handling                                     | Device polling                                                                         |

| Power management/<br>Link Control | Optimized Power Management with idle, sleep and suspend states  | Port-level suspend with entry/exit latency                                             |

| Cable/Interface                   | 2 Differential pairs, Half Duplex, Unshielded twisted pair      | 3 Differential pairs, Full Duplex, Shielded twisted pair                               |

Figure 3. Physical layer differences between USB 2.0 and 3.0.

#### USB 3.0 and Physical Layer Test Challenges

USB 2.0 technology adoption and acceptance highlights its success as a high bandwidth bus. The continued evolution of computing and data storage applications has presented new opportunities and challenges. Industry trends such as increasing memory storage capacities, accelerated video performance such as real-time video streaming and enhanced graphics processing units (GPU), and fast syncing of portable electronic devices with PCs have created a bottleneck with USB 2.0 performance.

USB 3.0 addresses the need for increased bandwidth to support applications that provide a more real-time experience. With billions of USB devices in use USB 3.0, referred to as SuperSpeed USB, also provides the necessary backwards compatibility to support legacy USB 2.0 devices. A list of physical layer differences between USB 2.0 and 3.0 are shown in Figure 3. Along with new capabilities SuperSpeed USB also brings new design and test challenges. USB 3.0 shares similar characteristics found in existing high speed serial technologies such as PCI Express<sup>®</sup> and Serial ATA: 8b/10b encoding, significant channel attenuation, and spread spectrum clocking. Those familiar with test methods for SATA and PCIe may be more prepared to handle the test challenges associated with USB 3.0. We'll review methods for compliance and how to get the most accurate, repeatable measurements possible for transmitters, receivers, cables and interconnects. Additional techniques for thorough characterization and debug will be presented to provide a complete test strategy.

#### Application Note

| Pattern | Value              | Desciption                                                           |

|---------|--------------------|----------------------------------------------------------------------|

| CPO     | D0.0 Scrambled     | A pseudo-random data pattern equivalent to logical idle without SKPs |

| CP1     | D10.2              | Nyquist frequency                                                    |

| CP2     | D24.3              | Nyquist / 2                                                          |

| CP3     | K28.5              | COM pattern                                                          |

| CP4     | LFPS               | Low Frequency Periodic Signaling                                     |

| CP5     | K28.7              | With de-emphasis                                                     |

| CP6     | K28.7              | Without de-emphasis                                                  |

| CP7     | 50-250 1's and 0's | With de-emphasis Repeating 50-250 1's and then 50-250 0's            |

| CP8     | 50-250 1's and 0's | Without de-emphasis Repeating 50-250 1's and then 50-250 0's         |

Figure 4. SuperSpeed USB Transmitter Compliance Test Patterns.

| Signal<br>Characteristic | Minimal | Nominal | Maximum | Units | Note       |

|--------------------------|---------|---------|---------|-------|------------|

| Eye Height               | 100     |         | 1200    | mV    | 2, 4       |

| Dj                       |         |         | 0.43    | UI    | 1, 2, 3    |

| Rj                       |         |         | 0.23    | UI    | 1, 2, 3, 5 |

| Tj                       |         |         | 0.66    | UI    | 1, 2, 3    |

Notes:

1. Measured over 10<sup>6</sup> consecutive UI and extrapolated to 10<sup>-12</sup> BER.

2. Measured after receiver equalization function.

3. Measured at end of reference channel and cables at TP1 in Figure 6-14.

4. The eye height is to be measured at the maximum opening (at the center of the eye width  $\pm$  0.05 UI).

5. The Rj specification is calcualted as 14.069 times the RMS random jitter for 10<sup>-12</sup> BER.

Figure 5. USB 3.0 Transmitter Eye height and jitter requirements.

### Transmitter Testing

#### **Compliance Measurements**

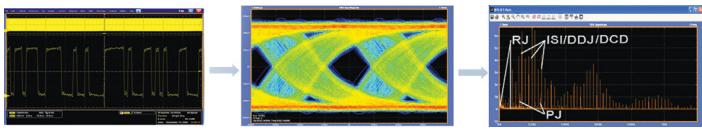

Transmitter testing is facilitated through the use of various test patterns, which are listed in Figure 4. Each pattern was selected for characteristics relating to the test under which the pattern is evaluated. CP0, a D0.0 scrambled sequence, is used to measure deterministic (Dj) jitter such as datadependent jitter (DDJ) while CP1, an unscrambled D10.2 full rate clock pattern, doesn't produce DDJ and is therefore better suited for evaluating random jitter (Rj). Jitter and eye height are measured with 1 million consecutive unit intervals after applying an equalizer function and appropriate clock recovery settings (2nd order PLL, closed loop bandwidth of 10 MHz and damping factor of 0.707). Jitter results are calculated by projecting beyond the measured data population to quickly extract jitter performance at  $1 \times 10^{-12}$  BER levels. For example, with jitter extrapolation the target Rj is calculated by multiplying measured Rj (rms) by 14.069.

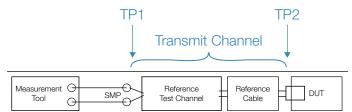

Figure 6. Transmitter test points.

| overall Test Result                                            |               |            | Preferences •              |  |  |

|----------------------------------------------------------------|---------------|------------|----------------------------|--|--|

| Test Name                                                      | Pass/Fail     | Value      | Margin                     |  |  |

| <ul> <li>UI-Unit Interval</li> </ul>                           | Pass          | 200.433 ps | 492.963 fs & 627.037 ft    |  |  |

| High Limit                                                     | 🔮 Pass        | 201.06 ps  |                            |  |  |

| Low Limit                                                      | 💙 Pass        | 199.94 ps  |                            |  |  |

| VTx-Diff-PP-Diff     I PP Tx voltage s                         |               | 283.475 mV | 183.475 mV & 916.525<br>mV |  |  |

| High Limit                                                     | 🕑 Pass        | 1.2 V      |                            |  |  |

| Low Limit                                                      | Pass          | 100.0 mV   |                            |  |  |

| TCDR_Slew_Ma     mum Slew Rate                                 | x-Maxi 🕜 Pass | 3.663 ms/s | 6.337 ms/s                 |  |  |

| High Limit                                                     | O Pass        | 10.0 ms/s  |                            |  |  |

| Low Limit                                                      | N.A.          | N.A        |                            |  |  |

| <ul> <li>Mask Hits</li> </ul>                                  | Pass          | 0.000      | 0.000                      |  |  |

| <ul> <li>DJ-Tx determini</li> <li>Jitter-Dual Dirac</li> </ul> | istic 🔮 Pass  | 39.710 ps  | 46.290 ps                  |  |  |

| Eye Height -<br>Transmitter Eye                                | Mask 📀 Pass   | 171.099 mV | 71.099 mV & 1.029 V        |  |  |

| High Limit                                                     | 🔮 Pass        | 1.2 V      |                            |  |  |

| Low Limit                                                      | 💙 Pass        | 100.0 mV   |                            |  |  |

| 🕨 🖬 Width@BER                                                  | 🦁 Pass        | 111.861 ps | 43.861 ps                  |  |  |

| High Limit                                                     | NA            | N.A        |                            |  |  |

| Low Limit                                                      | Pass          | 68.0 ps    |                            |  |  |

| Rj-Tx random     iitter-Dual Dirac                             | Pass          | 1.290 ps   | 2.000 ps                   |  |  |

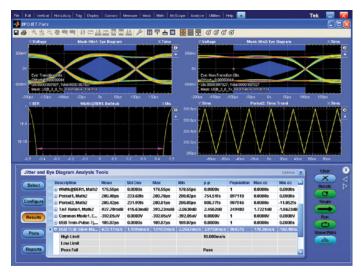

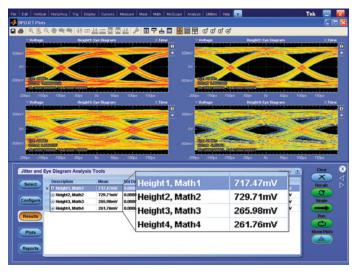

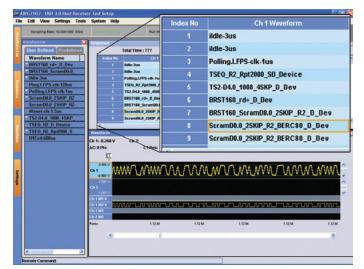

Figure 7. DPO/DSA70000 Series Option USB-TX for USB 3.0 Normative and Informative measurements.

Figure 8. USB 3.0 debug with DPOJET including custom control settings.

Figure 6 shows the normative transmitter compliance setup including the reference test channel and cable. Test point 2 (TP2) is located closest to the device under test (DUT) while test point 1 (TP1) is the far end measurement point. Note all Tx normative measurements are performed on signals at TP1.

After the signal is acquired at TP1 the data is processed using a software tool called SigTest, similar to official PCI Express compliance testing. For applications that require pre-compliance, characterization or debug other tools are available that provide additional insight into design behavior over varied conditions or parameters. The Tektronix MSO/ DPO/DSA70000 Series Oscilloscopes with option USB-TX enables execution of all USB 3.0 Normative and Informative PHY layer transmitter tests as shown in Figure 7. Singlebutton automation software tools like USB-TX save time by ensuring the test equipment is configured properly. This enables the testing to be accurately run by lab technicians instead of a senior engineer who has deep domain expertise in the USB specification. After the tests complete a detailed pass/fail test report highlights where design issues may occur. If there are discrepancies between different test locations (e.g. company lab, test house, etc.) the tests can be run again using the saved data from previous test run.

The TekExpress test automation software with Option USB-TX leverages the characterization and debug environment built upon the general purpose analysis capabilities of DPOJET. A flexible jitter and eye analysis software package provides more user-defined control of analysis parameters which helps speed in troubleshooting and makes design characterization much easier. For example, multiple eye diagrams can be displayed at one time allowing the user to analyze the effects of different clock recovery techniques or software channel models. Also different filters can be applied to analyze the effects of SSC for resolving system interoperability issues.

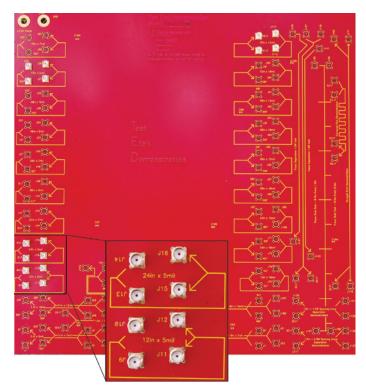

Figure 9. ISI board with 12 and 24 inch traces.

#### **Reference Test Channels**

There are two methods for capturing 'far end' signals at TP1. The first method is to use hardware-based cables and fixtures from USB-IF and acquire the data at TP1. The second method is to simulate the hardware channel effects in software using extracted models from TDR, VNA, or a simulator. The generally accepted channel model is an S-Parameter file, which includes magnitude and phase response effects. The signal is first

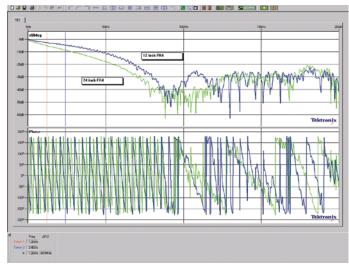

Figure 10. Magnitude and Phase response of 12 and 24 inch PCB traces.

acquired at TP2 or closest to the transmitter. The acquired data is then convolved with the S-Parameter file, which has been converted to a Finite Impulse Response (FIR) filter (for more information about applications for filters on Tektronix oscilloscopes see the white paper "Arbitrary FIR Filter Theory, Design, and Application" on www.tektronix.com).

This method allows the engineer to measure the device under test with specific channel requirements that are variable but also repeatable. For example, let's compare measurements of a 5 Gb/s signal across varying PCB trace lengths. Figure 9 shows an ISI test board with connections to 12 and 24 inch traces and Figure 10 provides the corresponding Sdd21 channel response.

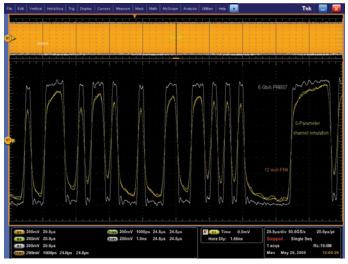

Figure 11. Hardware channel vs. Software emulation of 12 inch trace.

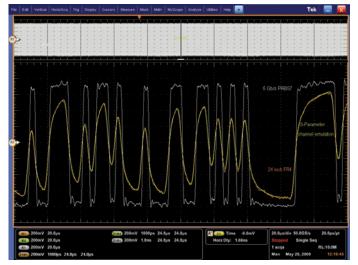

Figure 12. Hardware channel vs. Software emulation of 24 inch trace.

Figure 13. 5 Gb/s eye diagrams after 12, 24 inch traces with hardware (left) and software (right) channels.

The test signal is acquired both with and without the hardware channel included. Figures 11 and 12 show the original signal (white), far end hardware response (orange), and the original signal convolved with the S-Parameter data for each trace length. Figure 13 includes the eye diagrams from the hardware and software based test data.

#### Equalization

With significant channel attenuation SuperSpeed USB requires some form of compensation to open the eye at the receiver. To accomplish this, equalization, in the form of de-emphasis, is used at the transmitter. The nominal de-emphasis ratio specified is 3.5 dB or 1.5x in linear scale. As an example, with a transition bit level of 150 mV pk-pk the non-transition bit level would be 100 mV pk-pk.

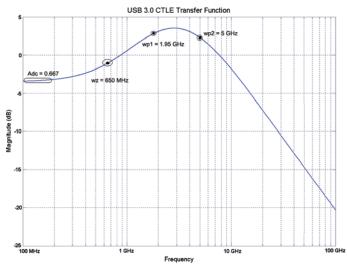

The compliance equalization model is a Continuous Time Linear Equalizer (CTLE). CTLE implementations include on-die, active receiver equalization or passive high frequency filters such as those found on cable equalizers. This model is well suited for compliance testing because of its simplicity in describing the transfer function. A CTLE is implemented with a set of poles and zeros in the frequency domain resulting in peaks at desired frequencies. As mentioned above, the TekExpress software with option USB-TX includes the reference compliance channels as well as the required CTLE filter, all combined into a single file.

$$H(s) = \frac{A_{dc}\omega_{p1}\omega_{p2}}{\omega_{z}} \cdot \frac{s + \omega_{z}}{(s + \omega_{p1})(s + \omega_{p2})}$$

$$A_{dc} = 0.667$$

$$\omega_{z} = 2\pi (650 \times 10^{6})$$

$$\omega_{p1} = 2\pi (1.95 \times 10^{9})$$

$$\omega_{p2} = 2\pi (5 \times 10^{9})$$

Figure 14. USB 3.0 CTLE transfer function and magnitude response.

Figure 15. SDLA equalization configuration for CTLE, FFE, and DFE.

Figure 16. 5 Gb/s signal (yellow) after de-emphasis (blue), long channel (white), CTLE (red) and 3 tap DFE (grey).

In addition to using compliance filters provided in the TekExpress automation software, designers can use the Tektronix Serial Data Link Analysis (SDLA) software to validate different CTLE parameters and how they impact link performance. Advantages of CTLE implementations are that they are simpler to design and they consume less power than alternative techniques. However in some instances they may not be adequate due to limitations in adaptation, precision, and noise amplification. Alterative techniques include Feed-Forward (FFE) and Decision-Feedback (DFE) equalization, which uses data samples weighted with scale factors to compensate for channel loss. CTLE and FFE are linear equalizers and as such both suffer from signal to noise degradation through boosting of high frequency noise. DFE, however, uses a non-linear component in a feedback loop thereby minimizing noise amplification and compensating for ISI. Figure 16 shows a 5 Gb/s signal after significant channel attenuation along with the equalized signals using de-emphasis, CTLE, and DFE techniques.

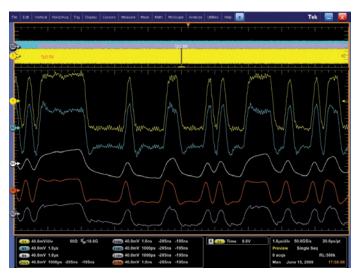

Figure 17. DPOJET software for advanced serial data characterization and debug.

#### Characterization and Debug

Throughout the process of design characterization and compliance testing invariably debug tools will be needed to resolve signal integrity or jitter issues. With added complexity of reduced margin for circuit and link problems silicon designers and system integrators need tools that incorporate intelligent statistical analysis capabilities along with visualization tools such as histogram, jitter spectrum, and BER "bathtub" plots. DPOJET analysis plots, like Spectrum and Trend, provide insight beyond simple measurements and results display. Trend analysis shows how timing parameters change over time, like frequency drift, PLL startup transients, or a circuit's response to power supply changes. Jitter spectrum analysis can show the precise frequency and amplitude of jitter and modulation sources such as adjacent oscillators and clocks, power-supply noise, or signal crosstalk. After a failure occurs it's important to be able to switch from "compliance-mode" using automated test software to a "userdefined" jitter and eye analysis toolset. The DPOJET software provides users with control over parameters such as clock recovery, filters, reference levels, Rj/Dj separation techniques, or measurement limits and gating. It also includes many timing, amplitude, and eye measurements in addition to the standard normative and informative USB 3.0 measurements.

An example procedure for debugging and analyzing jitter is shown in Figure 17. First the data is acquired with a relatively large data population for jitter analysis including the effects of SSC. One 33 kHz SSC cycle requires a 30 us time window. Once the data is acquired eye diagram analysis provides a quick visual indication of voltage and timing performance. This eye shows excessive periodic jitter and data-dependent jitter. Finally jitter decomposition is performed to isolate signal integrity problems. The jitter spectrum plot highlights jitter components and their corresponding relative amplitude and frequencies.

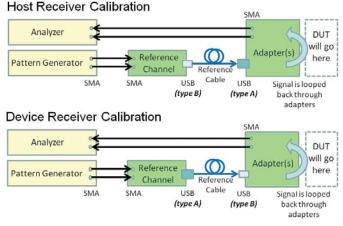

Figure 18. USB 2.0 and 3.0 receiver testing examples.

# Set AFBI Grad 0 Entrol (COC) (Sas (1007)(SOC))

# **Receiver Testing**

#### **Compliance Testing**

The purpose of USB receiver testing is to confirm a receiver's ability to correctly detect transmitted data at or below a target Bit Error Rate (BER) of 1x10<sup>-12.</sup> While the focus of transmitter testing is on amplitude, jitter and other parametric measurements a receiver test strategy usually involves a single test: jitter tolerance. Jitter tolerance ensures a receiver system will interoperate with a high degree of confidence with other products. The conditions of interoperability may vary widely with factors such as different cable lengths, low signal amplitudes, asynchronous reference clocks, and power management and link states. A good stressed eye calibration approach will ensure that jitter tolerance is reaching as many potential conditions as possible.

USB 3.0 compliance testing has changed significantly to accommodate the new challenges associated with a higher speed interface. Validation of a USB 2.0 receiver involves performing a receiver sensitivity test. A High Speed device must respond to a test packet at or above 150 mV and ignore (squelch) signals below 100 mV. SuperSpeed USB receivers must function with many more signal impairments and therefore the test requirements are more demanding than USB 2.0. While the USB 3.0 specification defines a target BER of 1x10<sup>-12</sup> the receiver compliance test strategy allows for shorter test times by increasing the deterministic jitter which creates an effective BER of 1x10<sup>-10</sup>. With increased Di and a lower effective Ri, based on a lower BER, this results in an equivalent Ti(BER) for both target BER levels. For USB 3.0 testing there are several testing options available to thoroughly evaluate USB 3.0 Rx devices.

Tektronix provides its customers with a choice between two solutions for automated receiver test for USB 3.0. For characterization testing, which is often done for first article silicon, instruments such as a BERTScope are available. A BERTScope Bit Error Rate Analyzer combines the capabilities of an enhanced high performance Bit Error Rate Tester (BERT), with the eye pattern display of an oscilloscope. For test scenarios where it is important to dynamically change parameters such as data rate, jitter profile or data patterns; a BERTScope provides versatile pattern generation and BERbased troubleshooting tools that supports the complete suite of measurements required for USB 3.0 Rx testing.

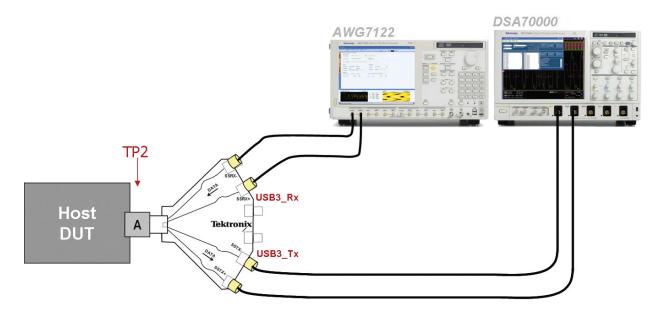

For conformance testing, where full automation is often required, a test platform using an Arbitrary Waveform Generator (AWG), Tektronix DPO/DSA/MSO70000 Series Oscilloscope and TekExpress automation software may be the best solution. The AWG7122 has the ability to emulate serial data streams, signal impairments and compliance channel channels simultaneously, drastically simplifying the test configuration. The DPO/DSA/MSO Oscilloscope, equipped with the Bit Error Rate Detector (Option ERRDT), provides error detection capability with automated configuration control. Both instruments are controlled by the TekExpress software which provides a simple and efficient way to automate testing for USB 3.0 transmitter/receiver hosts and devices consistent to the requirements specified by the Electrical Compliance Test Specification (CTS).

#### Receiver Characterization and Debug Testing

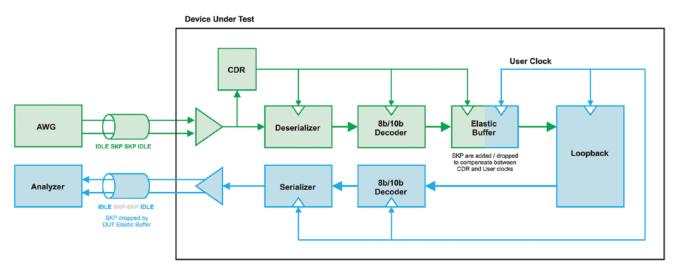

The primary basis of evaluating a receiver is determining the effective bit error rate. A known pattern is transmitted to the receiver and the data is verified after the receiver's comparator. Data is checked externally through a loopback mechanism inside the receiver. One of the challenges of receiver testing is generating the required test patterns and initiating test modes within the device under test.

Receiver testing for USB 3.0 is similar to other high speed serial bus receiver compliance testing, and is generally split up into two phases.

- Stressed eye calibration is the industry name for the procedure to create a worst case signal condition to test receivers. This worst case signal is usually impaired both horizontally by added jitter, and vertically, by setting the amplitude to the lowest a receiver would see when deployed. Stressed eye calibration must be performed when any of the test fixtures, cabling, or instrumentation have been changed.

- Jitter tolerance tests the receiver by using the calibrated stressed eye as input, and then applies additional sinusoidal jitter (SJ) of increasing frequency. This applied SJ exercises the clock recovery circuitry inside the receiver, so not only is the receiver being tested using worst case signal conditions, but its clock recovery is also explicitly tested. The magnitude and frequency of the applied SJ follows a template as prescribed by the standard. This jitter tolerance template covers the bandwidth of the clock recovery PLL; high amounts of applied SJ should be tolerated within the loop bandwidth since the clock recovery will track out this sinusoidal jitter, but only small amounts can be withstood beyond the loop bandwidth, since this jitter is not tracked out, and will affect the downstream receiver circuit.

This characterization process can be automated, ensuring accurate results and proper stressed pattern generation capability. Here is a review of the automated characterization functionality:

- Loopback initiation provides users who may otherwise be unable to perform receiver testing. Loopback initiation is a specific handshake between the BERTScope and device under test (DUT) that prepares the DUT for receiver testing. This is a key step that is a challenge for many customers, regardless of test instrumentation.

- Automated stressed eye calibration simplifies a procedure that can otherwise be tedious and time consuming.

- Jitter Tolerance testing is performed with a single click, and results are stored in a database for straightforward management of test results. The automated Jitter Tolerance test can also search for the limits of the device, termed "search for margin."

Figure 19. Stressed Eye Calibration with BERTScope BSA Series.

#### Stressed Eye Calibration

There are three impairment calibrations that must be made to calibrate the stressed eye, Random Jitter (RJ), Sinusoidal Jitter (SJ), and eye height. Each of these requires particular settings on the Tektronix BSA Series pattern generator and analyzer along with measurements made on the Tektronix MSO/DSA/DPO70000 Series Oscilloscope.

#### 1. Random Jitter (RJ)

- Definition: RJ is unbounded jitter that is not correlated to the data pattern, which means that its measurement should be the same regardless of the data pattern used. Because it is unbounded, it grows with measurement depth; the deeper the measurement in terms of number of waveforms measured, the larger the peak-peak RJ measurement becomes.

- How to adjust: To achieve the proper amount of RJ, the pattern generator must be able to adjust the amount of injected RJ.

- How to measure: The MSO/DSA/DPO70000 Series Oscilloscope with DPOJET can provide automated RJ measurements.

#### 2. Sinusoidal Jitter (SJ)

Definition: SJ is bounded jitter that is periodic in nature, but usually not correlated to the data pattern (unless the SJ frequency just happens to be a multiple of the pattern repetition frequency), so like RJ, its measurement is the same regardless of data pattern. Unlike RJ, it does not grow with measurement depth due to its bounded nature.

- How to adjust: Like RJ, the pattern generator must be able to adjust the amount of injected SJ to achieve the desired amount. The injected SJ must be of a particular frequency, with adjustable amplitude. All SJ frequencies and amplitudes in the USB 3.0 Jitter Tolerance Mask need to be calibrated.

- How to measure: The USB 3.0 compliance test procedures specify that the amount of SJ should be measured by taking the difference in Total Jitter (TJ) between a signal with 0 amplitude of injected SJ, and the desired amount of injected SJ. TJ measurements can be found on the DPOJET analysis option in the Tektronix MSO/ DSA/DPO 70000 Series Oscilloscope.

#### 3. Eye Height

- Definition: Eye height is the opening of the eye in the center of the unit interval and is accompanied by a measurement depth, in this case, 106 waveforms. The eye height is data pattern dependent because it is impacted by the amount of Data Dependent Jitter (DDJ) in the signal. The eye height specification is different for Hosts (180 mV) and Devices (145 mV).

- How to adjust: The eye height is adjusted via the output amplitude of the BERTScope pattern generator.

- How to measure: Eye height can be measured on a Tektronix MSO/DSA/DPO70000 Series Oscilloscope.

#### Jitter Tolerance Testing

Once the stressed eye has been calibrated, testing of the receiver can commence. As mentioned in the Introduction, USB 3.0 requires BER testing, unlike its 2.0 predecessor. Bit error ratio (BER) testing in the form of a Jitter Tolerance test is the only test required for USB3.0 receiver testing and it can be performed with a Tektronix BERTScope BSA Series Analyzer.

The Jitter Tolerance test exercises the receiver using worst case input signal conditions (the stressed eye calibrated in the previous section). On top of the stressed eye, a series of SJ frequencies and amplitudes covering the frequency range surrounding the -3 dB cutoff frequency of the JTF are injected into the test signal while the error detector monitors the receiver for mistakes or bit errors, and calculates the BER.

#### Automation Software on PC controls BERTScope, DPP, and CR

Figure 20. Setup for USB 3.0 Receiver Test.

The setup of equipment for receiver testing is similar to that of stressed eye calibration, with the DUT inserted into the test loop. Instead of the signal being routed straight back to the analyzer, the test signal from the pattern generator passes through the DUT's receiver, is "looped back" through its transmitter (hence, the term "loopback"), back through the adapter, and to the error detector. The connection to the error detector should be as high quality as possible. (See Figure 20)

For Jitter Tolerance testing, the test instrumentation must be able to perform error detection and keep track of the BER. Instruments such as BERTs and some protocol analyzers and oscilloscipes are capable of this function.

Loopback is one of the USB 3.0 link states in which the device sends the bits it receives back through its transmitter. If the receiver makes a mistake, the bit in error will be sent back through the transmitter and to the downstream analyzer for detection. To initiate loopback, a series of handshakes must be performed between the pattern generator and DUT.

USB 3.0 uses 8b/10 encoding, and as is common in 8b/10b encoded systems, the receiver and transmitter may be on slightly different clock frequencies – the recovered clock of the received data stream may not be exactly equal to the clock frequency of the transmitter. When in loopback mode for receiver testing, this mismatch in frequencies poses a problem for the DUT; bits may be coming in faster than they can be sent back out, or vice versa. To compensate for the frequency mismatch, clock compensation symbols are used and either deleted or inserted into the data stream as it is passed from the receiver back through the transmitter. For example, symbols are added if the recovered clock frequency is less than (slower than) the transmitter clock frequency and vice versa. USB 3.0 uses SKP symbols for clock compensation. The BERTScope BSA Series can be setup to handle this non-deterministic number of clock compensation symbols in the incoming data stream, commonly termed asynchronous BER testing. This may be difficult for some BERTs, as BER is typically measured by comparing the incoming data stream to a known data pattern. Protocol analyzers may be able to handle this mode of testing by maintaining the frame error count.

As a final note, the USB 3.0 specification includes two types of loopback for BER testing. The first is as described above, where the bits received are re-transmitted back to the analyzer for BER testing. The second relies on the DUT to keep track of its own BER, and report this back in bits embedded in special symbols called ordered sets. However, the second method is not included in the latest Compliance Test Specification.

Once the stressed eye has been calibrated, the DUT and equipment have been set up for testing, and the DUT has been put into loopback mode, the DUT's receiver is ready to be tested.

Jitter tolerance testing applies varying levels of SJ amplitude at specific SJ frequencies to test the receiver. The lower SJ frequencies tend to have higher SJ amplitude, as these frequencies are well within the loop bandwidth of the CR of the receiver and will thus get tracked out. As the SJ frequency approaches the loop bandwidth and surpasses it, the SJ amplitude levels out at an amplitude less than 1 UI. Jitter above the loop bandwidth of the receiver will not get tracked out, and will be passed down to the receiver's decision circuit.

The USB 3.0 CTS specifies that each SJ point on the tolerance curve be tested using 3x1010 bits. The DUT fails if more than one error is detected at any SJ test point.

For proper USB 3.0 receiver testing, the test regimen is wholly based on Jitter Tolerance using a calibrated stressed eye input. For receiver characterization and debug; the BERTScope BSA Series combines the calibrated stressed eye setup and automation capability to ensure a successful receiver test troubleshooting environment.

For conformance testing, the Tektronix AWG7000 paired with a Tektronix Oscilloscope and TekExpress automation software is a solid choice.

Figure 21. USB 3.0 Receiver Characterization Test Setup for Loopback BER.

Figure 22. Frame Error Detection with AWG and Oscilloscope.

#### Receiver Conformance Testing with an AWG

The primary basis of characterizing a receiver is determining the effective bit error rate. Using automation of a pat gen like an AWG7000, a known pattern is transmitted to the receiver and the data is verified after the receiver's comparator. Data is checked externally through a loopback mechanism inside the receiver. One of the challenges of receiver testing is generating the required test patterns and initiating test modes within the device under test. These test modes include forcing of the transmitter to "repeat" the detected data, after re-timing, out through the transmitter and invoking internal error detection states. The advantage of an arbitrary waveform generator (AWG) is its ability to sequence through required link training, enable entry into receiver loopback and issue loopback Bit Error Rate Test (BERT) commands. Figures 21 and 22 show an example process for testing a host using the loopback BERT method for test initiation and error detection as the AWG sequences through the steps below. The Tektronix DSA70000 real-time scope acquires and decodes the error count that is transmitted from the receiver. In addition to the internal BERT method a receiver can be characterized with external error detection. USB 3.0 requires separate reference clocks between a host and device which can result in differences in the local clock speeds. A SKP ordered set is used to compensate for the clock timing offsets within a link. Temporary buffering of symbols by the receiver is handled with an elasticity buffer. The elasticity buffer depth must be sufficient to handle extreme clocking differences including the effects of SSC. With a maximum tolerable frequency range of +/-300 ppm between a host and device and accounting for the effects of SSC (0 to -5000 ppm) this results in a worst case maximum frequency offset range of +300 to -5300 ppm. As mentioned previously USB 3.0 receivers include an internal bit error detection capability. Internal error detection is a cost-effective alternative to performing receiver testing. One limitation, however, is its

flexibility in pattern usage as pattern recognition is only supported with the CP0 pattern (scrambled D0.0). External error detection can be used to test other patterns such as CJTPAT or PRBS patterns, provided the error detector supports the pattern used. For validating external loopback there are two methods: synchronous and asynchronous error detection. Synchronous error detection means the pattern generator and error detector are timealigned with a common reference clock, resulting in a bit by bit evaluation of the receiver. Asynchronous error detection does not require a reference clock and is able to perform symbol error detection by removing or inserting idle characters such as SKPs. The error detection instrument is a protocol analyzer and in addition to error detection can also perform a variety of other functions such as traffic monitoring, emulate hosts, and perform link training.

#### Channel Emulation and Automation

With 5 Gb/s signaling and long host channels and cables this results in a closed eye at the receiver requiring equalization. Test specification developers define the requirements of a channel that will enable testing to worst case conditions, but practical enough for engineers to design and manufacture products in a cost-effective and efficient manner. After the channel model and budget are created they are validated to ensure actual physical layer performance matches expected results. Software simulation tools provide many degrees of freedom and allow for quick modeling and corner case testing. However at some point the model has to be produced into a physical channel for verification. Usually a reference design is fabricated on a PCB that provides similar electrical characteristics to the specification.

An alternative method to creating a channel model in hardware is to convert the model into a differential S-Parameter file and convolve the channel, including magnitude and phase effects, with the signal generator's test pattern. This method allows the engineer to drive the device under test with specific channel requirements that are variable but also repeatable. There are software tools available, such as Tektronix SerialXpress and BERTScope BSAUSB3, which can automate complex signal generation for USB 3.0 receiver testing by integrating all impairments into one signal. Complex jitter components such as Ri, Si, ISI, custom SSC modulation profiles, ISI scaling with fine granularity (e.g. 12 vs. 12.1 inch PCB traces), and pre-emphasis can be added simultaneously to create complex channel models that are often seen in real world environments. Figure 23 & 24 show examples of USB3 Receiver Test Automation Tools for consistent pattern generation and device control.

Figure 23. SerialExpress setup screen for AWG7000.

Figure 24. BSAUSB3 Automation Software setup screens.

## **Channel Measurements**

#### Compliance

At 5 Gb/s data rate, anything that affects a signal's rise time, pulse width, timing, jitter or noise content can impact reliability at the system level. To ensure signal integrity, it is necessary tounderstand and control impedance and losses in the transmission environment through which the signals travel. Mismatches and variations can cause reflections that decrease signal quality as a whole. USB 3.0 channel compliance helps minimize potential sources of performance degradation. The list below includes the required USB 3.0 channel measurements. The DSA8200 sampling oscilloscope, 80E04 TDR module with IConnect measurement software and A/B receptacle test fixtures provide complete channel compliance testing.

- 1. Impedance

- 2. Intra-Pair Skew

- 3. Differential Insertion Loss

- 4. Differential Return Loss

- 5. Differential Near-End Crosstalk

- 6. Differential Crosstalk between USB3.0 and USB2.0 Pairs

- 7. Differential to CM Conversion

Figure 25. DSA8200 Sampling oscilloscope with IConnect TDR/S-Parameter measurement software.

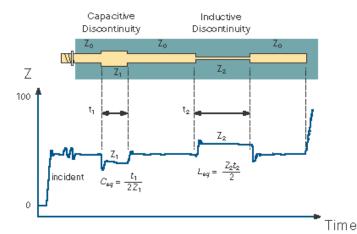

Figure 26. TDR uncovers impedance discontinuities.

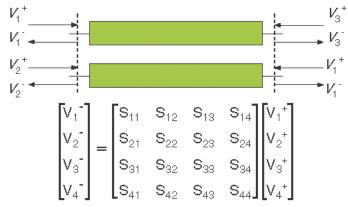

Figure 27. 4x4 matrix describes system of equations for computing 4 port S-Parameters.

|          |              | Differential    | Common          |

|----------|--------------|-----------------|-----------------|

| Response | Differential | Sdd             | Sdc             |

|          | Common       | S <sub>cd</sub> | S <sub>cc</sub> |

Figure 28. Differential and Common-mode stimulus and response.

#### Characterization and Debug

Impedance measurements are relative; they are made by comparing reflected amplitudes to incident amplitudes. Modern TDR instruments perform all of the calculations to compare the incident and reflected amplitudes with reported values in rho (reflection coefficient) or ohms. Figure 26 shows impedance variations from the characteristic impedance  $Z_0$  as the incident TDR step moves along from the connector to the end of the trace into an open circuit. Note the accuracy of this process is highly dependent upon the reference impedance of the TDR source, in this case  $Z_0$ .

S-Parameters (scattering parameters) have become more common-place in describing frequency domain network performance. They are defined in terms of incident and reflected waves at each port and describe power or voltages present as a function of frequency. Figure 27 shows the single-ended incident and return voltages relative to each port. A more popular measurement configuration is found in Figure 28 where measurements are performed in differential mode. S-Parameter measurements in mixed mode, including differential and common-mode measurements, offer advantages of insight into potential signal integrity issues. Differential measurements directly relate to signal attenuation as most of the signal's energy propagates in this mode. Common mode relates to skew and ground bounce. Mode conversion results in electromagnetic interference (Diff-CM) and electromagnetic susceptibility (CM-Diff). Finally cross-coupling between adjacent lines can produce crosstalk. Both impedance and S-Parameter measurements are invaluable to the designer as tools to identify potential signal integrity issues. In the timedomain TDR can isolate impedance discontinuities and even correlate simulation models to physical measurements. In the frequency-domain S-Parameters provide essentially a transfer function representation or behavioral model in relative terms.

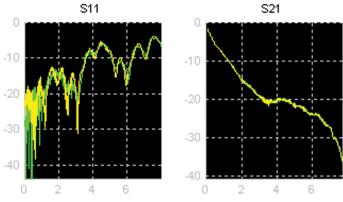

USB 3.0 measurements that can be made with TDR include differential impedance, frequency domain crosstalk, and S-Parameters including Sdd21 insertion loss and differentialto-common-mode conversion. These measurements are performed using a reference impedance of 45 ohms or 90 ohms differential. Since most TDR systems use a 50 ohm reference impedance the measured data will need to be normalized in software to the target 90 ohm differential reference impedance.

Figure 25. S-Parameters before (green) and after (yellow) 90 ohm normalization.

# Summary

In this application note we've explored many of the new challenges associated with USB 3.0 and have introduced tools needed for validation and debug of SuperSpeed designs. Since the advent of USB in the late 1990s Tektronix equipment has been used to certify millions of USB devices through industry plugfests and at independent test labs. USB-IF members can leverage the Platform Integration Lab (PIL) to test and correlate early designs. The PIL is available for USB devices perform correct USB 3.0 electrical and link level signaling

For more details about USB compliance testing visit the USB Implementers Forum page at www.usb.org. Here you will find detailed test procedures, white papers, and other support materials. Additional information about USB testing can be found at www.tektronix.com/usb. This site includes extensive materials like application notes, webinars and recommended test equipment.

#### References

- 1. D. Derickson, M Muller, Digital Communications Test and Measurement: High-Speed Physical Layer Characterization, - Prentice Hall, 2008

- 2. Universal Serial Bus Specification Revision 3.0 (2008). www.usb.org

- 3. USB 3.0 Electrical Compliance Methodology White Paper Revision 0.5, www.usb.org

- 4. Understanding and Performing USB 2.0 Physical Layer Testing, www.tektronix.com/usb

#### **Contact Tektronix:**

ASEAN / Australia (65) 6356 3900 Austria\* 00800 2255 4835 Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777 Belgium\* 00800 2255 4835 Brazil +55 (11) 3759 7627 Canada 1 (800) 833-9200 Central East Europe and the Baltics +41 52 675 3777 Central Europe & Greece +41 52 675 3777 Denmark +45 80 88 1401 Finland +41 52 675 3777 France\* 00800 2255 4835 Germany\* 00800 2255 4835 Hong Kong 400-820-5835 Ireland\* 00800 2255 4835 India +91-80-30792600 Italy\* 00800 2255 4835 Japan 0120-441-046 Luxembourg +41 52 675 3777 Macau 400-820-5835 Mongolia 400-820-5835 Mexico, Central/South America & Caribbean 52 (55) 56 04 50 90 Middle East, Asia and North Africa +41 52 675 3777 The Netherlands\* 00800 2255 4835 Norway 800 16098 People's Republic of China 400-820-5835 Poland +41 52 675 3777 Portugal 80 08 12370 Puerto Rico 1 (800) 833-9200 Republic of Korea +822-6917-5000 Russia +7 (495) 7484900 Singapore +65 6356-3900 South Africa +27 11 206 8360 Spain\* 00800 2255 4835 Sweden\* 00800 2255 4835 Switzerland\* 00800 2255 4835 Taiwan 886-2-2656-6688 United Kingdom\* 00800 2255 4835 USA 1 (800) 833-9200

> \* If the European phone number above is not accessible, please call +41 52 675 3777

> > Contact List Updated March 2013

#### For Further Information

Tektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit www.tektronix.com

- F

Copyright © 2013, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies.

07/13 EA/WWW

55W-23452-3