RapidIOアーキテクチャ: 次世代ネットワーキング・ インフラストラクチャの 構築

## ▶ はじめに

高性能パケット交換バス技術RapidIORは、通信市場における次世代ネットワーク機器の設計に必要なデータ帯域幅、 ソフトウェアの独立性、フォールト・トレランス、低レイテンシを提供します。

通信業界でデジタル・ハードウェアや組込み型ソフトウェアの設計に携わるエンジニアは、プロセッサの高速化やプロセッサにデータを供給するデータ帯域幅で発生するさまざまな問題に直面しています。なかでも、ボトルネックになっているのが、「ボックスの中の」さまざまなコンポーネントの相互通信速度です。

バックプレーンを経由し、チップ間および基板間を接続するために設計されたオープン通信規格RapidIOが、このボトルネックを解消します。RapidIOアーキテクチャにより、シャーシ内のチップ間および基板間でデータや制御情報が高速に転送でき、PCIなどの従来のバス技術のデータ帯域幅の制限をはるかに超えて、伝送速度を大幅に高速化します。

## RapidIOの仕様

RapidIOをオープン規格として開発、普及させていくのが RapidIO Trade Associationです。Trade Associationの運営委員 会は、TWG (テクニカル・ワーキング・グループ) およびMWG (マーケティング・ワーキング・グループ) を監督します。

現在取り組まれている仕様の開発、管理、保守は、運営委員会およびTWGのもとで専門分科委員会が行っています。この仕様では、1リンク1方向につき2.5Gbpsのデータ転送レートを持つ1Xシリアルから、1方向最高32Gbpsの1GHzクロック、16ビット・パラレルまでの広範なデータ幅、クロック・レートが規定されています。RapidIO仕様で定義されている中で最も一般的な仕様には、次のようなものがあります。

- ► 500MHzクロックを持つ8ビット・パラレル (1方向につき 8Gbps)

- ▶ 1×シリアル (1方向につき2.5Gbps)

- ▶ 4×シリアル (1方向につき10Gbps)

#### パラレルおよびシリアル仕様

RapidIOのパラレル仕様は、最大のデータ帯域幅、オーバヘッドの削減、低レイテンシを提供し、短距離伝送に用います。一方シリアル仕様は、パラレルよりも長い距離の伝送および最少ピン数、低消費電力を必要とするアプリケーション用です。

| 仕様          | パラレル      | シリアル     |

|-------------|-----------|----------|

| バス/リンク帯域    | 16、32Gbps | 1~10Gbps |

| バス/リンク全二重帯域 | 32~64Gbps | 2~20Gbps |

| ピン数         | 40~76     | 4 ~ 1 6  |

RapidIO Trade AssociationおよびRapidIO仕様の詳細については、Trade Associationのホームページwww.rapidio.org をご参照ください。

## RapidIOのアプリケーション

RapidIO技術の主要アプリケーションは、ネットワーク機器内の通信ファブリックで、第一にターゲットとするのは、ネットワークおよび通信機器、エンタープライズ・ストレージ、その他の高性能組み込み機器市場ですが、軍事や医療市場も潜在的な市場です。

チップ集積度の向上およびプロセッサ・チップとのインタフェースへの影響により、インタコネクトに関連するトランザクションの性質が根本的に変化し、クライアント/サーバ・モデルからピア・ツー・ピア・モデルへ移行しています。PCIバスを介してプロセッサに接続される今日のインタフェースは、実装には別のチップを必要とします。今後は、複数のインタフェース機能を備えた単一のチップに一体化され、最終的にこれらのインタフェースは、I/Oプロセッサ・チップに統合されるでしょう。こうしたトランザクション・モデルの変化により、PCIのようなI/Oバスの必要性は徐々に減少し、RapidIO技術は特に重要になります。

パラレルおよびシリアルのRapidIOコンフィグレーションは、レイテンシ、信頼性、電力消費、低コストが優先される組込み型アプリケーションおよびリアルタイム・アプリケーションに最適で、プロセッサ・バスや基板レベルの接続のように、市場を細分化する必要はなくなります。

パラレルRapidIO技術のアプリケーションは、チップ間実装から 基板間実装に及び、特にプロセッサ・バス、チップ間、内蔵カードのインタコネクト用に最適化されています。これは、 HyperTransport、PCI Express(3GIO)のほか、StarFabricおよび GigaBridgeが対象とするアプリケーションの一部と重複しています。

シリアルRapidIO技術は、バックプレーンおよびDSPファームのインタコネクト用に最適化されており、複数のコンピュータ・シャーシを単独のシステムとして接続するために使用します。このアプリケーションは、パラレルRapidIOと重複しており、InfiniBandが対象とするアプリケーションの一部に加えて、現在FibreChannelが使用されているアプリケーションにも拡大しています。

RapidIO技術は、基板上のチップ間を相互接続するためのバックボーンも提供します。また、ローカルI/Oバスのニーズが残っているPCIを補完するよう設計されています。

RapidIOは、レイテンシ、電力、コスト面の要求を満たすために、低レイテンシと簡単な実装が必要とされるシステム内での使用を目的としています。システム間の接続には、レイテンシが高くなる代わりに、システムの独立性を高めるInfiniBandやFibreChannelなどのSANソリューションを使用します。

## RapidIOの特徴と利点

## 性能

RapidIOファブリックベース・アーキテクチャは、システム内の すべてのチップおよびデバイスを直接相互接続し、10Gbps以上の 伝送速度をサポートするとともに、複数の同時トランザクション を可能にします。データ・パスは、8ビットまたは16ビット幅で、 データはクロックの両エッジでサンプリングされます。RapidIO では、LVDS技術の使用により、マルチGHzの速度まで、またポ ート幅は16ビットまで対応可能です。大量のデータ帯域幅が使用 でき、システムの性能は今日の階層バス・インタコネクトより数 百倍も向上します。

低レイテンシ(トランザクションの要求からトランザクションの 開始までに経過する時間)を実現するには、小容量のパケット・ ヘッダを使用し、ソフトウェア・プロトコル・スタックをなくし ます。この小容量ヘッダは、速く効率的に組み立て、分解を行え るように構成されており、オーバヘッドが少なくなっています。

RapidIOアーキテクチャには、最重要トランザクションの通過順 に優先順位を付ける機能があり、ポイント・ツー・ポイントを特 定し、伝送のサービス品質を維持できます。複数のメッセージ優 先レベルにより、非常に困難な条件下でも重要な送信内容が確実 に受信先に届くことが保証されます。

## スケーラビリティ

RapidIOアーキテクチャは、多くのシステム・トポロジ、アドレ ス・マップ、トランザクションをサポートするスケーラブルな技 術で、さまざまなアプリケーションに適合します。これらのトポ ロジには、ポイント・ツー・ポイント、リング、スター、リンク スター、メッシュ、任意のファブリックなどがありますが、スタ ー型が最も一般的です。

さらに、RapidIOスイッチ・ファブリックの通信帯域幅は、接続 デバイスの数に比例して増加します。RapidIOを使用したシステ ムでは、インタコネクトの劣化を最小限に抑えながら、実質的に 無制限の新しいデバイスや周辺機器が接続できます。

RapidIOリンクのデータ・レートは、さまざまなデータ幅および クロック周波数により決定されます。1つのシステムに異なる速 度のリンクが存在可能で、設計の柔軟性および転送互換性を最大 限にします。組み込み市場のさまざまな分野をサポートするため に、RapidIOインタコネクトには長期にわたって発展していく可 能性があります。

## 歴史

RapidIO技術は、Mercury Computers, Inc.およびMotorola Semiconductor Products Sectorによる共同開発から生まれました。両 社にはそれぞれ独自の高性能インタコネクト開発プログラムがありました。Mercury社は、大きな成功をおさめているRACEwayおよび RACE++アーキテクチャの新世代をターゲットにしていました。両社は、長年にわたるサプライヤと顧客の関係から互いの業務について認 識しており、また同じような目的を持っていたことから、自然に共同作業へと発展していきました。Mercury社はRACEway技術およびマ ルチプロセッサ・コンピューティング・システムにおける専門知識や技術を、Motorola社はチップ・アーキテクチャに関する専門知識や 技術、ネットワーキング市場へソリューションを提供する経験をこの共同プロジェクトに提供しました。

RapidlO技術の開発は、当初からさまざまな企業が参加する共同開発と想定されていました。まず、Motorola社の顧客であるネットワー ク機器メーカが初期の仕様開発に協力依頼され、その意見が取り入れられて、2000年2月にRapidIOが発表されました。その後まもなく RapidIO Trade Associationが結成されました。1年間の綿密な公開検討を経て2001年3月に最初の規格が承認されました。この仕様は、 RapidIOのホームページ www.rapidio.org からダウンロードできます。

## 信頼性

RapidIOアーキテクチャは、ハードウェアによるエラー検出および修正サービスをデータ転送パスの個々のリンクで行うことができる唯一の主要ファブリック・インタコネクトです。CRC識別アルゴリズムを使用してヘッダおよびデータ・ペイロードの破損を検出し、すべての制御パケットを重複して逆に送信することで、完全な保護を行います。

修正不可能なエラーの場合、パケットは再送されるため、パケットがなくなることはありません。問題が検出された場合、パケットのタイム・スタンプが記録され、エラー・リカバリに必要な時間を短縮できます。

RapidIOアーキテクチャは、確実に情報パケットを伝送します。パケットは、スイッチ・ファブリックを経由して一度に1つのリンクを進みます。ある特定のリンクがビジーの場合、パケットは戻るのではなく、リンクが空くまで待ちます。

#### 互換性

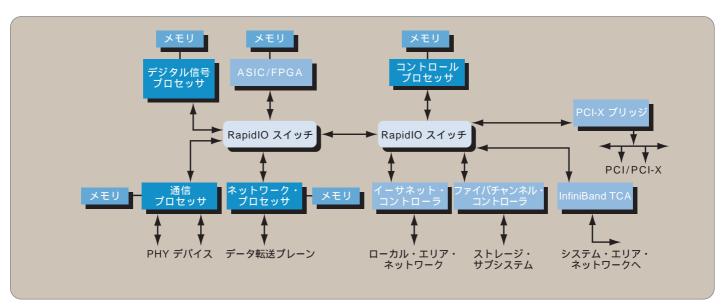

RapidIO技術は、マイクロプロセッサの外部インタフェースやPCIデバイス・ドライバなどの標準的なロードストア・アーキテクチャのデバイス上で、既存アプリケーションとのソフトウェア互換性を提供します。RapidIOアーキテクチャは、汎用プロセッサ、デジタル信号プロセッサ、通信プロセッサ、ネットワーク・プロセッサ、周辺機器、およびレガシー・バスとのブリッジ接続のための共通接続規格です。必要なマイクロプロセッサおよびI/Oトランザクションをすべてサポートし、既存アプリケーションおよびオペレーティング・システム・ソフトウェアに対して透過的で、ソフトウェア・ベンダはコア・システム・インタフェース・プログラムを書き直す必要はありません。ソフトウェアから見ると、RapidIOインタコネクトは、従来のマイクロプロセッサや周辺バスと同じです。

たとえば、RapidIOバス技術は、PCI、PCI-64、PCI-Xに簡単にプリッジ接続でき、PCIベース・システムに対して透過的で、特別なデバイス・ドライバを必要としません。また、RACEwayなどの既存インタコネクトおよびInfiniBandなどのSANインタコネクトに簡単にプリッジ接続できます。さらに、プロトコル・チップを使用してEthernet、ATM、USBなどとのインタフェースをとるためにRapidIO技術を取り入れることもできます。

▶ 図1. RapidIOアーキテクチャは、既存のシステムやネットワークへブリッジ接続するポイント・ツー・ポイント・インタコネクトです。

#### フレキシビリティ

RapidIOは、論理層、トランスポート層、物理層の3層構造に分か れ、他の2層に影響を及ぼすことなく、1つの層を自由に追加、変 更できます。

論理層は、PCIのような読み取りや書き込みトランザクション、 ポートベースのオペレーションを行い、デバイスはアドレス空間 が直接見えなくても、相互に通信できます。この層は、分散キャ ッシュ・コヒーレント・メモリ・サブシステムやオペレーティン グ・システムの基本要素などのグローバル共有メモリもサポート します。

トランスポート(ルーティング)層は、送信元および宛先デバイ スのIDを含むパケットを配信します。1つのシステム内のデバイ ス数は、64000個まで持つことができます。この層のピア・ツ ー・ピア・アーキテクチャにより、集中制御ではなく分散制御で き、共通ホストを通過する必要がありません。パケット・ペイロ ードのサイズは256バイトまでの可変で、複数のトポロジをサポ ートし、レイテンシを短くするための「真のスイッチング」を提 供します。

物理層は、パラレルとシリアルの2つのサブセットから構成され ています。8ビットまたは16ビットLP-LVDSパラレル・インタフ ェースにより、各方向に最高32Gbpsのデータ転送が可能です。 1×または4×のLPシリアル・インタフェース、すなわち1組のシ リアル・インタフェースまたは4組の連動シリアル・インタフェ ースは、各方向に最高10Gbpsのスループットを提供し、XAUI電 気仕様を採用、8B/10B符号化方式によりクロックの多重化と信 号の直流成分を減らすことでエラー保護しています。

## コスト

RapidIOインタコネクトは、低コストのフルカスタムASICベース およびFPGAベースの設計用に最小限のシリコン・チップ面積で 設計されているため、プロセッサの隅に実装でき、インタコネク ト処理に必要な実スペースを減らしています。シリアル・インタ フェースのRapidIOでは、DSPのような電力やピン数に要求が厳 しい設計のために非常に少ないピン数を実現しています。

RapidIOの標準FPGAとの互換性、今日のFPGAデバイスでは、 ほんのわずかな面積で実装可能な点、合わせてASICまたはマイ クロプロセッサに複数ポート実装が可能なことから、すばやいプ ロトタイピング、低コスト製造、新製品発表までの時間短縮が可 能です。設計エンジニアは、新しいI/Oチップに複数のRapidIO ポートを追加でき、専用スイッチングICを追加するコストをかけ ずに、ファブリック・インタコネクトの性能メリットが利用でき ます。

## マルチプロセシング対応

RapidIOアーキテクチャは、オプションの分散共有メモリ拡張機 能により、ハードウェア支援の対称型マイクロプロセッシングを 提供します。分散共有メモリは、コンピュータ・ワークステーシ ョン、サーバ市場で広く使用されており、高性能組込み型アプリ ケーションではさらに普及しています。またこの機能は、分散メ モリ・コントローラを持つシステム内の単独プロセッサのキャッ シュ・コヒーレンシを維持するためにも有用です。

このアーキテクチャは、Numa (物理アドレスを持つ) ccNuma、 メッセージ・パッシングなどの複数のプログラミング・モデルを サポートし、1つのシステム内で分散I/Oプロセッシングおよび汎 用マルチプロセッシングを同時に行えます。

## HIP (ハードウェア相互運用プラットフォーム)

RapidIOバス技術は、通信市場における次世代ネットワーク機器の開発に必要な広データ帯域幅、ソフトウェアの独立性、フォールト・トレランス、低レイテンシを提供しますが、解決しなければならない新しいコンプライアンスおよび相互運用性の問題ももたらします。

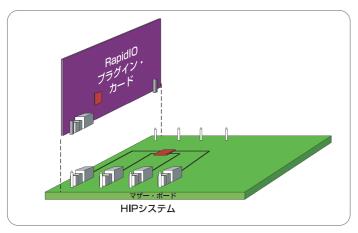

新しい規格を成功させるために重要な要素は、複数のベンダのシリコンをシームレスに組み込めることを示すことで、相互運用プラットフォームは不可欠です。RapidIOのHIP (ハードウェア相互運用プラットフォーム)アーキテクチャは、RapidIO技術に関わる複数のベンダによるプロトタイピングを促進するための手段です。このアーキテクチャは、シリコン・ベンダが相互運用性を示すための共通環境を提供し、多くの機器、半導体メーカに対して門戸を開放します。

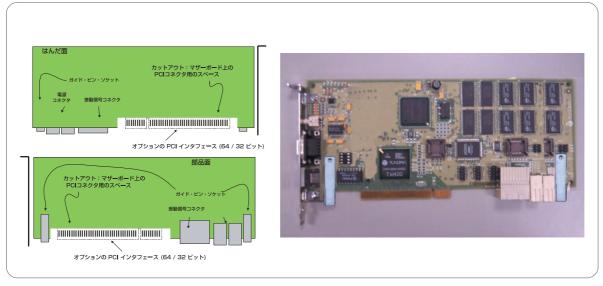

このHIPアーキテクチャでは、スイッチ・ファブリックとエンド・ポイントの大きさを共通にし、相互運用性テストに影響を与える重要な要素である電力およびRapidIOシグナル・パスに共通コネクタ、共通のピン配置にしています。このアーキテクチャは、マザーボードとRapidIOプラグイン・カードで構成されています。HIPマザーボードは、図2に示すように、RapidIOプラグイン・カードへのRapidIO接続を提供することを目的としています。

▶ 図2. HIPアーキテクチャ

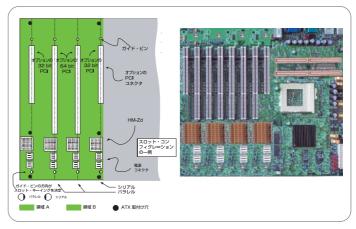

HIPマザーボードは、ATX仕様(REF3)に準拠しており、取り付け穴の位置、ATXの大きさ、RapidIOプラグイン・カード・スロット位置、電源コネクタ・タイプがATX仕様に適合するため、必要に応じてATX筐体内でマザーボードが使用でき、ATX電源を使用できるようになっています。電源コネクタの位置は、マザーボードと電源がATX筐体内に実装されている場合、標準ATX電源ハーネスの範囲内でなければなりません。ATX筐体が使用されている場合、電力は標準ATX電源から供給され、RapidIOプラグイン・カードにカード・ガイドを使用できます。図3はHPマザーボードの実装例です。

▶ 図3. HIPマザーボードの実装例

RapidIOプラグイン・カード・スロットを使用して、PCIまたは RapidIOプラグイン・カードを実装できます。RapidIOプラグイ ン・カードは、図3に示すように、使用するRapidIOコネクタの幅 から、標準PCIカード・スロット2個分を使用します。RapidIOプ ラグイン・カードにより、差動トレース信号ルーティングが簡単 に行え、またコンポーネントの高さに余裕ができるため、CPUの ヒート・シンクとファンを取り付けることができます。RapidIO プラグイン・カード・スロットは、電源コネクタ2個のほかに、 RapidIO差動信号コネクタをサポートし、追加PCIコネクタもオ プションでサポートできます。図4は、プラグイン・カード・ス ロットの実装例です。

HIPアーキテクチャは、シリコン・ベンダが相互運用性を示す共 通環境だけではなく、相互運用がうまくいかない場合には、なぜ シリコンはうまく相互運用できないのかを評価するる共通環境を も提供します。2つのポイント・ツー・ポイント・デバイス間の 2GHzのデータ・パスが通信に失敗すると、何が起きるでしょう か。エラーが発生すると、設計エンジニアは、エラーを正確に観 察、評価、解析、デバッグしなければなりません。

ロジック・アナライザ、オシロスコープ、プローブ、テスト・ソ フトウェアなどの測定器とこのプラットフォームを併用すること により、こうしたエラーを正確に評価、解析でき、確実に設計を 通信規格に準拠させることができます。

▶ 図4. プラグイン・カード・スロットの実装例

## RapidIOのプロトコルとトランザクション

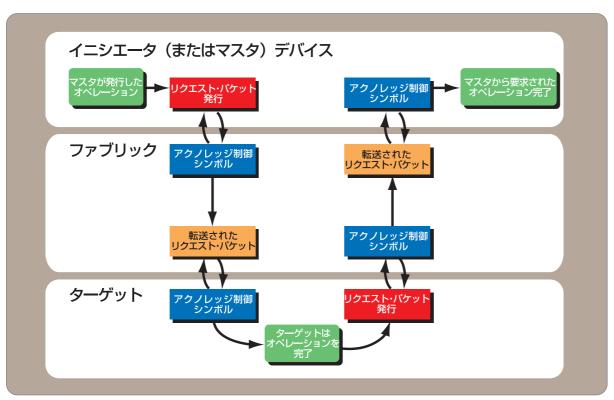

RapidIOのエンド・ポイント、つまりイニシエータ・デバイスとターゲット・デバイスが、直接接続されていることはまずありません。ほとんどの場合、メッセージやトランザクションは、間にあるRapidIOファブリックを通過します。通信要素、特にリクエスト・パケットとレスポンス・パケットの対は、システム内のエンド・ポイント・デバイス間でメッセージやトランザクションを伝送します。制御シンボルを使用して、パケット・アクノリッジ、フロー制御、メンテナンスの機能を実行し、RapidIO物理層のトランザクションのフローを管理します。

## RapidIOシステム内のパケットの流れ

図5は、RapidIOシステム内のパケットの流れを示しています。複雑なファブリックの場合、イニシエータ・デバイスとターゲット・デバイス間にはいくつかのファブリック・デバイスがあることがあります。これらのファブリック要素間で、パケットは同じ手順を経て保持、転送、通知されます。制御シンボルは、エラーの検出および再送信要求を示すこともあります。データ・ペイロードのサイズは、1 256バイトで可変です。

イベントは、次の順に発生します(図5参照)。

- (1) イニシエータ・デバイス、すなわちマスタは、リクエスト・パケットを発行してトランザクションを開始します。このパケットは、ファブリック・デバイスに送信されます。

- (2) ファブリック・デバイスはリクエスト・パケットをストアし、イニシエータ・デバイスにアクノリッジ制御シンボルを返信します。

- (3) リクエスト・パケットは、ターゲット・デバイスに転送されます。

- (4) ターゲット・デバイスは、ファブリック・デバイスにアクノリッジ 制御シンボルを返信し、要求されたオペレーションを実行します。

- (5) 要求されたオペレーションが完了すると、ターゲット・デバイスは ファブリック・デバイスにレスポンス・パケットを返信します。

- (6) ファブリック・デバイスはレスポンス・パケットをストアし、ター ゲット・デバイスにアクノリッジ制御シンボルを返信します。

- (7) レスポンス・パケットはイニシエータ、つまりマスタ・デバイスに 転送されます。

- (8) マスタ・デバイスは、ファブリック・デバイスにアクノリッジ制御シンボルを返信します。

- (9) 以上で、マスタ・デバイスはトランザクションが完了し、レスポンス・データがあればデータを受領したことを「認識」します。

▶ 図5. パケットの流れ

8

#### パケットの構築

図6は、リクエスト・パケットの構造を示しています。パケッ ト・フォーマットは、任意の幅をサポートしますが、特に1、4、 8、16、32ビット幅の物理インタフェースに最適化されています。 このフォーマットは、エンド・ポイントでのパケットの組み立て、 分解を簡単にするために分割されています。フィールドの上の数 字は、該当するフィールドのビット長です。

▶ 図6. パケット・フォーマット

図6のパケットのフィールドは、次のように定義されています。

S: データ・パケットか制御シンボルかを識別

ファブリック・デバイスまたはターゲットが制御シンボルで応答するパケット(またはグループ) AckID:

のID。RapidIOは、2つの隣接するデバイス間で最高8個の無応答パケットをサポート。

PRIO: パケットの優先順位、フロー制御で使用

使用するトランスポート・アドレスのメカニズムのタイプ TT:

フォーマット・タイプ。要求されているトランザクションを示す(以下を参照) Ftype:

Target Address: パケットが配信されるアドレス

Source Address: パケットの送信元

Transaction: 要求されているトランザクション(以下を参照) Size: エンコードされたトランザクションのサイズ

srcTID: ソース・トランザクションID。RapidIOデバイスは、2個のエンド・ポイント間で最高256の未処

理トランザクションを持つことが可能

Device Offset: メモリ・マップ方式のトランザクションのアドレス 「書き込み」オペレーション用。サイズは1~256バイト Optional Data Payload:

CRC: エラー検出用に中間挿入されるCyclic Redundancy Code。ロング・パケットにのみ存在。

Optional Data Payload: データ・ペイロード (オプション)

CRC: 最終エラー検出用CRC。ショート・パケット、ロング・パケットの両方に存在

## RapidIO

#### -▶ テクニカル・ブリーフ

レスポンス・パケットは、構造がよく似ています。リクエスト・パケットの「Size」フィールドは、レスポンス・パケットでは「Status」フィールドに置き換えられます。「Status」フィールドは、トランザクションが正常に終了したかどうかを示します。リクエスト・パケットの「srcTID」フィールドは、レスポンス・パケットでは「TargetTID」フィールドに置き換えられます。「TargetTID」フィールドには、対応するリクエスト・パケットのトランザクションIDが含まれています。リクエスト・パケットの「Device Offset Address」フィールドは、レスポンス・パケットにはありません。

リクエスト・パケットとレスポンス・パケットの両方に、「Ftype」と「transaction」フィールドが含まれていますが、これらは次の表に従ってトランザクションのタイプを定義するために使用します。

| Ftype | クラス                | トランザクション例                                      | 論理仕様     |  |  |

|-------|--------------------|------------------------------------------------|----------|--|--|

| 0、15  | ユーザ                | ユーザ定義                                          | すべて      |  |  |

| 1     | インターベンション・リクエスト    | 現在の「オーナ」からの読み取り                                | GSM      |  |  |

| 2     | ノン・インターベンション・リクエスト | ホームからの読み取り、非コヒーレント読み取り、I/O読み取り、TLB sync、ATOMIC | GSM、IOS  |  |  |

| _ 5   | 書き込み要求             | キャストアウト、フラッシュ、非コヒーレント書き込み、ATOMICスワップ           | GSM, IOS |  |  |

| 6     | ストリーミング書き込み        | ストリーム書き込み                                      | IOS      |  |  |

| 8     | メンテナンス             | コンフィグレーション、コントロール、ステータス・レジスタの読み取りおよび書き込み       | すべて      |  |  |

| 10    | ドアベル               | インバンド・インタラプト                                   | MSG      |  |  |

| 11    | メッセージ              | メールボックス                                        | MSG      |  |  |

| _13   | レスポンス              | 読み取りおよび書き込み応答                                  | すべて      |  |  |

| 3, 4, | 3、4、7、9、12、14 予約   |                                                |          |  |  |

GSM = グローバル共有メモリ拡張機能(オプション)

IOS = 基本的な入出力システム

MSG = メッセージ・パッシング拡張機能

## フロー制御

フロー制御は、RapidIO物理仕様の一部として定義されています。 フロー制御には、リトライ、スロットル、クレジットベースの3 つがあります。

フロー制御のリトライ・タイプは、フロー制御の最も簡単なメカ ニズムで、ハードウェアのエラー・リカバリ機構の一部でもあり ます。受信デバイスが、リソース不足のため、またはエラーが検 出されたためにパケットを受信できない場合、このデバイスはパ ケットの再送を要求する制御シンボルで応答できます。

フロー制御のスロットル・タイプでは、デバイスはアイドル制御 シンボルを使用してパケットの中央に「ウェイト・ステート」を 挿入できます。受信デバイスは、このアイドル制御シンボルを使 用して伝送速度を落とすように要求することもできます。

フロー制御のクレジットベース・タイプは、トランザクション・ バッファまたはバッファ・プールを備えたファブリック・デバイ スなどで使用されます。制御シンボルの中には、バッファ・ステ ータス・フィールドを持つものもあります。宛先デバイスにパケ ットを保存できる十分なバッファ・スペースがあるときのみ、送 信側はパケットを送信します。

## RapidIO**の実装**

基板対基板のRapidIO通信には、特別なバックプレーンが必要になりま すが、まだ仕様は策定されていません。しかし、バックプレーン上の汎 用高速シリアル接続を標準化するための取り組みは、シリアルRapidIO 技術に応用され、PICMGにおける新しいシリアル技術の活用に向けて進 められています。

## まとめ

RapidIOアーキテクチャが提供する伝送速度の大幅な高速化は、 次世代ネットワーク/通信機器の開発を可能にしますが、製品に RapidIOポートを搭載する前に解決しなければならないコンプラ イアンスおよび相互運用性の問題が伴います。

HIP (ハードウェア相互運用プラットフォーム)は、RapidIO技 術に関わる多くのベンダによるプロトタイプ化を促進するよう設 計されており、ベンダは相互運用性を示すことができます。この プラットフォームに、ロジック・アナライザ、オシロスコープ、 プローブ、テスト・ソフトウェアなどの測定器を使用すれば、エ ラー原因を判断するために必要なツールが実現します。

RapidIO実装のための当社のソリューションについては、 www.tektronix.co.jp/rapid\_io をご参照ください。

## RapidIO実装用の総合的なツール・セット

当社のトップクラスのロジック・アナライザ、高性能オシロスコープ、豊富なブローブが提供する、優れたブロービング、トリガ、表示、解析機能により、設計にRapidIOをすばやく簡単に採り入れることができます。

最新製品情報については、当社ホームページ(www.tektronix.com または www.tektronix.co.jp)をご参照ください。

Copyright C 2002, Tektronix, Inc. All rights reserved. Tektronix の製品は、発行済み、出願中を問わず、米国およびその他の国の特許法で保護されています。 本文書は過去に公開されたすべての文書に優先します。 仕様および価格は予告なしに変更することがあります。 TEKTRONIXおよびTEKはTektronix, Inc.の登録商標です。参照されているその他のすべての商品名は、該当する各会社が保有するサービス・マーク、商標、または登録商標です。 07/02 HMH/BT 5AW-15975-0

12 www.tektronix.co.jp/rapid io

Enabling Innovation

# 日本テクトロニクス株式会社

東京都港区港南2-15-2 品川インターシティ B棟6階 〒108-6106 製品についてのご質問・ご相談は、お客様コールセンターまでお問合せください。

## TEL 03-6714-3010 FAX 0120-046-011

電話受付時間/9:00~12:00·13:00~19:00 月曜~金曜(祝日は除く)

当社ホームページをご覧ください。http://www.tektronix.co.jp/お客様コールセンター ccc.jp@tektronix.com

●記載内容は予告なく変更することがありますので、あらかじめご了承ください。