## BERTScope<sup>™</sup> CR125A, 175A, & 286A Clock Recovery Fact Sheet

## Versatile Precision Clock Recovery and Analysis

| Features                                                                                                               | Benefits                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Rate Range up to 28.6 Gb/s                                                                                        | Continuous data rate coverage for next generation I/Os including PCIe 3.0, 10GBASE-KR, 16xFC, 25 & 28G CEI and 100GBASE-LR-4 & ER-4.                                                                                     |

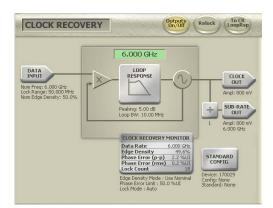

| Independent control, measurement, and display of phase lock loop (PLL) BW, JTF (jitter transfer function) and peaking. | Provides accurate "Golden PLL" response for transmitter jitter<br>compliance testing and stressed receiver sensitivity test<br>calibration. Provides full flexibility for device characterization.                       |

| Clock Recovery Input Equalization                                                                                      | Enables clock recovery on high ISI signals without impacting<br>the data stream under test. Recovered clock enables other<br>analysis including "clean eye", application of FIR filtering to<br>signal, and BER testing. |

| Edge Density Measurement                                                                                               | Allows instant determination of the mark density of the signal under test.                                                                                                                                               |

| Jitter Spectral Analysis and Frequency Gated<br>Integrated Jitter Measurements                                         | Provides 200 Hz to 90 MHz display of jitter vs frequency with cursor based measurements of jitter peaks' amplitude and frequency. Frequency gated integrated jitter measurements PCIe 2.0 compliance testing.            |

| Optional 24 MHz PLL BW                                                                                                 | Meets the JTF bandwidth requirements of USB 3.0, 6 G SATA, and PCIe-Gen 3.                                                                                                                                               |

| Extensive set of subrate (recovered) clock outputs.                                                                    | Frequently needed for device reference clocks.                                                                                                                                                                           |

"The choice for resolving analog issues in digital systems"

Instrumentation Quality Clock Recovery with BERTScope CR

## Taking the stress out of receiver testing

- BER Measurements and analysis to BER 10<sup>-12</sup>

- BER-contoured masks support analysis of specified 1×10–12 eye opening.

- Independent control, measurement, and display of phase lock loop (PLL) BW, JTF (jitter transfer function) and peaking

- Accurate jitter analysis/display of jitter spectral components from 200 Hz to 90 MHz

- Jitter Spectral Analysis and Frequency Gated Integrated Jitter Measurements

## BERTScope<sup>™</sup> CR125A, 175A, & 286A Clock Recovery Fact Sheet Key Specs and Ordering Information

| Models | Data Rate | Description               |

|--------|-----------|---------------------------|

| CR125A | 12.5 Gb/s | Clock Recovery Instrument |

| CR175A | 17.5 Gb/s | Clock Recovery Instrument |

| CR286A | 28.6 Gb/s | Clock Recovery Instrument |

| Recommended Software Options   |                                                                                                   |  |

|--------------------------------|---------------------------------------------------------------------------------------------------|--|

| GJ                             | Spectral Jitter Analysis                                                                          |  |

| PCIE                           | PCIe 2.5 and 5.0 G PLL Loop<br>Analysis (Requires Option GJ)                                      |  |

| Recommended Hardware Options   |                                                                                                   |  |

| XLBW                           | Extends PLL BW to 24 MHz                                                                          |  |

| Fixture, Cable and Kit Options |                                                                                                   |  |

| CR125ACBL                      | High Performance Delay Matched<br>Cable Set (required for BERTScope &<br>CR in SSC applications). |  |

| Service Options | Description                                      |

|-----------------|--------------------------------------------------|

| CA1             | Provides a single calibration event or coverage  |

| C3              | Calibration service 3 years                      |

| R3              | Repair service 3 years (including warranty)      |

| R1PW            | Repair service coverage<br>1-years post warranty |

| R2PW            | Repair service coverage<br>2-years post warranty |

| R3PW            | Repair service coverage<br>3-years post warranty |

| Key Applications                                                                                                       | Benefits                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Device &amp; Module<br/>Transmitter<br/>Compliance Test</li> </ul>                                            | <ul> <li>Provides clock recovery with<br/>the required "Golden PLL"<br/>BW and peaking for<br/>compliance testing</li> </ul>                                            |

| <ul> <li>Device &amp; Module<br/>Stressed Receiver<br/>Sensitivity and/or<br/>jitter tolerance<br/>testing.</li> </ul> | <ul> <li>The stressed data signal<br/>needs to be measured and<br/>calibrated using clock<br/>recovery with a compliant<br/>"Golden PLL" BW and<br/>peaking.</li> </ul> |

| <ul> <li>Signal Integrity of<br/>High Speed<br/>Communications<br/>Systems</li> </ul>                                  | <ul> <li>Support for Mask Testing,<br/>Jitter Peak, BER Contour,<br/>and Q-Factor Analysis<br/>enables a deep level of<br/>Signal Integrity insight.</li> </ul>         |

| <ul> <li>Design and<br/>Verification of<br/>Optical<br/>Transceivers</li> </ul>                                        | <ul> <li>Verifies performance using<br/>optical inputs and stressed<br/>eye analysis for Fibre<br/>Channel and IEEE803<br/>Ethernet Standards</li> </ul>                |