# Simplifying Validation and Debug of USB 3.0 Designs

- Tektronix USB Testing Solutions Introduction

## Agenda

- Introduction

- USB 3.0 SuperSpeed

- Why USB 3.0?

- Timeline

- Cable

- Transmitter

- Receiver

- Protocol analysis

- USB 2.0

- Introduction

- Compliance Testing

- Wireless USB

- Overview

- Compliance and Debug

Disclaimer: The material and content that describes specific details of the USB 3.0 specification (and SuperSpeed logo) belong to the USB 3.0 Promoters. Tektronix is not speaking or presenting on behalf of the USB 3.0 Promoters.

# **USB Industry Leadership**

- Tektronix 1<sup>st</sup> to market for USB 2.0

- Millions of certified products shipped, enabled by Tektronix USB solutions

- Only approved Method of Implementation (MOI) for WiMedia PHY Leadership in USB

- Tektronix is only T&M Technical Contributor in the USB 3.0 specification!

- Members of the Compliance Workgroup and Contributors to the Physical Layer Compliance Test Specification

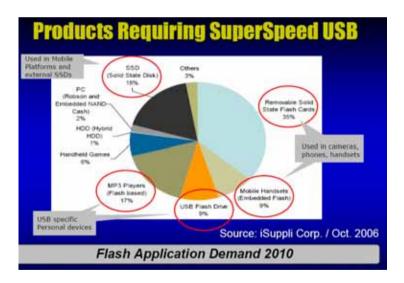

# Why SuperSpeed USB?

- USB 2.0 is adequate for many products...

- Emerging applications will benefit from higher performance.

- Something faster is needed for large digital multi-media files

| <ul> <li>User wait time requirement is 1½ minutes to synchronize</li> </ul> |           |           |           |          |           |          |  |  |

|-----------------------------------------------------------------------------|-----------|-----------|-----------|----------|-----------|----------|--|--|

|                                                                             | Song /Pic | 256 Flash | USB Flash | SD-Movie | USB Flash | HD-Movie |  |  |

|                                                                             | 4 MB      | 256 MB    | 1 GB      | 6 GB     | 16 GB     | 25 GB    |  |  |

| USB 1.0                                                                     | 5.3 sec   | 5.7 min   | 22 min    |          | 5.9 hr    |          |  |  |

| USB 2.0                                                                     | 0.1 sec   | 8.5 sec   | 33 sec    | 3.3 min  |           |          |  |  |

| USB 3.0                                                                     | 0.01 sec  | 0.8 sec   | 3.3 sec   | 20 sec   | 53.3 sec  | 70 sec   |  |  |

Source: USB-IF

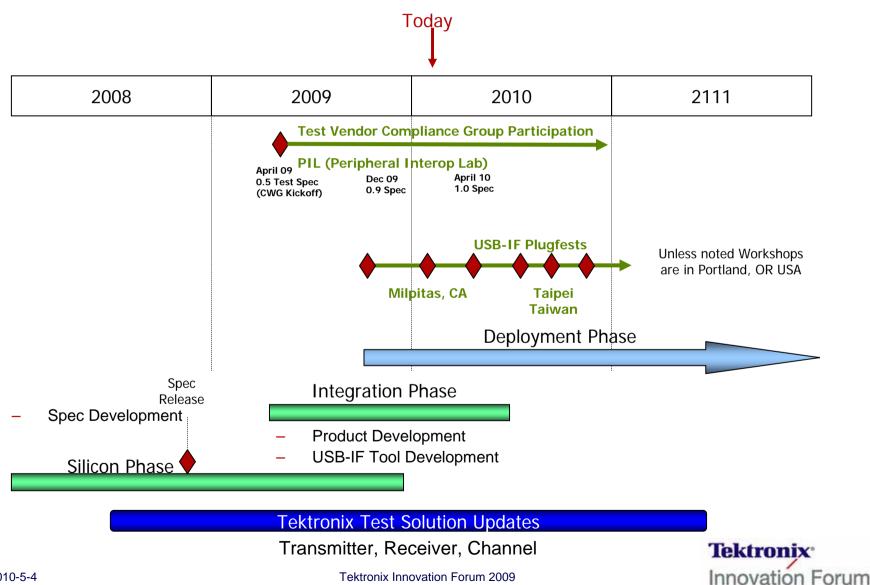

# USB 3.0 Technology Timeline & Tektronix Involvement

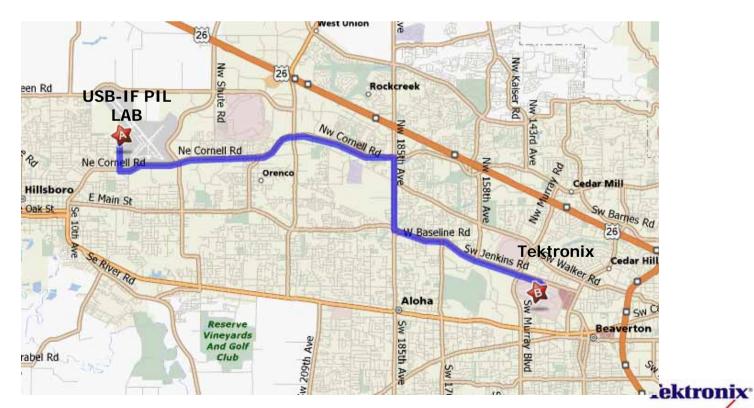

# USB-IF Platform Interoperability Lab (PIL) Collaboration

- The PIL is available for USB developers to test host and device interoperability and ensure that devices perform correct USB 3.0 electrical and link level signaling

- Tektronix is located less than 10 miles from the PIL

- Tektronix will work with you at the PIL or local Tektronix Technology Centers

- Contact your local Tektronix representative to schedule an appointment

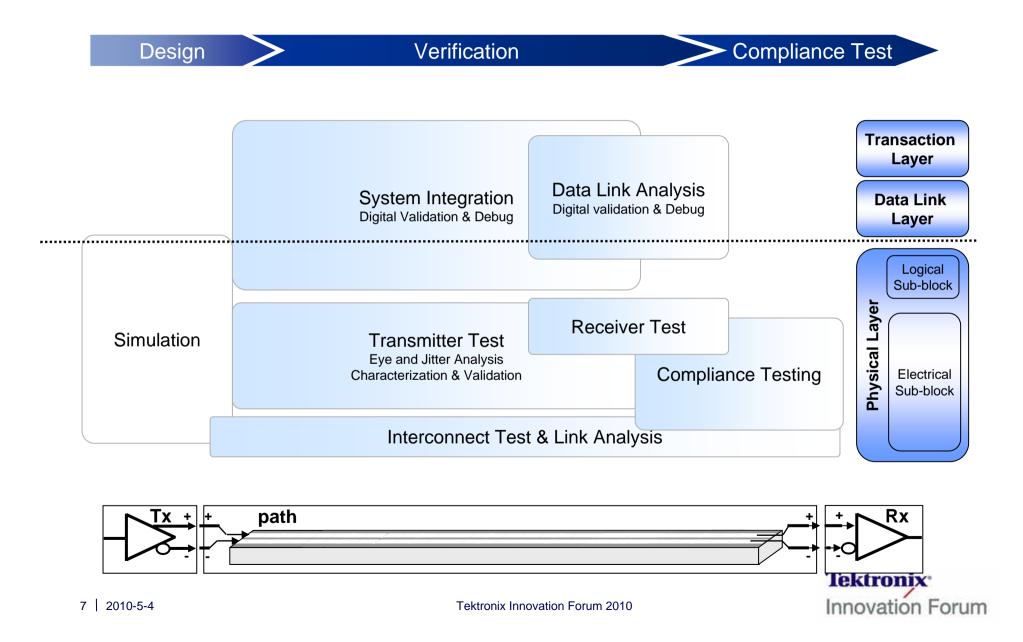

# High Speed Serial Test Challenges

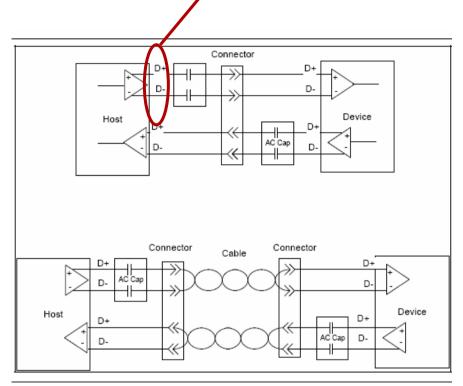

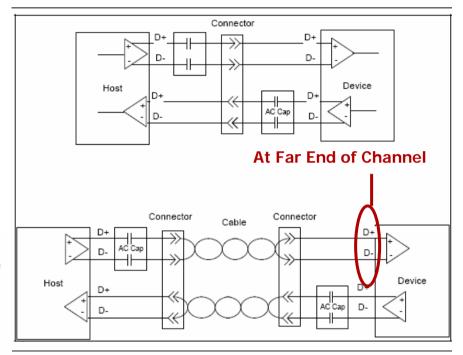

# Differences from High-Speed Electricals

- High-Speed

- 480MT/s

- No-SSC

- 2 wires for signaling

- Tx and Rx use the same wire

- 1 bi-directional link

- DC coupled bus

- NRZ encoding

- SuperSpeed

- 5.0GT/s (10X speed increase)

- SSC is required

- 4 wires for signaling

- 2 for Tx and 2 for Rx

- Each Uni-directional

- AC Coupled bus

- 8b/10b Encoded (Scrambing)

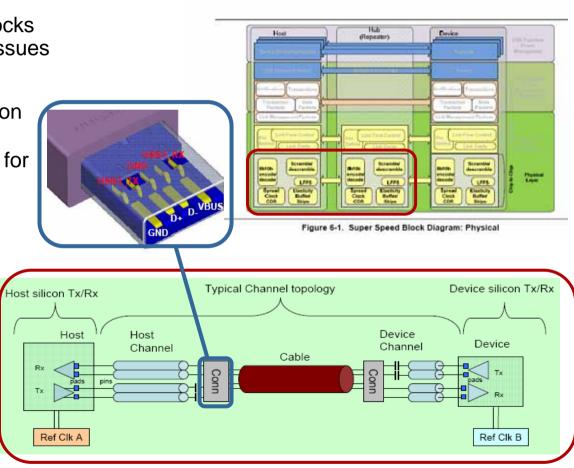

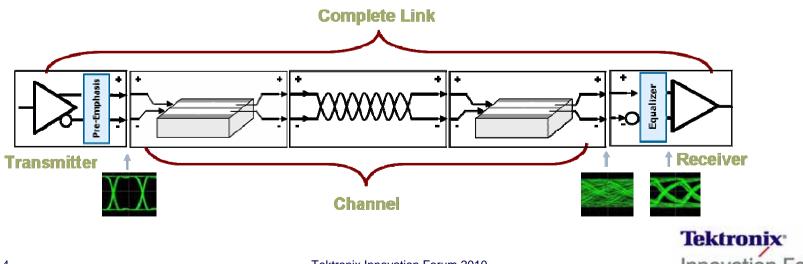

## **USB 3.0 Key Considerations**

- Receiver testing now required

- Jitter tolerance

- SSC, Asynchronous Ref Clocks can lead to interoperability issues

- Channel considerations

- Need to consider transmission line effects

- Software channel emulation for early designs

- New Challenges

- 12" Long Host Channels

- Closed Eye at Rx

- Equalization

- De-emphasis at Tx

- Continuous Time Linear Equalizer (CTLE) at Rx

- Test strategy

- Cost-effective tools

- Flexible solutions

**Physical Layer**

Source: USB 3.0 Rev 1.0 Specification

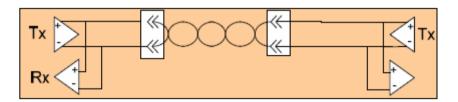

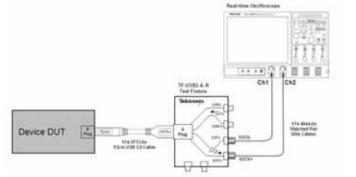

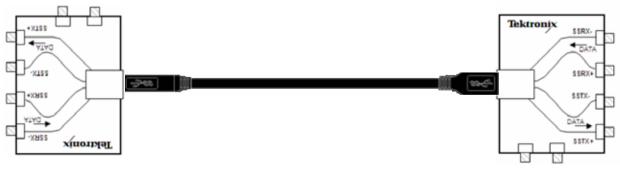

## Connecting to the Device Under Test

- For Host Tx/Rx Testing

- A Plug

- B Receptacle + Short USB3 Cable

- For Device Tx/Rx Testing

- A Receptacle + Short USB3 Cable

- For Cable Testing

- A Receptacle

- B Receptacle

- USB 2.0 for X-Talk

- For De-Embed

- A Receptacle mated with A Plug

### TF-USB3-A-P

World's Only Plug Style Fixture!

### **TF-USB3-AB-KIT**

Manufactured on single flat

## **Fixture Considerations**

- Acquire signal as close to the Silicon/Connector

- Host Testing

- A Plug

- B Receptacle + Short USB3 Cable

- Device Testing

- A Receptacle + Short USB3 Cable

- 13cm Cable Adds Error!

- 7% Amplitude Loss

- 500fs Rj

- 2.5ps Dj

|                  | 13cm Hosiden Cable w/    |      |       |        |  |  |

|------------------|--------------------------|------|-------|--------|--|--|

|                  | Tek B-Receptable Fixture |      |       |        |  |  |

|                  | No CTLE                  |      |       |        |  |  |

| D / 400          | Rj                       | Dj   | Tj    | Height |  |  |

| Port-420         | 1.8                      | 12.5 | 37.3  | 487    |  |  |

| Margin           | 1.5                      | 73.5 | 94.67 | 387    |  |  |

| Compliance Limit | 3.27                     | 86.0 | 132.0 | 100    |  |  |

## **USB** Characterization and Debug

Beyond Compliance

- USB 3.0 specification has informative measurements

- Measurements at silicon pads

- AC/DC parametric, common-mode measurements

- Complete link analysis with custom equalization functions

- De-embed fixture for accurate results

- Model channel and cable beyond required compliance reference channels

- Worst case channel analysis

- Cascading of S-Parameters for various interconnect topologies

- **Equipment considerations**

Informative Transmitter Measurements At Transmitter Pads

Measurement at Transmitter Pads Requires Tx Channel DeEmbed

Table 6-10. Transmitter Normative Electrical Parameters

| Symbol                     | Parameter                                                      | 5.0 GT/s                     | Units  | Comments                                                                                                                                                                                                                              |

|----------------------------|----------------------------------------------------------------|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                         | Unit Interval                                                  | 199.94 (min)<br>200.06 (max) | ps     | The specified UI is equivalent to a tolerance of ±300 ppm for each device. Period does not account for SSC induced variations.                                                                                                        |

| V <sub>TX-DIFF-PP</sub>    | Differential p-p Tx<br>voltage swing                           | 0.8 (min)<br>1.2 (max)       | V      | Nominal is 1 ∨ p-p                                                                                                                                                                                                                    |

| V <sub>TX-DE-RATIO</sub>   | Tx de-emphasis                                                 | 3.0 (min)<br>4.0 (max)       | dB     | Nominal is 3.5 dB                                                                                                                                                                                                                     |

| R <sub>TX-DIFF-DC</sub>    | DC differential impedance                                      | 72 (min)<br>120 (max)        | Ω      |                                                                                                                                                                                                                                       |

| V <sub>TX-RCV-DETECT</sub> | The amount of voltage change allowed during Receiver Detection | 0.6 (max)                    | V      | Detect voltage transition should be an increase in voltage on the pin looking at the detect signal to avoid a high impedance requirement when an 'off' receiver's input goes below ground. See Section 1.2.5.6 and Note 9 for details |

| C <sub>AC-COUPLING</sub>   | AC Coupling<br>Capacitor                                       | 75 (min)<br>200 (max)        | nF     | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself.                                                                                                |

| T <sub>CDR_SLEW_MAX</sub>  | Max slew rate                                                  | 10                           | ms/sec | See the jitter white paper for details on this measurement.                                                                                                                                                                           |

Table 6-11. Transmitter Informative Electrical Parameters at Silicon Pads

| Symbol                    | Parameter                                  | 5.0 GT/s    | Units | Normative | Comments                                                       |

|---------------------------|--------------------------------------------|-------------|-------|-----------|----------------------------------------------------------------|

| T <sub>MIN-PULSE-Dj</sub> | Deterministic min<br>pulse                 | 0.96        | UI    |           | Tx pulse width variation that is deterministic.                |

| T <sub>MIN-PULSE-TJ</sub> | Tx min pulse                               | 0.90        | UI    |           | Min Tx pulse at 10 <sup>-12</sup> including Dj and Rj.         |

| T <sub>TX-EYE</sub>       | Transmitter Eye                            | 0.625 (min) | UI    |           | Includes all jitter sources                                    |

| T <sub>TX—DJ-DD</sub>     | Tx deterministic jitter                    | 0.19 (max)  | UI    |           | Deterministic jitter only assuming the Dual Dirac distribution |

| CTX-PARASITIC             | Tx input<br>capacitance for<br>return loss | 1.25 (max)  | pf    |           | Parasitic capacitance to ground                                |

Source: USB 3.0 Rev 1.0 Specification

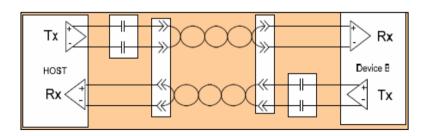

Figure 6-4. Channel Models without Cable (Top) and with Cable (Bottom)

| Symbol                          | Parameter                                                        | 5.0 GT/s             | Units | Normative | Comments                                                                                                                       |  |

|---------------------------------|------------------------------------------------------------------|----------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Rткос                           | Transmitter DC common mode<br>impedance                          | 18 (min)<br>30 (max) | Ω     |           | DC impedance limits to guarantee Receiver<br>detect behavior. Measured with respect to AC<br>ground over a voltage of 0-500mV. |  |

| Ітхановт                        | Transmitter short-<br>circuit current limit                      | 60 (max)             | mA    |           | The total current Transmitter can supply when<br>shorted to ground.                                                            |  |

| Vтивосм                         | Transmitter DC<br>common-mode<br>voltage                         | 0 (min)<br>2.2 (max) | V     |           | The instantaneous allowed DC common-mode<br>voltages at the connector side of the AC<br>coupling capacitors.                   |  |

| VTXIONACI<br>PP_ACTIVE          | Tx AC common<br>mode voltage<br>active                           | 100 mv               | m\/PP |           | Max mismatch from D+ D- for both time and<br>amplitude. While signaling.                                                       |  |

| VTX-CM-20-ACTIVE-<br>CLE CR. TA | Absolute Common<br>Mode Voltage<br>between U1 and<br>U0          | 200 (max)            | mV    |           | peak                                                                                                                           |  |

| Vтивывовтноєр                   | Electrical Idle<br>Differential Peak –<br>Peak Output<br>Vottage | 0 (min)<br>10 (max)  | mV    |           |                                                                                                                                |  |

| Vтыватес                        | DC Electrical Idle<br>Differential Output<br>Voltage             | 0 (min)<br>10 (max)  | mV    |           | Voltage must be low pass filtered to remove any<br>AC component.  This limits the common mode error when<br>resuming U1 to U0  |  |

13 | 2010-5-4

## **Accurate Transmitter Characterization**

Channel De-Embedding

- Measure true representation of signal at the Tx output

- Characterize channel with TDR or Simulator

- Import S-Parameter file

- Create fixture de-embed filter with SDLA software

- Identify root cause failures

- Removes fixture effects

- Improved margin

# **USB Channel Modeling**

- Understand transmitter margin given worst case channels

- Model channel and cable combinations beyond compliance requirements

- Easily create interconnect models with SDLA software to analyze channel effects

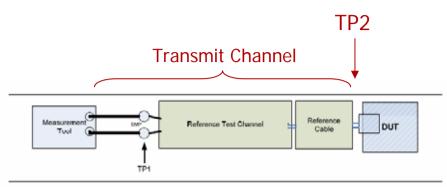

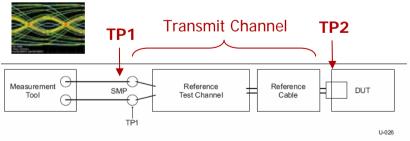

Figure 6-14. Tx Normative Setup with Reference Channel

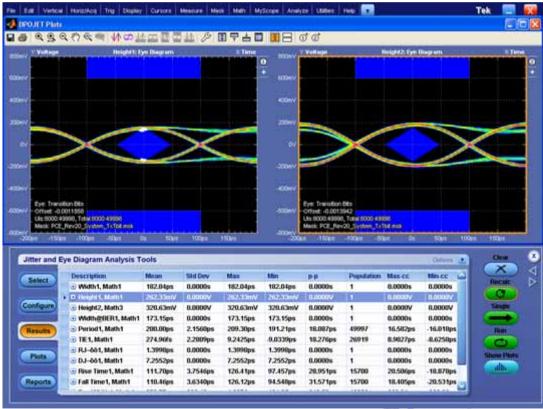

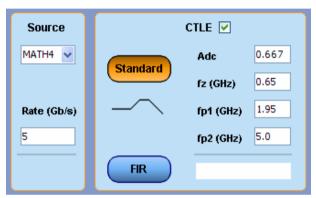

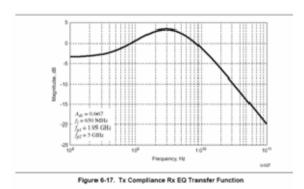

# **Custom Equalization Analysis**

- Equalizer models

- Pole, Zero, and Frequencies for Continuous Time Linear Equalizer (CTLE)

- Feed-Forward (FFE) and Decision-Feedback (DFE) Equalizers

$$H(s) = \frac{A_{dc} \omega_{p1} \omega_{p2}}{\omega_{z}} \cdot \frac{s + \omega_{z}}{(s + \omega_{p1})(s + \omega_{p2})}$$

$$A_{dc} = 0.667$$

$$\omega_{z} = 2\pi (650 \times 10^{6})$$

$$\omega_{p1} = 2\pi (1.95 \times 10^{9})$$

$$\omega_{p2} = 2\pi (5 \times 10^{9})$$

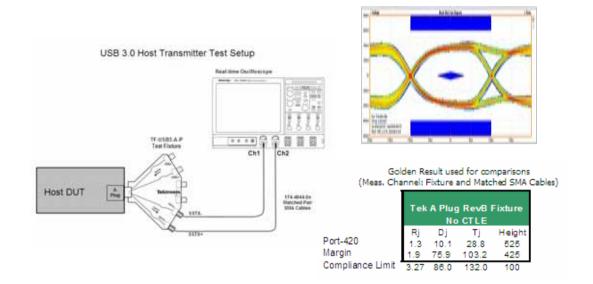

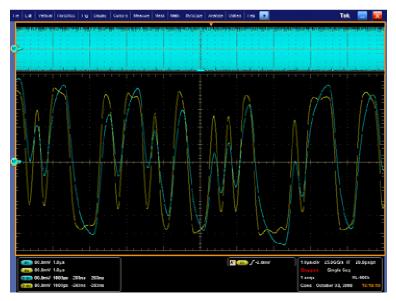

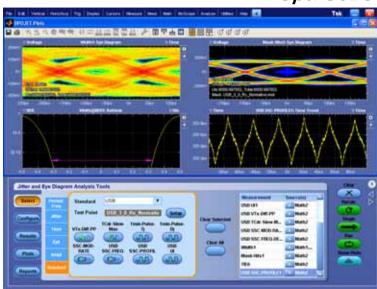

## Transmitter Compliance Testing (Normative Testing)

Channel Embedding

- Measurements at TP1

- HW Channel Probed at TP1

- CTLE applied in SW

- SW Channel Probed at TP2

- CTLE combined with Channel

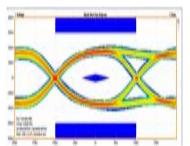

#### 6.7.2 Transmitter Eye

The eye mask is measured using the compliance data pattern CD1 described in Section 6.4.4. Eye Height is measured from 10<sup>6</sup> UI. Jitter is extrapolated from 10<sup>6</sup> UI to 10<sup>-12</sup>.

Table 6-12. Normative Transmitter Eye Mask

| Signal Characteristic | Minimal | Nominal | Maximum | Units | Note  |

|-----------------------|---------|---------|---------|-------|-------|

| Eye Height            | 100     |         | 1200    | m∨    | 2     |

| Dj                    |         |         | 93      | ps    | 1,2,3 |

| Rj                    |         |         | 60      | ps    | 1,2,3 |

| Tj                    |         |         | 132     | ps    | 1,2,3 |

#### Notes:

- Measured over 10<sup>6</sup> UI and extrapolated to 10<sup>-12</sup> BER

- 2. Measured after receiver equalization function

- 3. Measured at end of reference channel and cables at TP1 figure 6-14

Figure 6-4. Channel Models without Cable (Top) and with Cable (Bottom)

Figure 6-14. Tx Normative Setup with Reference Channel

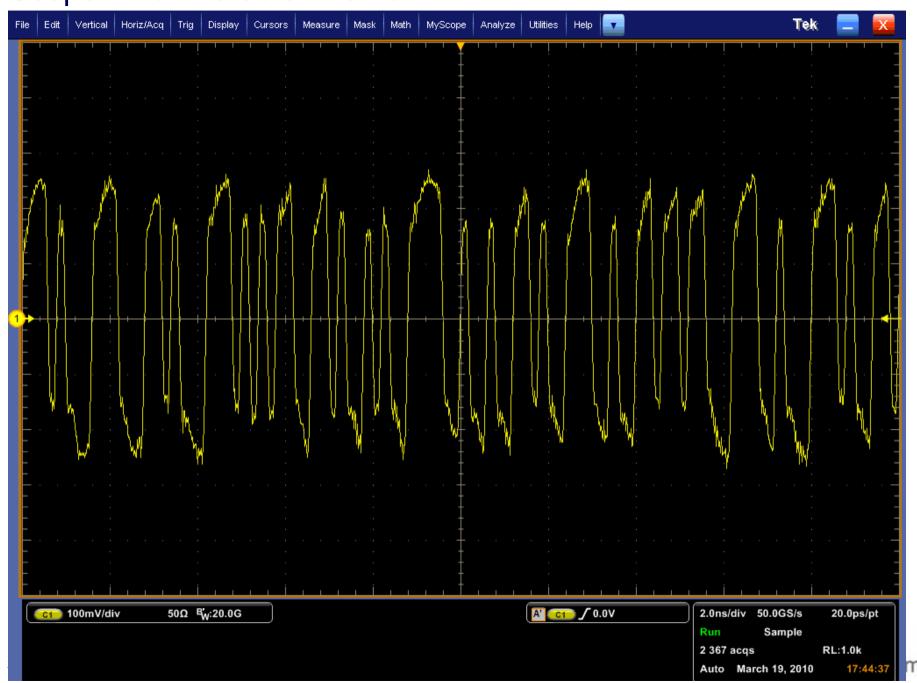

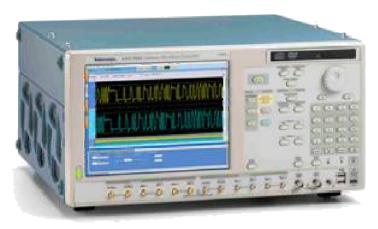

## Complete USB 3.0 Transmitter Solution

DPO/DSA70000B Series Oscilloscopes

Opt. USB3

- Tektronix Super Speed USB Fixtures

- 12.5 GHz Real-Time Scope

- 5<sup>th</sup> Harmonic Performance

- 50GS/s Sample Rate

- P7313SMA Differential Probe (Optional)

- Analysis software for validation and debug

- Serial Data Link Analysis SW (Optional)

- DPOJET with option USB3

- Automation software for characterization and compliance

- TekExpress with option USB-TX

TF-USB3-AB-KIT

Opt. USB-TX

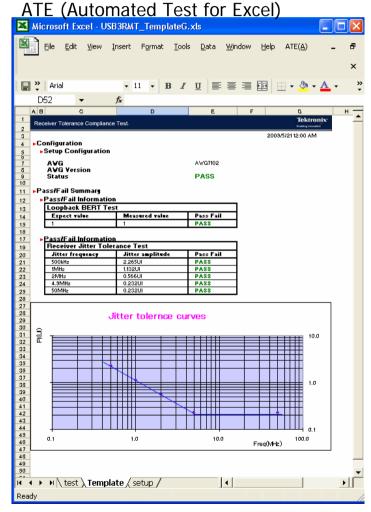

## Normative Receiver Tolerance Test

- SSC Clocking is enabled

- BER Test is performed at 10<sup>-10</sup>

- De-Emphasis Level is set to -3dB

- Voltage Level is set to 0.75V

- Each SJ term in the table below is tested one at a time after the device is in loopback mode

| Frequency | SJ    | RJ     |

|-----------|-------|--------|

| 500kHz    | 400ps | 2.42ps |

| 1MHz      | 200ps | 2.42ps |

| 2MHz      | 100ps | 2.42ps |

| 4.9MHz    | 40ps  | 2.42ps |

| 50MHz     | 40ps  | 2.42ps |

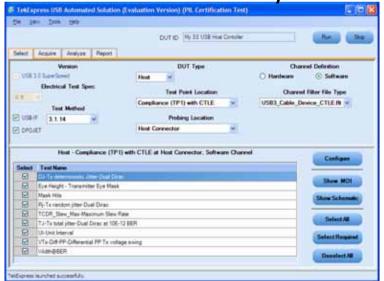

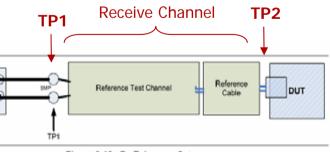

## Normative Receiver Testing

- Receiver processes the BERT Ordered Sets using 'built-in BERT' feature

- Impairment at TP1

- HW Channel Attached at TP1

- SW Channel Attached at TP2

#### 6.7.4.1 Loopback BERT

During loopback the receiver processes the BERT ordered sets BRST, BDAT, and BERC. These ordered sets are given in Table 6-14 through Table 6-17. BRST and BDAT are looped back as received. BERC ordered sets are not looped back but are replaced with BCNT ordered sets. Anytime a BRST is received the error count register EC is set to 0 and the scrambling LFSR is set to 0FFFF h. Any number of consecutive BRST ordered sets may be received.

BRST followed by BDAT starts the bit error rate test. BDAT sequence is the output of the scrambler and is equivalent to the logical idle sequence. It consists of scrambled 0 as described in Appendix B. As listed in Appendix B, the first 16 characters of the sequence are reprinted here:

FF 17 C0 14 B2 E7 02 82 72 6E 28 A6 BE 6D BF 8D

The receiver must compare the received data to the BDAT sequence. Errors increment the error count register (EC) by 1. EC may not rollover but must be held at FFFF h. The LFSR is advanced once for every character except SKPs. The LFSR rolls over after 2^16 symbols. SKPs inserted or deleted as necessary for clock tolerance compensation.

Source: USB 3.0 Specification

Figure 6-18. Rx Tolerance Setup

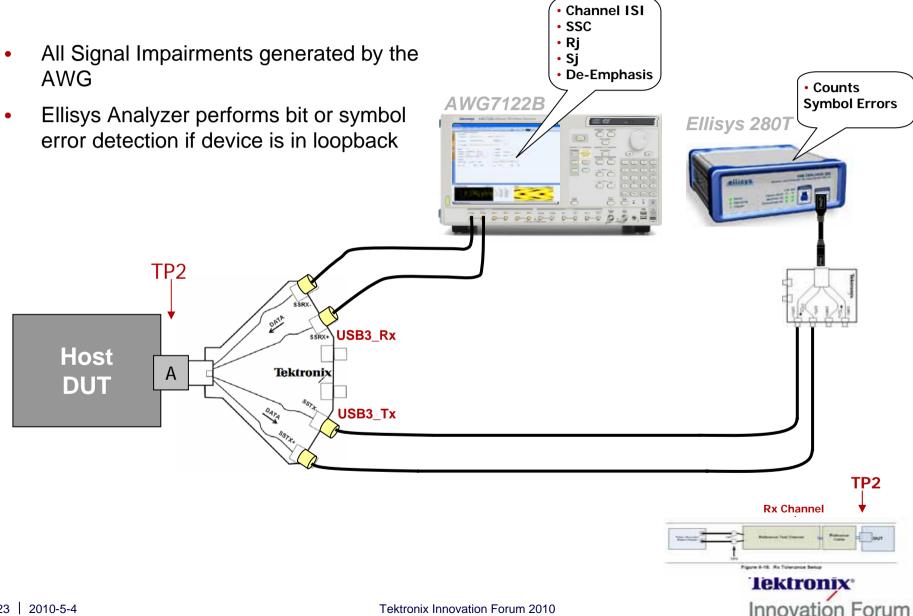

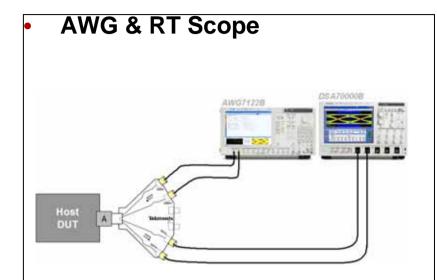

## Receiver Test Setup (with SW Channel Emulation)

Oscilloscope Based Error Detection Bit or Symbol Error · Channel ISI Detection SSC - OR -Common configuration for Receiver and • Rj BERC Decode **Transmitter Testing** • Si De-Emphasis All Signal Impairments including channel DSA70000B AWG7122B impairments generated by the AWG No need for external error detectors Oscilloscope performs bit or symbol error detection Scope performs BERC decode if internal error detector is used TP2 USB3 Rx Host **Tektronix** DUT USB3\_Tx TP2 **Rx Channel** Tektronix\* 21 | 2010-5-4 Innovation Forum

# Scope Error Detector Demo

## Receiver Test MOI (with SW Channel Emulation)

Protocol Analyzer Based Error Detection

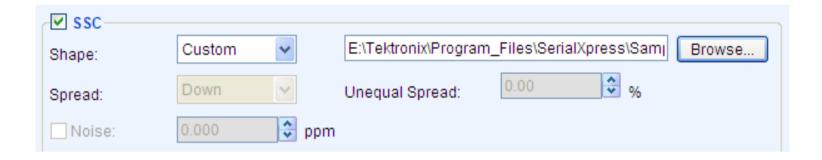

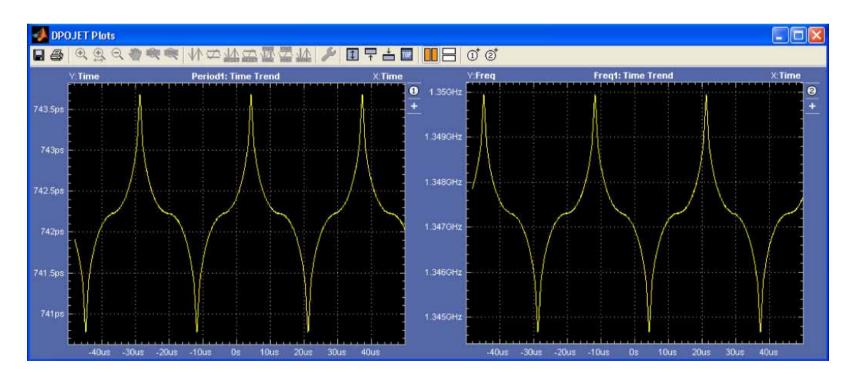

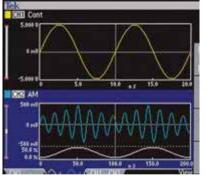

# **Custom SSC**

## SerialXpress SW

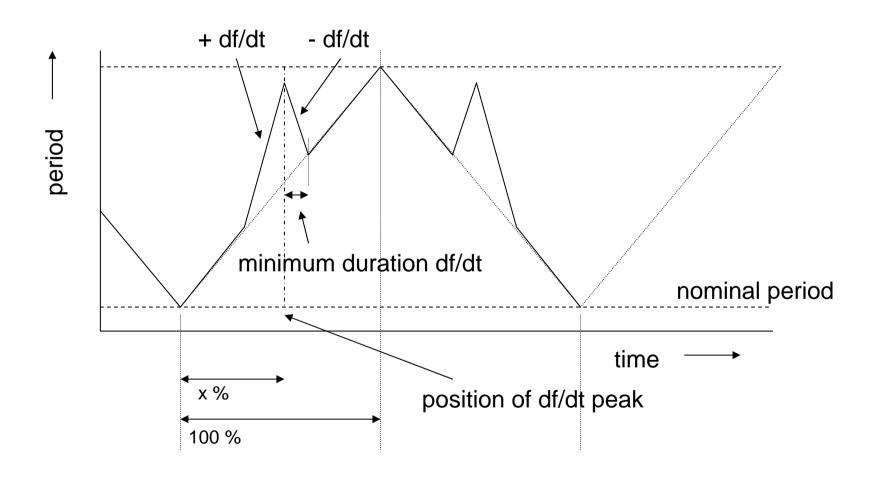

# SSC Slew Rate

## Receiver Compliance & Margin Testing

Early Market Automated Test Solution

Table 6-19. Input Jitter Requirements for Rx Tolerance Testing

| Symbol                 | Parameter                                     | Value  | Units  |

|------------------------|-----------------------------------------------|--------|--------|

| f1                     | Tolerance corner                              | 4.9    | MHz    |

| J <sub>RJ</sub>        | Random Jitter                                 | 0.0121 | UI rms |

| J <sub>R]_P-p</sub>    | Random Jitter peak- peak at 10 <sup>-12</sup> | 0.17   | UI p-p |

| J <sub>PL</sub> 500kHZ | Sinusoidal Jitter                             | 2      | UI p-p |

| J <sub>PL1Mhz</sub>    | Sinusoidal Jitter                             | 1      | UI p-p |

| J <sub>PL2MHz</sub>    | Sinusoidal Jitter                             | 0.5    | UI p-p |

| J <sub>PLf1</sub>      | Sinusoidal Jitter                             | 0.2    | UI p-p |

| J <sub>PL</sub> 50MHz  | Sinusoidal Jitter                             | 0.2    | UI p-p |

| V_full_swing           | Transition bit differential voltage swing     | 0.75   | V p-p  |

| V_EQ_level             | Non transition bit voltage (equalization)     | -3     | dB     |

USB-IF DevCon Demo - Tokyo, Japan May 20<sup>th</sup>, 2009 - NEC Electronics Booth

### Receiver Test Setup (with HW Channel Emulation) Oscilloscope Based Error Detection • SSC Bit or Symbol Error • Rj **Detection** • Si - OR - De-Emphasis **BERC Decode** DSA70000 AWG7122B **USB-IF** 'Compliance Channel' Same HW Configuration TP1 3 Meter Cable USB3 Rx Reference Reference Test Channel **Host/Device** Reference Reference Test Channel USB3\_Tx Tx Channel Long Return Path a problem for External Analyzers Innovation Forum 27 | 2010-5-4 Tektronix Innovation Forum 2010

## USB 3.0 Tx/Rx Test Equipment Considerations

### Simplified Setup

- 2 Instruments, add Protocol Analyzer for system level test

- 1 Fixture, 4 Cables, 4 Connectors

- AWG7122B (Opt. 06, 08)

### RX Tolerance Testing

Supports Silicon, Host/Device per the USB 3.0 Specification

### Flexible Signal Impairment Generation

- All required impairments are generated with the AWG using Direct Synthesis

- Precise ISI generation for channel emulation

## BERT & RT Scope

(2) Waveform

Generators

Signal

Generator

**JBERT**

De-Emphasis Generator

Scope

### Complex Setup

- 6 Instruments, add Protocol Analyzer for system level test

- 1 Fixture. 35 Cables/Connectors

- BERT HW + External impairment sources

### RX Tolerance Testing

Synchronous Clock Required, BERT method not suitable for system/device test

### Impairment Capabilities Limited by Hardware

- SSC and Sj require external equipment

- ISI generation limited by Hardware Channels

## Key Advantages of the AWG for USB Receiver Testing

AWG7000B Arbitrary Waveform Generators with SerialXpress®

- Flexibility to support all signal impairments required for jitter tolerance testing

- Model real-world complexities of SSC profiles to avoid system interoperability issues

- No tradeoffs between any signal impairments -No limitations in generating SSC and SJ at the same time

- Multiple SJ tones can be generated at one time

- Flexible ISI generation enables customers to test ISI models that exceed the test specification

- No need to wait for USB hardware compliance channels

- Minimize time needed for re-cabling

- Improved repeatability and portability of Receiver test configurations with setup files

## **Cable Testing**

## DSA8200 Sampling Oscilloscope with IConnect®

- Test Fixtures

- A Receptacle

- B Receptacle

- USB2/USB3 Connectors Available for Crosstalk measurements

- Using Sampling Oscilloscope & S-Parameter SW

- Measurements:

- Impedance

- Intra-Pair Skew

- Differential Insertion Loss

- Differential Return Loss

- Differential Near-End Crosstalk

- Differential Crosstalk between USB3.0 and USB2.0 Pairs

- Differential to CM Conversion

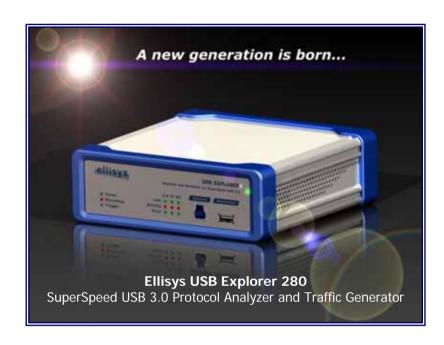

## **Tektronix Partner Solution**

## Ellisys EX280 Explorer- USB 3.0 Analyzer/Exerciser

- Analyzer Applications

- USB host & device monitoring

- Performance analysis

- Debug of drivers & software stacks

- Link state analysis

- Protocol errors checks

- Generator Applications

- USB host & device emulation

- Testing error recovery mechanisms

- Performance stress testing

- Compliance verification

- Link state analysis

## **USB 2.0 Compliance**

## Signal Quality

- Eye-Diagram testing

- Signal Rate

- End of Packet Width

- Cross-over voltage range (for LS and FS)

- JK jitter

- KJ jitter

- Consecutive jitter

- Monotonicity test (for HS)

- Rise and Fall times

## **Timing Measurements**

- Packet Parameters

- Suspend

- Resume

- Reset from High-Speed

- Reset from Suspend

## **Tektronix Wireless USB Validation Solution**

- Easy to setup: Automatically detect Time Frequency Codes (TFCs) and data rates from the RF waveform header

- Demodulate, Analyze and Record measurements of each packet independently

- Perform Measurements Outlined in the Wireless USB EVM Test Specification

- Industry's only MOI (Method of Implementation) for WiMedia test!

- WUSB EVM test is a subset of WiMedia PHY certification

## **Tektronix USB Solution**

**Complete solution:** from PHY layer to Protocol for USB 2.0, 3.0 and Wireless USB (Only approved Method of Implementation (MOI) for WiMedia PHY Leadership in USB)

**Cost Effective:** Automation with a single box solution

Connectivity: Measure closest to Tx output for true performance of

USB 3.0 device/host

**Flexibility:** Compliance, debug, characterization with software channel emulation

### **USB** leadership:

- Tektronix 1st to market for USB 2.0

- Tektronix is active in USB-IF Compliance Group and USB 3.0 PIL and contributes to USB 3.0 specification (only T&M Technical Contributor in the USB 3.0 specification)

### Resources

- Access to Specifications

- Rev 1.0, <a href="http://www.usb.org/developers/docs/">http://www.usb.org/developers/docs/</a>

- Tektronix USB Electrical PHY Tools

- www.tektronix.com/usb

- www.tektronix.com/software

- Ellisys Protocol Tools

- www.ellisys.com

# Enabling Innovation in the Digital Age

# Accelerating Performance

Enabled by High-speed Serial Technologies