# PCI Express 3.0 Testing Approaches for PHY and Protocol Layers

### Agenda

- Introduction to PCI Express 3.0

- Trends and Challenges

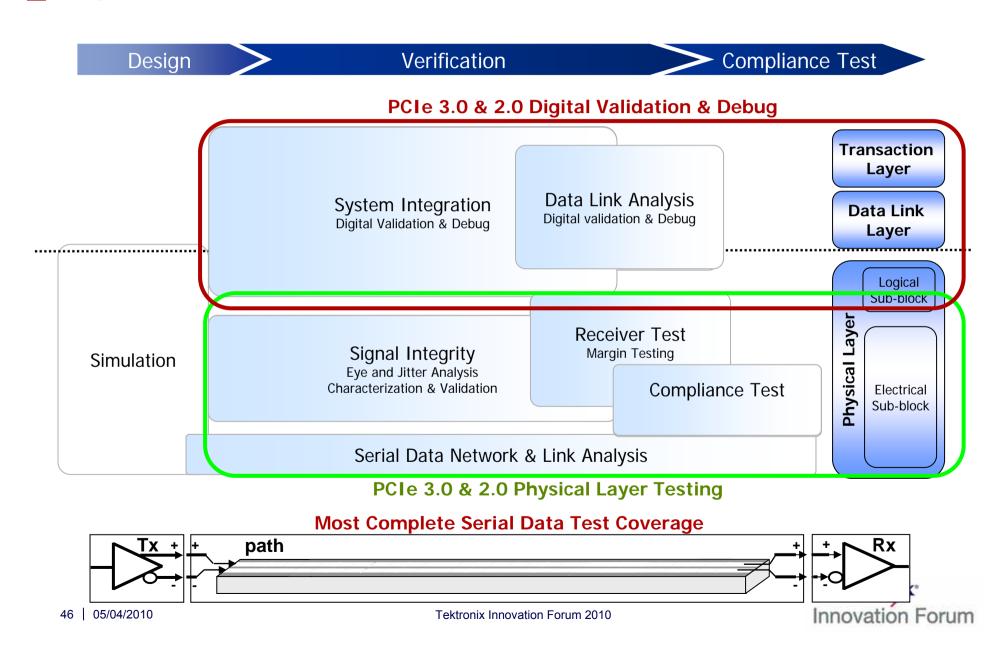

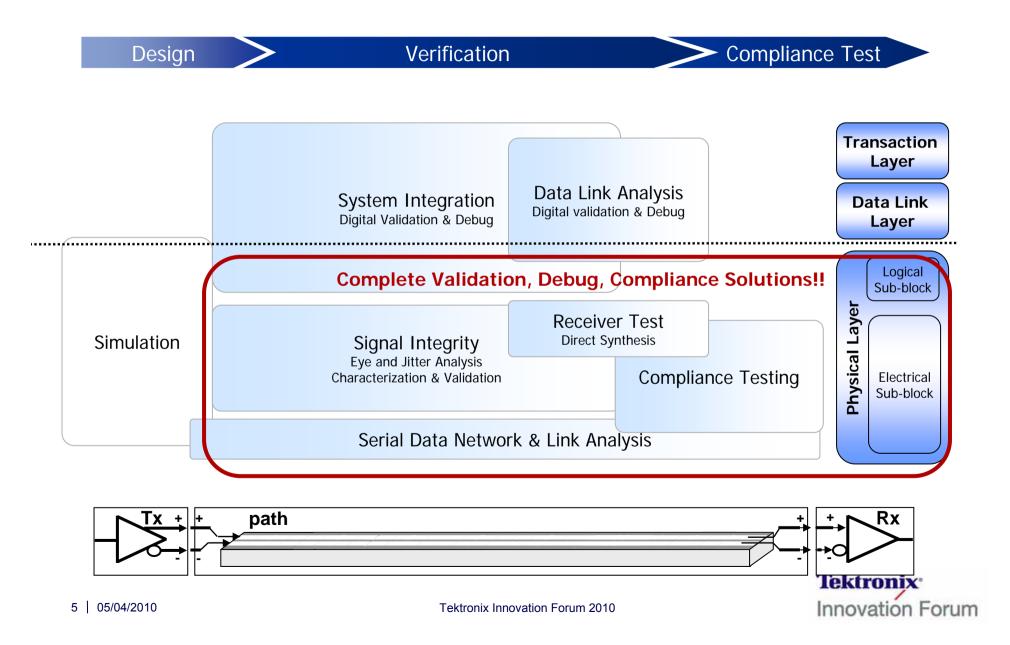

- Physical Layer Testing Overview

- Transmitter Design & Validation

- Transmitter Compliance

- Receiver & Summary of Tools for PCIe PHY Testing

- Protocol

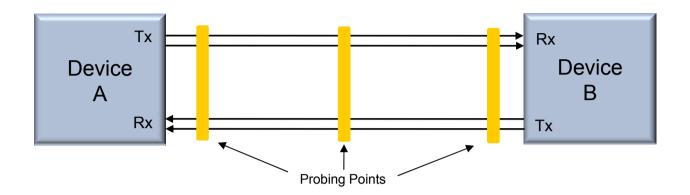

- Planning probe access

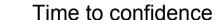

- Time to confidence

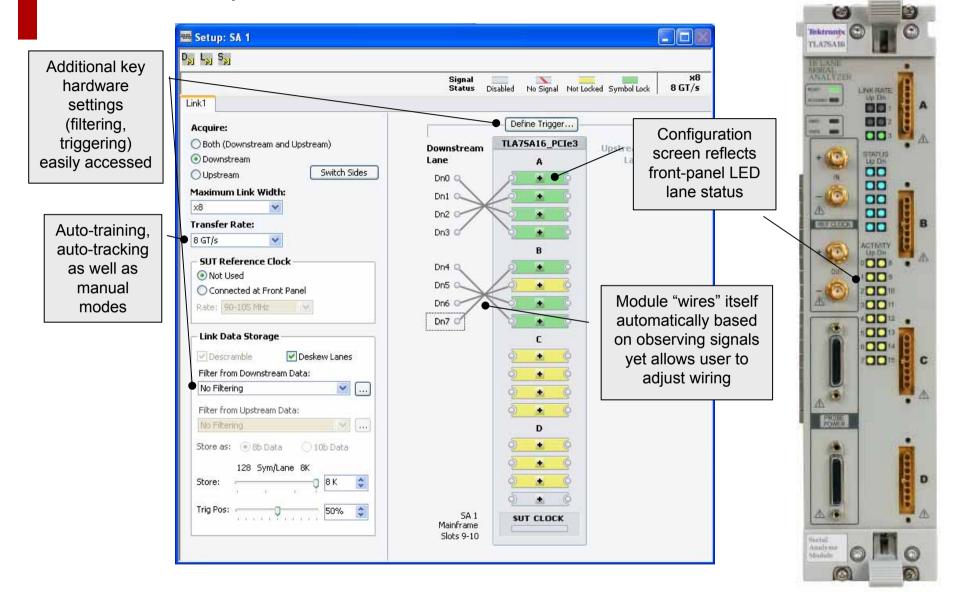

- Information density

- Applications

- Summary

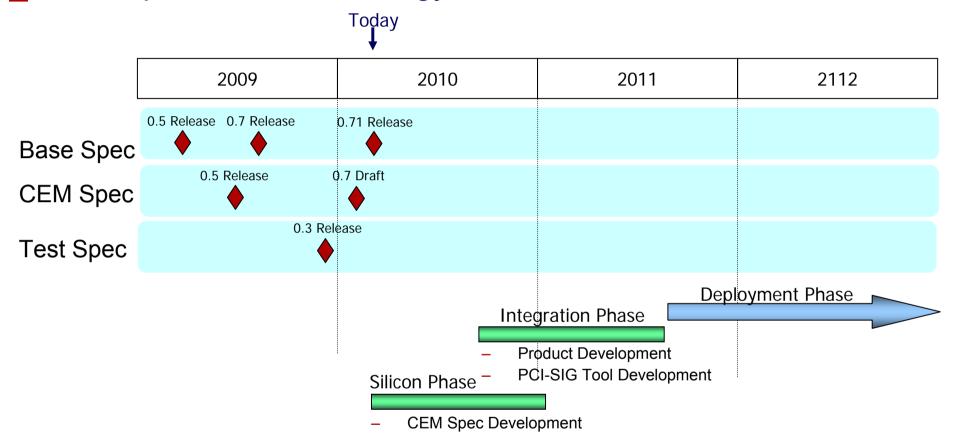

### PCI Express 3.0 Technology Timeline

Presentation Content based on

- .9 Base Specification Draft and

- .7 CEM Specification Draft

Tektronix Involved in PCIe EWG, CEM, and Serial Enabling Working Groups

### PCI Express 3.0

### Trends and Implications

#### Industry/Technology Trends

- Data transfer rates continue to increase:

2.5 → 5 → 8 GT/s

- 128b/130b encoding

- · Backwards interoperability

- Energy efficiency (Lower mW/Gb/s)

#### *Implications*

- Greater system complexity increases the engineering challenge

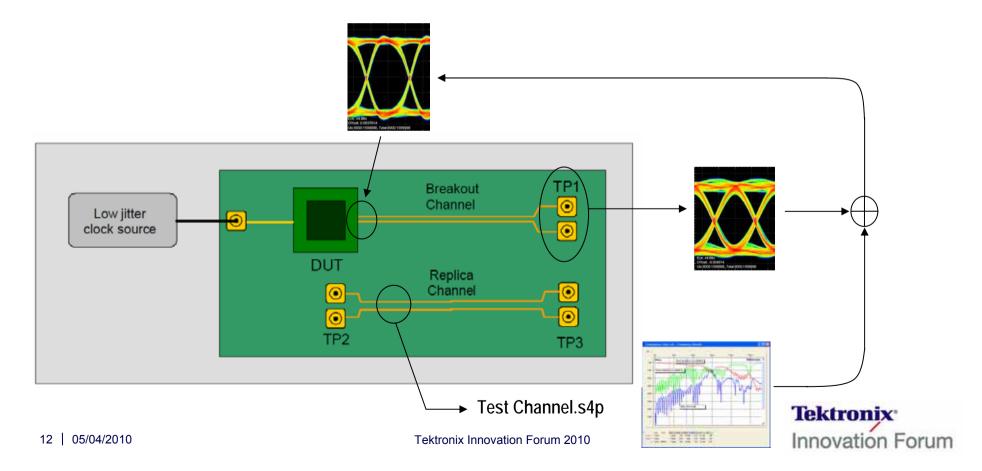

- Higher data rate signals have less margin – requires de-embedding

- Crosstalk, skew, noise and attenuation more significant

- Link training and power management continue to be the most difficult challenges

Tektronix

Innovation Forum

### High Speed Serial Test Challenges

### Agenda

- Introduction to PCI Express 3.0

- Trends and Challenges

- Physical Layer Testing Overview

- Transmitter Design & Validation

- Transmitter Compliance

- Receiver & Summary of Tools for PCIe PHY Testing

- Protocol

- Planning probe access

- Time to confidence

- Information density

- Applications

- Summary

### What's New for PCI Express Gen 3.0

- Double bandwidth (8GT/s with 128b/130b)

while using traditional circuit board (FR-4)

- Requires de-embedding measurements to Tx pins, specifies breakout and replica channels.

- Large channel losses require Tx and Rx equalization

- Tx equalization- Defined pre-shoot and deemphasis Presets

- Rx equalization—behavioral CTLE & DFE

- New jitter separation algorithms

# Transmitter Design & Validation

**PCI** Express

# PCIe 3.0 Base Spec Transmitter Voltage and Jitter Measurements

- Base Spec Measurements defined at the pins of the transmitter

- New Jitter Measurements are defined for PCIe 3.0

| Table 4-3: 8.0 GT/s Tx Voltage and Jitter Parameters |                                                |                          |                           |                                                                                          |

|------------------------------------------------------|------------------------------------------------|--------------------------|---------------------------|------------------------------------------------------------------------------------------|

| Symbol                                               | Parameter                                      | Value                    | Units                     | Notes                                                                                    |

| V <sub>TX-FS-NO-EQ</sub>                             | Full swing Tx voltage with no TxEq             | 1200 (max)<br>800 (min)  | mVPP                      | Note 1                                                                                   |

| V <sub>TX-RS-NO-EQ</sub>                             | Reduced swing Tx<br>voltage with no TxEq       | 1200 (max)               | mVPP                      | Note 1                                                                                   |

| V <sub>TX-EIEOS-FS</sub>                             | Min swing during<br>EIEOS for full swing       | 250 (min)                | mVPP                      | Note 2                                                                                   |

| V <sub>TX-EIEOS-RS</sub>                             | Min swing during<br>EIEOS for reduced<br>swing | 232 (min)                | mVPP                      | Note 2                                                                                   |

| T <sub>TX-UTJ</sub>                                  | Tx uncorrelated total jitter                   | 31.25 (max)              | ps PP @ 10 <sup>-12</sup> |                                                                                          |

| T <sub>TX-UDJDD</sub>                                | Tx uncorrelated deterministic jitter           | 12 (max)                 | ps PP                     |                                                                                          |

| T <sub>TX-UPW-TJ</sub>                               | Total uncorrelated PWJ                         | 24 (max)                 | ps PP @ 10 <sup>-12</sup> | Notes 3,4                                                                                |

| T <sub>TX-UPW-DJDD</sub>                             | Deterministic DjDD uncorrelated PWJ            | 10 (max)                 | ps PP                     | Note 3,4                                                                                 |

| T <sub>TX-DDJ</sub>                                  | Data dependent jitter                          | 15 (max)                 | ps PP                     | Note 4.                                                                                  |

| ps21 <sub>TX</sub>                                   | Pseudo package loss                            | -4.0 (min)               | dB                        | PP ratio of 64 ones/64 zeroes<br>pattern vs. 0101 pattern. No Tx<br>equalization. Note 5 |

| V <sub>TX-BOOST-FS</sub>                             | Tx boost ratio for full swing                  | 8.0 (min)                | dB                        | Assumes ±1.5 dB tolerance from diagonal elements in Figure 4-6                           |

| V <sub>TX-BOOST-RS</sub>                             | Tx boost ratio for reduced swing               | 2.5 (min)<br>4.5 (max)   | dB                        | Assumes ±1.0 dB tolerance from diagonal elements in Figure 4-6                           |

| EQ <sub>TX-COEFF-RES</sub>                           | Tx coefficient resolution                      | 1/24 (max)<br>1/63 (min) | N/A                       |                                                                                          |

#### New PCIe 3.0 Jitter Measurements

- Uncorrelated Total Jitter and Uncorrelated Deterministic Jitter

- Uncorrelated jitter is not mitigated by Tx or Rx equalization and represents timing margin that cannot be recovered with equalization.

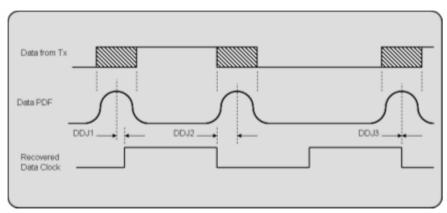

- Data Dependent Jitter is determined by averaging from a repeated compliance pattern

- Uncorrelated Jitter derived after removing Data Dependent Jitter

- Construct the bathtub curve in Q scale

- Estimate Total Jitter with Q Scale extrapolation

Figure 4-10: Relation Between Data Edge PDFs and Recovered Data Clock

Figure 4-11: Derivation of T<sub>TX-UTJ</sub> and T<sub>TX-UDJDD</sub>

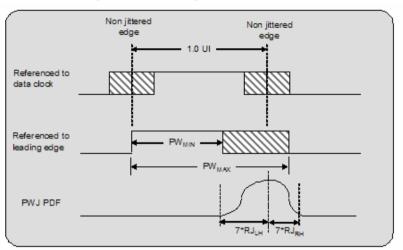

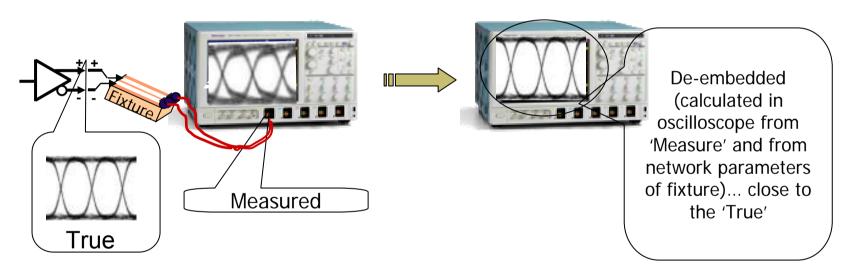

### New PCIe 3.0 Jitter Measurements (cont'd)

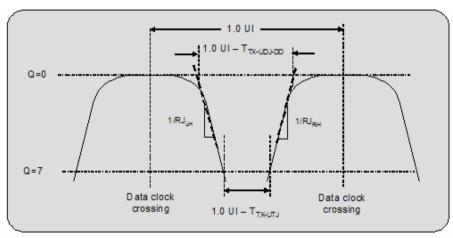

- Uncorrelated Total and Deterministic PWJ

- Long lossy channels cause single pulses to be attenuated

- ISI contributions need to be removed to determine PWJ

- Calculate the edge to edge Jitter

- Construct the bathtub curve in Q scale

- Estimate Total Jitter with Q

Scale extrapolation

Figure 4-12: PWJ Relative to Consecutive Edges 1 UI Apart

Figure 4-13: Definition of TTX-UPW-DIDD and TTX-UPW-TI

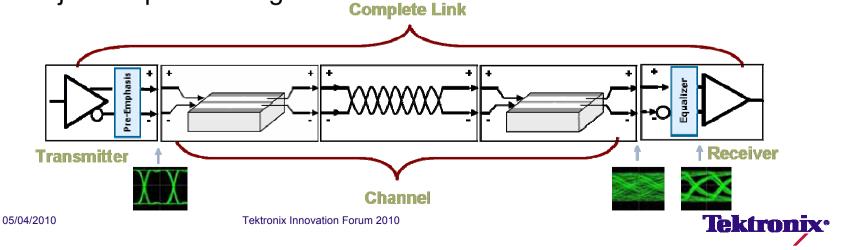

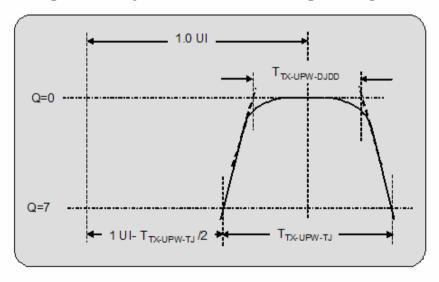

### **Transmitter Characterization**

- Tx measurements referenced to pins but can only access TP1

- Extract replica channel transfer function (S-Parameter)

- Acquire signals at TP1 then mathematically remove channel effects

### De-embedding

Removal of signal impairment caused by selected known part of the circuit. Measurement setup often known – i.e., a fixture.

- When impacts does the test fixture add?

- What does the signal look like at the Tx, without the fixture?

- Measure the Fixture (with TDR, VNA, etc) and and capture the network's parameters (e.g. as a S parameter touchstone file)

- In the oscilloscope Import the S parameter file, view the waveform as it was at the source.

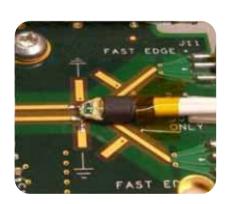

### **Probing and Signal Access**

- Typically used when a signal needs to be measured and no SMA or RF connector is available

- Debug

- Require a quick way to check that signals are present

- Solder tips can be used for a more permanent connection for troubleshooting

- Validation and Compliance Testing

- Chip to chip buses

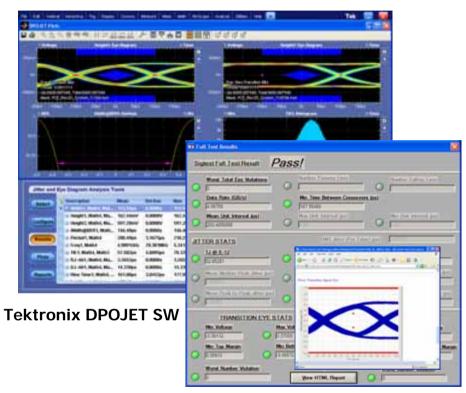

### Tektronix' Solutions for PCIe 3.0 Base Spec Testing

#### **Available Today**

- Channel Embedding / Deembedding support with (Serial Data Link Analysis) Software

- TX Voltage V<sub>TX-FS-NO-EQ</sub> and V<sub>TX-RS-NO-EQ</sub> Measurements available today in DPOJET

- 20Ghz Real-Time Oscilloscope and Probes for Fifth Harmonic Capture

**Tektronix DPOJET PCIe 3.0 SW**

# **Transmitter Compliance**

**PCI** Express

### **CEM Specification Add-In Card Transmitter Testing**

- TX measurements based on one preset value (assumption is the best preset will be used for compliance)

- Measurements taken after RX

Equalization using the Compliance

Base Board

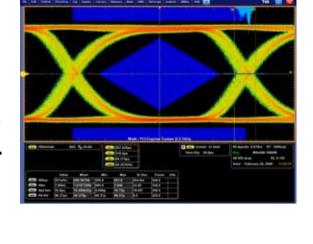

- Voltage Measurements on Both Transition and Non-Transition Bits at a BER of 10-6

- Eye Width Measurements taken with a sample of at least 10<sup>6</sup> UI and Eye opening is computed at 10<sup>-6</sup>

| Preset<br>Number | preshoot<br>(dB) | de-emph<br>(dB) | C <sub>-1</sub> | C <sub>+1</sub> |

|------------------|------------------|-----------------|-----------------|-----------------|

| P4               | 0.0              | 0.0             | 0.000           | 0.000           |

| P1               | 0.0              | -3.5 ±1 dB      | 0.000           | -0.167          |

| P0               | 0.0              | -6.0 ±1.5 dB    | 0.000           | -0.250          |

| P9               | 3.5 ±1 dB        | 0.0             | -0.166          | 0.000           |

| P8               | 3.5 ±1 dB        | -3.5 ±1 dB      | -0.125          | -0.125          |

| P7               | 3.5 ±1 dB        | -6.0 ±1.5 dB    | -0.100          | -0.200          |

| P5               | 1.9 ±1 dB        | 0.0             | -0.100          | 0.000           |

| P6               | 2.5 ±1 dB        | 0.0             | -0.125          | 0.000           |

| P3               | 0.0              | -2.5 ±1 dB      | 0.000           | -0.125          |

| P2               | 0.0              | -4.4 ±1.5 dB    | 0.000           | -0.200          |

| P10              | 0.0              | -9.5 ± 1.5 dB   | 0.000           | -0.333          |

| Va    | Vb    | Vc    |

|-------|-------|-------|

| 1.000 | 1.000 | 1.000 |

| 1.000 | 0.668 | 0.668 |

| 1.000 | 0.500 | 0.500 |

| 0.668 | 0.668 | 1.000 |

| 0.750 | 0.500 | 0.750 |

| 0.800 | 0.400 | 0.600 |

| 0.800 | 0.800 | 1.000 |

| 0.750 | 0.750 | 1.000 |

| 1.000 | 0.750 | 0.750 |

| 1.000 | 0.600 | 0.600 |

| 1.000 | 0.333 | 0.333 |

Table 4-13: Add-in Card Transmitter Path Compliance Eye Requirements at 8 GT/s

| Parameter          | Min  | Max  | Unit | Comments      |

|--------------------|------|------|------|---------------|

| V <sub>TXA</sub>   | 18   | 1200 | mV   | Notes 1, 2, 4 |

|                    |      |      |      |               |

| V <sub>TXA_d</sub> | 18   | 1200 | mV   | Notes 1, 2, 4 |

| T <sub>TXA</sub>   | 37.5 |      | ps   | Notes 1, 3, 4 |

|                    |      |      |      |               |

|                    |      |      |      |               |

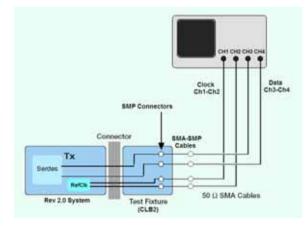

### **CEM Specification System Transmitter Testing**

- Same methodology as Add-In Card Testing, but uses the dual port method (clock and data)

- Measurements taken after RX Equalization using the Compliance Load Board

- Voltage Measurements on Both Transition and Non-Transition Bits at a BER of 10-6

- Eye Width Measurements taken with a sample of at least 10<sup>6</sup> UI

Table A TO S STYCE BODE IN ING IT S POO PARILLE CE A TRequirements at 8 GT/s

|              | TO DE TO TO TO THE TO THE TOTAL OF THE TOTAL |      |      |      |               |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------|--|

| O-6Parameter |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min  | Max  | Unit | Comments      |  |

| ,            | V <sub>TXS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21   | 1200 | mV   | Notes 1, 2, 4 |  |

| ١            | V <sub>TXS_d</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21   | 1200 |      | Notes 1, 2, 4 |  |

| -            | T <sub>TXS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37.5 |      | ps   | Notes 1, 3, 4 |  |

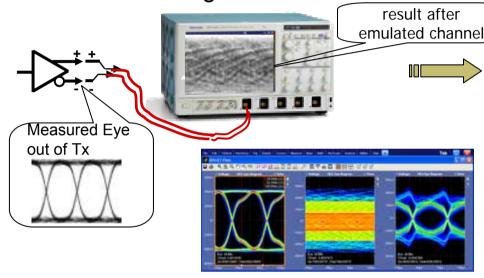

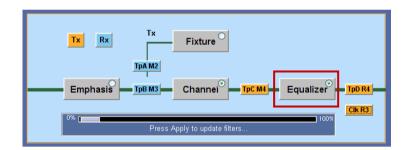

### Receiver Equalization

- PCIe Gen 3.0 uses Transmitter De-emphasis plus RX CTLE and Dfe

- What would the signal look like inside the receiver after equalization?

- Link analysis with Continuous Time Linear Equalizer (CTLE) or Decision Feedback (DFE) **Edualizers**

- Three DFE modes

- Coefficients values adapted based on measured data-Auto adapt taps

- Coefficient values adapted based on existing taps-Adapt from current taps

- Do not adapt

- Slicer controls and training sequence support

| FFEÆFE ✓          |                    |                    |  |  |

|-------------------|--------------------|--------------------|--|--|

| FFE Taps 0        | DFE Taps 3         | PLL Type 0 1 0 2   |  |  |

| Sample/bit 1      | Amplitude (V) 0.15 | PLL BW (MHz) 3.6   |  |  |

| Ref Tap 1         | Threshold (V) 0.0  | PLL Damp 0.7       |  |  |

| Use trainSeq 🗌    | Autoset Voltages   | Clk Delay (ps) 0.0 |  |  |

| ● Auto adapt taps |                    |                    |  |  |

result after

Equalization

### Tektronix' Solutions for PCIe 3.0 CEM Testing

#### **Available Today**

- Receiver Equalization support for CTLE and DFE with SDLA (Serial Data Link Analysis)

Software

- Measurements available today in DPOJET

**PCI-SIG SigTest SW**

### Summary of Tektronix Tools for PCIe Testing

#### TDR/TDT/IConnect for Serial Data Network Analysis

- 50 GHz TDR/TDT system and S-Parameter measurements, highly accurate impedance and loss measurements

- Up to 1M record length

#### **Real-Time Oscilloscope and Analysis Tools**

- Transmitter Validation, Debug, Compliance, and Receiver Calibration

- "Complete Link" channel embedding/de-embedding, equalization (CTLE/DFE) with SDLA

- CEM and Base Spec Measurements with DPOJET and TekExpress

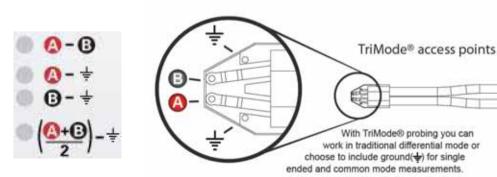

- TriMode Differential probes 20GHz to the probe tip

#### **Receiver Stress Generation**

- Flexibility to support all signal impairments required for jitter tolerance testing

- Model real-world complexities of SSC profiles to avoid system interoperability issues

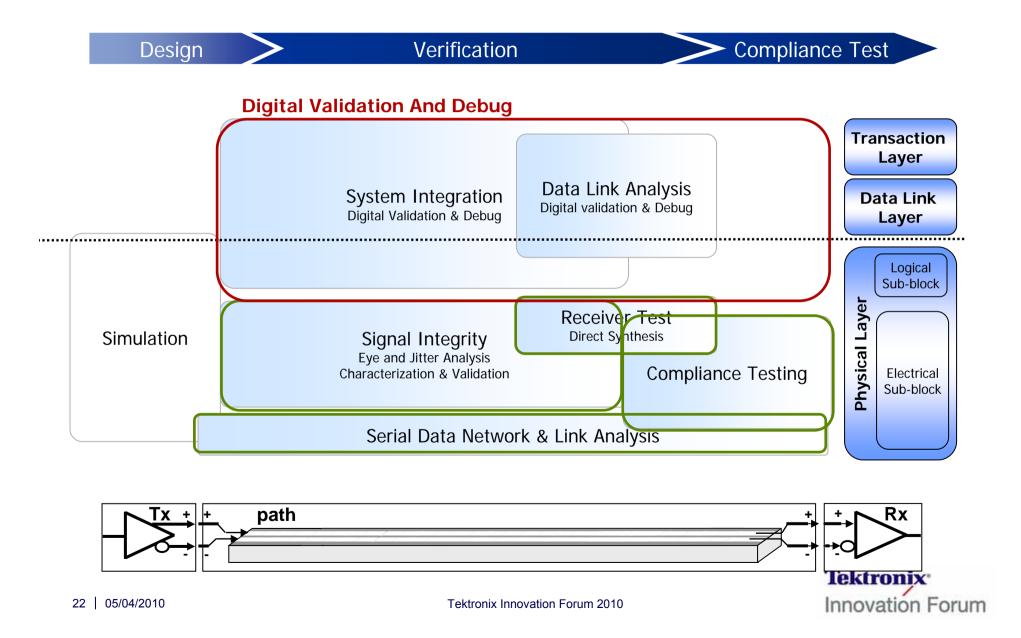

### Digital Validation And Debug

Logic layer validation

### Agenda

- Introduction to PCI Express 3.0

- Trends and Challenges

- Physical Layer Testing Overview

- Transmitter Design & Validation

- Transmitter Compliance

- Receiver & Summary of Tools for PCIe PHY Testing

- Protocol

- Planning probe access

- Time to confidence

- Information density

- Applications

- Summary

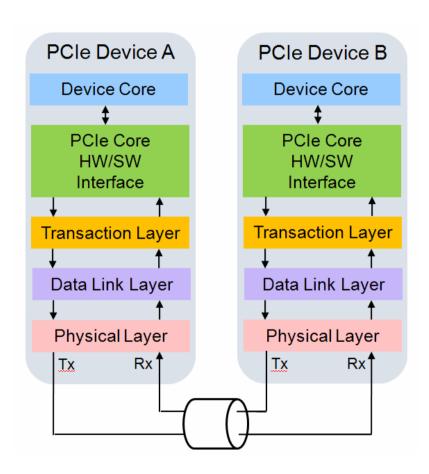

### Testing Challenges with PCI Express 3.0

#### **Transaction Layer**

- Creates Request/Completion Transactions

- Messaging

- TLP Flow Control

#### Data Link Layer

- Flow control information

- Data Integrity, Error Checking/Correction

- Calculates/Check TLP Sequence Number

- Calculate/Check CR

#### Physical Layer – Logical Sub Block

- Link Initialization and Training

- Distribution of packet information over multiple lanes

- Power management and link power state transitions

#### Physical Layer – Electrical Sub Block

- Transmitter Signal Quality and Ref Clock Testing

- Receiver Testing

- Interconnect Testing

- PLL Loop BW

### Challenges Selecting Tools for PCI Express 3.0

- Accessing PCle3 signals

- Assessing probing impact

- Probing flexibility

#### Time to confidence

- Automating setup

- Recovery options

- Powerful triggering

- Wide acquisition window

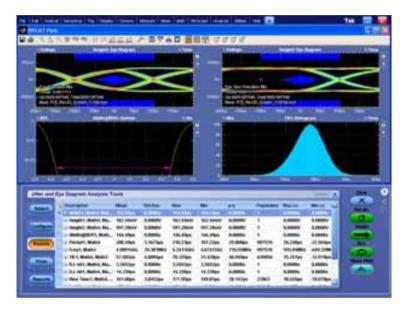

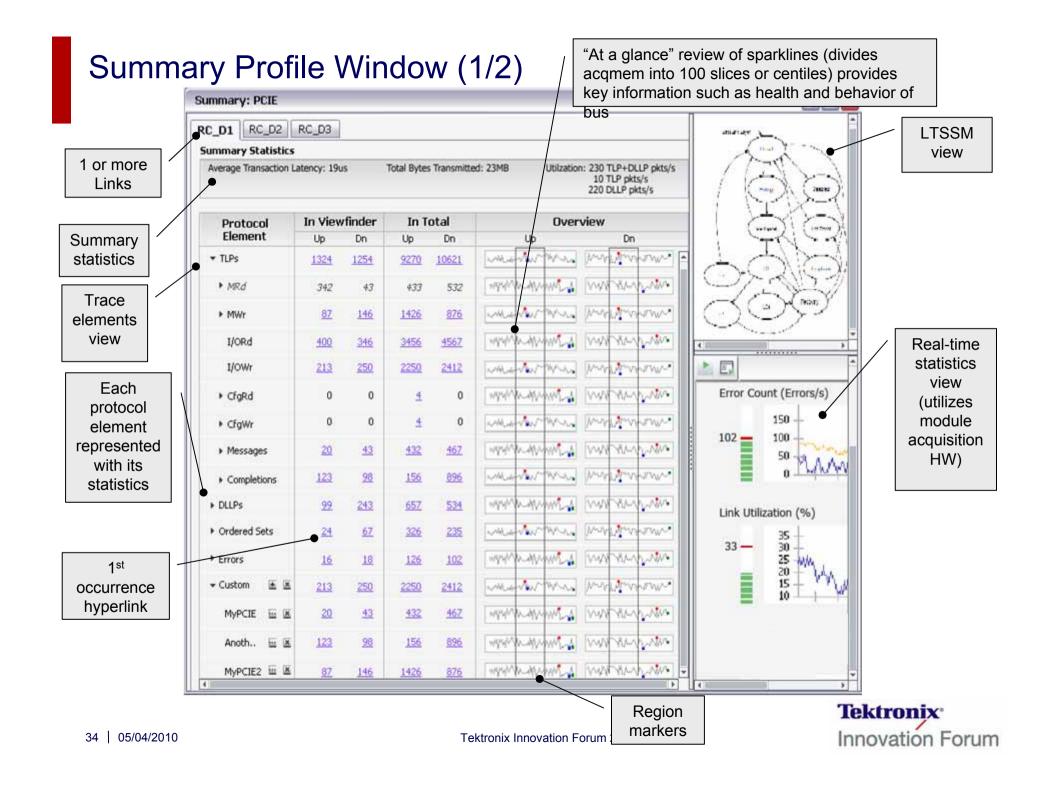

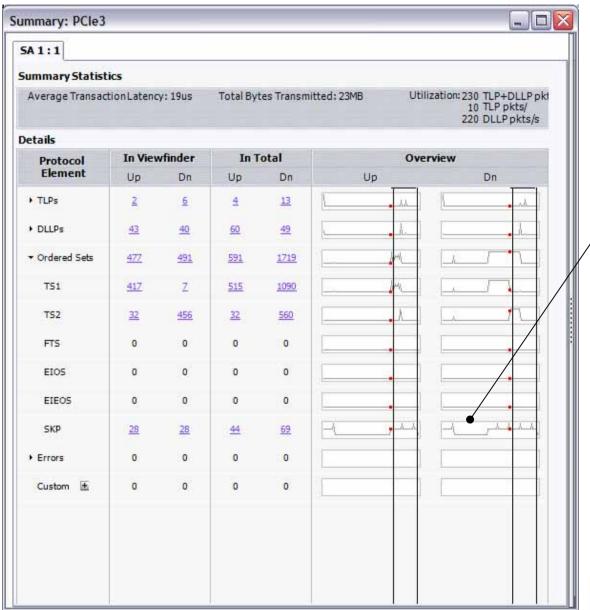

#### Information density

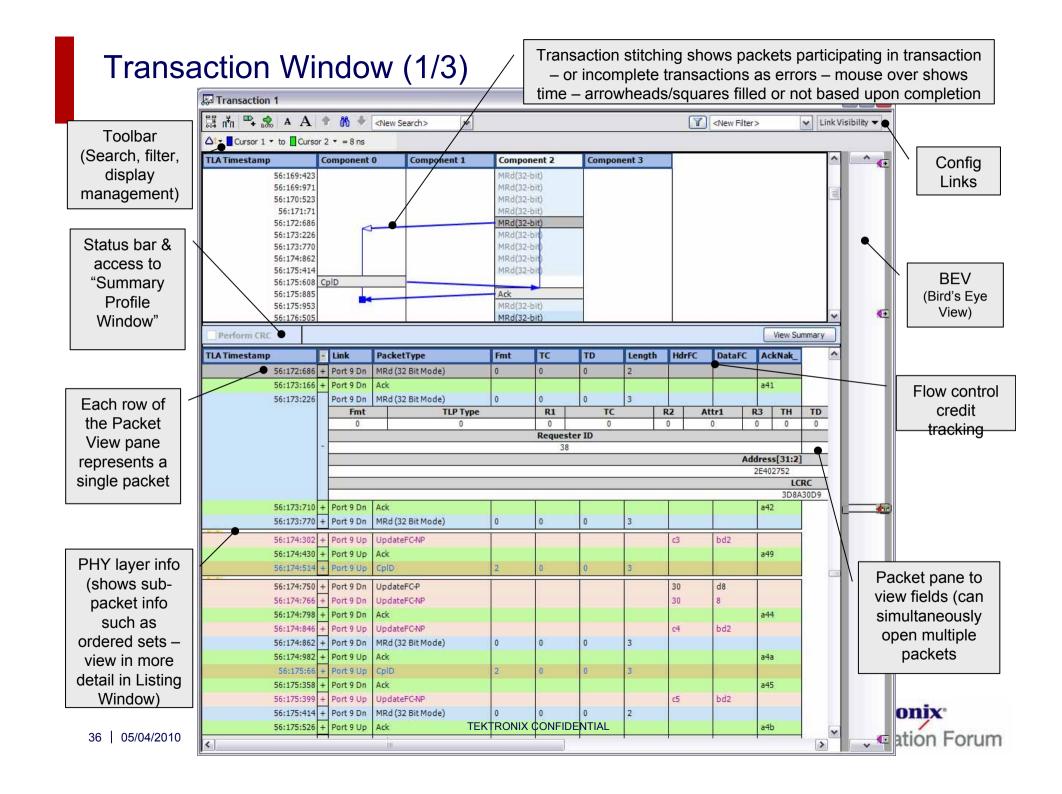

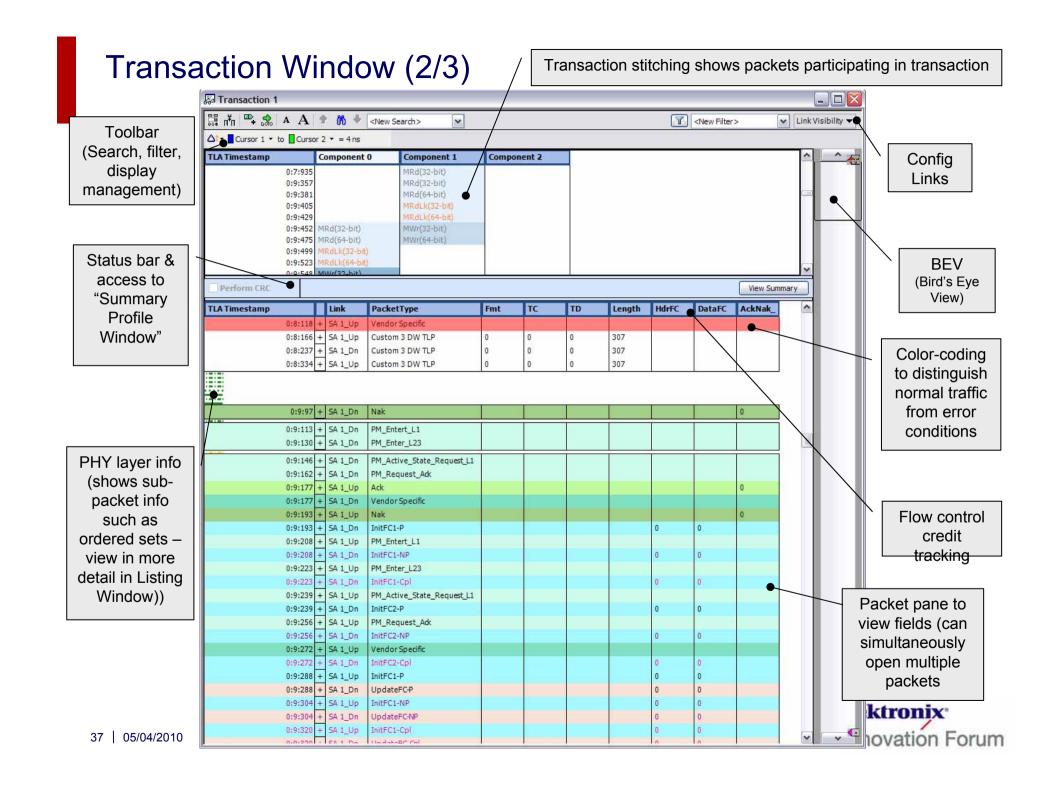

- Four (4) different data visualizations that provide views dedicated to different types of investigations:

- Summary statistics window

- Transaction window

- Listing window

- Waveform window

#### **Applications**

- Transaction Window Intro

- Transaction Window Normal Traffic

- Transaction Window Transaction Error

- Transaction Window Physical Layer

- **Summary Profile Window**

### Challenges Selecting Tools for PCI Express 3.0

- Planning probe access

- How access PCle3 signals?

- Is there a probe design guide available showing a variety of probing access?

- Does it include mechanical KOV (Keep Out Volume) info?

- Are PCB CAD symbols available for their midbus footprints?

- Is probing available for legacy PCle2 midbus footprints?

- Is there a probe available that I can solder-down as a last resort?

- How assess the probing impact?

- How is the PCle3 signal recovered without breaking the link?

- What is the maximum PCle3 channel length supported?

- Are electrical load models of all probes available for computer simulation?

- How flexible is the probing?

- How long are the probe cables?

- Can I reconfigure my PCle3 probe channels if there are layout errors?

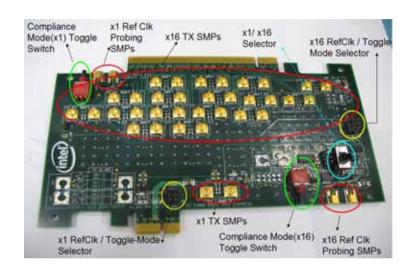

### Primary Debug Challenges When Implementing PCIe 3.0

#### **Probing Access**

- · Midbus vs interposer vs solder-down

- Need to compensate for Tx de-emphasis

- Need to compensate for channel loss

- Need to compensate for reflections

#### Link training

- Multi-lane systems x1, x4, x8, x16

- Dynamic speed negotiations 2.5 GTs → 5 GTs → 8 GTs 2.5 GTs → 8 GTs

- Dynamic link width changes  $x16 \rightarrow x8 \rightarrow x4 \rightarrow x1$

#### **Active State Power** Management (ASPM)

- Power Management: Electrical Idle Entry and Exit for power savings (L0  $\rightarrow$  L0s  $\rightarrow$  L0)

- · Dynamic link width and link speed changes depending on data bandwidth requirements

#### **Total System Visibility**

- · Critical cross bus dependencies increase with speed

- Flow Control

- Time-correlated visibility across multiple buses

- · Signal access across the entire system

Link training and power management continue to be the most difficult challenges!

### Challenges Selecting Tools for PCI Express 3.0

#### Planning probe access

- Accessing PCle3 signals

- Assessing probing impact

- Probing flexibility

- Automating setup

- Recovery options

- Powerful triggering

- Wide acquisition window

#### Information density

- Four (4) different data visualizations that provide views dedicated to different types of investigations:

- Summary statistics window

- Transaction window

- Listing window

- Waveform window

#### **Applications**

- Transaction Window Intro

- Transaction Window Normal Traffic

- Transaction Window Transaction Error

- Transaction Window Physical Layer

- **Summary Profile Window**

### Challenges Selecting Tools for PCI Express 3.0

- Time to confidence

- Does the analyzer automatically configure?

- Are there real-time statistics that show bus utilization, link width, etc. so that I can get an

overall indication of the link health?

- Does the GUI show the health of each lane?

- Are there front-panel LEDs that show me the status of the link?

- What options do I have if I can't get the analyzer to automatically configure?

- Is there an option to use my oscilloscope so that I can see whether my signal meets the input requirements or whether the probe is inoperable?

### PCIe3 Setup Window

### Challenges Selecting Tools for PCI Express 3.0

#### Planning probe access

- Accessing PCle3 signals

- Assessing probing impact

- Probing flexibility

#### Time to confidence

- Automating setup

- Recovery options

- Powerful triggering

- Wide acquisition window

#### Information density

- Four (4) different data visualizations that provide views dedicated to different types of investigations:

- Summary statistics window

- Transaction window

- Listing window

- Waveform window

#### **Applications**

- Transaction Window Intro

- Transaction Window Normal Traffic

- Transaction Window Transaction Error

- Transaction Window Physical Layer

- **Summary Profile Window**

### Challenges Selecting Tools for PCI Express 3.0

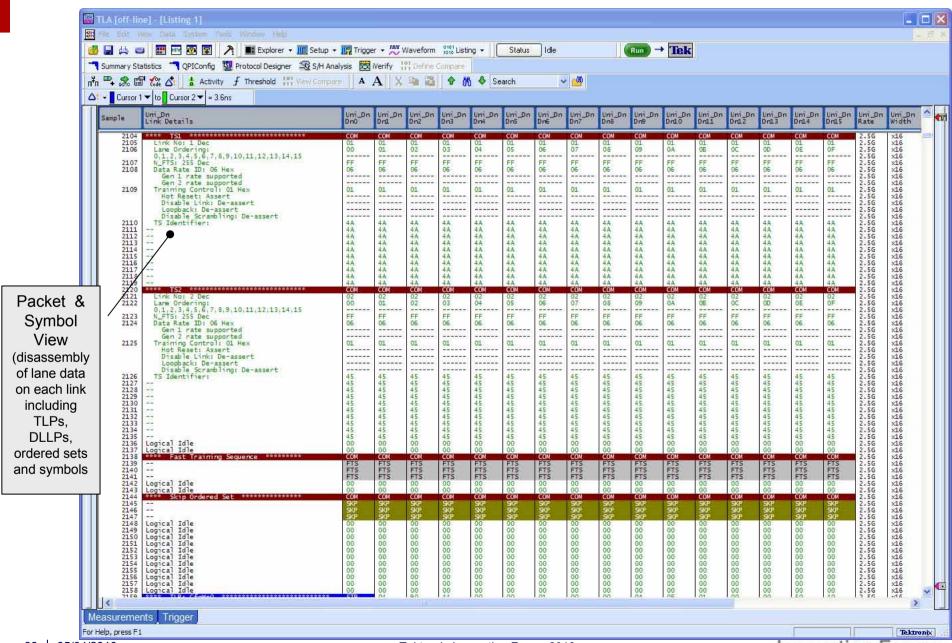

- Information density

- How powerful is the triggering?

- Can I trigger on ordered sets or packet types?

- Can I trigger on errors, e.g., loss of framing, illegal sync characters?

- How wide is the acquisition time window?

- · Can I control what gets stored?

- How fast can I access and move around within the acquisition record?

- What information do each of the data windows provide?

- **Summary Profile** (Statistics) *Acquisition summary statistics* based view of protocol elements (distribution of protocol elements across acquisition)

- Transaction Link based behavior of protocol elements (transactions, packets, fields, ordered sets)

- Listing Lane based behavior of protocol elements (symbols, tokens, ordered sets, DLLPs, TLPs)

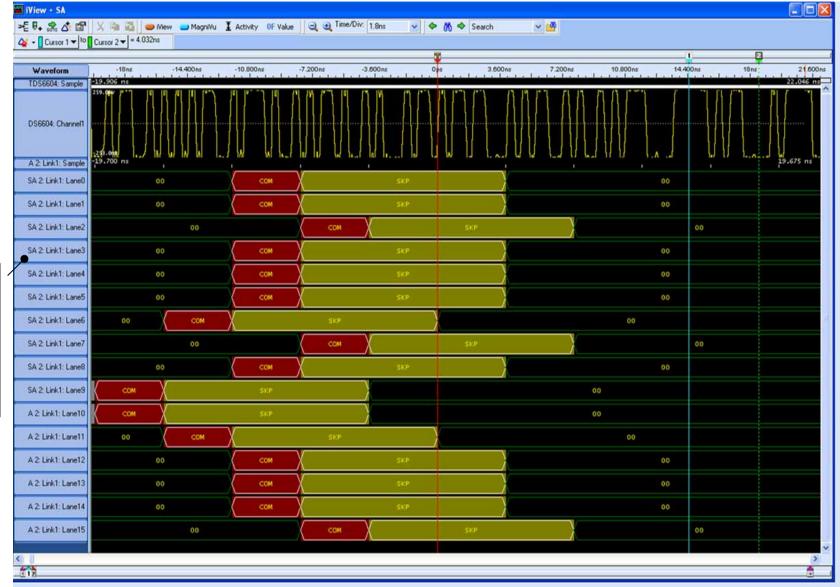

- Waveform Time based view of the data on each lane

- Can I correlate data from my PCle3 bus with other buses (e.g., DDR3) and see it all on a single display?

### **PCIe3 Trigger Window**

Innovation Forum

### Summary Profile Window (2/2)

Visually see training occur by recognizing patterns. For example, can see electrical idle (gap in SKP) followed by training (TS1 & TS2).

Tektronix\* Innovation Forum

Tektronix Innovation Forum 2010

### **Listing Window**

#### **Waveform Window**

Waveform symbolic

### Challenges Selecting Tools for PCI Express 3.0

#### Planning probe access

- Accessing PCle3 signals

- Assessing probing impact

- Probing flexibility

#### Time to confidence

- Automating setup

- Recovery options

- Powerful triggering

- Wide acquisition window

#### Information density

- Four (4) different data visualizations that provide views dedicated to different types of investigations:

- Summary statistics window

- Transaction window

- Listing window

- Waveform window

#### Applications

- Transaction Window Intro

- Transaction Window Normal Traffic

- Transaction Window Transaction Error

- Transaction Window Physical Layer

- Summary Profile Window

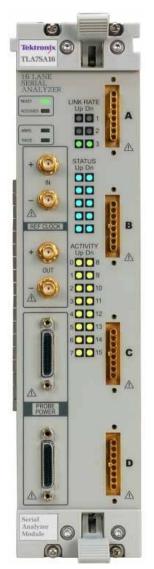

### PCI Express 3.0 Acquisition Solutions

- 8.0 GTs, 5GTs, and 2.5GTs acquisition rates for PCle3/2/1

- Sync to L0s within 4 FTS PCle3 packets or 12 FTS PCle2 packets

- Automatic configuration of link training speed changes and link width

- Track 2.5 GTs to 5.0 GTs to 8.0 GTs data rate changes without dropping parts of transactions or critical packets

- Dynamically track changes in link width

- Front-panel LEDs that show link rate and link status for both Upstream/Downstream links

- Powerful trigger state machine spans all layers of the protocol

- 8 states

- 8 packet recognizers

- 4 symbol sequence recognizers

- 4 counter/timers

- 4 event flags

- Conditional storage

- 8 GB memory/module (16 GB memory, x16 link) with 160 Msymbols/lane record length

- Two acquisition modules available:

- 16 differential inputs, x8 (2 required for x16)

- 8 differential inputs, x4

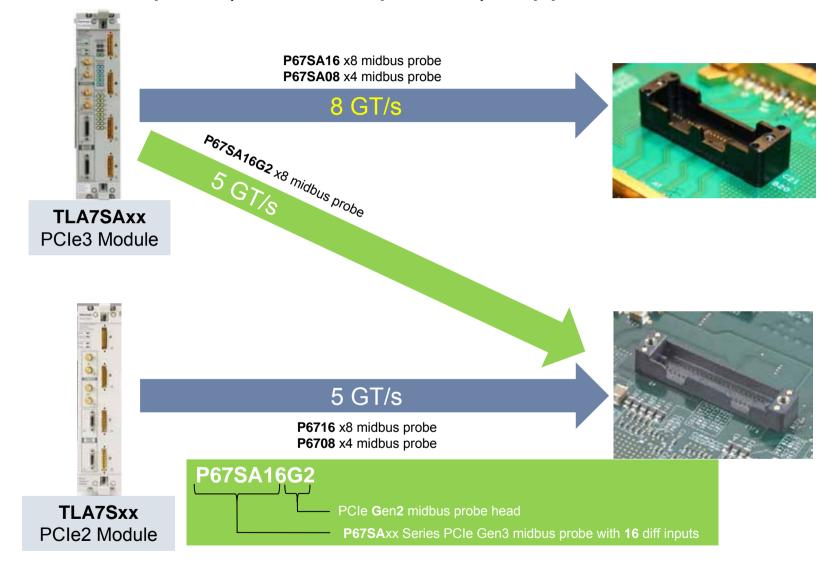

### Tektronix PCIe3 Probes – With Active Equalization

#### Slot Interposer Probes

#### Midbus Probes

- Available in x16, x8, x4, x1 link widths

- Probe cover

- Bracket for SUT end point card provides mechanical stabilization and reliable connection

- 6' probe cable

- Ships in antistatic, foam-lined, plastic case

- Available in x8 or x4 link widths (2 for x16)

- Rugged probe head with contacts contained in retention module

- Retention module securely attaches to PCB (0.031" to 0.250") using back mounting plate with screws

- Midbus probe also available for legacy PCle2 x16 midbus footprint

- 6' probe cable

- Ships in antistatic, foam-lined, plastic case

#### Solder-down Probes

- High-performance solder-down probing of one (1) PCle3 differential pair

- Supports 8 GT/s

- Compatible with P7500 Series TriMode probing leadsets that can be shared with oscilloscope

- 6' probe cable

- Ships in antistatic, foam-lined, plastic case

### Midbus footprint (PCB land pattern) support

#### **TLA Mainframe Solutions**

**TLA7012** 2-module mainframe

Shown with 2 TLA7SA16 modules

for x16 PCle3 link

- Mainframe with integrated 15" display and PC controller

- Connects to PC via

GbE for running TLA

Application Software

**TLA7016** 6-module mainframe Shown with 2 TLA7SA16 modules for x16 PCle3 link

**TLA7016** 6-module mainframe

Shown with 2 TLA7SA16 modules

for x16 PCle3 link & 4 TLA7BB4 modules for 2

channels DDR3-1600

- Mainframe with GbE controller

- Connects to PC via GbE for running TLA Application Software

- Up to 8 frames interconnected via TekLink

### **PCI Express Test Summary**

- Tektronix is heavily involved in PCI Express Standards Development

- Electrical Working Group (EWG) for Base Specification Development

- Card Electromechanical Group (CEM) for CEM Specification Development

- Serial Enabling Group (SEG) for Compliance Program

- PCI Express 3.0 specification is at 0.7 (.9 draft)

- Expect Rev 0.9 spec. in Q2 2010

- Physical layer testing

- De-embedding important for accurate measurements

- Minimum 12 GHz bandwidth scope for validation

- DPOJET for measurement automation and test reporting

- SDLA for measurement-based link analysis

- Protocol validation and debug

- TLA7000 series mainframes and TLA7SAxx serial acquisition modules

- Flexible probing and triggering

- Data visualization

- Cross-bus analysis

#### Proven Expertise in High Speed Serial Data Design & Test

### High-Speed Serial Data Test Solutions