# テクトロニクスの DDR ソリューション

DDR3-SDRAM 搭載 PC の普及に伴い、デジタル家電製品でも高速化と低電圧動作の両立が可能な DDR3-SDRAM の採用が進んでます。モバイル機器では、部品点数や省電力特化した LPDDR-SDRAM や、高速化に対応した LPDDR2-SDRAM の採用も進んでます。

また、高性能の画像処理を実現するメモリとして、GDDR5-SDRAMが注目されてます。

DDR メモリ測定上の基本的な問題の1つは、双方向性バスに起因するリード・バーストとライト・バーストの分離の難しさにあります。さらには信号の高速化にともない、基板設計、評価に要求されるレベルも高くなっており、ジッタ、タイミング測定などの多くの考慮すべきポイントがあります。

当社ではこれらに対し、オシロスコープによるアナログからロジック・アナライザによるデジタルまで、スピーディな検証とデバッグの豊富な DDR メモリ測定ソリューションを提供しています。

### What's New

| 理想的な統計処理が全DDRメモリ測定で実現                       | P3 |

|---------------------------------------------|----|

| <ul><li>GDDR5-SDRAMの測定項目フル・サポート</li></ul>   |    |

| インタポーザが強化                                   | P5 |

| - ソケット・タイプのGDDR5-SDRAM とLPDDR/2-SDRAM をサポート |    |

| ビジュアル・トリガで使い勝手が向上                           | РЗ |

| - 直感的なトリガ設定可能                               |    |

| オシロスコープによるプロトコル解析が実現                        | P4 |

| - コマンド・バスのサーチによるメモリ特性やリフレッシュ・サイクルの解析        |    |

| - プロトコル・デコード・イベント・テーブルによるコマンド・プロトコルの解析      |    |

| ロジック・アナライザによるデジタル解析のローコスト化が実現               | P6 |

## DDR メモリで要求される測定

DDR メモリ搭載基板の設計検証には、次の3つのステップがあります。

- 1. 実装する前の試作基板/伝送路やコネクタの検証

- 2. シグナル・インテグリティやジッタ/タイミング評価などのアナログ検証

- 3. システム・レベルでの動作/デジタル検証

システム・レベルに問題がある場合は、再度アナログ検証に戻る必要があるケースが多々あります。DDR メモリ搭載基板の設計検証では、プロービングも重要な考慮すべきポイントとなります。当社では、単なるスペックの測定だけではなく、トラブルの発見と原因特定のスピード・アップに役立つソリューションを提供しています。

|        | 伝送路評価                                             | アナログ検証とデバッグ                                                                        | デジタル検証とデバッグ                                                                                                                        |  |  |  |

|--------|---------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | トレース・インピーダンス<br>電気長<br>クロストーク                     | アイ・ダイアグラム<br>(オーバシュート、アンダシュートを含む)<br>タイミング測定<br>(セットアップ/ホールド時間、スキュー)<br>クロック・ジッタ測定 | モード・レジスタおよび拡張モード・レジスタへの<br>書込み内容確認<br>アドレス、コマンド、データのトレース/タイミン<br>グ解析<br>リフレッシュ・サイクル違反<br>システム・レベル・デバッグ<br>(他のバス、信号との時間相関をとっての同時解析) |  |  |  |

| プロービング | 18GHz差動TDR<br>ブローブ<br>P80318 型                    | TriMode差動プローブ<br>- 20GHz~4GHz                                                      | BGA<br>インターポーザ<br>インターポーザ                                                                                                          |  |  |  |

|        | 20GHzTDR ブローブ<br>P8018型                           | ソケット・タイプ ダイレクト・タイプ<br>インタポーザ インタポーザ<br>ソケット・ケーブルとソルダー・チップ                          | - P69xxシリーズ<br>DMAX高実装密度<br>プローブ ローコスト・プロトコル用<br>DIMM/SO-DIMM<br>インタポーザ                                                            |  |  |  |

| 信号の取込み | 対応サンプリング・オシロスコープ<br>DSA8300型                      | 対応オシロスコープ - MSO/DSA/DP070000シリーズ - DP07000Cシリーズ - MSO/DP05000シリーズ                  | 対応ロジック・アナライザ - TLA7000シリーズ - TLA7Bxx型モジュール - TLA6000シリーズ                                                                           |  |  |  |

| 解析/測定  | IConnect®シグナル・インテグリティ<br>インテグリティ<br>TDR/VNAソフトウェア | DDR自動測定/<br>解析ソフトウェア・パッケージ*                                                        | DDR2/3サポート・パッケージ DDR2/3プロトコル・チェック・ ソフトウェア                                                                                          |  |  |  |

- \*DDR自動測定/解析ソフトウェア・パッケージ構成

- 1. DDR解析ソフトウェア (Opt. DDRA) 2. 拡張波形サーチ (Opt. ASM) 3. DPOJET Advanced (Opt. DJA)

## アナログ検証とデバッグ

MSO/DSA/DPO70000 シリーズ、DPO7000C シリーズ、MSO/DPO5000 シリーズは、DDR 自動測定/解析ソフトウェア・パッケージを組み合わせることにより、DDR メモリのアナログ検証とデバッグを効率的に行なえます。また、基本機能の Pinpoint トリガと FastAcg による連続高速取込みは、不具合解析に有効です。

MSO/DSA/DP070000 シリーズ

DP07000C シリーズ

MS0/DP05000 シリーズ

### ■ DDR 自動測定/解析ソフトウェア・パッケージ

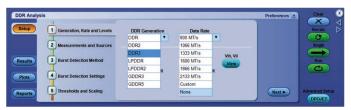

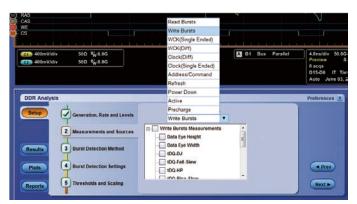

DDR 自動測定/解析ソフトウェア・パッケージにより、JEDEC に準拠した DDR/DDR2/DDR3/LPDDR/LPDDR2/GDDR3/GDDR5-SDRAM の適合性試験を簡単に実施できます。リード・バーストとライト・バーストの自動識別、主要パラメータ設定、測定と Pass/Fail 判定、レポートの自動生成を迅速にできるので、評価時間を大幅に短縮できます。

ウィザードに従って順番に設定するだけで、自動測定が可能です。 スピード・グレードは、DDR3-SDRAM が 2133MT/s、LPDDR2-SDRAM が 800MT/s、GDDR3-SDRAM が 5500MT/s と、高速化に対応してます。

ストローブとデータの位相差によるバースト識別が困難なこともあります。 MSO70Kシリーズを使用した場合、コマンドによるバースト識別が可能です。 コマンドによるバースト識別をする場合、レーテンシやバースト長を設定します。

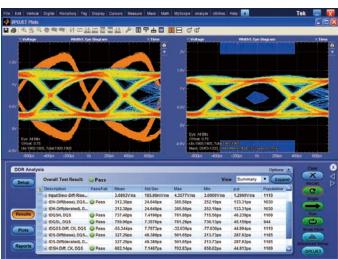

DDR3-1333のライト・バーストの測定結果の例です。 瞬時に判断できるよう、全体と各測定項目の Pass/Fail 判定を表示します。 左のアイ・ダイアグラムはストローブとデータを表示してます。 右のアイ・ダイアグラムはデータのマスク・テストをした例です。 10項目に対して約1000エッジの測定に要した時間は30秒程度です。

高機能な画像処理を求められるメモリ・システムには、GDDR5-SDRAM が最適です。MSO70000C シリーズを活用することで、バス・タイミングを含む多くの項目の、自動測定が可能になります。

バス・タイミングは、コマンド処理を行う多くのメモリ・デバイスの定義されている項目です。

GDDR5-SDRAM 以外でも、この測定を可能とする機能が、標準搭載されました。 MS07000C シリーズのロジック・チャンネルでバス定義を行うことで、容易 にバス間のタイミング測定が可能になります。

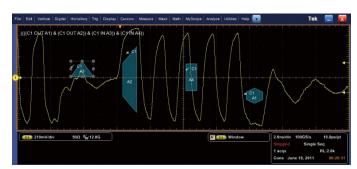

### ■ ビジュアル・トリガ

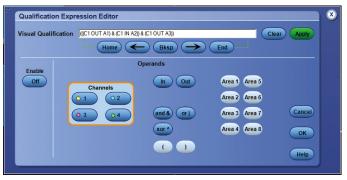

直感的にスクリーン上で実波形に合わせてトリガを設定するオプション機能です。 Pinpoint トリガ機能との組み合わせことも可能で、困難な信号も簡単、確実にトリガ/サーチが可能となりので、デバック効率が向上します。

直感的にスクリーン上で実波形に合わせてエリアを指定します。 エリアは三角形、長方形、六角形、不等辺四角形から選択可能です。 各チャンネルにそれぞれのエリアのイン/アウトの設定を行います。 エリアは自由に移動、サイズ変更可能で最大8個まで定義可能です。 各チャンネル及びエリアを非表示設定しても、トリガは有効となります。

エリア間ロジック設定(AND/OR/EXOR)は、自在に設定可能です。

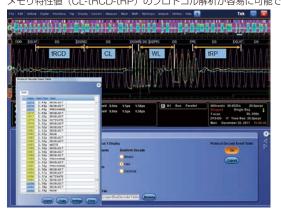

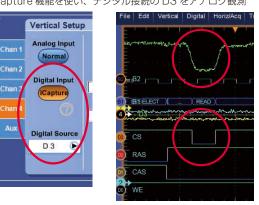

### ■ MSO70000C シリーズのバス機能と iCapture

MSO70000C シリーズには、メモリ・バスのコマンド・ステートを使用して信号を取込む、数多くのバス機能が用意されています。デジタル・チャンネル・メニューで、SO#、RAS#、CAS#、WE#の4つのコマンド信号を割り当てます。割り当てられたコマンド・バスは、バイナリ、16 進、シンボル\*など、さまざまなフォーマットに表示可能です。ピンポイント・トリガにおいてもバス設定が可能ですので、FastAcq機能により毎秒30万波形以上の連続高速取込みが無限にできます。従って、アイ・ダイアグラム評価時に間欠的トラブル波形をスピーディに見つけることができます。MSO70000CシリーズのiCapture機能により、16のデジタル・チャンネルの任意のチャンネルをオシロスコープのアナログ信号入力経路にマルチプレクスできます。デジタル・データのサンプリングで使用されているロジック・スレッショルドを確認したり、シグナル・インテグリティを検証できます。

| シンボル定義 | #Command     | CS RAS CAS WE | MODE_REG  | 0000 | ACTIVATE | 0011 | NOP      | 0111 |

|--------|--------------|---------------|-----------|------|----------|------|----------|------|

|        | #Symbol Name | Pattern       | REFRESH   | 0001 | WRITE    | 0100 | DESELECT | 1XXX |

|        | PATTERN      | BIN           | PRECHARGE | 0010 | READ     | 0101 |          |      |

\*シンボルとは、ビット・パターンを文字列に置換することです。

ライト・コマンドによるバス・トリガ

ライト・コマンドのバス・トリガで FastAcq の高速波形取込み

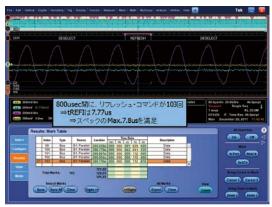

プロトコル・デコード・イベント・テーブルによるコマンド・プロトコル表示 メモリ特性値(CL-tRCD-tRP)のプロトコル解析が容易に可能です。

iCapture 機能を使い、デジタル接続の D3 をアナログ観測

サーチ/マークにおいてもバス機能が用意されてます。 これまで、オシロスコープでは困難だった、メモリ特性値などの プロトコル解析が可能となります。

エッジ、グリッジ、ラント、トランジション、パルス幅、ウィンドウ、タイムアウト、セットアップ/ホールド、パターン、ステート、バス、DDR メモリ・サイクル(オプション DDRA)の検索とマーク表示が可能です。

リフレッシュ・サイクルの平均周期の解析が容易に可能です。

### ■ プローブ

差動信号とシングルエンド信号の両方に使用できるソルダイン・アダプタ対応のプローブを使用することで、再現性の高い測定を 効率的に行なえます。

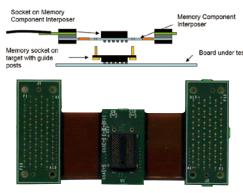

### BGA インターポーザ

プロービングが困難な FBGA パッケージには、BGA インタポーザが最適です。ダイレクト・タイプはロー コストのプロービングの要求に応えます。ソケット・ タイプは、メモリ IC 交換やボード交換を可能とし、 ロジック・アナライザへのインタポーザに切り替え も容易です。

- 1 DDR3-1867 まで対応

- 2 メモリ IC の交換が容易

- 3 ロジック・アナライザ用とオシロスコープ用 インターポーザの切り替えが容易

- 4 インターポーザの再利用が可能なため、 低ランニング・コスト

### ■ オシロスコープ用インターポーザ

BGA インタポーザ

ソケット・タイプ BGA インタポーザ

DDR3 NEX-DDR3MP シリーズ NEX-DDR2MP >U-X

NEX-LPDDR1MPシリーズ

GDDR5: NEX-GDDR5MP シリーズ

NEX-LPDDR2PoPシリーズ

### ■ P7520 型、P7516 型、P7513A 型、P7508 型、P7506 型、P7504 型

TCA 20GHz、16GHz、13GHz、8GHz、6GHz、4GHz TriMode プローブ

P7520型、P7516型、P7513A型、P7508 型、P7506 型、P7504 型 (P75PDPM 型モ ジュールは含まれません) 差動、シングル・エンドおよびコモン・モード の測定に対応。

P75PDPM 型精密差動プロービ ング。モジュール先端部

P75TLRST 型ロング・リーチ・ソルダ・チップはんだ付け例

ソケット·ケーブル(020-2954-XX)とTriModeマイクロ同軸チップの半田例

### 多様な接続方法に対応 ─ ハンダ付け、ハンドヘルド、プロービング・アーム

(020-2960-XX)(恒温槽などでのプロービングに対応)

ソケット・ケーブル(10.4cm)(020-2954-XX)

TriModeマイクロ同軸チップ (020-2955-XX)

ダンプト・ワイヤ・チップ (020-2959-XX)

## ハンダ付けが簡単な抵抗ソルダ・チップ TriMode 抵抗ソルダ・チップ (020-2936-XX) TriMode 拡張抵抗ソルダ・チップ (020-2944-XX)

### ■ P7313型、P7380A型、 P7360A型、P7340A型

TCA 12.5GHz、8GHz、6GHz、4GHz差動プローブ

### ■ P6330型

TEKPROBE II BNC3.5GHz 差動プローブ

※ DP07354型、DP07254型との使用では TPA-BNC型 TekVPI-BNC アダプタが必要です。

■ TDP3500型 TPA 3.5GHz 差動プローブ

## デジタルの検証とデバッグ・ソリューション

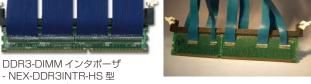

TLA7000 シリーズ TLA7Bxx 型ロジック・アナライザ・モジュールまたは TLA6000 シリーズに、当社パートナである米国 Nexus Technology 社あるいは米国 FuturePlus Systems 社の各種ソリューションと組合せることにより、タイミング解析は もちろんのこと、DDR3-1867までのデータの取込み/デコード、プロトコル解析を行えます。データの解析では、モード・レジスタおよび拡張モード・レジスタへの書込み内容のデコード、バス・サイクル(コマンド、データ)の識別が可能です。 iCapture 機能により、ロジック・アナライザのプローブだけでデジタルとアナログ波形を同時に取込み、オシロスコープと連動さ せ、デジタルと同じ時間軸上でアナログ波形と相関をとって解析することも可能です。さらに FPGA 内部デバッグや他のバスとの 時間相関を取っての解析も可能にしています。

TLA7000 シリーズ・ロジック・アナライザ - TLA7012型ポータブル本体(2モジュール) - TLA7016型: ベンチトップ本体(6 モジュール)

TLA7Bxx 型ロジック・アナライザ・モジュール - TLA7BB2型:68チャンネル、最大メモリ長64M - TLA7BB3 型:102 チャンネル、最大メモリ長 64M - TLA7BB4型: 136 チャンネル、最大メモリ長 64M - TLA7BC4型: 136 チャンネル、最大メモリ長 128M

TLA7000 シリーズ・ロジック・アナライザ - TLA6202型: 68 チャンネル、最大メモリ用 128M - TLA6203 型: 102 チャンネル、最大メモリ用 128M - TLA6204型: 136 チャンネル、最大メモリ用 128M

### ■ プローブ

当社および当社パートナは業界唯一のプロービング・ソリューションを提供しています。当社ロジック・アナライザの誇る高性能・ 高機能をフルに引き出せ、目的に合った最適なプロービングを選択できます。すべてのプローブ・アダプタはバッファを通さず 信号に直接プロービングする方法なので、各信号のタイミング、アナログ波形の観測も可能です。

業界最小 O.5pF 以下のプローブ負荷の P69xx シリーズの cLGA コネクタレス・コンタクト・プローブは、最適な回路基板の直 接実装が可能となります。

直接実装の困難な回路基板の場合、ソケット・タイプの BGA インタポーザが最適です。 DDR2-SDRAM においては、TLA6000 シリーズを使ったローコストの構成も可能です。 DIMM 及び SO-DIMM に特化したインタポーザも高速なデータレートに対応してます。 また、ローコストにプロトコル解析を実現可能なインタポーザも提供してます。

cLGA コネクタレス・コンタクト・プロ ーブによる回路基板への直接プロービ ング(P69xx シリーズ)

ソケット・タイプ BGA インタポーザ - DDR3: NEX-DDR3MP シリーズ - DDR2: NEX-DDR2MP/CIシリーズ

- NEX-SODDR3INTR-HS 型

- NEX-DDR3INTR-HS型

- FS2358B 型

プロトコル用インタポーザ - NEX-DDR3INTR-P型 - NEX-SODDR3INTR-P型

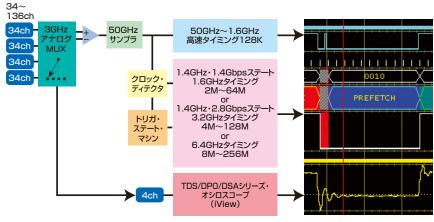

### ■ TLA7Bxx 型 TLA7000 シリーズ・ロジック・アナライザ・モジュール

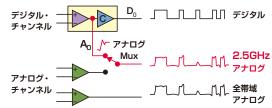

すべての信号をフロントエンドで高速でサンプリングする当社独自の MagniVu アーキテクチャにより、高分解能のタイミングとステートの同時解析を、さらに iCapture(アナログ MUX)により任意入力チャンネルのアナログ解析をも同時に実現します\*。当社従来比6倍以上高速化された50GS/s MagniVu により20ps分解能タイミング解析、DDR3-1867に余裕を持って対応可能な1.4GHzクロック2.8Gbpsデータ・レートのステート・アクイジションと圧倒的なパフォーマンスを実現しています。\*外部オシロスコープが必要です。

トリガ・バルス 放形 データ

アナログ信号

iCapture:ロジック・アナライザで接続した最高 136 チャンネル入力の中の任意の 4 チャンネルまでの信号を モジュール側面の BNC コネクタから外部オシロスコープへ導き出します。

TLA7Bx4型モジュール・アーキテクチャ概念図

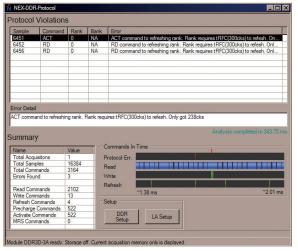

### ■ 解析: DDR2/3 コマンド識別、プロトコル・チェック

当社パートナが提供する各種ソリューションにより、DDR2/3 に対するモード・レジスタおよび拡張モード・レジスタへの書込み内容のデコード、バス・サイクル(コマンド、データ)の識別が可能です。またプロトコル解析も提供しています。

- モード・レジスタおよび拡張モード・レジスタへの書込み内容のデコード

- バス・サイクル (コマンド、データ) の識別

- コマンド・シーケンス、書込み/読出しデータの解析が可能

- DDR2 / 3 プロトコル・チェック・ソフトウェアによるプロトコル違反の自動検出

- ーサマリおよび統計解析

- ライセンス・フリーとライセンスの2種類のバージョン

モード・レジスタおよび拡張モード・レジスタへの書込み内容のデコード例

バス・サイクル(コマンド、データ)の識別表示例

DDR2 / 3 プロトコル・チェック・ソフトウェア表示例 (米国 Nexus Technology 社)

- DDR2/3 の各信号間の詳細なタイミング解析が可能

- 6 倍以上高速化された MagniVu 50GS/s 20ps タイミング

- DDR3-1867 にも余裕を持って対応可能な3倍以上高速化されたステート・アクイジション(当社比)

- 2.8Gbps データ、1.4GHz クロック、128Mb(ハーフ・チャンネル)

- 1.4Gbps データ、1.4GHz クロック、64Mb(フル・チャンネル)

- 180ps (代表値)、220ps (仕様) のセットアップ/ホールド時間ウインドウで余裕のあるデータ捕捉が可能

- ロジック・アナライザからオシロスコープへ信号を導き出しての波形観測。ダブル・プロービング不要

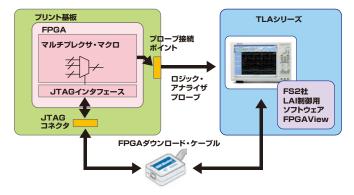

今日多くの FPGA で DDR2/3 のメモリ・コントローラをサ

ポートしています。FPGAView を TLA7000 シリーズに組合せることで、TLA7000 シリーズで Altera 社や Xilinx 社の

FPGA の内部ノードのデバッグ、解析が行えます。マルチプレ

クサ・マクロ(LAI)を FPGA に埋め込むことで、再コンパイ

ルすることなく、信号観測用のピン数を抑えてグループごとに

- 3GHz iCapture (アナログ MUX)

■ FPGA:内部回路をデバッグ可能

信号を切り替えての観測が可能となります。

2 1

∆t → Cursor 1 → to Cursor 2 → = -20ps

1 → Cursor 2 → T = -20ps

タイミング解析:DDR3-DIMM データ・ストローブのフライバイタイミングの 20ps 分解能での捕捉例

FPGAVie wによる FPGA 内部回路デバッグ全体図

## 伝送線路の特性評価と回路基板の検証

部品を実装する前に試作基板を検証することにより、後々のトラブル解析に要する時間を短縮できます。DSA8300型は真の差動 TDR 測定が可能なサンプリング・オシロスコープです。DSA8300型により、DDR メモリ搭載用基板やコネクタについて、シングルエンドだけでなく差動線路のインピーダンス、トレース長、クロストークの測定ができます。また、IConnect®シグナル・インテグリティ TDR/VNA ソフトウェアにより、簡単に正確なSパラメータ測定や回路モデリングを行なえます。

DSA8300 型サンプリング・オシロスコープ、80Exx 型電気サンプリング / TDR モジュールおよび IConnect® シグナル・インテグリティ TDR/VNA ソフトウェア

〒108-6106 東京都港区港南2-15-2 品川インターシティ B棟6階 ヨッlgい オシロテクトロニクス お客様コールセンター TEL:0120-441-046 電話受付時間/9:00~12:00~13:00~19:00(土・日・祝・弊社休業日を除く)

## www.tektronix.com/ja

- 記載内容は予告なく変更することがありますので、あらかじめご了承ください。

- © Tektronix 2011年12月 52Z-21167-9

- \* TEKTRONIX および TEK は Tektronix, Inc. の登録商標です。記載された商品名はすべて各社の商標あるいは登録商標です。