## MIPIの規格動向と測定ソリューション

テクトロニクス・イノベーション・フォーラム2011 宮崎 強

www.tektronix.com/ja

## 内容

- はじめに (MIPI® 技術の概要)

- MIPI D-PHYの概要

- MIPI D-PHY測定ソリューション

- M-PHYの概要

- MIPI M-PHY測定ソリューション

## はじめに MIPI®技術の概要

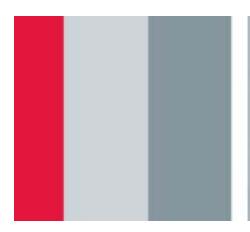

- MIPI AllianceはMobile Industry Processor Interface Allianceを意味する

- モバイル機器内のプロセッサとペリフェラルのインタフェースのシンプル化とその普及を目指したアライアンス

- MIPI規格では、プロセッサとカメラ、ディスプレイ、RF、GPS、オーディオ等とのインタフェースを規定

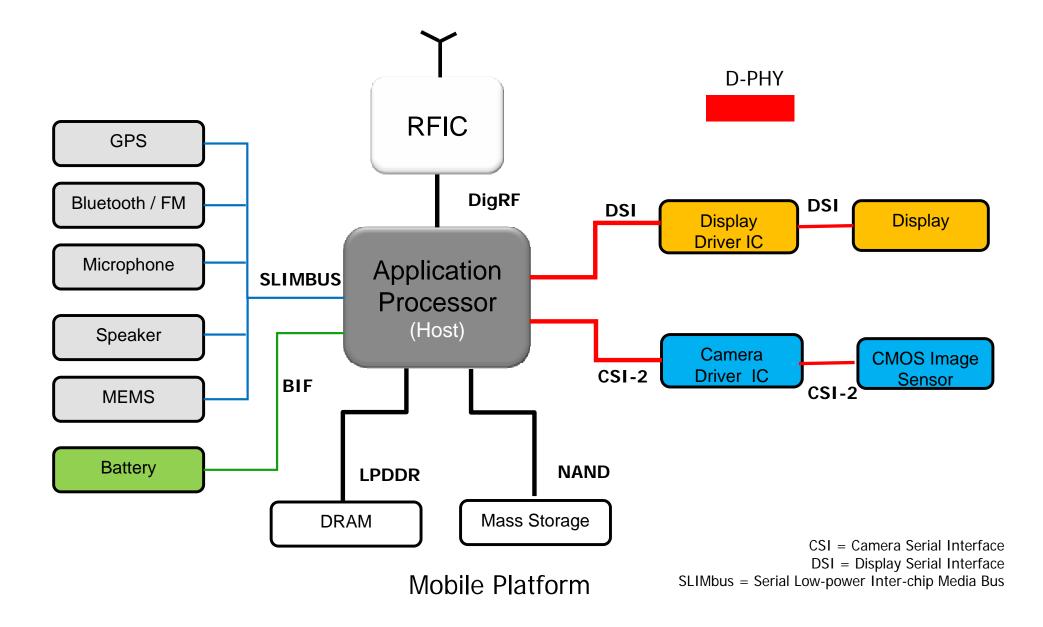

- 特にMIPI D-PHY規格ではカメラやディスプレイとのインタフェースの物理層を規定

- ディスプレイとのインタフェース・プロトコルはDSI規格(Display Serial Interface)にて規定

- カメラとのインタフェース・プロトコルはCSI-2規格(Camera Serial Interface-2)にて規定

- MIPI M-PHY規格ではRFやフラッシュ・メモリとのインタフェースも視野に 入れた物理層を規定

- プロトコルはDigRF、UniPro、UFS、LLIなど

- TektronixはMIPI AllianceのContributorメンバー

#### MIPI D-PHY

# MIPI の概要 次世代モバイル・プラットフォームの例

#### 1. MIPI D-PHYの概要

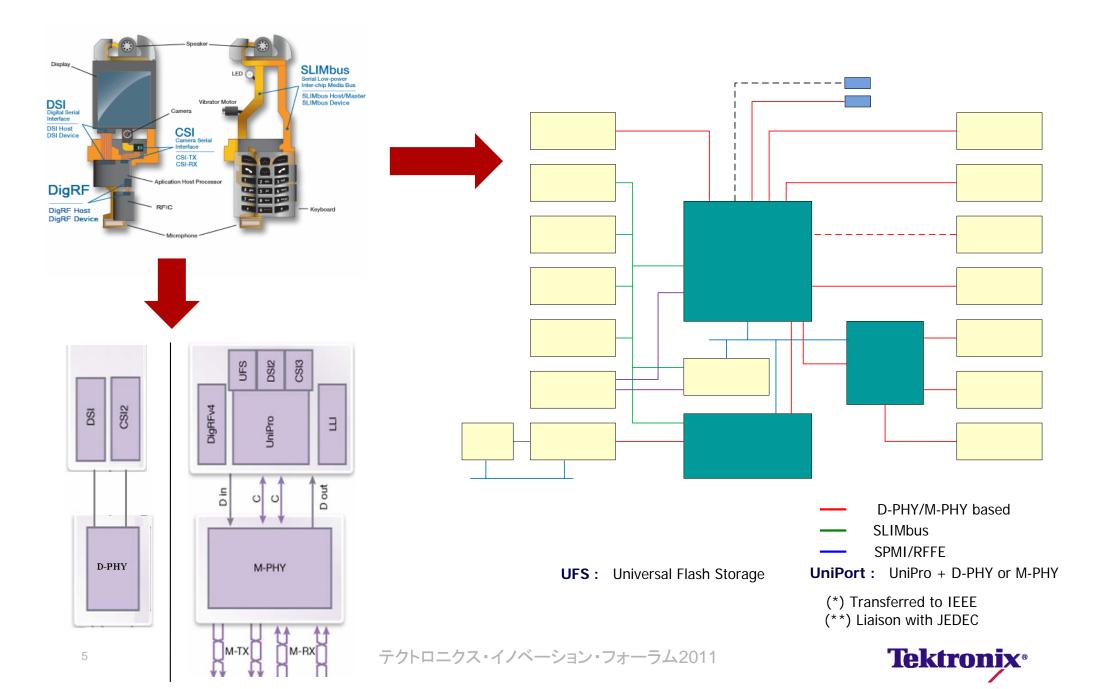

- MIPI D-PHYは、電気仕様を定めた物理レイヤで、その上位に Display Serial Interface(DSI)やCamera Serial Interface(CSI-2) などのプロトコルが位置する。

- クロック 1レーン + 1レーン以上のデータ・レーン

2Data Lane PHYの構成例

## MIPI D-PHY概要

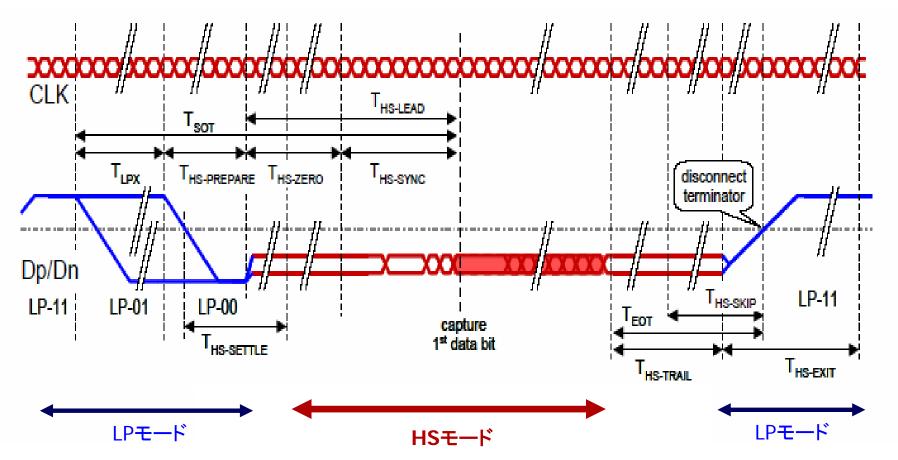

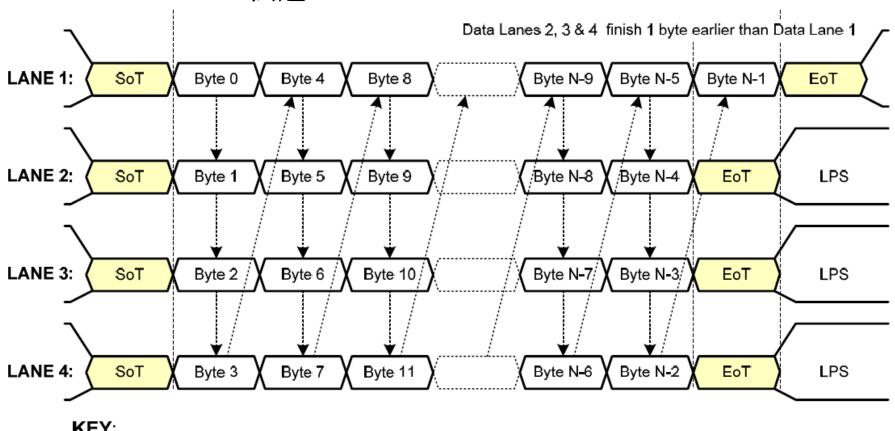

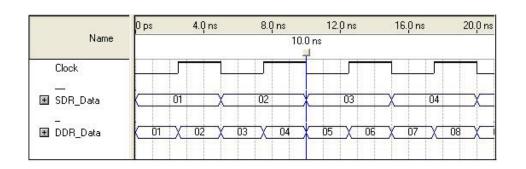

- クロックとデータによる伝送でクロックはDDR動作

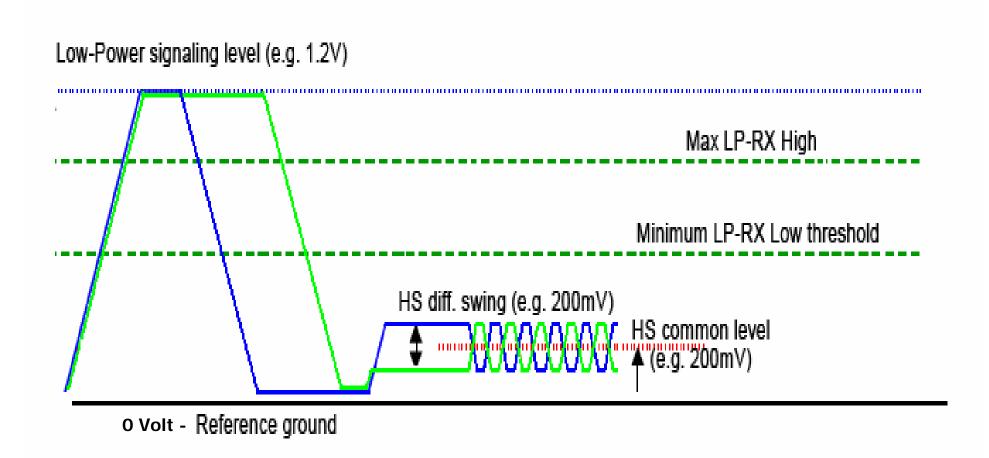

- 2つの伝送モード、Low Powerモード(LP)とHigh Speedモード(HS)がある

#### MIPI D-PHY概要

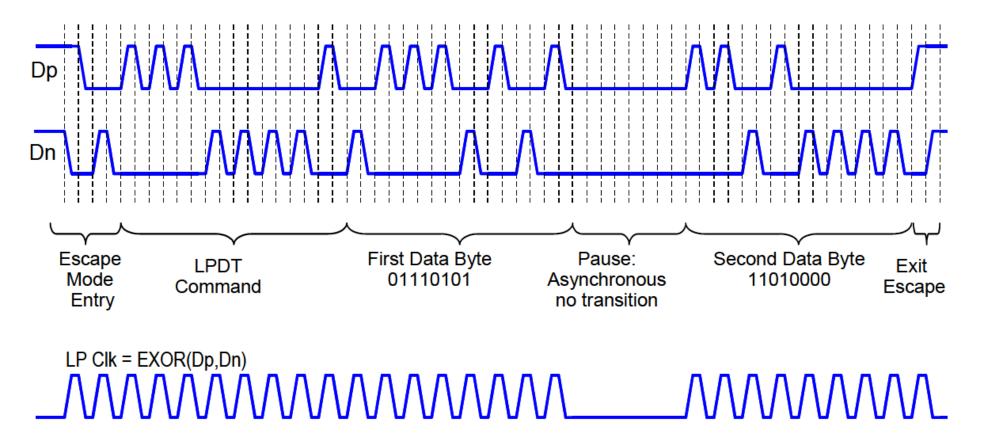

- 最大4データ・レーン + 1クロック・レーンによる伝送

- 各レーンの最大データ・レート

- HSモードは80 Mbps ~ 1Gbps

- LPモードは10 Mbps以下(主にコマンドの伝送用だがデータ伝送もあり)

- HS信号のTr/Tf(20-80%立上り時間/立下り時間)は最小150psと規定

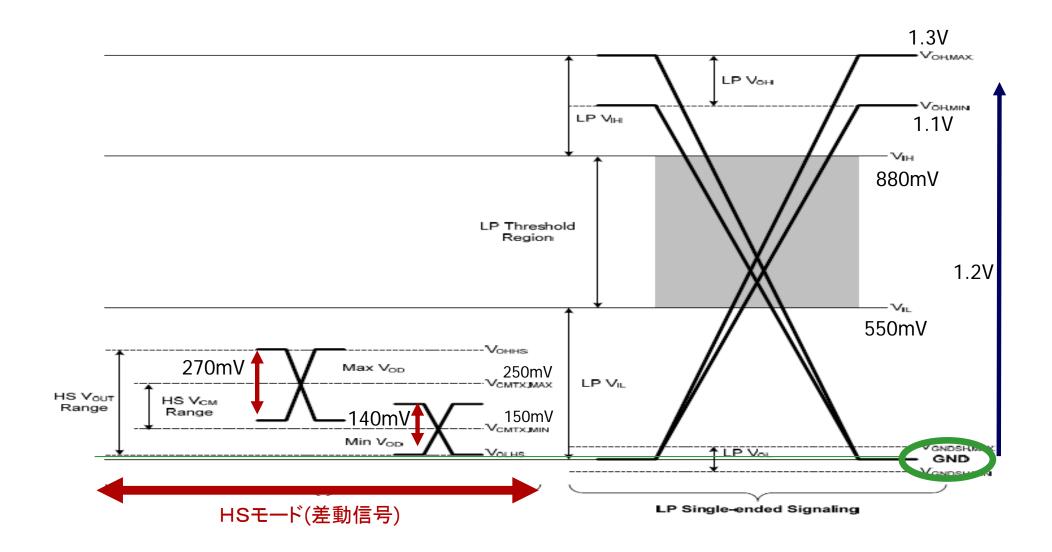

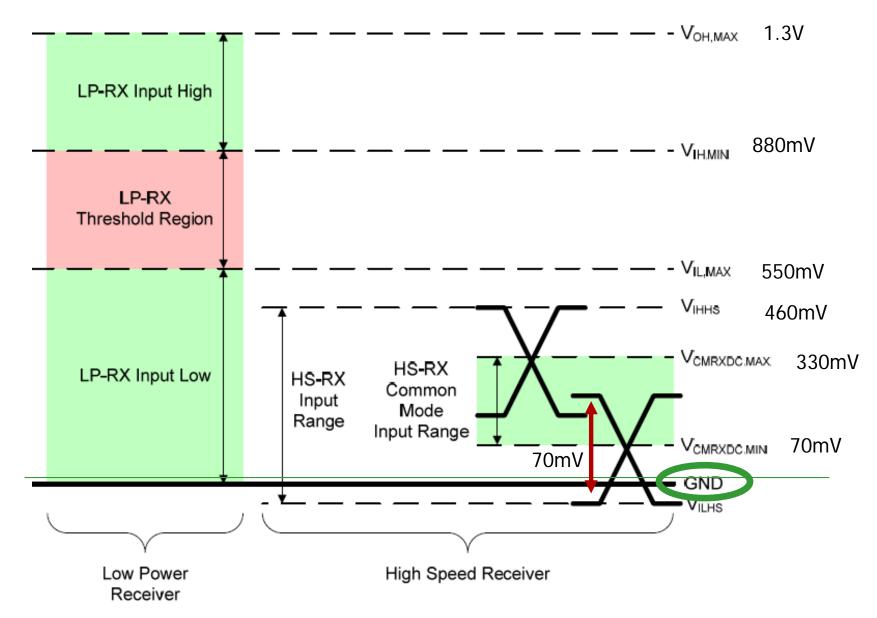

- 信号方式は、HSとLPの各モードで異なる

- HSモードはLVDSでCを介してGNDに50Ω終端(差動100Ω)

- LPモードは終端抵抗無しのシングルエンド動作

- 双方向伝送または片方向伝送

最近の高分解能ディスプレイや高分解能カメラの採用により 4Dataレーン+ 1Clockレーン構成の採用が増えています。 また、HSモードで1Gbps超、LPモードで10Mbps超の検討もされています。 将来の高分解能化に向けた模索が行われています。

## MIPI D-PHY概要

#### HSモードとLPモードがダイナミックに遷移

## D-PHY Tx信号レベル

## D-PHY Rx信号レベル

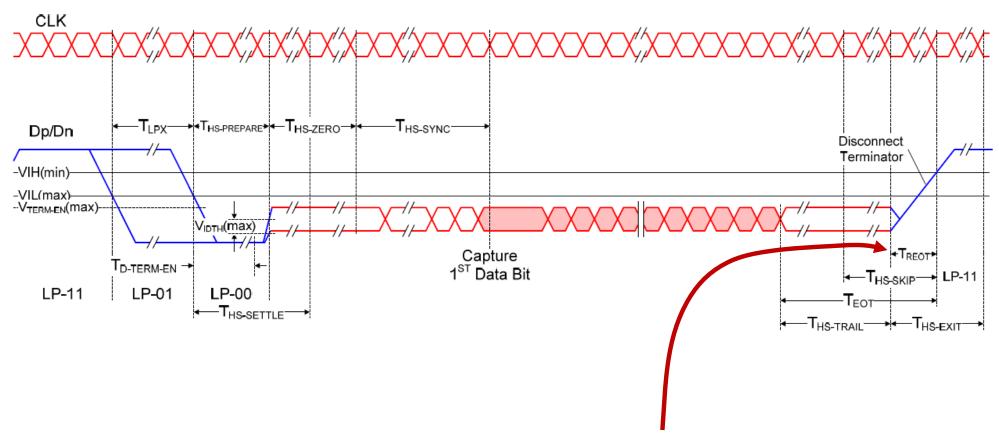

## Tx Data Lane の HS/LP遷移タイミング

TREOT (30% to 85% のTf/Tf)は35ns以下

## Tx Clock Lane の HS/LP遷移タイミング

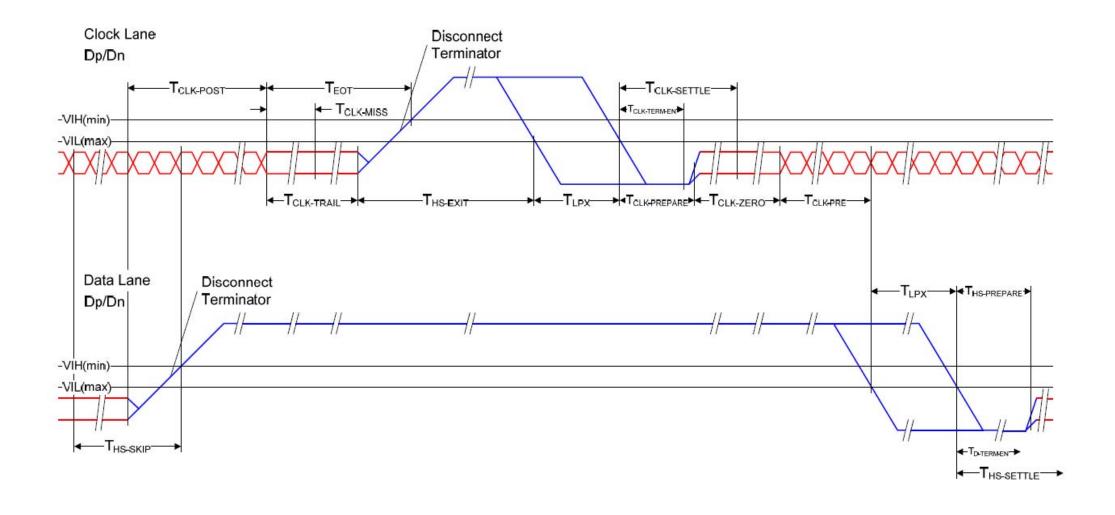

#### **LPDT**

- LPDT(Low Power Data Transmission)では、レシーバがDpとDnの EXORでクロックを再生

- TRLP/TFLP(Tx LP Dataの15% to 85% Tr/Tf)は25ns以下

## MIPI DSIの論理層

Multi Data Lane 伝送

KEY:

LPS - Low Power State

SoT – Start of Transmission

EoT – End of Transmission

4データ・レーン構成時の伝送

## MIPI DSIの論理層

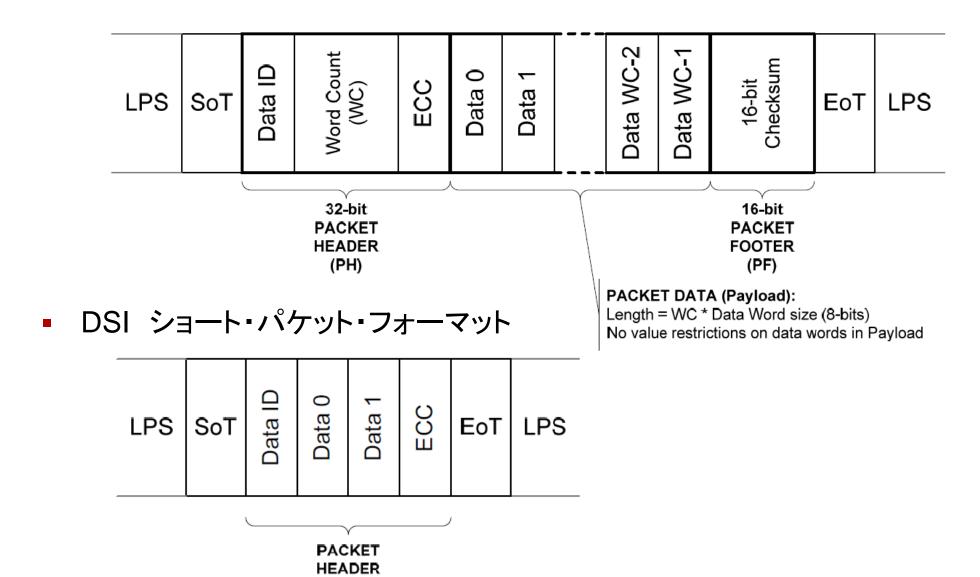

■ DSI ロング・パケット・フォーマット

(PH)

## MIPI DSIの論理層

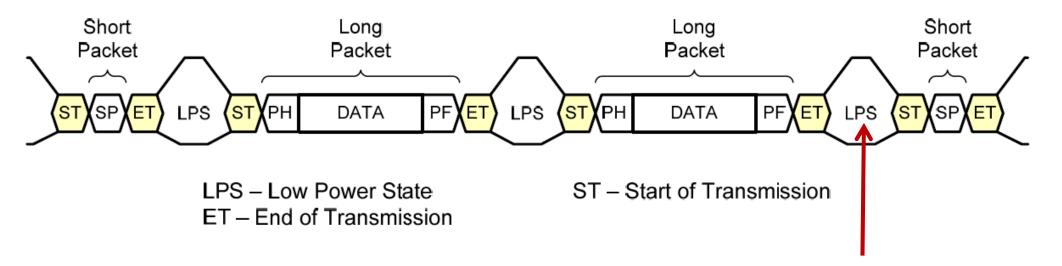

複数パケットのHS伝送 (SOT) SP (EOT) LPS LPS LPS SOTX SPXEOT LgP Separate Transmissions LPS - Low Power State Short Packet SoT - Start of Transmission Long Packet LaP -EoT - End of Transmission LPSでは差動100Ω終端が 複数パケットの連続HS伝送 切り離され、低消費電力となる LPS LgP Single Transmission

## MIPI CSI-2の論理層

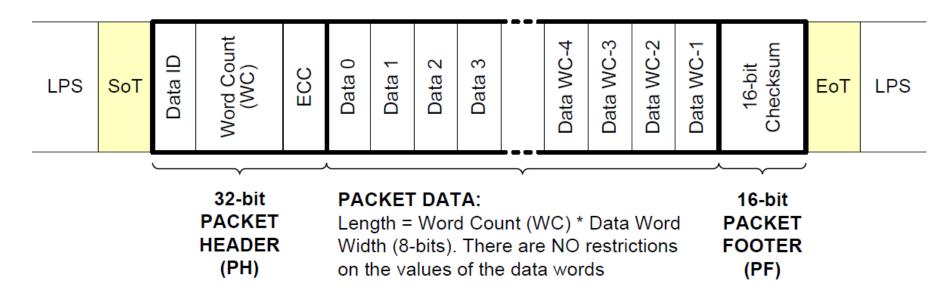

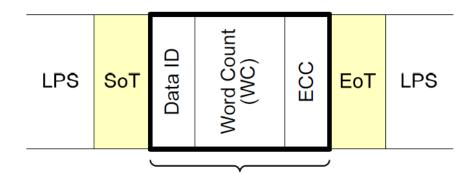

CSI-2 ロング・パケット・フォーマット

CSI-2 ショート・パケット・フォーマット

32-bit SHORT PACKET (SH) Data Type (DT) = 0x00 - 0x0F

## MIPI CSI-2の論理層

#### 複数パケットのHS伝送

LPSでは差動100Ω終端が 切り離され、低消費電力となる

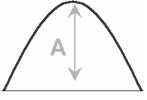

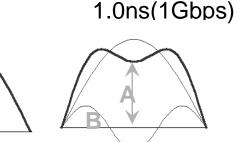

## 2. MIPI D-PHY測定ソリューション 必要なオシロスコープの周波数帯域は?

- 高速デジタル信号は一般的に方形波

- 周波数領域で見ると、方形波は基本波と奇数高調波により構成

- 方形波の基本波周波数(最高)=ビット・レート(NRZ)/2例: 1Gbpsの場合500MHz

- 方形波では<u>5次高調波までの捕捉が目安</u>

- 実際は立上り時間Tr(20-80%)がキー

- 二一周波数(fKnee)\*=0.4/Tr

- 3%誤差内での立上り時間測定には、 周波数帯域=1.4 × fKnee が目安

• 基本波:500MHz

• 第3高調波 : 1.5GHz

• 第5高調波 : 2.5GHz

• fKnee=2.67GHz

推奨周波数帯域=3.74GHz

(5%測定確度ならfKnee × 1.2で 3.2GHz)

$3\omega$

$5\omega$

2.0ns (500MHz)

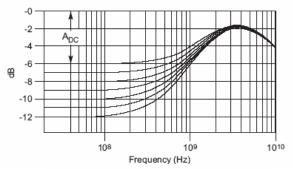

$$H(s) = \omega_{P2} \frac{s + \omega_{P1} * A_{DC}}{(s + \omega_{P1}) * (s + \omega_{P2})}$$

Tektronix<sup>®</sup>

ω<sub>P1</sub> = pole 1 = 2π\*2 GHz ω<sub>P2</sub> = pole 2 = 2π\*8 GHz A<sub>DC</sub> = dc gain

W

<sup>\*</sup>*高調波成分が急速に減衰する点。引用:* Howard Johnson and Martin Graham,「High-Speed Digital Design: A Handbook of Black Magic」, p.2. Prentice Hall, 1993

# 推奨オシロスコープ

DPO7000CシリーズとTDP3500型プローブ

DSA/DPO70000CシリーズとP7340A型プローブ

|   | 機種名           | 周波数帯域   | 立ち上がり<br>(20%-80%) | 最大サンプリング・レート                                    | プロ <b>ー</b> ブ・<br>インターフェース |

|---|---------------|---------|--------------------|-------------------------------------------------|----------------------------|

|   | DSA/DPO72004C | 20GHz   | 17ps               | 100GS/s@2チャンネル<br>50GS/s@4チャンネル                 | TekConnect                 |

|   | DSA/DPO71604C | 16GHz   | 21ps               |                                                 |                            |

|   | DSA/DPO71254C | 12.5GHz | 23ps               |                                                 |                            |

|   | DSA/DPO70804B | 8GHz    | 33ps               | 25GS/s@4チャンネル                                   |                            |

|   | DSA/DPO70604C | 6GHz    | 43ps               |                                                 |                            |

| • | DSA/DPO70404C | 4GHz    | 65ps               |                                                 |                            |

| ٠ | DPO7354       | 3.5GHz  | 95ps               | 40GS/s@1チャンネル<br>20GS/s@2チャンネル<br>10GS/s@4チャンネル |                            |

|   | DPO7254       | 2.5GHz  | 100ps              |                                                 | TekVPI                     |

|   | DPO7104       | 1GHz    | 200ps              |                                                 |                            |

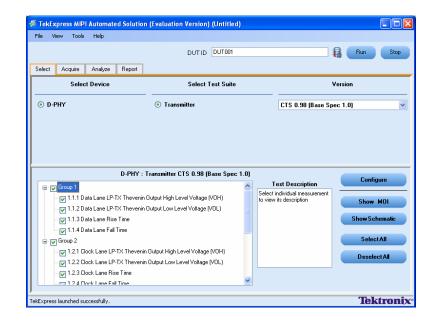

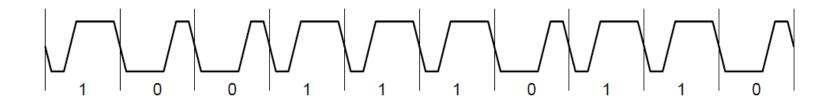

## Opt.D-PHYTX 規格適合性自動テスト

- Opt.D-PHYTX (D-PHY 自動測定機能)

- D-PHY規格適合性を全自動測定

- 使用にはTEKEXP(自動コンプライアンス・テスト・ソフトウェア TekExpress)が必要

- DPO7000C, DPO/DSA/MSO70000Cシリーズのオプション

#### D-PHYTXの特長

- カーソル設定、測定範囲指定も含め全自動

- 最新のD-PHY規格 (v1.0)に準拠

- 最新の CTS (v1.0)に適合

- UNH Conformance Test Suiteに準拠

- ツリー構造による測定項目、測定グループ選択

- カスタム・リミット/ リミット値の編集(on the fly)

- テスト・レポート

- 測定部分の波形イメージ

- Pass/Fail サマリ(マージンの詳細付)

- 高精度テスト用最小構成は3.5GHz(DPO7354C)から可能

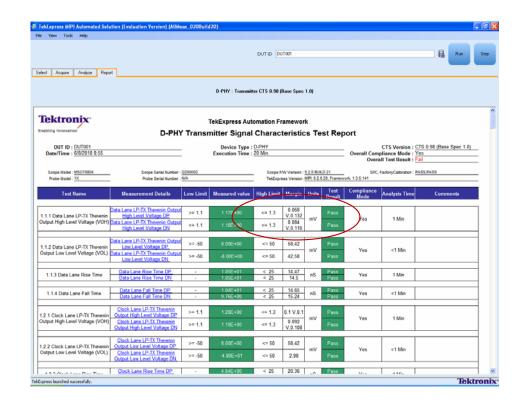

## D-PHYTX の測定結果レポート画面

- 詳細なテスト・レポート

- Pass/Failサマリ表

- 各テストにおけるマージンの 詳細

- 各テスト箇所の波形画面を リンク

- 全レーンの全テストについて 統合レポート生成

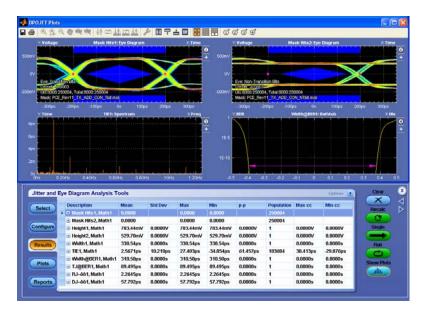

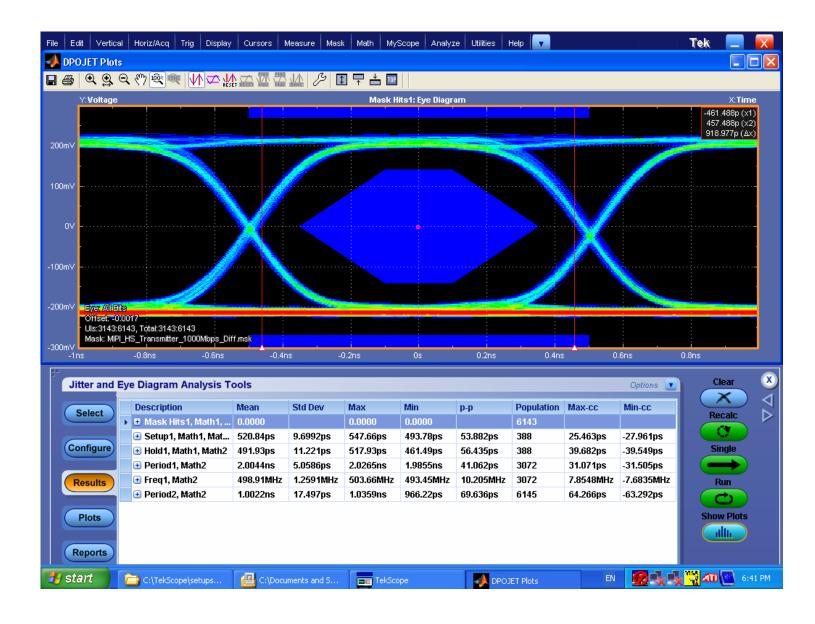

## 解析ソフトウェア DPOJET

- DPOJETジッタ&アイ・ダイアグラム解析 ソフトウェア

- クロック・リカバリとアイ・ダイアグラム測定、 ジッタ/タイミング測定、周波数/周期、振幅、 各種タイミング測定

- クロック、データ、クロックとデータ間

- エンベデッド・クロックと外部クロックの両方に対応 (逓倍クロックにも対応)

- 同時に99項目まで測定

- アイ・ダイアグラム、ヒストグラム、スペクトラム、 バス・タブ、サイクル・トレンド・プロット表示

- Arb Filterによるディエンベデッド波形の解析

- 以前に保存した波形での測定も可能

- Pass/Fail自動判定とレポート生成機能

- D-PHY Essential (Opt. DPHY)により MIPI D-PHY規格適合性試験が可能

- D-PHY base spec に準拠

- UNH Conformance Test Suiteに準拠

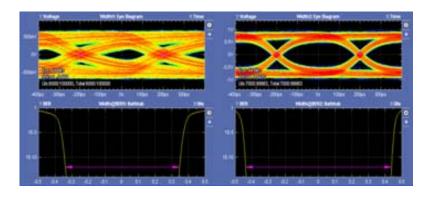

ジッタとアイダイアグラムの測定例

ソフトウェア・イコライズ前後の波形を用いた アイダイアグラムとバスタブ・カーブによるBER予測

# Test 8.1.5 – Data Lane HS TX Single-Ended Output High Voltage (VOHHS)

# Test 8.2.3 – Data Lane LP-TX Slew Rate vs. C–LOAD ( $\delta$ V/ $\delta$ tSR)

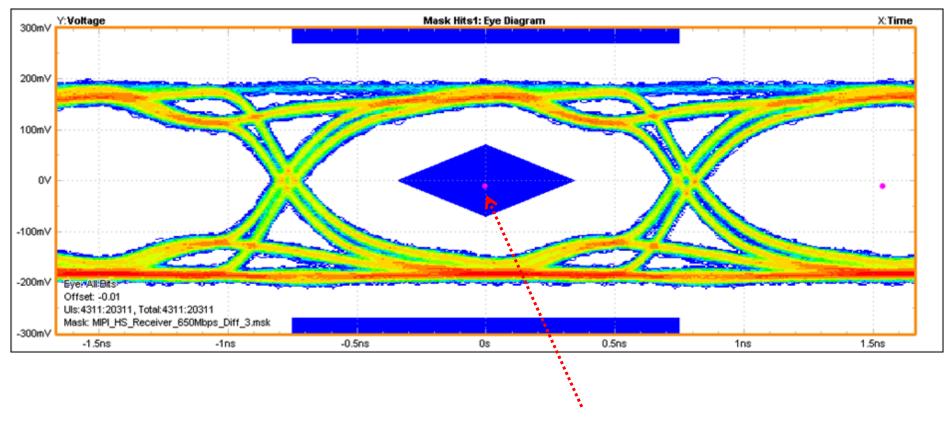

## MIPI D-PHY HS信号 マスクテストの例

■ 振幅、ジッタ、セットアップ時間、ホールド時間、立上り時間などの 仕様からマスクを作成し、マスクテストを行うことが可能

## MIPI D-PHY TX テスト用推奨機器 その1 規格適合自動テスト

- TEKEXP(自動コンプライアンス・テスト・ソフトウェア)

- Opt. D-PHYTX

- D-PHYTX自動テスト・ソフトウェア

- MIPI D-PHYの規格適合性、特性評価用ソフトウェア

- 動作には、TEKEXPが必要

- DPO7000C、DSA/DPO/MSO70000Cシリーズ上で動作

DPO7000Cシリーズ

- 推奨オシロスコープ: DPO7254C型以上

- DPO7254C/DPO7354C型

- DSA/DPO/MSO70000Cシリーズ

Rise Time 150psを±5%誤差以下で測定のためにはDPO7354C型以上推奨 ±3%誤差以下で測定のためにはDSA70404C型以上推奨

- 推奨プローブ

- DPO7000Cシリーズ: TAP3500×4本またはTDP3500型×3本(または4本)

- DSA/DPO/MSO70000Cシリーズ:

P7240×4本またはP73xx×3本(または4本)

# MIPI D-PHY TX テスト用推奨機器 その2 物理層の解析

- MIPI D-PHY Essentials (Opt. D-PHY)

- D-PHYテスト用セットアップ・ライブラリおよびMOI

- MIPI D-PHYの特性評価、デバッグ、コンプライアンス・テスト

- テスト・レポートを自動生成

- DPO7000(C)、DSA/DPO70000(B/C)、MSO70000(C)シリーズ上で動作

- 動作にはDPOJET Advancedが必要 (Opt. DJA)

- 推奨オシロスコープ: DPO7254(C)型以上

- DPO7254(C)/DPO7354(C)型

- DSA/DPO70000(B/C)シリーズ

- MSO70000(C)シリーズ

Rise Time 150psを±5%誤差以下で測定のためにはDPO7354C型以上推奨 ±3%誤差以下で測定のためにはDSA70404B/C型以上推奨

- 推奨プローブ

- DPO7000Cシリーズ: TAP3500×4本またはTDP3500型×3本(または4本)

- DSA/DPO70000(B/C)、MSO70000(C)シリーズ:

P7240×4本またはP73xx×3本(または4本)

## CSI2/DSI 信号発生 PG3A シリーズ・デジタル・パターン・ジェネレータ

|                | PG3AMOD                      | PG3ACAB         |  |

|----------------|------------------------------|-----------------|--|

| 最大クロック・レート     | 300 MHz (SDR) / 600MHz (DDR) |                 |  |

| 出力チャンネル数       | 64 (SDR) / 32 (DDR)          |                 |  |

| メモリ長           | 32M Vectors                  |                 |  |

|                |                              |                 |  |

|                |                              |                 |  |

| 使用形態           | TLA7000へのインストール              | スタンドアローン・キャビネット |  |

| アプリケーション専用のGUI | MIPI – DSI, MIPI - CSI       |                 |  |

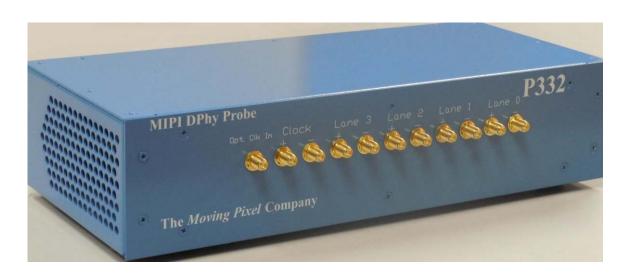

## P332型 MIPI DPhy 出力プローブ (PG3A用)

- MIPI D-PHY規格に準拠

- 業界唯一、4レーン同時出力をサポート: 1.5Gbps/レーン

- レーン毎に独立した遅延調整、信号レベル調整

- ビデオ、動画、オン・ザ・フライでのビデオへのコマンド挿入をサポート

P332型 プローブ

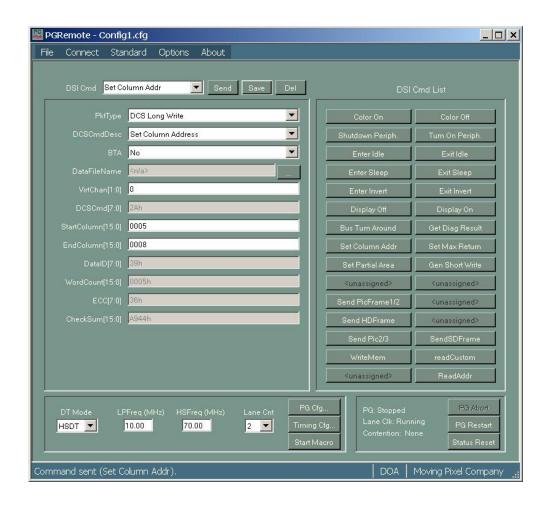

## CSI2/DSI 信号発生ソフトウェア

#### PGRemote-CSI-DSI

- ボタン操作により MIPI CSI2 または MIPI DSI信号を自動生成

- DSI V1.02もサポート

- ユーザによる0、1のベクタ設定は 不要

- カスタム・コマンド、マクロ、リモート・コントロール、オフライン・サポート

- TLAまたはPCのWindows上で動作

- ビットマップ画像ファイルからMIPI信号に自動変換可能

# PG3A + P332 MIPI DPhy プローブ のHS出力例

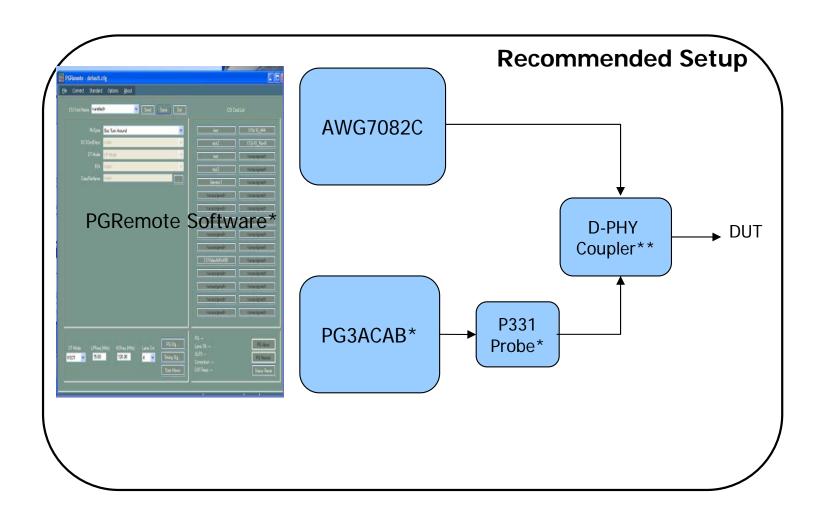

## CSI2/DSI 信号発生用推奨機器

- PG3ACAB A6型

- キャビネット付デジタル・パターン・ジェネレータ (TLA7000で使用する場合は、PG3AMOD型)

- P332型と組み合わせて1.5Gbpsまでサポート

- P332 A6型

- MIPI D-PHY プローブ (PG3A用)

- 1.5Gbps/レーン で4レーン同時出力をサポート

- PGRemote-CSI-DSI型

- CSI2/DSI信号発生ソフトウェア

- DSI V1.02 もサポート

## D-PHY Rx: テスト・ソリューション

■ AWG7000Cシリーズにてノイズとジッタを付加

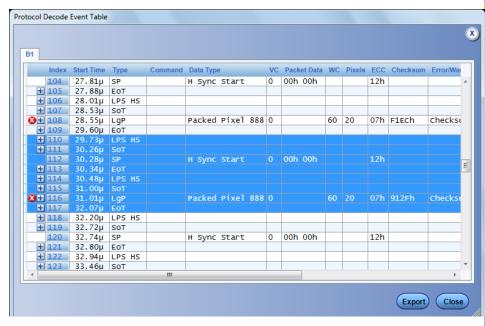

## プロトコル解析 オシロスコープによるDSI-1/CSI-2のデコード

- バス・デコード表示トイベント・テーブル表示

- Start of Transmission (SoT)

- Data Type (Packed Pixel 888など)

- Virtual Channel, Word Count

- Pixel値(Red-255,Green-216,Blue-000など)

- Checksum

- End of Transmission (EoT)

- 問題箇所のエラー/警告表示

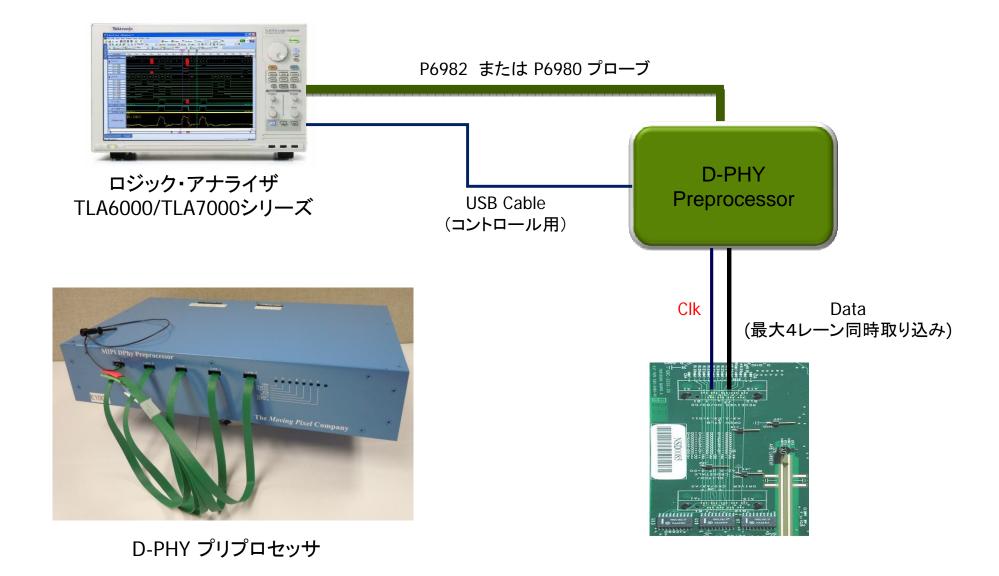

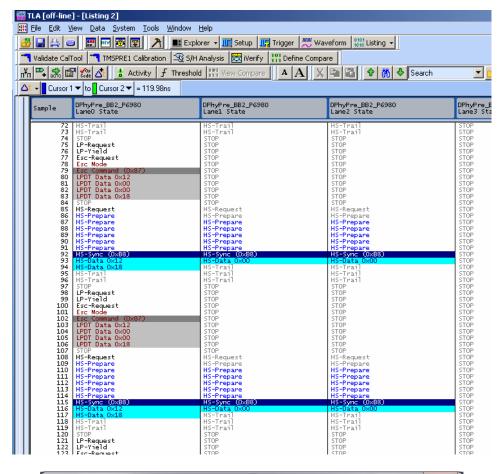

# プロトコル解析 ロジック・アナライザによるCSI-2/DSIのデコード

# D-PHY プリプロセッサ

- 最大4レーン同時取り込み、各レーン1.5Gbps まで対応

- CSI-2/DSIプロトコルをデコード

- LPとHSデータを一括取り込み

- パケット・レベル・トリガ機能

- リアルタイム・フィルタリング

- レーン・アクティビティとエラー・ステータス表示

- ソルダイン・プローブ(カラーコード付き)

- 画像ファイル出力(保存)

- TLA6000シリーズ または TLA7000シリーズと組み合わせて使用

## D-PHY デコード

- 1 ~ 4 レーン D-PHY data

- デコード表示

- LP コマンドとデータ

- LP/HS遷移

- DCSコマンド

- DSIデータ・フォーマット (RGB888など)

- CSIデータ・フォーマット (YUV420 10bit、RGB888など)

- ECC/CRCエラー

## MIPI D-PHYプロトコル解析用推奨機器

## オシロスコープによるプロトコル解析

- DPO7000CシリーズまたはDPO/DSA/MSO70000Cシリーズ

- Opt.SR-DPHY (DSI/CSI-2シリアル解析機能)

- プローブ

- TDP3500型、TAP3500型など(DPO7000C用)

- P7340Aなど(DPO/DSA/MSO70000C用)

### ロジック・アナライザによるプロトコル解析

- TLA6202型

- 68chロジック・アナライザ

- P6982型 ×2本

- ロジック・アナライザ用D-Maxプローブ

- DPHYPRE

- D-PHYプリプロセッサおよびソフトウェア

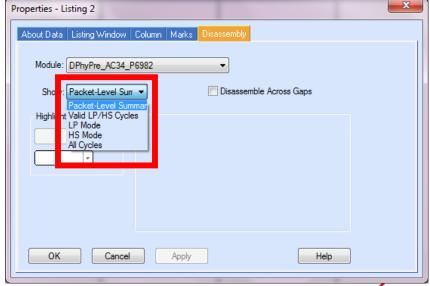

## 3. M-PHYの概要

- 高速シリアル通信

- M-PHY TxとM-PHY Rx 間の通信(dual-simplex)

- 1レーンまたは複数レーンをサポート

- 8b10b

- CSI、DSI、UniPro、UFS、DigRF、LLIなどのプロトコル

# M-PHY のデータ・レート

- - 2つのシリーズ、A-seriesとB-series

- それぞれ3つのGear、G1、G2、G3

- 50Ω終端(差動100Ω)されている

- Low Speedモード

- 2つのType、TYPE- I (PWM)、TYPE- II (SYS)

- PWMには7つのGear

- 差動100Ωまたは10kΩ以上

| Signaling<br>Mode | Max.Speed | Level (V)      | Impedance                  |

|-------------------|-----------|----------------|----------------------------|

| HS                | 5.83Gbps  | 200e-3/ 120e-3 | 50 ohms<br>(差動100 ohm)     |

| PWM               | 576Mbps   | 400e-3/ 240e-3 | 10k/50 ohms                |

| (TYPE-I)          |           | 200e-3/ 120e-3 | (差動100 ohm)                |

| SYS               | 576Mbps   | 400e-3/ 240e-3 | 10k/50 ohms<br>(差動100 ohm) |

| (TYPE-II)         |           | 200e-3/ 120e-3 |                            |

|  | Data rates |       |            |            |  |  |

|--|------------|-------|------------|------------|--|--|

|  |            | Gears | A (Gbps)   | B (Gbps)   |  |  |

|  | HS         | G1    | 1.25       | 1.45       |  |  |

|  |            | G2    | 2.5        | 2.91       |  |  |

|  |            | G3    | 5          | 5.83       |  |  |

|  | PWM        | Gears | Min (Mb/s) | Max (Mb/s) |  |  |

|  |            | G0    | 0.01       | 3          |  |  |

|  |            | G1    | 3          | 9          |  |  |

|  |            | G2    | 6          | 18         |  |  |

|  |            | G3    | 12         | 36         |  |  |

|  |            | G4    | 24         | 72         |  |  |

|  |            | G5    | 48         | 144        |  |  |

|  |            | G6    | 96         | 288        |  |  |

|  |            | G7    | 192        | 576        |  |  |

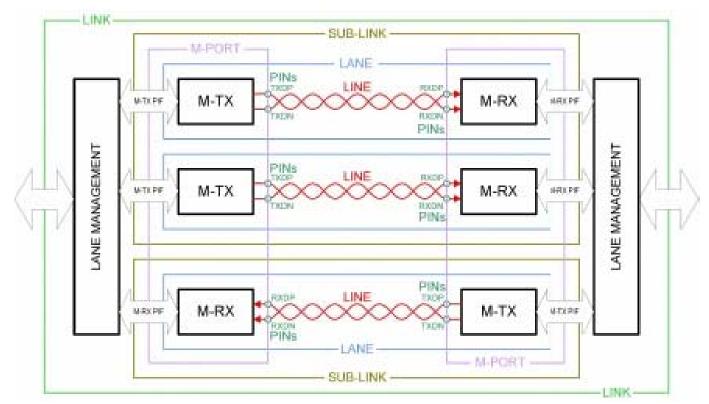

# M-PHYのシグナリング

- HSモード

- Embedded Clock

- NRZ

- TYPE- I PWM

- TYPE-II SYS

- Reference Clockを共有

- NRZ

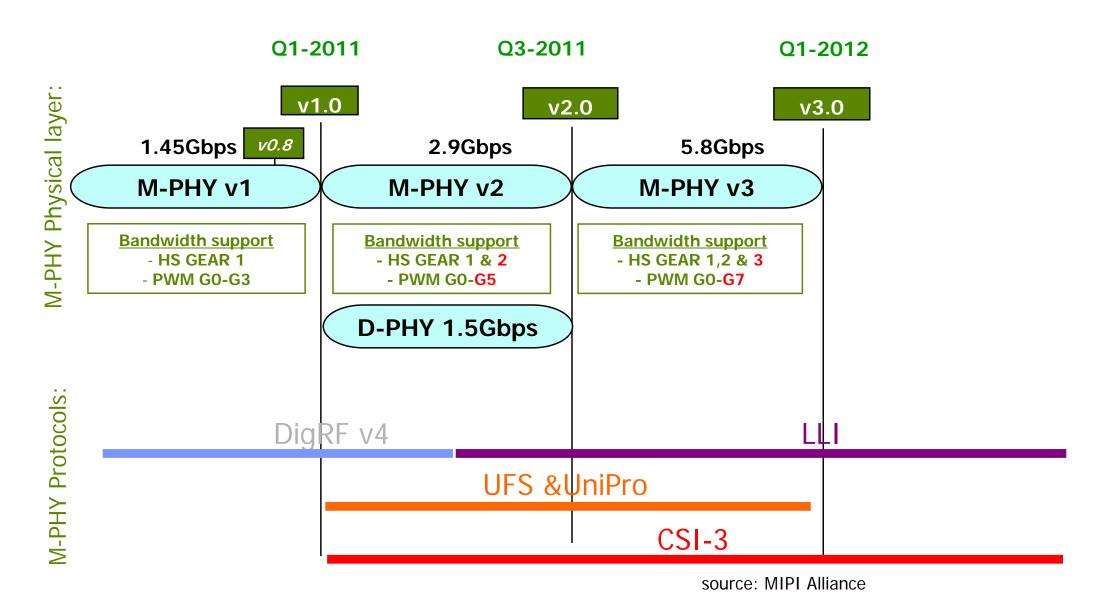

# M-PHY Technology のロードマップ

#### **UFS**

- UFS (Universal Flash Storage)

- M-PHY物理層によるUnipro(Unified Protocol)とUFSを理想的なインタフェースとしてJEDECが承認

- 2011年2月にJEDEC STANDARD JESD220としてUFS規格を公開

- モバイル機器のストレージ・インタフェースとして普及が見込まれる

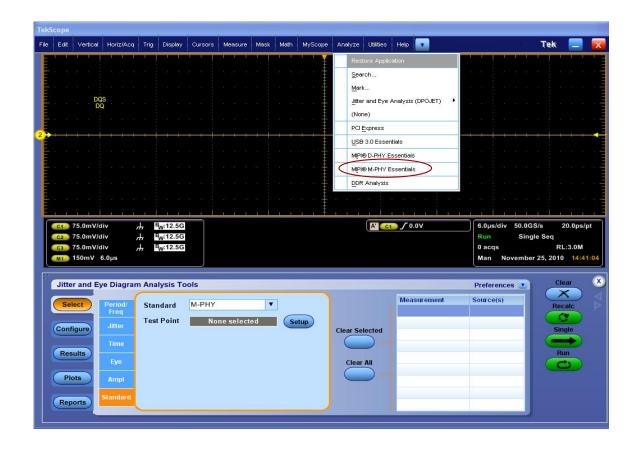

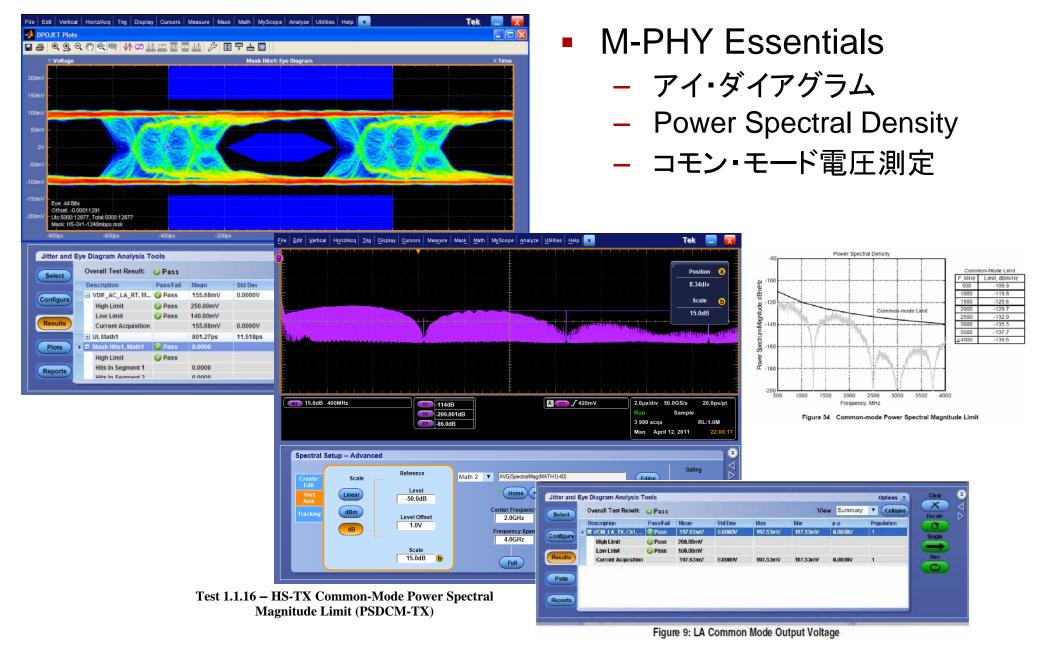

# 4. MIPI M-PHY測定ソリューション M-PHY Tx 物理層テスト

- M-PHY Essentials (Opt. M-PHY)

- DPOJET用設定ライブラリ(DPOJET Advancedが必要)

- 解析および規格適合性試験

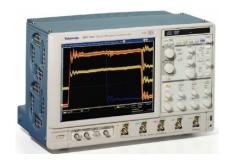

## M-PHY Essentialsによる測定例

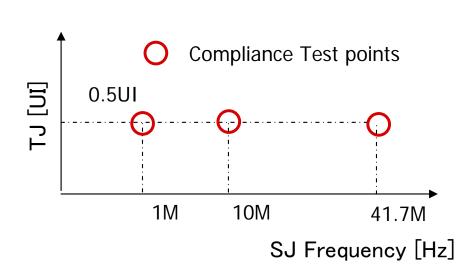

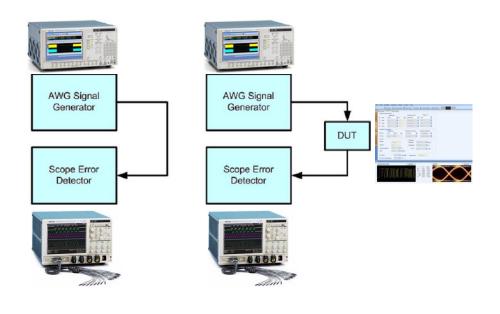

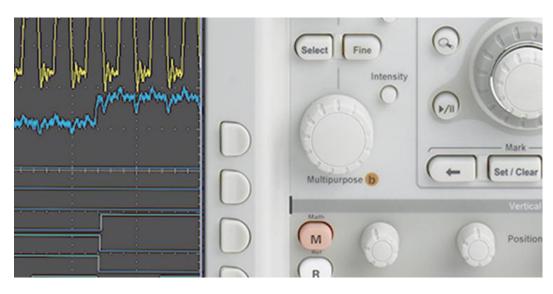

## M-PHY Rx: ジッタ耐性テスト

- Rx ジッタ耐性

- Rx アイ開口、差動入力振幅耐性

- コモン・モード入力耐性

- 入力パルス幅耐性

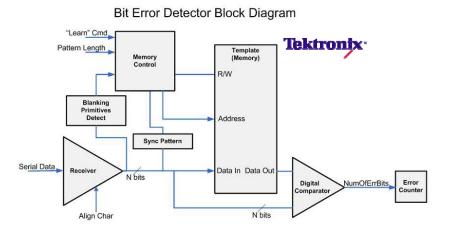

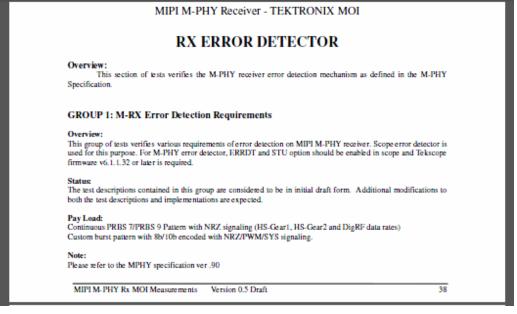

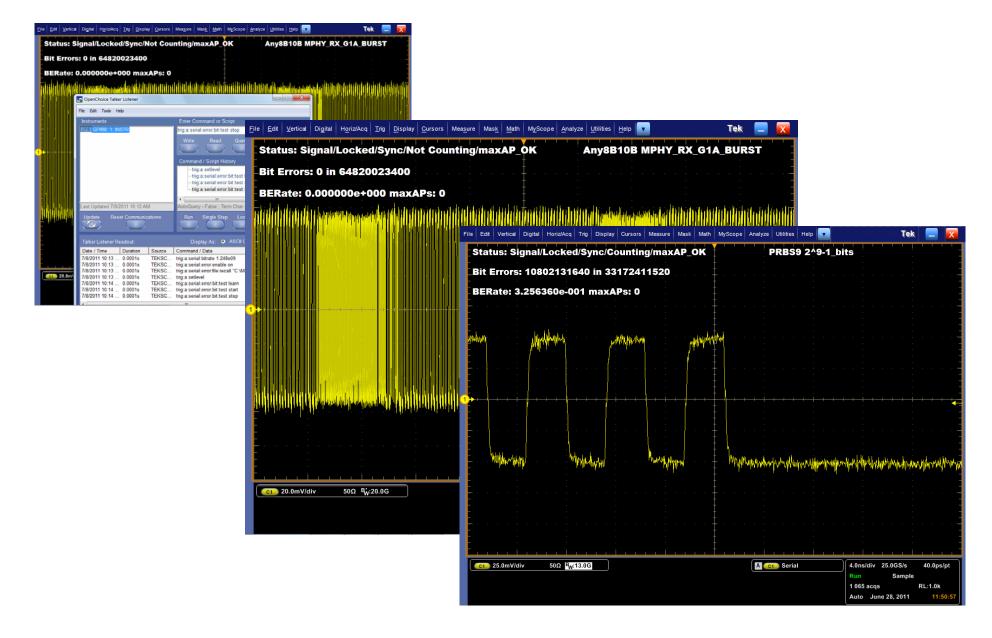

## M-PHY Rx:ビット・エラー検出テスト

オシロスコープ内蔵 BER測定機能Opt.ERRDT

# M-PHY Rx: エラー検出テスト例

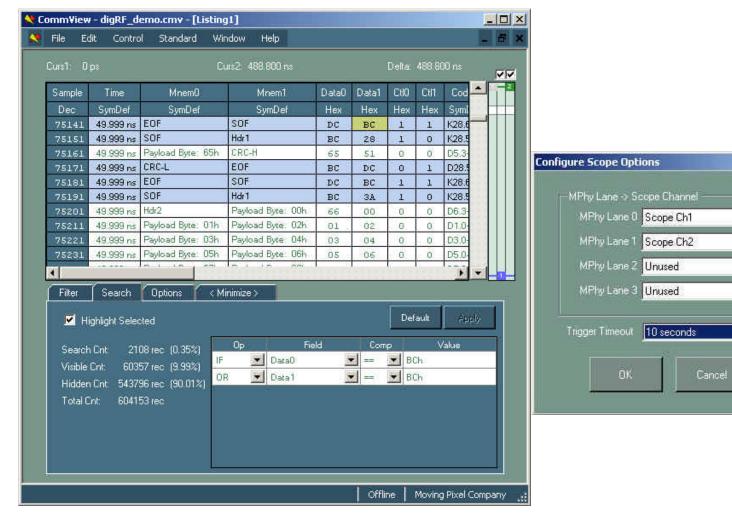

#### M-PHYVIEW

- DigRF v4 プロトコル・デコード

- オシロスコープ上または外部PC上で動作

#### M-PHY Tx &Rx テスト用推奨機器

#### オシロスコープ

- HS-GEAR1: DPO7DSA70604C 型

- HS-GEAR2: DPO7DSA70804C 型

- HS-GEAR3: DPO7DSA72004C 型

#### プローブ

P73xxSMA×2本 またはP73xx型あるいはP75xx型 ×レーン数

#### Rxテスト用信号発生器

- HS-GEAR1 または HS-GEAR2: AWG7082/ AWG7102 以上

– HS-GEAR3: AWG7122C -06

#### ソフトウェア

- Opt.M-PHY(DPOJET Advancedが必要)

- Opt.ERRDT (Scope Error Detector)

- Opt.SR-810B (8b-10b Decode)

- Opt.MPHYVIEW (DigRFv4 Protocol Decode)

- SerialXpress(AWG用カスタム・パターンを作成の場合)

# ありがとうございました。

本テキストの無断複製・転載を禁じますテクトロニクス社 Copyright Tektronix