# TNCSi

# DDR・高速シリアルI/Fを 安定動作するための勘所

- 1. 基板設計を取り巻く諸要因

- 2. 設計・解析事前検証について

- 3. DDR I/F設計·解析事例

- 3-1. DDR3 I/F設計·解析事例

- 3-2. 低コストDDR2 I/Fの設計・解析事例

- 4. 高速シリアルI/F設計・解析事例

- 5. PIについて

2013. 7. 2

株式会社 トッパン NEC サーキット ソリューションズ

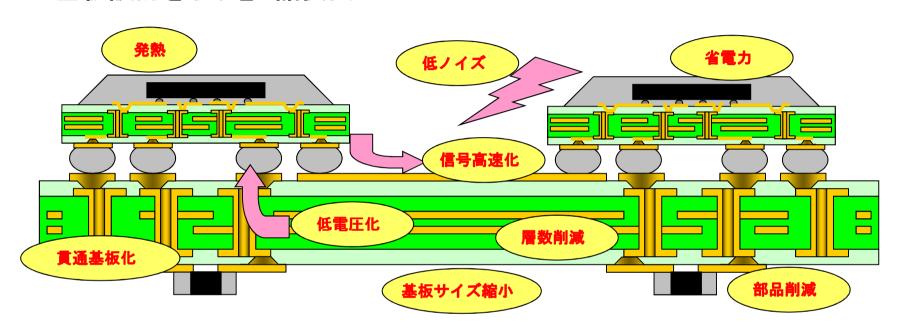

## 1. 基板設計を取り巻く諸要因

#### ▲ 基板設計を取り巻く諸要因

電気特性や様々な要因を考慮しないとシステム開発が できない時代になっている

シミュレーション技術と設計ノウハウを 組み合わせた弊社対応をご紹介

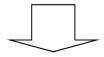

#### ◆ シミュレーション活用による部品点数・基板層数・配線領域の削減

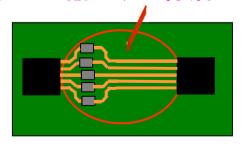

バス配線のスキューを 考慮し、基板配線が クロスしないように 最適なピンアサインを 御提案します

バッファ能力の最適化

配線エリアの縮小、配線層の低減

信号ピンアサインの最適化

抵抗部品点数の削減、配線エリアの縮小

## ▲ 基板設計仕様の検討イメージ

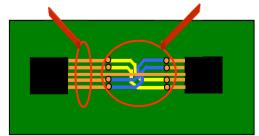

製品仕様によってコントローラの最適なピンアサインは変わってしまう。

⇒ 最適基板実現のためには初期段階での製品仕様の確定を含む 製品設計フロー自体の見直し+協調設計が必要。

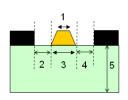

## ▲ 層構成検討 - インピーダンス

特性インピーダンスは電気特性を決める重要な要素です

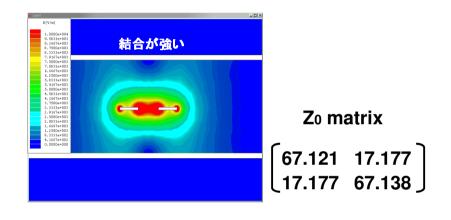

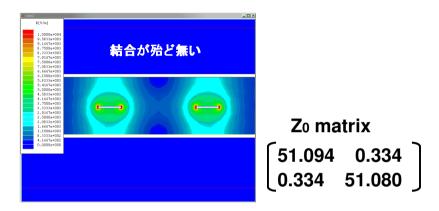

## ▲ 層構成検討 - 差動配線

#### Differential信号ラインの結合の様子

differential impedance  $= 100\Omega$

differential impedance  $= 100\Omega$

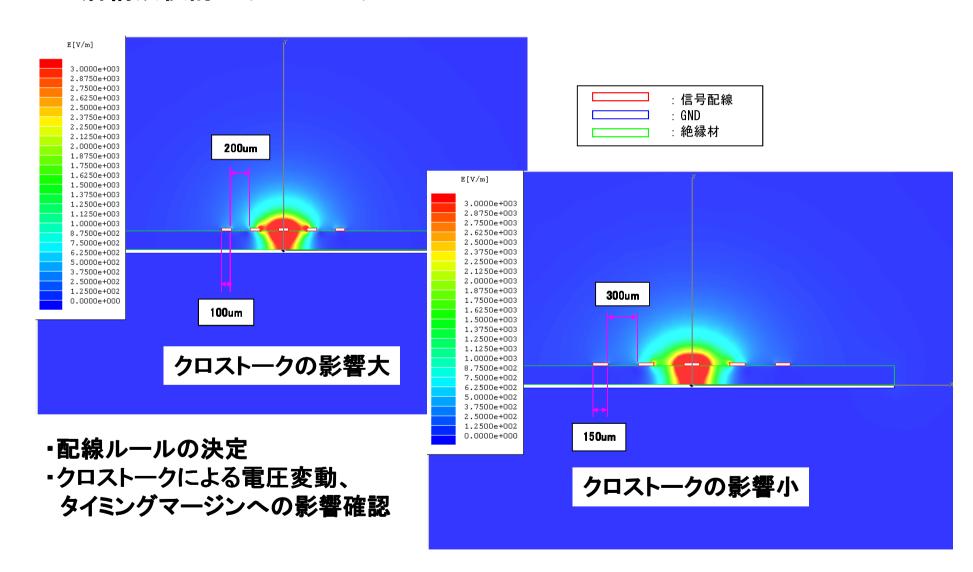

## ♣ 層構成検討 - クロストーク

## 3. DDR I/F設計 • 解析事例

## ♣ DDR/DDR2/DDR3の比較

| 項目                                                     | DDR                                                     | DDR2                                                  | DDR3                                                     |  |  |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| 転送速度                                                   | 200 / 266 / 333 / 400Mbps<br>(100 / 133 / 166 / 200MHz) | 400 / 533 / 667 800Mbps<br>(200 / 266 / 333 ( 400MHz) | 800 / 1066 / 1333 / 1600Mbps<br>(400 / 533 / 667 800MHz) |  |  |  |  |  |  |

| 電源電圧 (VDD/VDDQ)                                        | 2.5 ± 0.2V                                              | 1.8 ± 0/1V                                            | 1.5 ± 0.075V                                             |  |  |  |  |  |  |

| インターフェース                                               | SSTL_2                                                  | SST <mark>/</mark> C_18                               | SSTL_15 /                                                |  |  |  |  |  |  |

| バンク数                                                   | 4                                                       | 4≵たは8                                                 | 8                                                        |  |  |  |  |  |  |

| プリフェッチ                                                 | 2ピット                                                    | 4ビット                                                  | 8ビット                                                     |  |  |  |  |  |  |

| バースト長                                                  | 2/4/8                                                   | 4/8                                                   | 4 (Burst chop) / 8                                       |  |  |  |  |  |  |

| Posted CAS, Additive Latency                           | なし                                                      | あり (AL = 0/1/2/3/4/5)                                 | あり (AL = 0/0 L-1/CL-2)                                   |  |  |  |  |  |  |

| RL,WL                                                  | RL = CL (AL機能なし)                                        | RL = AL + CL                                          | RL = AL + CL                                             |  |  |  |  |  |  |

|                                                        | WL = 1                                                  | WL = RL - 1 = AL + CL - 1                             | WL = AL + CWL                                            |  |  |  |  |  |  |

| ZQ ピン                                                  | なし                                                      | なし                                                    | あり。Z <mark>Q</mark> Calib.用 <sup>注1</sup>                |  |  |  |  |  |  |

| /Reset ピン                                              | なし                                                      | なし                                                    | /あり <sup>注3</sup>                                        |  |  |  |  |  |  |

| DQ Driver impedance (Ron)                              | プログラマブル                                                 | プログラマブル                                               | プログラマブル                                                  |  |  |  |  |  |  |

| DQ Driver calibration                                  | なし                                                      | OCD Calib.利用 <sup>注2</sup>                            | Z/Q Calib.利用 <sup>注1</sup>                               |  |  |  |  |  |  |

| ODT機能                                                  | なし                                                      | あり                                                    | <b>/</b> あり                                              |  |  |  |  |  |  |

| ODT calibration                                        | なし                                                      | なし                                                    | ZQ Calib.利用 <sup>注1</sup>                                |  |  |  |  |  |  |

| Dynamic ODT                                            | なし                                                      | なし                                                    | あり <sup>注4</sup>                                         |  |  |  |  |  |  |

| CLK-DQS間De-skew機能                                      | なし                                                      | なし                                                    | あり (Write leveling、Read leveling) <sup>注5</sup>          |  |  |  |  |  |  |

| パッケージ                                                  | TSOP II                                                 | FBGA                                                  | FBGA                                                     |  |  |  |  |  |  |

| 625ps (tCK/4)  KG+基板パラツキ許容値  メモリ Setup/Hold コントローラバラツキ |                                                         |                                                       |                                                          |  |  |  |  |  |  |

高速化・低電圧化が顕著で、 タイミングマージン、ノイズマージンが減少しており、 設計難易度が上がっています。

※ 資料はエルピーダメモリ様 ユーザーズマニュアル(J1503E10.pdf)から抜粋

## 3. DDR I/F設計 • 解析事例

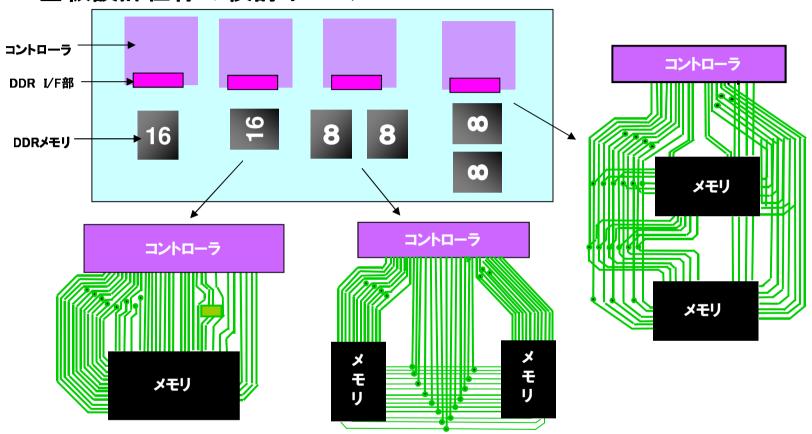

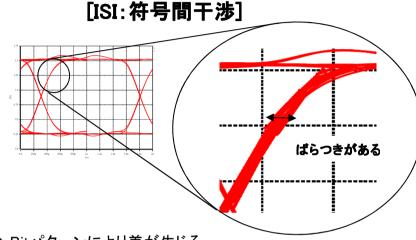

## ▲ ばらつきを考慮した解析

⇒ Bitパターンにより差が生じる

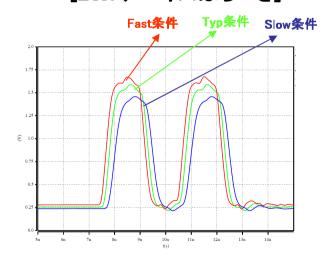

[LSI:デバイスばらつき]

⇒ LSIバラツキ(プロセス, 温度等)により差が生じる

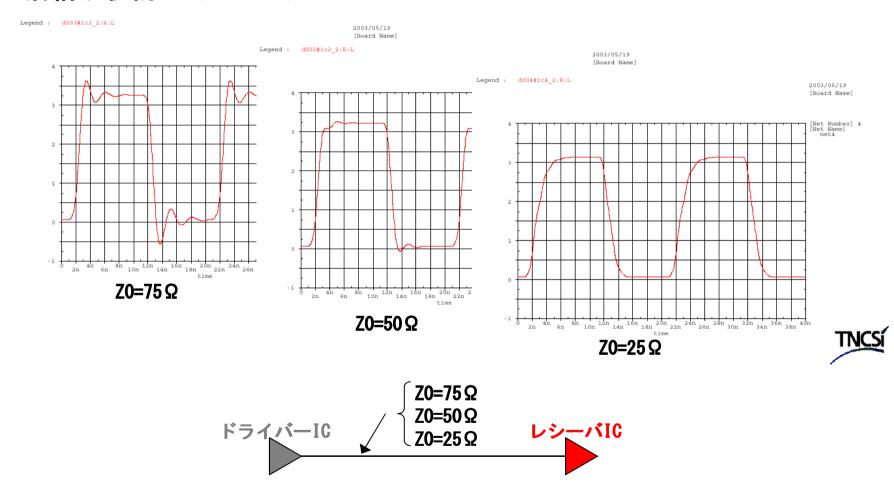

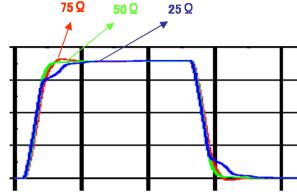

[Z0: インピーダンスばらつき] 75 Q 50 Q 25 Q

⇒ 基板のインピーダンスバラツキにより差が生じる

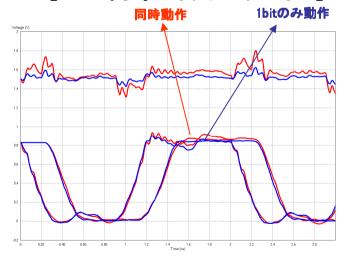

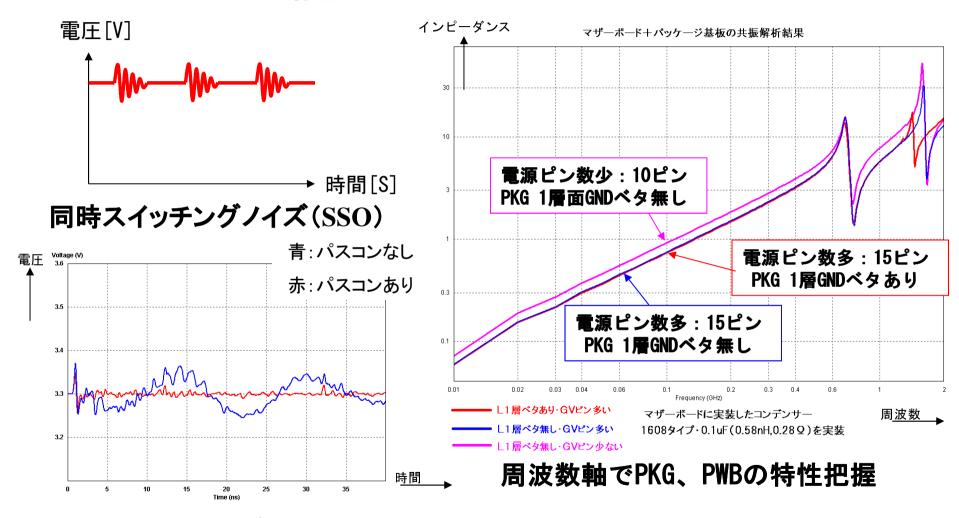

#### [SSO:同時スイッチングノイズ]

⇒ 電源の揺れにより差が生じる

## 3-1. DDR3 I/F設計 • 解析事例

## ♣ DDR3 I/Fの特長

DDR3 DIMM

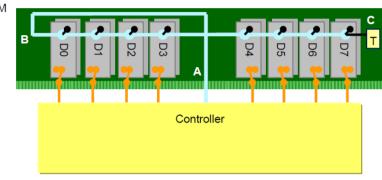

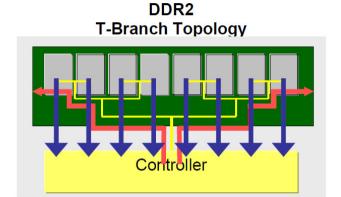

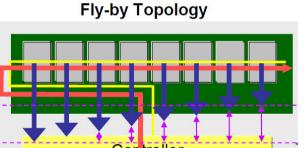

DDR3のDIMMに関して、CLK/ADDの配線方法が 等長(T-Branch)配線から一筆(Fly-by)配線に 変更となっています。

一方, メモリの数が2個の場合は一筆配線を 行うと配線スペースを多く取ってしまうなど 逆効果になるため, 等長配線が多くなっています。

DDR3

## → メモリ個数・ピンアサイン・コントローラ機能によって 最適な配線方法が異なります

※ 資料はエルピーダメモリ様 ユーザーズマニュアル(J1503E10.pdf)から抜粋

## 3-1. DDR3 I/F設計 • 解析事例

## 3-1. DDR3 I/F設計 • 解析事例

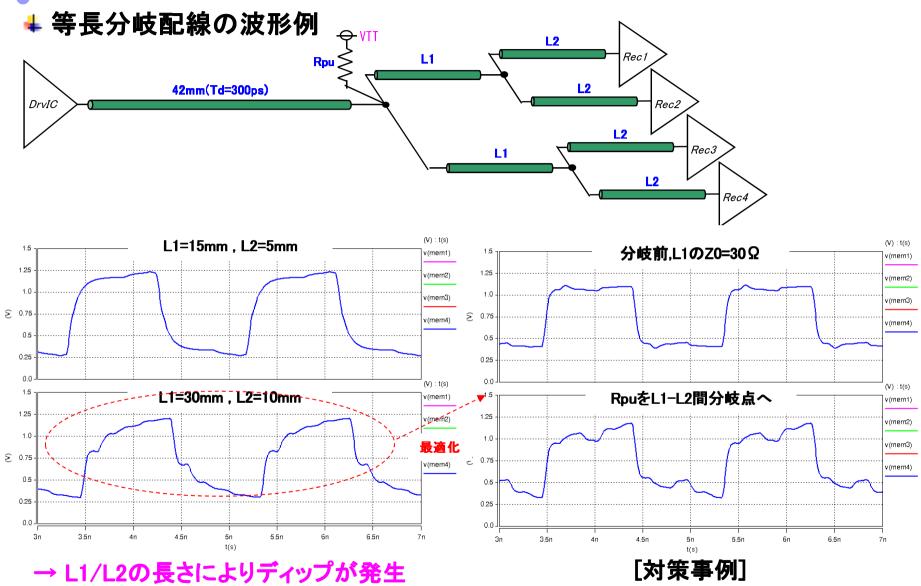

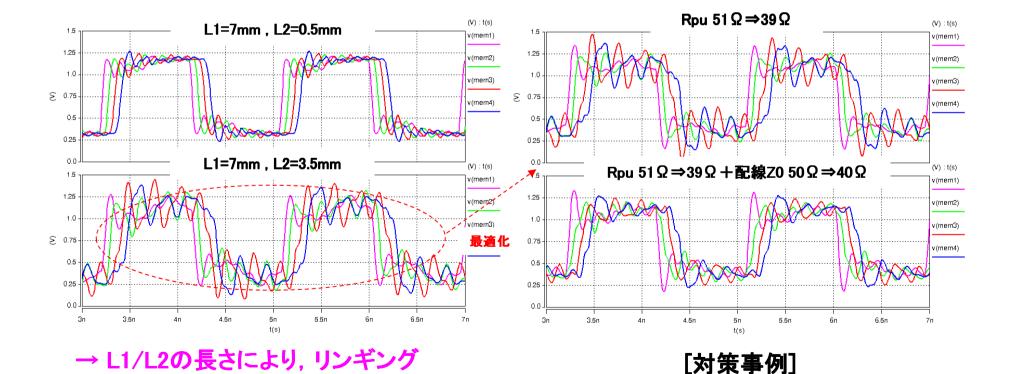

# → 一筆書き配線の波形例 | A2mm(Td=300ps) | L1 | L2 | Rec2 | Rec3 | Rec4 | Rec4

(ディップ)が発生

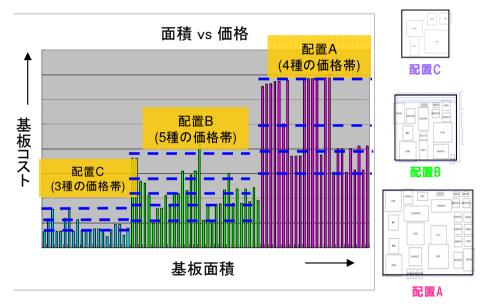

## ▲ 基板コストの決定方法

- ・基板コストは一般的に搭載部品数やパッケージ仕様(ピッチ・ピン数)などによって決定される。

- ⇒ Lowcost基板実現のためにはセット全体の部品数、信号数を考慮する必要がある。

→ AA~CC配置で、それぞれ3~5つの価格帯に大きく分類される。

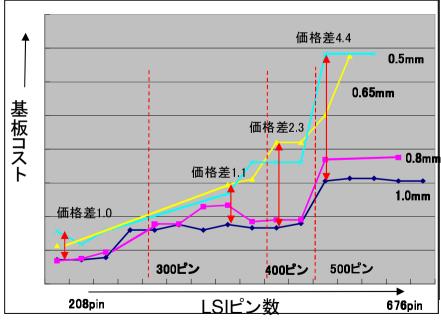

→ 400pinを超えると価格変動が約2倍。500pinを超えると 約4倍となり変動が大きい。

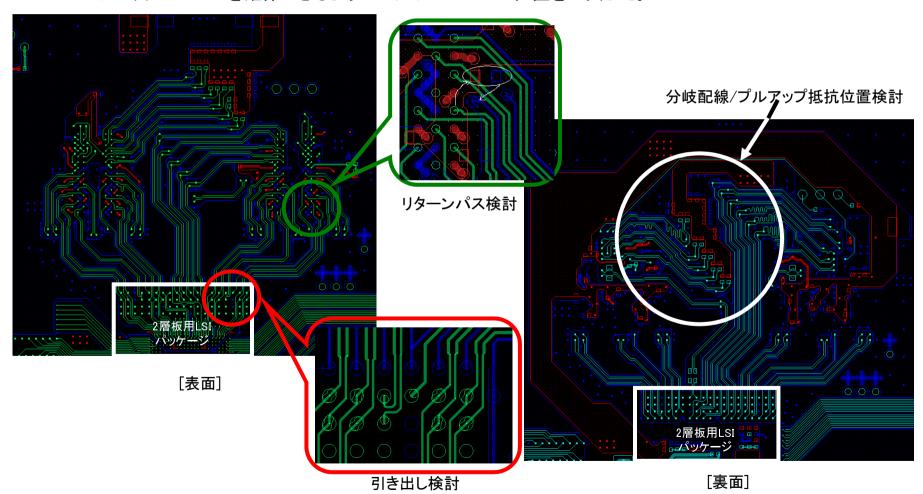

## ▲ 事前検討① - 2層板の実現性

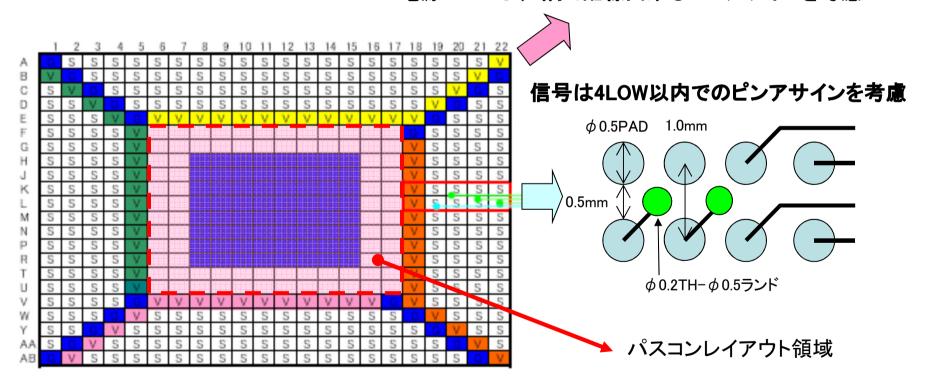

- ・2層板実現のためには以下に示すようなLSI配線の引き出し検討が必要となる。

- ・通常の設計作業とは逆にメモリ側からコントローラ側に向かって配線し、最適なピンアサインを確定する必要がある。

#### 電源/GNDは、4隅で配線出来るピンアサインを考慮

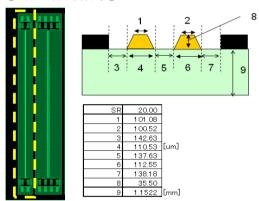

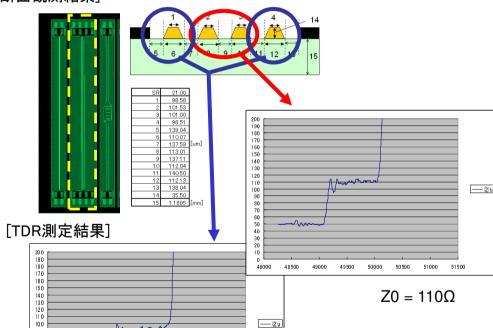

## ▲ 事前検討② - 基板配線(インピーダンス)仕様

- ・両脇のシールドでインピーダンスを取るため、全体的にインピーダンスは高くなっている。

- •S1G1構造は配線領域がNG, S4G1構造はインピーダンスがばらつき, かつ波形変動が大きいため, S2G1構造を採用した。

#### 【S1G1構造】

#### 【S2G1構造】

【S4G1構造】

「イメージ図]

[断面観測結果]

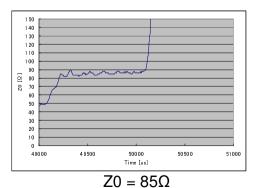

[TDR測定結果]

[断面観測結果]

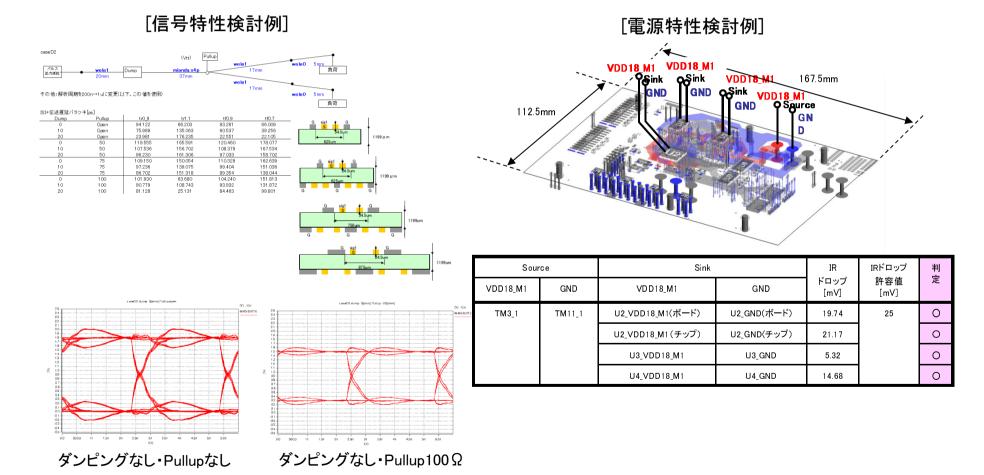

## ▲ 事前検討③ - 電気特性

- ・DCスペックを基準にダンピング抵抗・アドレス/制御信号のプルアップ抵抗が必要であるかなど、 シミュレーションを用いて検討した。

- ・信号特性だけではなく、IRドロップなどの電源特性も実現可能かを検討した。

## ▲ 配置・配線作業

- ・2層板実現のための最適なLSIピンアサインを検討した。

- ・現実的な配線領域内で、かつ分岐のビアが多くならないように配線した。

- ・シールドでリターンパスを確保できるようにビアやパスコンの位置を工夫した。

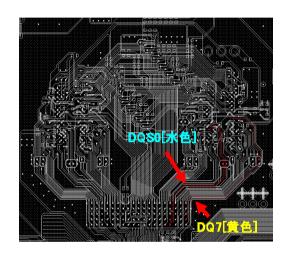

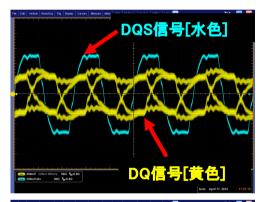

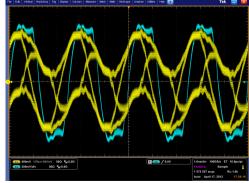

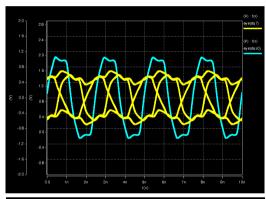

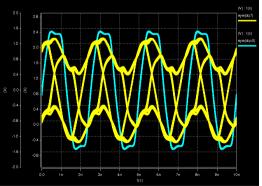

## ♣ 特性評価① - 信号特性

- ・実測にて電気特性(信号/電源)を検証した。

- ・動作条件/動作パターンによっては大きな電圧変動を観測した。

動作周波数: 800Mbps DQ7(Victim): 1bit動作 PRBS

他DQ信号(Aggressor): 31bit動作 PULSE

↓実測 (上:ODTあり,下:ODTなし)

↓シミュレーション (上:ODTあり、下:ODTなし)

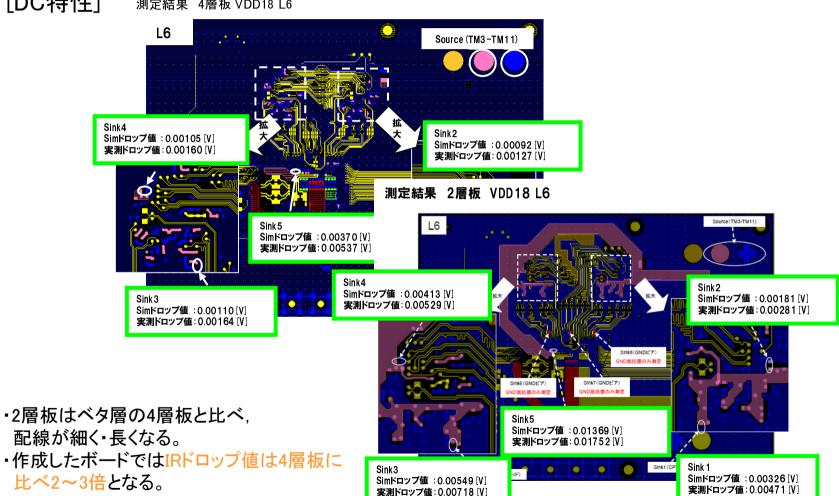

## ▲ 特性評価② - 電源特性

[DC特性]

測定結果 4層板 VDD18 L6

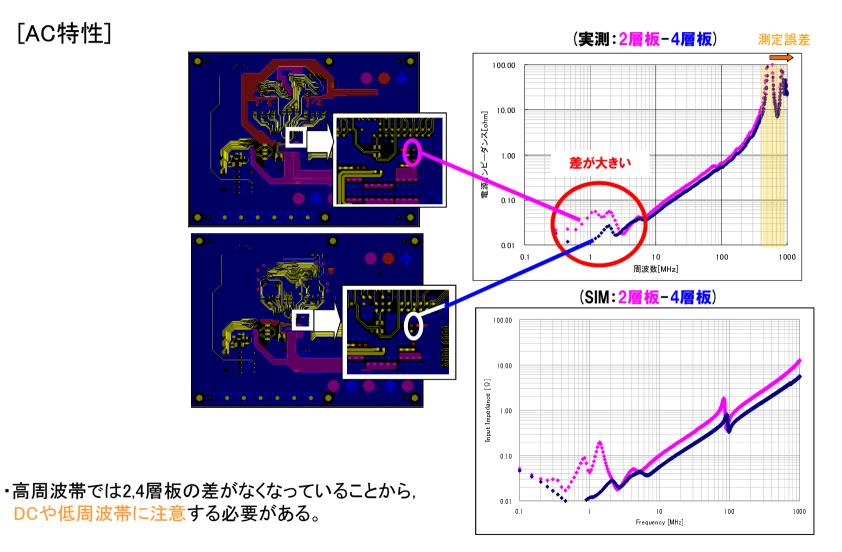

## ▲ 特性評価② - 電源特性

[AC特性]

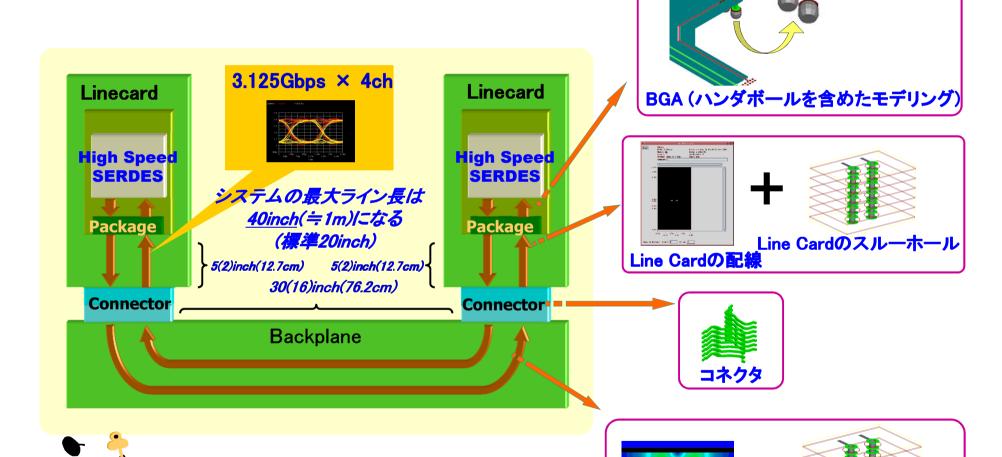

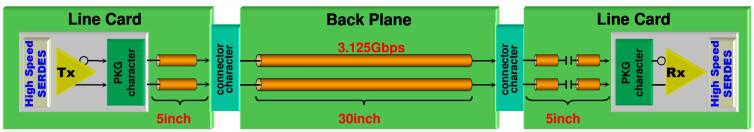

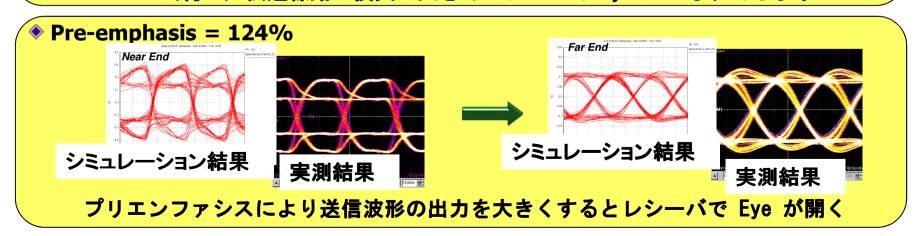

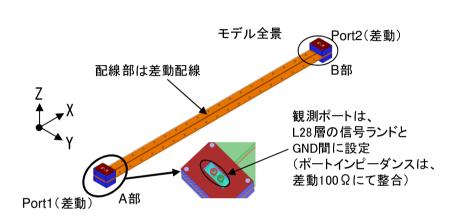

◆ シミュレーション解析事例 (XAUI インターフェース例)

Backplaneの配線

Backplaneのスルーホール

ンポーネントの最適化がキー

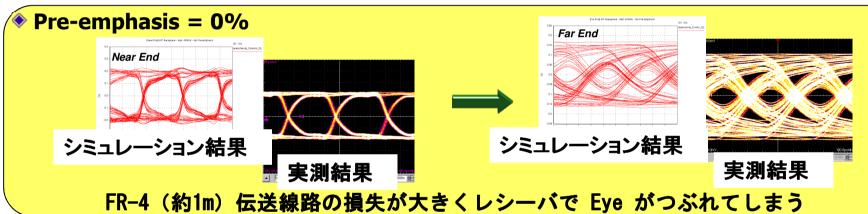

## ♣ シミュレーション結果と実測結果比較

#### 超高多層基板 (高アスペクト比)

特長:最大層数50層 板厚6.5mmまで対応可能

#### 多重積層基板(貼り合せ基板)

特長:最大層数28層 インビーダンスコントロール可能

#### 高多層コンデンサ機能内蔵基板

効果:ノイズ発生低減

コンデンサ実装面積低減

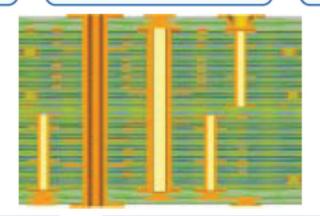

#### バックドリル技術

効果:信号伝播速度の均一化 伝送線路の反射・減衰量低減

#### 高多層ビルドアップ技術(Via on Via、Skip Via)

特長: Filled Via対応可能、2段ビルドアップ対応可能 インビーダンスコントロール対応可能

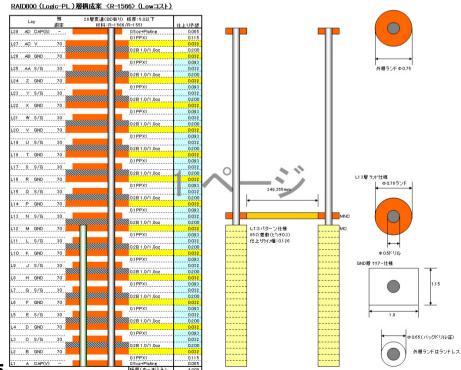

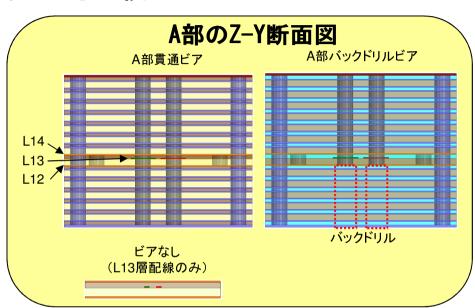

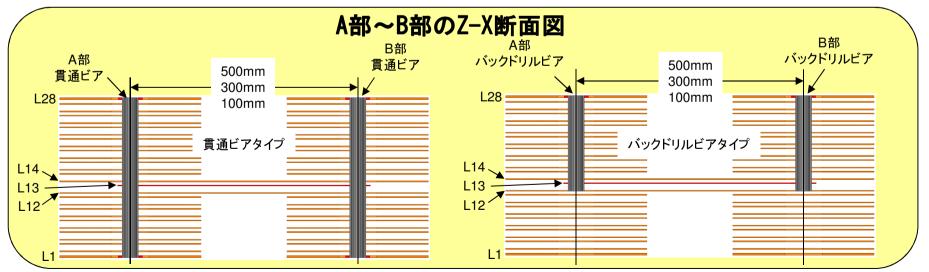

## ♣ スルーホールによるスタブ解析事例

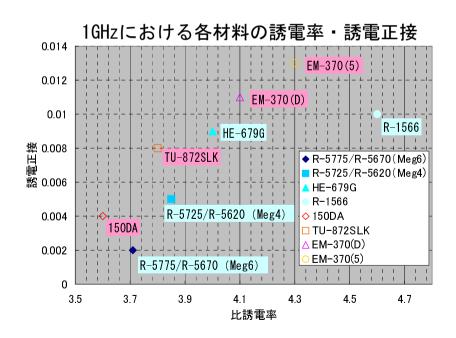

# **↓ ビア構造の3次元電磁界解析(HFSS)による比較**~材料特性と層構成~

| TT平 | 材質 比誘電率 おり 1000 1000 1000 1000 1000 |       |       |       |       |      |       |       | 誘電正接 |       |       |       |       |       |       |       |       |       |       |

|-----|-------------------------------------|-------|-------|-------|-------|------|-------|-------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 項番  | 10 貝                                | 1 MHz | 1 GHz | 2 GHz | 3 GHz | 4GHz | 5 GHz | 6 GHz | 8GHz | 10GHz | 1 MHz | 1 GHz | 2 GHz | 3 GHz | 4GHz  | 5 GHz | 6 GHz | 8 GHz | 10GHz |

|     | R-5775(core)<br>R-5670(pre)         |       | 3.71  | 3.64  |       | 3.63 |       | 3.63  | 3.62 | 3.61  |       | 0.002 | 0.002 |       | 0.003 |       | 0.003 | 0.004 | 0.004 |

| 2   | R-5725(meg4 core)                   |       | 3.84  |       |       | 3.80 |       | 3.79  |      | 3.77  |       | 0.005 |       |       | 0.006 |       | 0.006 |       | 0.007 |

|     | R-5620(meg4 pre)                    |       | 3.86  |       |       | 3.85 |       | 3.84  |      | 3.83  |       | 0.003 |       |       | 0.000 |       | 0.000 |       | 0.007 |

| 3   | HE-679G                             |       | 4.00  |       | 4.00  |      |       |       |      |       |       | 0.009 |       | 0.010 |       |       |       |       |       |

| 4   | R-1566                              | 5.20  | 4.60  |       |       |      |       |       |      |       | 0.010 | 0.010 |       |       |       |       |       |       |       |

| 5   | 150DA                               |       | 3.60  | 3.60  | 3.60  | 3.60 | 3.60  | 3.60  | 3.60 | 3.60  |       | 0.004 | 0.005 | 0.005 | 0.005 | 0.005 | 0.005 | 0.005 | 0.005 |

| 6   | TU-872SLK                           |       | 3.80  |       |       |      | 3.80  |       |      | 3.70  |       | 0.008 |       |       |       | 0.008 |       |       | 0.009 |

| 7   | EM-370(D)                           |       | 4.10  |       |       |      |       |       |      |       |       | 0.011 |       |       |       |       |       |       |       |

| 8   | EM-370(5)                           | 4.50  | 4.30  |       |       |      |       |       |      |       | 0.009 | 0.013 |       |       |       |       |       |       |       |

▲ ビア構造の3次元電磁界解析(HFSS)による比較

~配線構造~

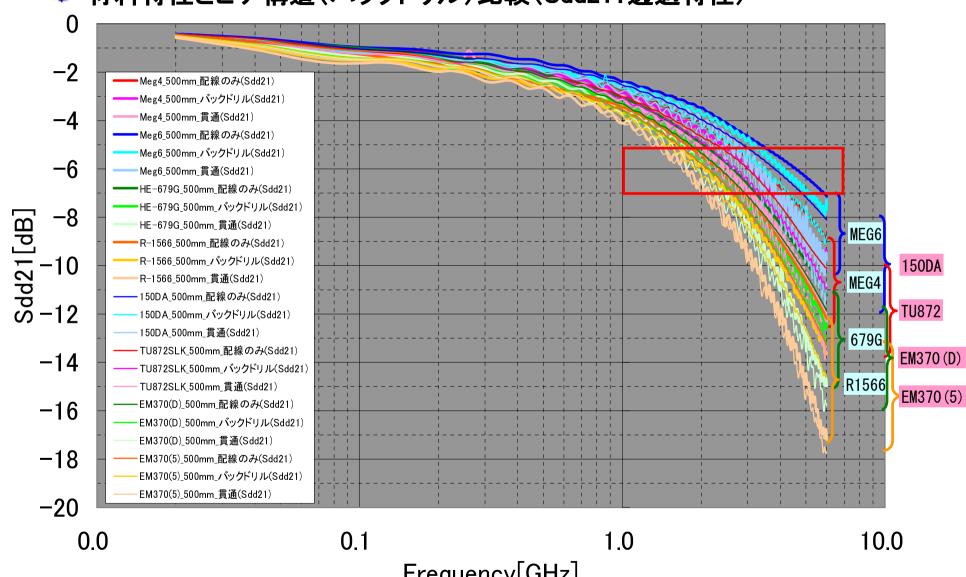

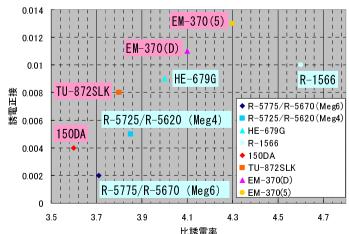

## ⑧ 材料特性とビア構造(バックドリル)比較: Sdd21(通過特性)

国内材料 500mm配線長 Sdd21到達時の周波数[GHz]

|       | R-577 | R-5775/R-5670(Meg6) |      |      | 25/R-5620(M | leg4) |      | HE-679G  |      | R-1566 |        |          |  |

|-------|-------|---------------------|------|------|-------------|-------|------|----------|------|--------|--------|----------|--|

| Sdd21 | 配線のみ  | バックドリル              | 貫通   | 配線のみ | バックドリル      | 貫通    | 配線のみ | バックドリル   | 黄通   | 配線のみ   | バックドリル | 貫通<br>TH |  |

| -6dB  | 4.58  | 3.96                | 3 08 | 3.36 | 3.02        | 2.38  | 2.64 | 2.28     | 1,98 | 2.31   | 2.01   | 1.66     |  |

|       |       |                     | ·    | 司等の結 | <br>果       |       | 等の結  | <b>果</b> | 事の結  | 果      | •      |          |  |

海外材料 500mm配線長 Sdd21到達時の周波数[GHz]

TNCSi Confidential and Proprietary

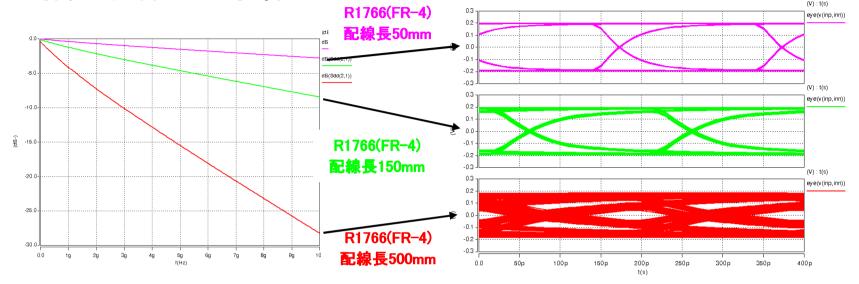

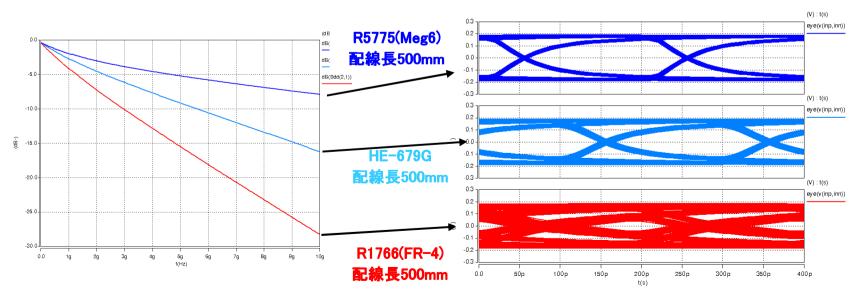

## ▲ 配線長・材料による影響

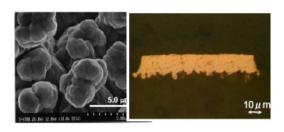

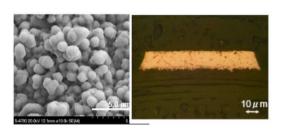

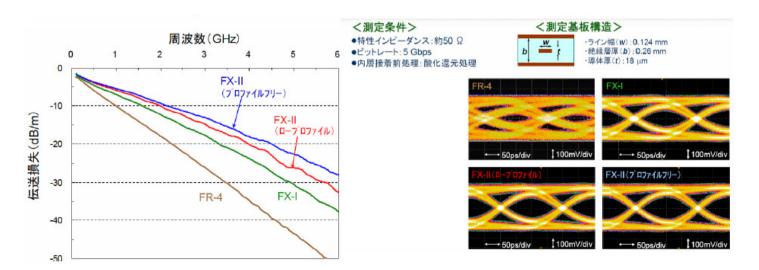

## ♣ 材料•工法

特に高周波帯では表皮効果の関係から、銅箔部の仕上がりが重要となります。

一般銅箔 (Rz: 6~8um)

ロープロファイル銅箔 (Rz: 3~4um)

プロファイルフリー銅箔 (Rz: 0.5~1.5um)

TNCSi Confidential and Proprietary

## 4. 高速シリアル I/F設計・解析事例

31

## ♣ スルーホールによるスタブ解析事例

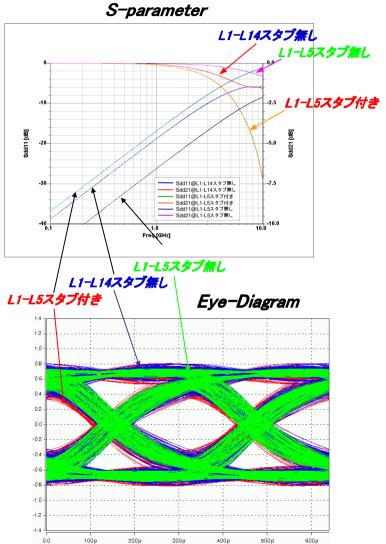

サ 伝送線路(スルーホール)の解析 (insertion loss & return loss ) 信号の流れ L1~L5 スタフ L14 L1-L5スタブ付き 信号の流れ L1~L14 L1-L14スタブ無し 信号の流れ L1~L5 特性が良い! バックドリルエ法を想定 L1-L5スタブ無し

# S-parameter L1-L14スタブ無し L1-L5スタブ無し -25 L1-L5スタブ付き Sdd11@L1-L14スタブ無し Sdd11@L1-L5スタブ付き L1-L5スタブ無し L1-L14スタブ無し L1-L5スタブ付き Evediagram

## 4. まとめ

## DDR・高速シリアルI/Fを安定動作させるためには

- ・SI/PI/EMCの相互結合を考慮したシステムの電気特性の最適化

- 開発初期段階からのチップ/パッケージ/基板の協調設計体制

- ・電気特性と基板や製品全体の諸要因(コスト)とのトレードオフの判断

- •トレードオフ判断のための設計・シミュレーション技術

といった製品の全体最適化・協力体制が必要となります。

トッパンNECサーキットソリューションズでは日々、様々な基板に関する問題に 取り組み、お客様のお困りごとを解決するソリューションをご提供しています。

## 5. PIについて

## ▲ 電源への要求

低電圧化

ノイズ対策: 出力電圧/電流の安定化

高速負荷応答

大電流化

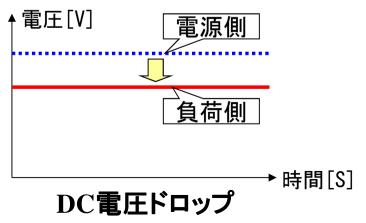

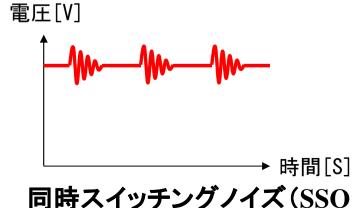

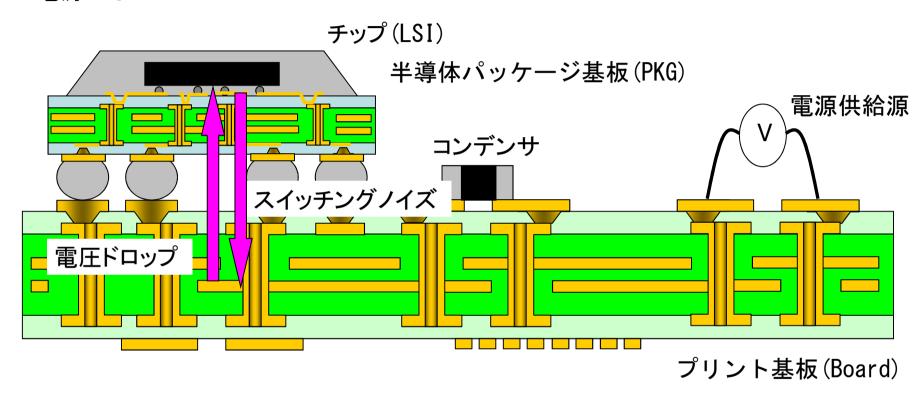

▲ 電源で問題となるノイズ現象

負荷側で電圧が降下してしまう

## 電圧が安定しない

## 5. PIについて

## ▲ 電源ノイズについて

| 電源ノイズ     | ノイズ現象              | 協調設計による対策                                |

|-----------|--------------------|------------------------------------------|

| DC電圧ドロップ  | チップ端子で電圧が降下        | 電源経路の最適化(DC的に低インピーダンスにする)                |

| スイッチングノイズ | チップの動作にあわせて電圧変動が発生 | キャパシタンスの最適化による電圧変動の低減 (電源インピーダンスの低減と安定化) |

## 5-1. DC電圧ドロップ

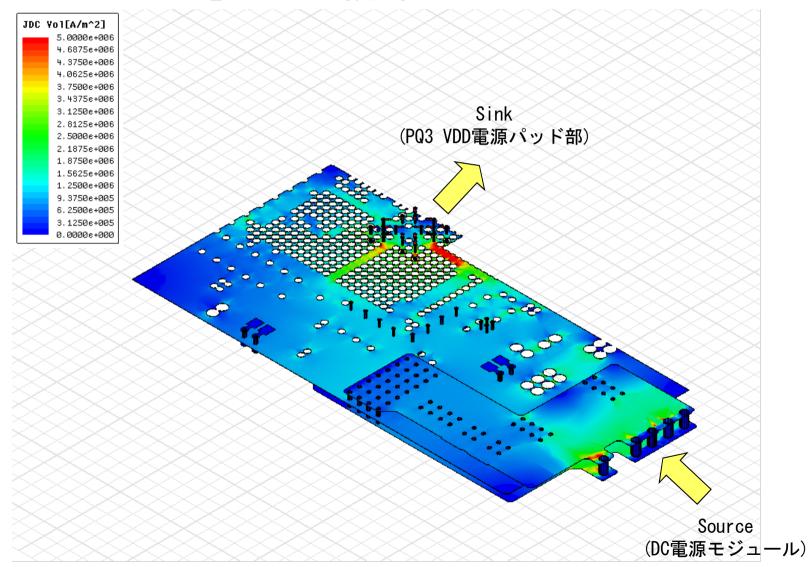

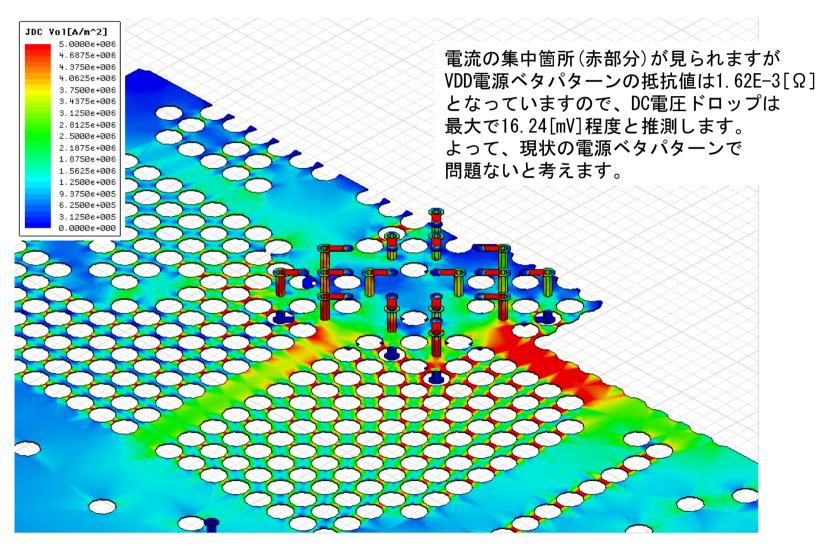

## ♣ フルグリッドBGAのDC電圧ドロップ解析事例

## 5-1. DC電圧ドロップ

## **♣** フルグリッドBGAのDC電圧ドロップ解析事例

## 5-1. DC電圧ドロップ

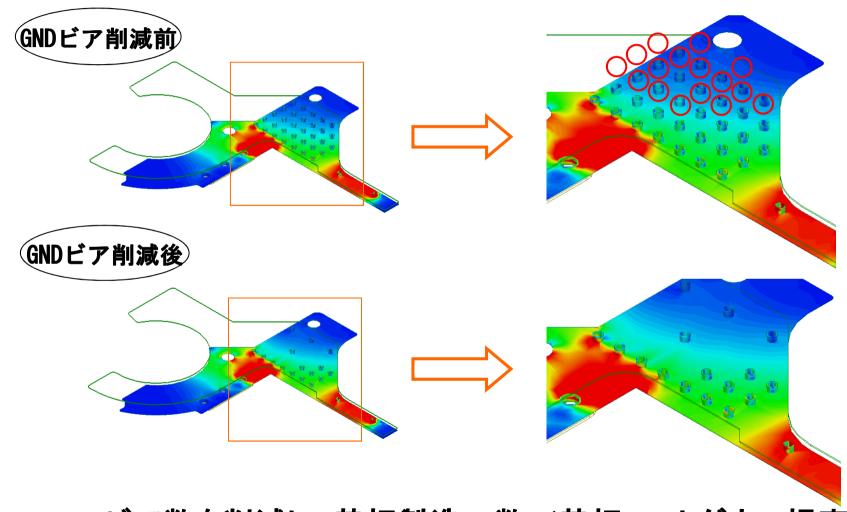

## **♣ DC電流分布を考慮したGNDビアの最適化事例**

GNDビア数を削減し、基板製造工数/基板コストダウン提案

## 5-2. AC電源ノイズの解析

## ▲ スイッチングノイズの解析

時間軸で電源ノイズの絶対量として解析

## 5-2. AC電源ノイズの解析

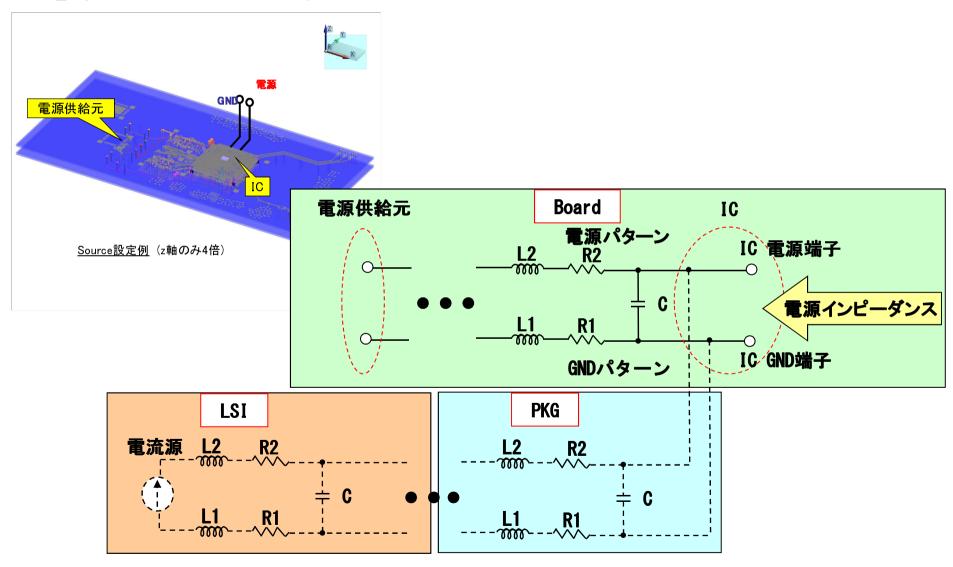

## ▲ 電源インピーダンスの考え方

## 5-2. AC電源ノイズの解析

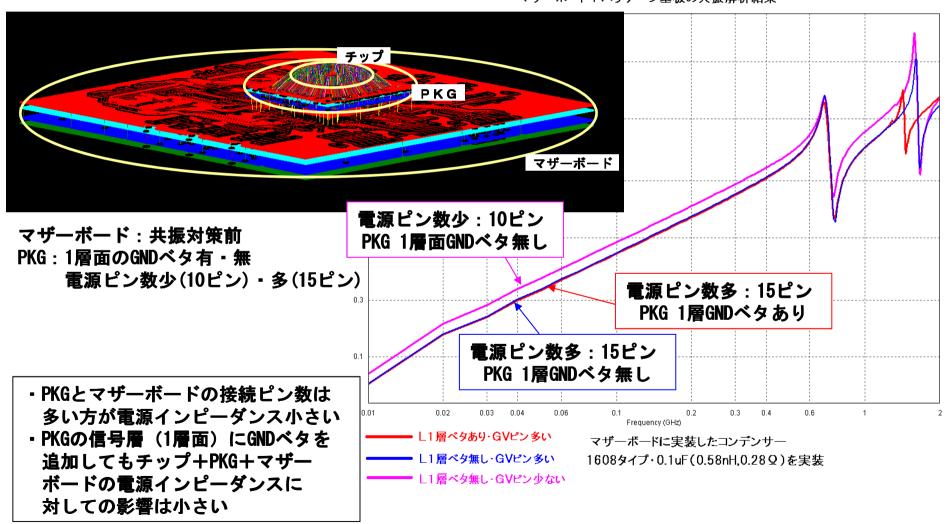

## **▲ 電源インピーダンス解析事例(チップ+PKG+ボードの共振)**

マザーボード+パッケージ基板の共振解析結果

## 5. PIについて

## ♣ まとめ

- 1. DC電圧ドロップ対策

- ・導体幅、導体厚、ビア数、ビア形状、ビア位置の最適化を実施する。

- ・ビアによるクリアランスの発生に注意する。

- ・ビア数が多くなりすぎると、基板製造の工数、コストUP要因になる。

- 2. 同時スイッチングノイズ対策

- ・電源の電圧変動を小さくすることで信号波形の改善が期待できる。

- ・スイッチングノイズは、LSIがノイズ源となって、基板上を伝播し、 特に、基板上の電源インピーダンスに共振、反共振点があると変動が大きくなる。

- ・LSIのノイズ源は、動作周波数が速くなり、立ち上がり時間が早くなると 電流値が大きくなる。また、同時動作するビット数が多くなると電流値が大きくなる。

- 3. 電源インピーダンスの最適化

- ・電源インピーダンスを検討する場合には、チップ、PKGの等価回路も検討する。

- ・容量の異なるコンデンサによる反共振、プレーン固有の共振に注意する。

- ・できるだけインダクタンスを小さくするように、LSIの電源端子そばにコンデンサを配置する。

## 今後とも

トッパンNECサーキットソリューションズを お引き立て頂けます様 よろしくお願い申し上げます。