### **Technical Reference**

# **Tektronix**

DPOJET Opt. PCE, PCE3, PCE4

PCI Express® Measurements & Setup Library

Methods of Implementation (MOI) for Verification, Debug and Characterization

**Version 4.6**

077-0267-00

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX, TEK and RT-Eye are registered trademarks of Tektronix, Inc.

Copyright © 2016, PCI-SIG, All Rights Reserved for Figures 47, 49, 51, 52, 54, 56, 57, 59, 61, 62, 64, 66, 67, 69, 71, 72, 74, 75, 76, 77, 79.

Copyright © 2016, PCI-SIG, All Rights Reserved for Table 7d,7e,7f,7g,7h,7i

### Contacting Tektronix

Tektronix, Inc. 14200 SW Karl Braun Drive or P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

| Revision History |            |                                                |                                                                                                                                                                                                                                                    |  |  |

|------------------|------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Version          | Issue Date | Pages                                          | Nature of Change                                                                                                                                                                                                                                   |  |  |

|                  |            |                                                |                                                                                                                                                                                                                                                    |  |  |

| 1.0              | Dec-2008   | All                                            | First released MOI for PCI Express                                                                                                                                                                                                                 |  |  |

| 2.0              | Aug-2009   | 3,8-<br>9,12,18,<br>34-38,                     | MXM test points added in setup library.<br>Updated Algorithms for new measurements.                                                                                                                                                                |  |  |

| 3.0              | March-2012 |                                                | Added PCI Express 3.0 MOI                                                                                                                                                                                                                          |  |  |

| 4.0              | March-2013 |                                                | Updated to support new SDLA                                                                                                                                                                                                                        |  |  |

| 4.1              | May-2013   |                                                | Added R11_RefClk setup details                                                                                                                                                                                                                     |  |  |

| 4.2              | July-2013  |                                                | Added Rev. 2.0 & 3.0 Ref Clock Setup details, VBoost measurement, Gen2 Cable support.                                                                                                                                                              |  |  |

| 4.3              | Oct-2014   | 36, 10-<br>32, 3-6,<br>44, 56,<br>58-61,<br>66 | Updated probing configurations for Rev3.0 CEM Specification System Board in the - Table 16 and DPOJET Settings is modified for Unit interval measurement, updated table 2 and 3 according to Base spec 3.0, PCIe AC Common Mode setup files added. |  |  |

| 4.4              | Apr-2015   | 4,5, 33,<br>35, 40,<br>42                      | Added PCI Express 4.0 Base Spec<br>Measurements and limits, Setup files(table<br>16), Required Equipment, Horizontal<br>setup(4.3.1), Math setup(4.3.3)                                                                                            |  |  |

| 4.5              | Jun-2015   | All                                            | Incorporated review comments                                                                                                                                                                                                                       |  |  |

| 4.6              | Mar-2016   | 78-102,                                        | Added Ref Clock Measurement in MOI                                                                                                                                                                                                                 |  |  |

|                  |            | 118                                            | Added Compliance Pattern description as<br>Appendix d                                                                                                                                                                                              |  |  |

### **Contents**

| 1 | I    | ntroduc | ction to the DPOJET PCI Express Setup Library            | 1  |

|---|------|---------|----------------------------------------------------------|----|

| 2 | P    | CI Exp  | ress Specifications                                      | 3  |

|   | 2.1  | -       | ferential Transmitter (TX) Output Specifications         |    |

|   | 2.2  | Dif     | ferential Transmitter (TX) Compliance Eye Diagrams       | 6  |

|   | 2.3  |         | ferential Receiver (RX) Input Specifications             |    |

|   | 2.4  |         | d-In Card Transmitter Path Compliance Specifications     |    |

|   | 2.5  | Sys     | tem Board Transmitter Path Specifications                | 14 |

|   | 2.6  | Ref     | ference Clock Specification                              | 19 |

|   | 2.7  | MX      | KM System Board Specifications                           | 23 |

|   | 2.8  | MX      | XM System Board Compliance Eye Diagrams                  | 24 |

|   | 2.9  | PC      | I ExpressModule <sup>TM</sup> Specifications             | 25 |

|   | 2.10 | MX      | XM ExpressModule Specifications                          | 27 |

|   | 2.11 | Exp     | pressModule System Board Transmitter Path Specifications | 28 |

|   | 2.12 | PC      | I Express External Cabling Specifications                | 29 |

|   | 2.13 | Ext     | ternal Cabling Receiver Path Specifications              | 30 |

|   | 2.14 | PC      | MCIA ExpressCard <sup>TM</sup> Specifications            | 31 |

| 3 | P    | CI Exp  | ress Library Contents                                    | 34 |

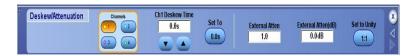

|   | 3.1  | Ret     | taining Deskew                                           | 36 |

| 4 | P    | reparin | ng to Take Measurements                                  | 38 |

|   | 4.1  | Rec     | quired Equipment                                         | 38 |

|   | 4.2  | Pro     | obing Options for Transmitter Testing                    | 38 |

|   |      | 4.2.1   | SMA Input Connection                                     |    |

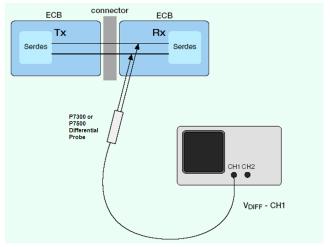

|   |      | 4.2.2   | ECB pad connection                                       | 39 |

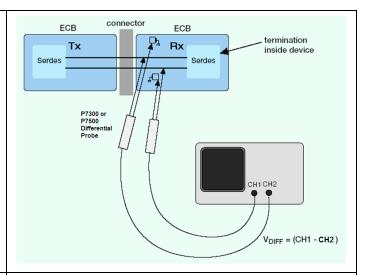

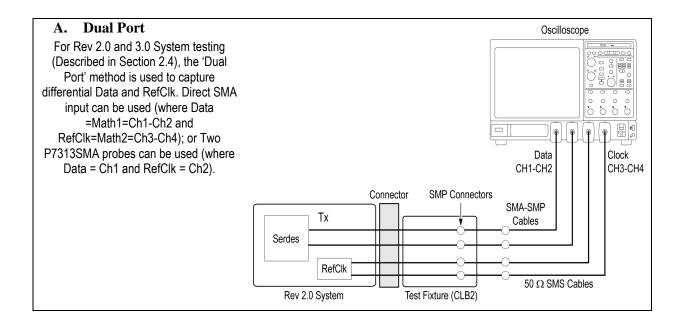

|   |      | 4.2.3   | Dual Port Connection                                     | 41 |

|   | 4.3  | SX      | Scope Support                                            | 42 |

|   | 4.4  | Rui     | nning the Test                                           | 42 |

|   |      | 4.4.1   | Horizontal Setup                                         | 43 |

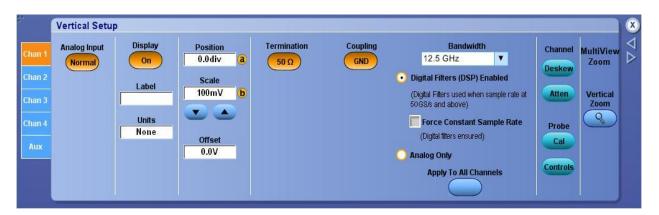

|   |      | 4.4.2   | Vertical Setup:                                          | 43 |

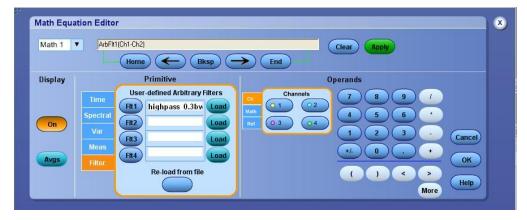

|   |      | 4.4.3   | Math Setup:                                              | 44 |

| 5 | P    | aramet  | er Definitions and Method of Implementation              | 47 |

|   | 5.1  | UI      | (Unit Interval) MOI                                      | 47 |

|   | 5.2  | TX      | Differential Pk-Pk Output Voltage MOI                    | 48 |

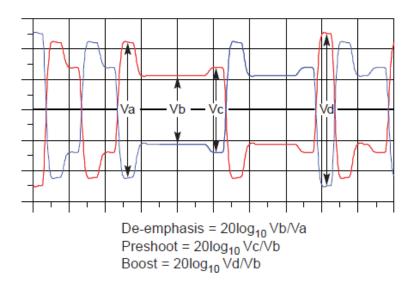

|   | 5.3  | TX      | De-Emphasis Ratio                                        | 48 |

|   |      |         |                                                          |    |

6 7

8

| 5.4  | TX Minimum Pulse Width MOI                                                | . 50 |

|------|---------------------------------------------------------------------------|------|

| 5.5  | TX Rise/Fall Time Mismatch MOI                                            | 51   |

| 5.6  | Minimum TX Eye Width MOI                                                  | 51   |

| 5.7  | TX Median-to-Max Jitter MOI                                               | 53   |

| 5.8  | VRX Max-Min Ratio (Voltage) MOI                                           | 54   |

| 5.9  | TX SSC Frequency Deviation MOI                                            | . 55 |

| 5.10 | TX Rise Time MOI                                                          | 56   |

| 5.11 | TX Fall Time MOI                                                          | 57   |

| 5.12 | Data Dependent Jitter MOI(T <sub>TX-DDJ</sub> )                           | 58   |

| 5.13 | Uncorrelated Total Jitter (T <sub>TX-UTJ</sub> )                          | 60   |

| 5.14 | Uncorrelated Deterministic Jitter(T <sub>TX-UDJDD</sub> )                 | 61   |

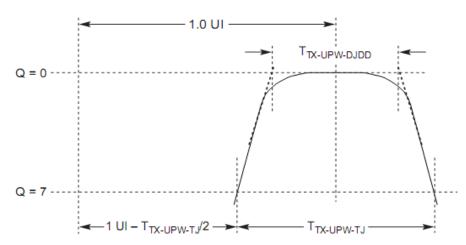

| 5.15 | Uncorrelated Total Pulse Width Jitter (T <sub>TX-UPW-TJ</sub> )           | 63   |

| 5.16 | Uncorrelated Deterministic Pulse Width Jitter (T <sub>TX-UPW-DJDD</sub> ) | 64   |

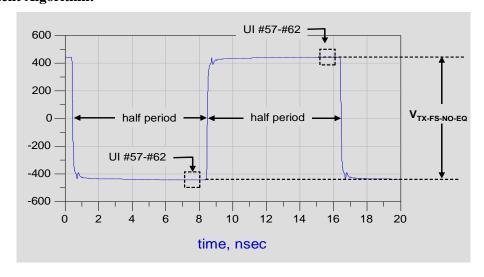

| 5.17 | Voltage swing with No Equalizer (V <sub>TX-NO-EQ</sub> )                  | 66   |

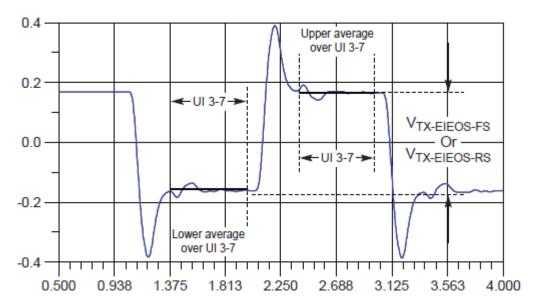

| 5.18 | P-P voltage swing in EIEOS sequence (V <sub>TX-EIEOS</sub> )              | 67   |

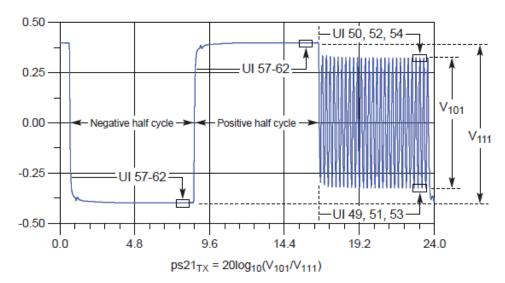

| 5.19 | Effective Tx package Loss ratio(Ps21 <sub>TX</sub> )                      | 68   |

| 5.20 | Maximum Boost Ratio(V-Tx-Boost)                                           | 69   |

| 5.21 | Pk-Pk RefClk Jitter for Common RefClk architecture, Gen1                  | 70   |

| 5.22 | RMS RefClk HF Jitter for Common RefClk architecture, Gen2                 | 73   |

| 5.23 | RMS RefClk LF Jitter for Common RefClk architecture, Gen2                 | 76   |

| 5.24 | RMS RefClk HF Jitter for Data Clocked Rx RefClk architecture, Gen2        | 79   |

| 5.25 | RMS RefClk LF Jitter for Data Clocked Rx RefClk architecture, Gen2        | 82   |

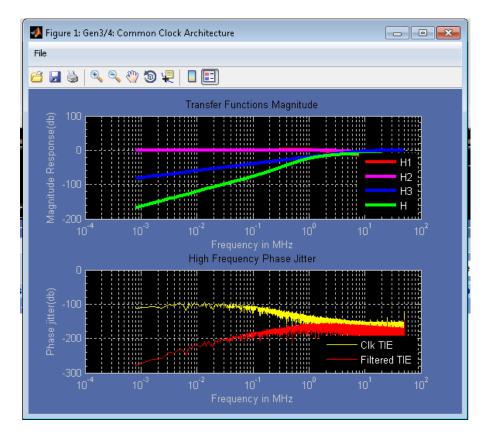

| 5.26 | RMS RefClk Jitter for Common RefClk architecture, Gen3                    | 85   |

| 5.27 | RMS RefClk Worst Case Jitter for Common RefClk architecture, Gen3         | 87   |

| 5.28 | RMS RefClk Jitter for Data Clocked Rx architecture, Gen3                  | 89   |

| 5.29 | RMS RefClk Worst Case Jitter for Data Clocked Rx architecture, Gen3       | 91   |

| 5.30 | RMS RefClk Jitter for Separate RefClk with Independent SSC Gen3/4         | 92   |

| 5.31 | RMS RefClk Jitter for Separate RefClk with no SSC Gen3/4                  | 94   |

| 5.32 | RMS RefClk Jitter for Separate RefClk with Independent SSC Gen2           | . 95 |

| 5.33 | RMS RefClk Jitter for Separate RefClk with no SSC Gen2                    | 98   |

| Appe | endix A                                                                   | .98  |

| Appo | endix B1                                                                  | 16   |

| Appe | endix C1                                                                  | 22   |

| 8.1  | Updated Limit Files                                                       |      |

|      |                                                                           |      |

|       | 8.1 New Limit Files and Limits                             | 123 |

|-------|------------------------------------------------------------|-----|

| 9     | Appendix D: Compliance Pattern                             | 125 |

| 10    | Appendix D: AC Common Mode Filter Design                   | 126 |

| Figui | re Table:                                                  |     |

| Figui | re 1: PCI Express Transmitter Eye Mask Definitions         | 6   |

| Figui | re 2: Receiver input eye mask                              | 8   |

| Figui | re 3: Add-in card compliance eye masks                     | 11  |

| Figui | re 4: Setup File Selection                                 | 11  |

| Figui | re 5: Serial Data Link Analysis window                     | 12  |

| Figui | re 6: Setup file selection in SDLA                         | 12  |

| Figui | re 7: DPOJET Measurement Results                           | 13  |

| Figui | re 8: System Board Compliance Eye Masks                    | 16  |

| Figui | re 9: Setup File Selection                                 | 16  |

| Figui | re 10: Serial Data Link Analysis window                    | 17  |

| Figui | re 11: Setup file selection in SDLA                        | 17  |

| Figui | re 12: DPOJET Measurement Results                          | 18  |

| Figui | re 13: Filter settings in Math menu                        | 19  |

| Figui | re 14: Selecting CTLE Filter                               | 19  |

| Figui | re 13: MXM System Board Compliance Eye Masks               | 24  |

| Figui | re 14: ExpressModule add-in card compliance eye masks      | 26  |

| Figui | re 15: MXM System Board Compliance Eye Masks               | 28  |

| Figui | re 16: ExpressModule system board compliance eye masks     | 29  |

| Figui | re 17: Cable (transmitter side) compliance eye masks       | 30  |

| Figui | re 18: Cable (receiver side) compliance eye masks          | 31  |

| Figui | re 19: ExpressCard Module Transmitter compliance eye masks | 32  |

| Figui | re 20: ExpressCard Host System compliance eye masks        | 33  |

| Figui | re 21: Retaining deskew setting unchanged                  | 37  |

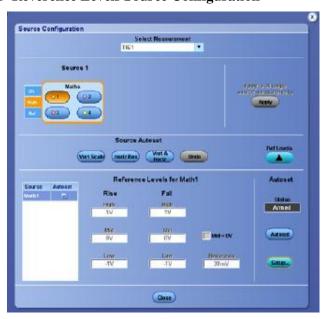

| Figui | re 22: Source Configuration window                         | 42  |

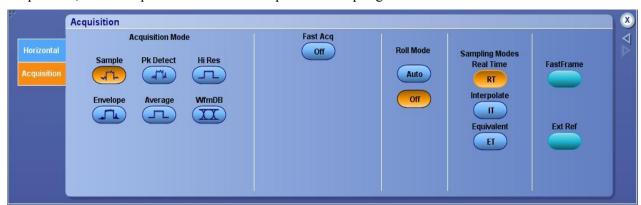

| Figui | re 24: Acquisition setup                                   | 43  |

| Figui | re 25: Vertical Setup                                      | 44  |

| Figui | re 26: Channel Deskew                                      | 44  |

| Figui | re 27: Math Setup                                          | 44  |

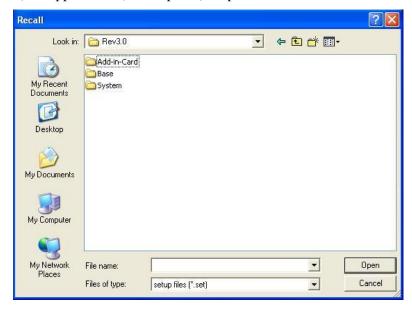

| Figui | re 28: Recall the desired file from the Setup Library      | 45  |

| Figure 29: Setting DPOJET measurements                                  | 45 |

|-------------------------------------------------------------------------|----|

| Figure 30: Displaying results in DPOJET panel.                          | 46 |

| Figure 31: Configure Panel                                              | 52 |

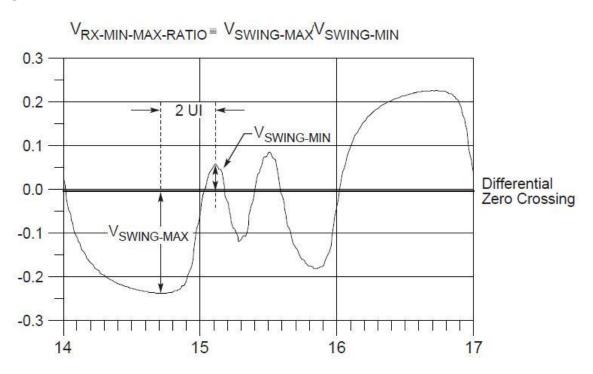

| Figure 32: Signal at Receiver Reference Load Showing Min/Max Swing      | 54 |

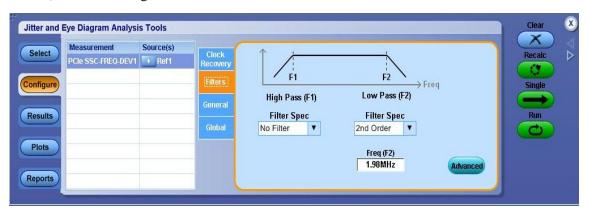

| Figure 33: Filter for SSC Frequency Deviation measurement               | 56 |

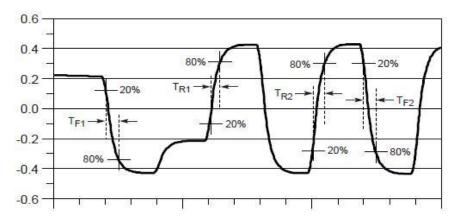

| Figure 34. Rise Time Definition                                         | 57 |

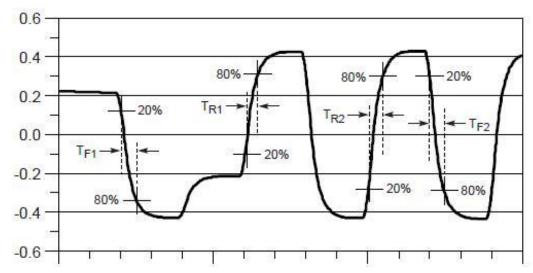

| Figure 35. Fall Time Definition                                         | 58 |

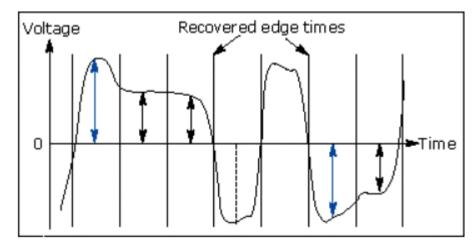

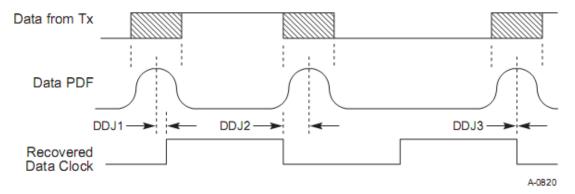

| Figure 36: Relation between Data Edge PDF and Recovered Data Clock      | 59 |

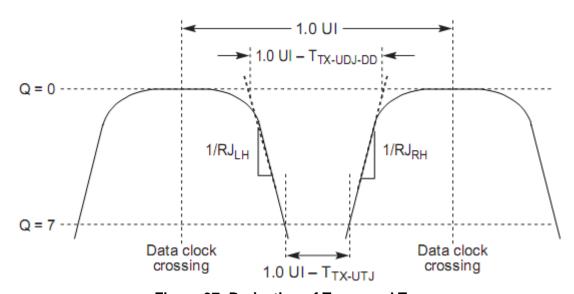

| Figure 37: Derivation of T <sub>TX-UTJ</sub> and T <sub>TX-UDJDD</sub>  | 60 |

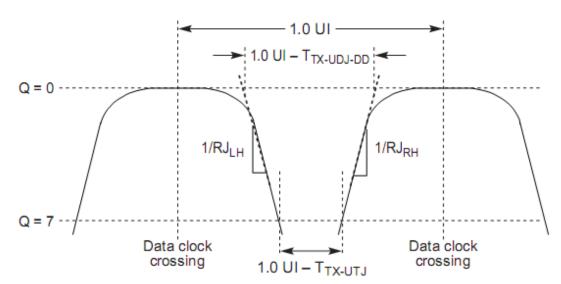

| Figure 38: Derivation of TTX-UDJDD                                      | 62 |

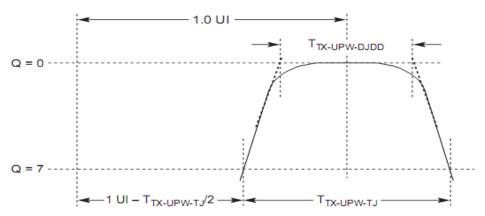

| Figure 39: Definition of TTX-UPW-TJ                                     | 64 |

| Figure 40: Definition of TTX-UPW-DJDD                                   | 65 |

| Figure 41: No Equalization PP Tx Voltage definition                     | 66 |

| Figure 42: EIEOS PP Tx Voltage definition.                              | 68 |

| Figure 43: Effective Tx package Loss Ratio definition.                  | 69 |

| Figure 44: Maximum Boost Ratio definition.                              | 70 |

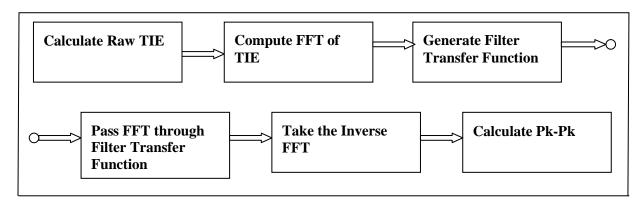

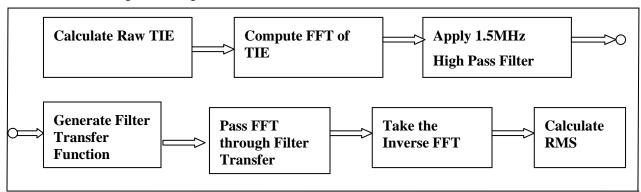

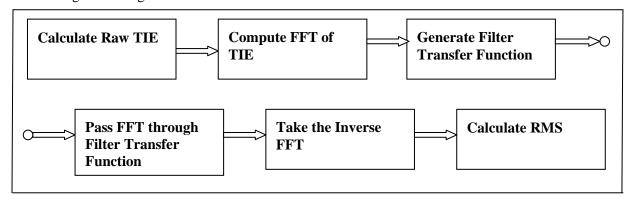

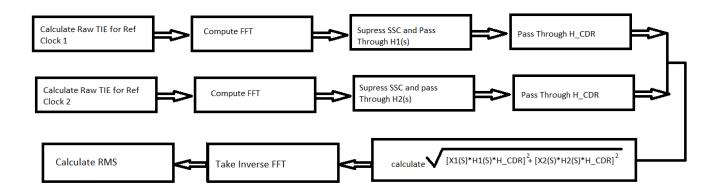

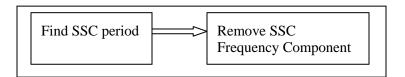

| Figure 46: Measurement algorithm block diagram                          | 71 |

| Figure 47: Filter transfer function for Gen1 Common Clock Architecture. | 72 |

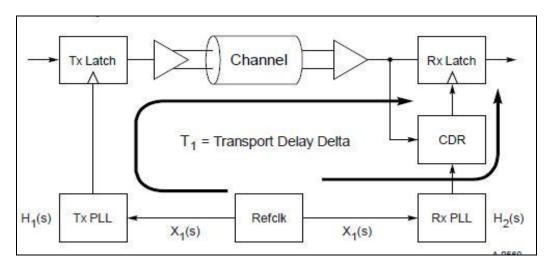

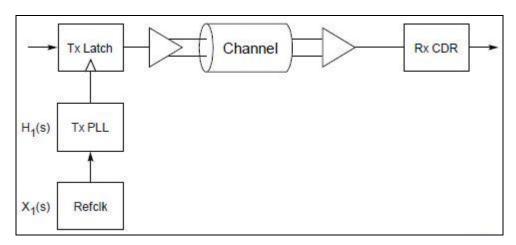

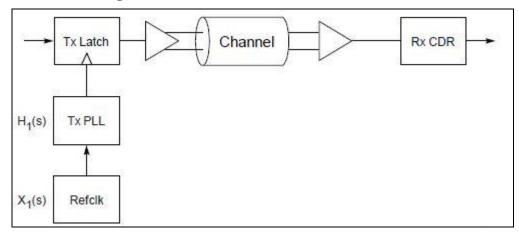

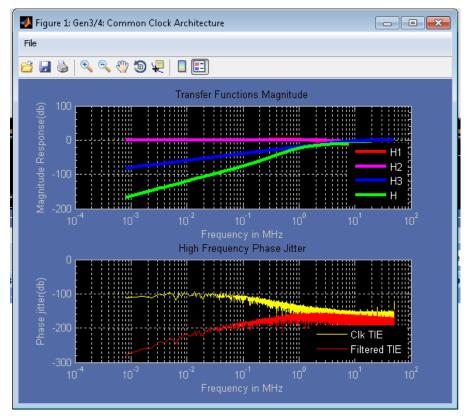

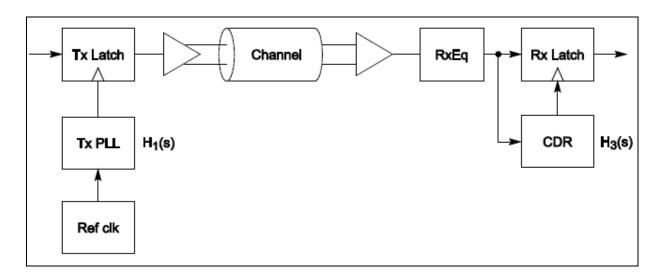

| Figure 49: Common RefClk Architecture, 5GT/s                            | 74 |

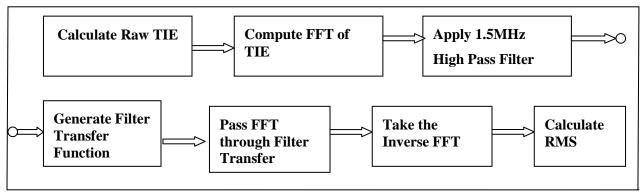

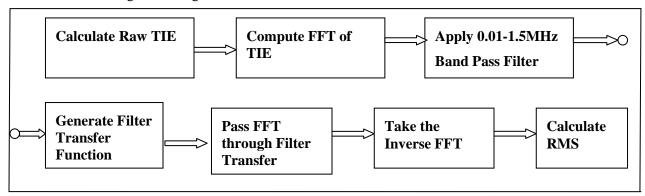

| Figure 50: Measurement algorithm block diagram                          | 74 |

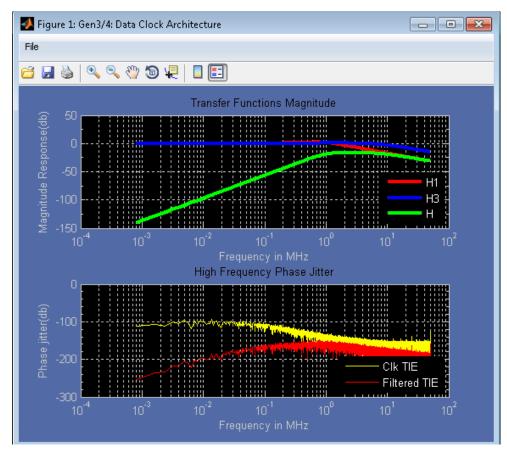

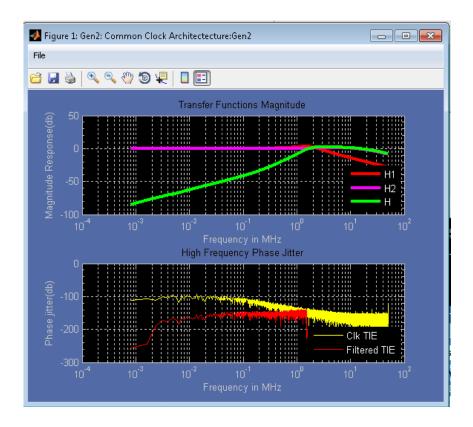

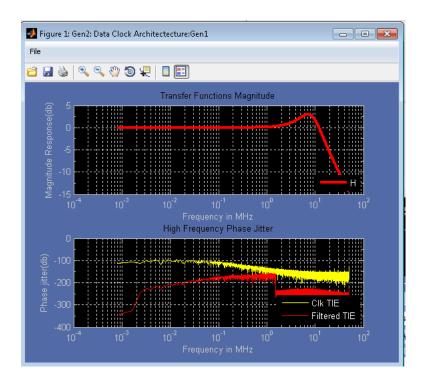

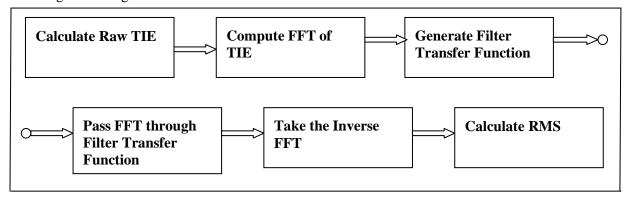

| Figure 51: Filter transfer function for Common Clock Architecture.      | 75 |

| Figure 52: Common Refclk bandwidth and damping for 5GT/s                | 75 |

| Figure 53: Raw TIE versus Filtered TIE                                  | 76 |

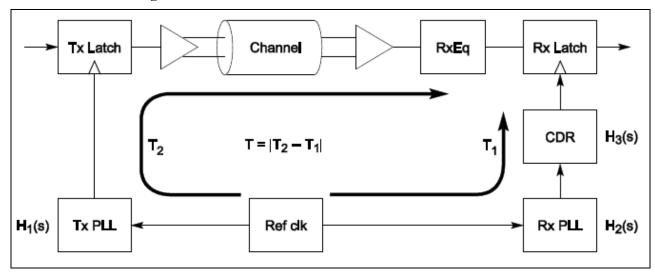

| Figure 54: Common RefClk Architecture                                   | 77 |

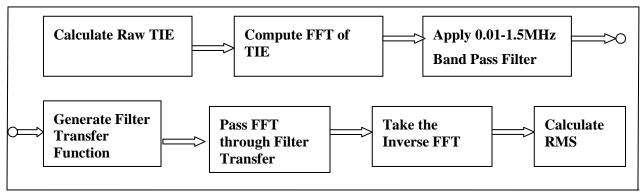

| Figure 55: Measurement algorithm block diagram                          | 77 |

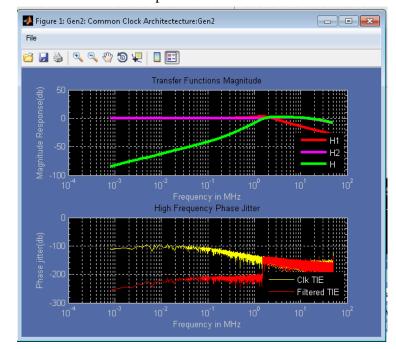

| Figure 56: Filter transfer function for Common Clock Architecture.      | 78 |

| Figure 57: Common Refclk bandwidth and damping for 5GT/s                | 78 |

| Figure 58: Raw TIE versus Filtered TIE                                  | 79 |

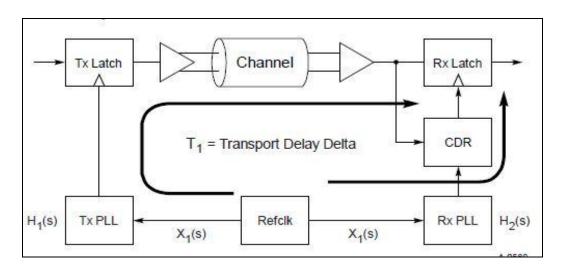

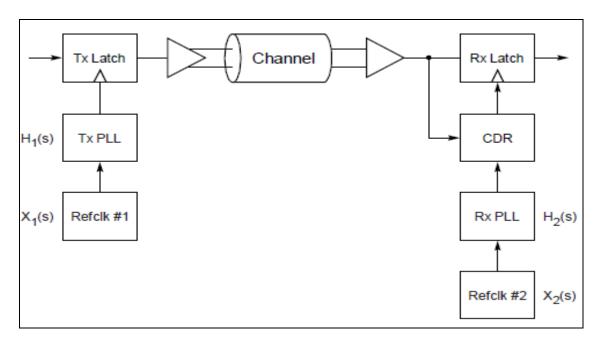

| Figure 59: Data Clocked RefClk Architecture                             | 80 |

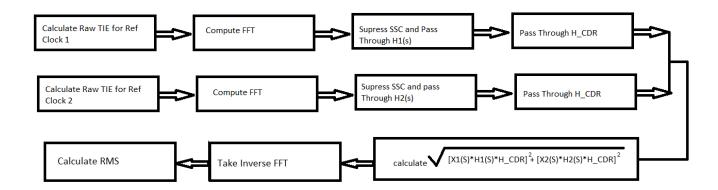

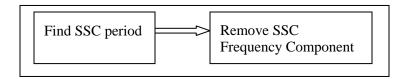

| Figure 60: Measurement algorithm block diagram                          | 80 |

| Figure 61: Filter transfer function for Common Clock Architecture.      | 81 |

| Figure 62: Data Clocked Refclk bandwidth and damping for 5GT/s          | 81 |

| Figure 63: Raw TIE versus Filtered TIE                                  | 82 |

| Figure 64: Date Cleaked DefClk Architecture                             | 92 |

| Figure 65: Measurement algorithm block diagram                                            | 83  |

|-------------------------------------------------------------------------------------------|-----|

| Figure 66: Filter transfer function for Common Clock Architecture.                        | 84  |

| Figure 67: Data Clocked Refclk bandwidth and damping for 5GT/s                            | 84  |

| Figure 68: Raw TIE versus Filtered TIE                                                    | 84  |

| Figure 69: Common RefClk Architecture                                                     | 85  |

| Figure 70: Measurement algorithm block diagram                                            | 86  |

| Figure 71: Filter transfer function for Common Clock Architecture.                        | 86  |

| Figure 72: Common Refclk Rx Architecture with ωn, ζ Limits                                | 86  |

| Figure 46: Measurement algorithm block diagram                                            | 88  |

| Figure 47: Filter transfer function for Gen1 Common Clock Architecture                    | 88  |

| Figure 48: Raw TIE versus Filtered TIE                                                    | 89  |

| Figure 74: Data Clocked Rx Architecture                                                   | 90  |

| Figure 75: Filter transfer function for Data Clocked Architecture                         | 90  |

| Figure 76: Data Clocked Rx Architecture with ωn, ζ Limits                                 | 91  |

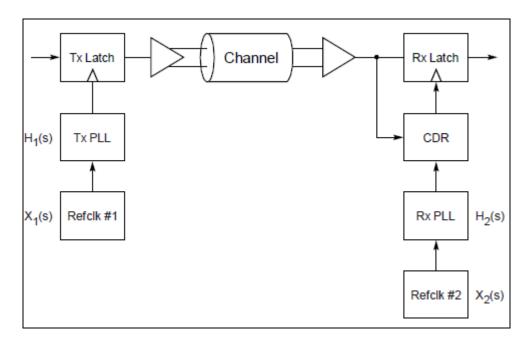

| Figure 77: Separate RefClk with Independent SSC Architecture                              | 93  |

| Figure 78: Measurement algorithm block diagram                                            | 94  |

| Figure 79: Filter transfer function for Separate RefClk with Independent SSC Architecture | 94  |

| Figure 77: Separate RefClk with Independent SSC Architecture                              | 96  |

| Figure 78: Measurement algorithm block diagram                                            | 97  |

| Figure 79: Filter transfer function for Separate RefClk with Independent SSC Architecture | 97  |

| Figure A1: Add-in card compliance eye masks                                               | 98  |

| Figure A2: Setup File Selection                                                           | 99  |

| Figure A3: Serial Data Link Analysis window                                               | 100 |

| Figure A4: SDLA Equalizer Setup Menu                                                      | 100 |

| Figure A5: DPOJET Measurement Results                                                     | 100 |

| Figure A6: System Board Compliance Eye Masks                                              | 101 |

| Figure A7: Setup File Selection                                                           | 101 |

| Figure A8: Serial Data Link Analysis window                                               | 102 |

| Figure A9: SDLA Equalizer                                                                 | 103 |

| Figure A10: DPOJET Measurement Results                                                    | 103 |

| Figure B1: Add-in card compliance eye masks                                               | 116 |

| Figure B2: Setup File Selection                                                           | 116 |

| Figure B3: Serial Data Link Analysis window                                               | 117 |

| Figure R4: Embadding Channel configuration                                                | 117 |

| Figure B5: Equalizer settings                | 118 |

|----------------------------------------------|-----|

| Figure B6: DPOJET Measurement Results        | 118 |

| Figure B7: System Board Compliance Eye Masks | 119 |

| Figure B8: Setup File Selection              | 119 |

| Figure B9: Serial Data Link Analysis window  | 120 |

| Figure B10: Embedding compliance channel     | 120 |

| Figure B10: Equalizer settings               | 121 |

| Figure B11: DPOJET Measurement Results       | 122 |

# 1 <u>Introduction to the DPOJET PCI Express Setup</u> <u>Library<sup>1</sup></u>

This document provides the procedures for taking PCI Express measurements with Tektronix DPO/DSA70000 Series Oscilloscopes with DPOJET (Jitter and Eye Analysis Tools) and probing solutions.

DPOJET and its PCI Express Setup Library provide transmitter path measurements (amplitude, timing, and jitter), waveform mask, and limits testing described in multiple variants of the PCI Express specifications.

Table 1 – Supported Specifications in the DPOJET Setup Library

| PCI Express Specification Title | Test Points Defined                                        |

|---------------------------------|------------------------------------------------------------|

| Base Specification              | Transmitter & Receiver                                     |

| base Specification              | (Section 4.3)                                              |

|                                 | , ,                                                        |

| CEM Specification               | System and Add-In Card                                     |

|                                 | (Section 4.7)                                              |

|                                 | Reference Clock (Section 2.1)                              |

| MXM Specification               | System and Module(0 & 3.5dB DeEmphasis)(Section 2.4 & 2.5) |

| Ref Clock Specification         | Reference Clock(Section 2.6)                               |

| Express Module Specification    | Transmitter Path and System Board (Section 5.4)            |

| PCMCIA Express Card Standard    | Host System Transmitter                                    |

|                                 | Express Card Transmitter                                   |

|                                 | (Section 4.2.1.2)                                          |

| External Cabling Specification  | Transmitter and Receiver Path (Section 2.12 & 2.13)        |

| External Cabling Specification  | Transmitter and Receiver Path (Section 2.12 & 2.13)        |

1

<sup>&</sup>lt;sup>1</sup> **Disclaimer:** The tests provided in DPOJET (which are described in this document) do not guarantee PCI Express compliance. The test results should be considered "Pre-Compliance". Official PCI Express compliance and PCI-SIG Integrator List qualification is governed by the PCI-SIG (Special Interest Group) and can be achieved only through official PCI-SIG sanctioned testing.

| PCI Express Specification Title     | Test Points Defined                                             |  |  |

|-------------------------------------|-----------------------------------------------------------------|--|--|

| Base Specification                  | Transmitter & Receiver (Section 4.4)                            |  |  |

|                                     | Mobile Low Power Transmitter (Section 4.4)                      |  |  |

| CEM Specification                   | System and Add-In Card (3.5 & 6dB DeEmphasis)                   |  |  |

|                                     | (Section 4.7)                                                   |  |  |

| MXM Specification                   | System and Module(0 & 3.5dB DeEmphasis)(Section 2.4 & 2.5)      |  |  |

| Base Specification                  | Transmitter                                                     |  |  |

|                                     | (Table 3)                                                       |  |  |

| CEM Specification                   | System and Add-In Card                                          |  |  |

|                                     | (Table 5 & 6)                                                   |  |  |

| Gen2 & Gen3 Ref Clock Specification | Reference Clock(Section 2.6, Table 7B & 7C)                     |  |  |

| Gen4 Base Specification             | Table 3- Specific PCI Express 4.0 Base transmitter measurements |  |  |

Refer to <a href="http://www.pcisig.com/specifications/pciexpress/">http://www.pcisig.com/specifications/pciexpress/</a> for the latest specifications.

In this document, for all references to the PCI Express Base Specifications and Card Electrical Mechanical (CEM) specifications, refer to all versions of the specifications. (Rev 1.1, 2.0, and 3.0, 4.0). Differences between the specifications are specifically called out when appropriate.

In the subsequent sections, step-by-step procedures are described to help you perform PCI Express measurements. Each measurement is described as a Method of Implementation (MOI). For further reference, consult the Compliance checklists and tools offered to PCI-SIG members at <a href="https://www.pcisig.com">www.pcisig.com</a>.

# 2 PCI Express Specifications

As shown in Table 2, Electrical Specifications for PCI Express are provided in multiple documents. This section provides a summary of the measurement parameters measured in the DPOJET Setup Library module and how they are related to the symbol and test limits in the specification.

### 2.1 Differential Transmitter (TX) Output Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base Specifications.

**Table 2- Supported Base Specification transmitter measurements**

|                                                    |                        |                                                                         |                                                                                                        | Specification                                                                                                                                                            |                                                                                    |

|----------------------------------------------------|------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                    |                        | DPOJET                                                                  | 2.5GT/s                                                                                                | 5.0 GT/s                                                                                                                                                                 | 8.0 GT/s                                                                           |

| Parameter                                          | Symbol(s)              | Measurement                                                             | Rev1.1/Rev2.0                                                                                          | Rev2.0                                                                                                                                                                   | Rev3.0                                                                             |

| Clock Recovery                                     | NA                     | See Setup by Data Rate >>                                               | 1st Order PLL Fc: 1MHz Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattern | 2 <sup>nd</sup> Order PLL<br>CDR w/ .707<br>Damping<br>Fc: 1.0MHz<br>- And -<br>3 <sup>rd</sup> Order LPF<br>Fc: 1.5MHz<br>Emulates Step<br>Function Filter<br>at 1.5MHz | 1st Order PLL Fc: 10MHz Assumes Scrambled Compliance Pattern with 50% Edge Density |

| Unit interval                                      | UI                     | PCIe UI<br>(min/max)<br>SSC filtered with 3rd<br>order LPF: Fc = 198kHz | 399.88 (min)<br>400.12 (max)                                                                           | 199.94 (min)<br>200.06 (max)                                                                                                                                             | 124.9625 (min)<br>125.0375 (max)                                                   |

| Differential p-p TX voltage swing                  | VTX-DIFF-PP            | PCle T-Tx-Diff-PP                                                       | 0.8 V (min)<br>1.2 V (max)                                                                             | 0.8 V (min)<br>1.2 V (max)                                                                                                                                               | Refer Table 3                                                                      |

| Low power differential p-p TX voltage swing        | VTX-DIFF-PP-Low        | PCle T-Tx-Diff-PP                                                       | 0.4 V (min)<br>1.2 V (max)                                                                             | 0.4 V (min)<br>1.2 V (max)                                                                                                                                               | Refer Table 3                                                                      |

| De-emphasized output voltage ratio of -3.5dB       | VTX-DE-RATIO-<br>3.5dB | PCIe T/nT Ratio                                                         | -3.0 dB (min)<br>-4.0 dB (max)                                                                         | -3.0 dB (min)<br>-4.0 dB (max)                                                                                                                                           | Not Specified                                                                      |

| De-emphasized output voltage ratio of -6dB         | VTX-DE-RATIO-<br>6dB   | PCIe T/nT Ratio                                                         | Not Applicable                                                                                         | -5.5 dB (min)<br>-6.5 dB (max)                                                                                                                                           | Not Specified                                                                      |

| Instantaneous lane pulse width                     | TMIN-PULSE             | PCle Tmin-Pulse                                                         | Not Specified                                                                                          | 0.9UI (min)<br>150 ps (min)                                                                                                                                              | Not Specified                                                                      |

| Transmitter eye<br>including all jitter<br>sources | $T_{TX-EYE}$           | For Rev1.1: Eye Width<br>For Rev2/3: PCIe T-TX                          | .75 UI (min)<br>300 ps (min)                                                                           | .75 UI (min)<br>150 ps (min)                                                                                                                                             | Refer Table 3                                                                      |

|                                                                                       |                                |                                                                           |                               | Specification                                                              |                                                                        |

|---------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|

| Parameter                                                                             | Symbol(s)                      | DPOJET<br>Measurement                                                     | 2.5GT/s<br>Rev1.1/Rev2.0      | 5.0 GT/s<br>Rev2.0                                                         | 8.0 GT/s<br>Rev3.0                                                     |

| Maximum time between<br>the jitter median and<br>maximum deviation<br>from the median | TTX-EYEMEDIAN-<br>to-MAXJITTER | PCIe Med-Mx Jitter                                                        | .125 UI<br>(min/max)          | Not Specified                                                              | Not Specified                                                          |

| Deterministic jitter                                                                  | TTX-DJ-DD                      | DJ–δδ                                                                     | Not Specified                 | 0.15 UI (max)<br>30 ps (max)                                               | TBD                                                                    |

| Tx RMS jitter < 1.5MHz                                                                | TTX-LF-RMS                     | TIE1 Jitter<br>3 <sup>rd</sup> Order LPF<br>Fc: 1.5 MHz<br>Std. Deviation | Not Specified                 | 3.0 ps (max)                                                               | Not Specified                                                          |

| D+/D- TX output rise/fall<br>Time <sup>2</sup>                                        | $T_{TX-RISE}$ $T_{TX-FALL}$    | PCIe T-Tx-Rise<br>PCIe T-Tx-Fall                                          | 0.125 UI (min)<br>50 ps (min) | 0.15 UI (min)<br>30 ps (min)                                               | Not Specified                                                          |

| Tx rise/fall mismatch                                                                 | TRF-MISMATCH                   | PCIe T-RF-Mismch                                                          | Not Specified                 | 0.1 UI (max)                                                               | Not Specified                                                          |

| Tx AC peak-peak<br>Common mode voltage                                                | VTX-CM-AC-PP                   | Common Mode<br>Pk-Pk                                                      | Not Specified                 | 100 mV (max) (no more than 100 mVPP in 0.03 500 MHz range) or 150 mV (max) | 50 mV (max) (no more than 50 mV in 0.03-500 MHz range) or 150 mV (max) |

| Tx AC peak Common mode voltage                                                        | VTX-CM-AC-P                    | Common Mode<br>Rev1.1 : StdDev                                            | 20mV RMS<br>(max)             | Not Specified                                                              | Not Specified                                                          |

| Absolute delta of DC common mode voltage between D+ and D-                            | $V_{TX-CM-DC-LINE-DELTA}$      | Common Mode<br>Mean                                                       | 0 V (min)<br>25 mV (max)      | 0 V (min)<br>25 mV (max)                                                   | 0 V (min)<br>25 mV (max)                                               |

| Pk-Pk Refclk jitter for<br>common Refclk Rx<br>architecture, Gen1                     | TREFCLK                        | T-REFCLK                                                                  | 86 ps                         |                                                                            |                                                                        |

| RMS Refclk HF jitter for common Refclk Rx architecture, Gen2                          | TREFCLK-HF-<br>RMSCC           | T-HF-RMSCC-RCLK                                                           |                               | 3.1 ps RMS                                                                 |                                                                        |

| RMS Refclk LF jitter for common Refclk Rx architecture , Gen2                         | TREFCLK-LF-<br>RMSCC           | T-LF-RMSCC-RCLK                                                           |                               | 4.0 ps RMS                                                                 |                                                                        |

\_

<sup>&</sup>lt;sup>2</sup> Rise/Fall time measurements in DPOJET are compliant to the Rev1.0a and Rev1.1 specification. For Gen2, rise and fall time is limited to TF2 and TR2 as defined in section 4.3.3.8 of the Base Specification

|                                                                             |                       |                   |               | Specification |            |

|-----------------------------------------------------------------------------|-----------------------|-------------------|---------------|---------------|------------|

|                                                                             |                       | DPOJET            | 2.5GT/s       | 5.0 GT/s      | 8.0 GT/s   |

| Parameter                                                                   | Symbol(s)             | Measurement       | Rev1.1/Rev2.0 | Rev2.0        | Rev3.0     |

| RMS Refclk HF jitter for data clocked Rx architecture, Gen2                 | TREFCLK-HF-<br>RMS-DC | T-HF-RMSDC-RCLK   |               | 4.0 ps RMS    |            |

| RMS Refclk LF jitter for data clocked Rx architecture, Gen2                 | TREFCLK-LF-<br>RMS-DC | T-LF-RMSDC- RCLK  |               | 7.5 ps RMS    |            |

| RMS Refclk jitter for common Refclk Rx architecture                         | TREFCLK-RMS-<br>CC    | T-REFCLK-RMS-CC   |               |               | 1.0 ps RMS |

| RMS Refclk jitter for<br>data clocked Rx<br>architecture                    | TREFCLK-RMS-<br>DC    | T-REFCLK-RMS-DC   |               |               | 1.0 ps RMS |

| RMS Refclk jitter for<br>separate Refclk<br>independent SSC<br>architecture | TREFCLK-RMS-<br>SRIS  | T-REFCLK-RMS-SRIS |               |               | 0.5 ps RMS |

Table 3- Specific PCI Express 4.0 Base transmitter measurements

| Parameter                                   | Symbol(s)        | DPOJET Measurement     | 8.0 GT/s<br>Rev3.0                                                  | 16.0 GT/s<br>Rev0.5                                                 |

|---------------------------------------------|------------------|------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| Clock Recovery                              | NA               | See Setup by Data Rate | 1st Order PLL                                                       | 1st Order PLL                                                       |

|                                             |                  | >>                     | Fc: 10MHz                                                           | Fc: 10MHz                                                           |

|                                             |                  |                        | Assumes Scrambled<br>Compliance Pattern<br>with 50% Edge<br>Density | Assumes Scrambled<br>Compliance Pattern<br>with 50% Edge<br>Density |

| Full Swing Tx voltage with noTxEq           | VTX-FS-NO-EQ     | V-TX-NO-EQ             | 1300 mV(max)<br>800 mV(min)                                         | 1300 mV(max)<br>800 mV(min)                                         |

| Reduced Swing Tx voltage with noTxEq        | VTX-RS-NO-EQ     | V-TX-NO-EQ             | 1300 mV(max)                                                        | 1300 mV(max)                                                        |

| Min swing during<br>EIEOS for full swing    | VTX-EIEOS-FS     | V-TX-EIEOS             | 250 mV(min)                                                         | 250 mV(min)                                                         |

| Min swing during<br>EIEOS for reduced swing | VTX-EIEOS-RS     | V-TX-EIEOS             | 232 mV(min)                                                         | 232 mV(min)                                                         |

| Pseudo package loss Root device             | ps21TXRootdevice | ps21TXRootdevice       | -3.0dB(min)                                                         | -3.0dB(min)                                                         |

| Pseudo package loss AIC device              | ps21TXAlCdevice  | ps21TXAlCdevice        | NA                                                                  | -5.0dB(min)                                                         |

| Tx uncorrelated total jitter                | TTX-UTJ          | T-TX-UTJ               | 31.25ps(max)                                                        | 12.5ps(max)                                                         |

| Parameter                                     | Symbol(s)     | DPOJET Measurement 8.0 GT/s Rev3.0 |            | 16.0 GT/s<br>Rev0.5 |

|-----------------------------------------------|---------------|------------------------------------|------------|---------------------|

| Tx uncorrelated deterministic jitter          | TTX-UDJDD     | T-TX-UDJDD                         | 12ps(max)  | 6.25ps(max)         |

| Data dependent jitter                         | TTX-DDJ       | T-TX-DDJ                           | 18ps(max)  | NA                  |

| Total uncorrelated PWJ                        | TTX-UPW-TJ    | T-TX-UPW-TJ                        | 24ps(max)  | 12.5ps(max)         |

| Deterministic DjDD uncorrelated PWJ           | TTX-UPW-DJDD  | T-TX-UPW-DJDD                      | 10ps(max)  | 5ps(max)            |

| Maximum Boost voltage ratio for full swing    | V-TX-BOOST-FS | V-TX-BOOST                         | 8dB(min)   | 8dB(min)            |

| Maximum Boost voltage ratio for reduced swing | V-TX-BOOST-RS | V-TX-BOOST                         | 2.5dB(min) | 2.5dB(min)          |

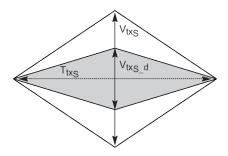

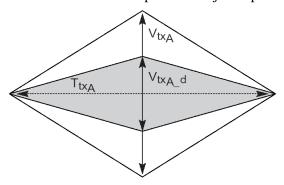

# 2.2 Differential Transmitter (TX) Compliance Eye Diagrams

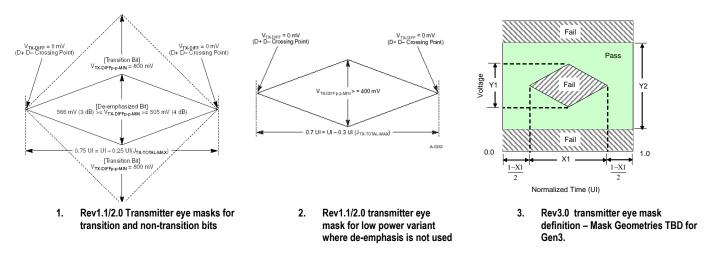

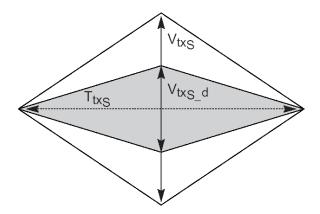

Figure 1a shows the eye mask definitions for the Rev1.1 Base Specification. It provides an example of a transmitter mask for a signal with de-emphasis. Transition and non-transition bits must be separated to perform the mask testing. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications. Low power transmitter variants in both Gen1 and Gen2 do not use de-emphasis (This is shown in Figure 1b).

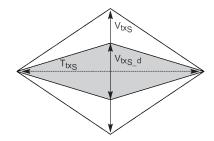

Figure 1: PCI Express Transmitter Eye Mask Definitions

### 2.3 Differential Receiver (RX) Input Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base specifications.

Table 4 – Supported base specification receiver measurements for Gen1 and Gen2

|                                                                               |                                | DPOJET                                                         | 2.5GT/s                                                                                                 | 5.0 GT/s                                                                                                                                                              |

|-------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                     | Symbol                         | Measurement                                                    | Rev1.1/Rev2.0                                                                                           | Rev2.0                                                                                                                                                                |

| Clock Recovery                                                                | NA                             | See Setup by Data Rate                                         | 1st Order PLL Fc: 1MHz  Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattern | 2 <sup>nd</sup> Order PLL CDR<br>w/ .707 Damping<br>Fc: 1.0MHz<br>- And -<br>3 <sup>rd</sup> Order LPF<br>Fc: 1.5MHz<br>Emulates Step<br>Function Filter at<br>1.5MHz |

| Unit interval                                                                 | UI                             | PCIe UI (min/max) SSC filtered with 3rd order LPF: Fc = 198kHz | 399.88 (min)<br>400.12 (max)                                                                            | 199.94 (min)<br>201.06 (max)                                                                                                                                          |

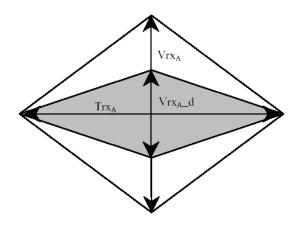

| Minimum receiver eye height                                                   | V <sub>RX_EYE</sub>            | PCle T-Tx-Diff-PP                                              | .175 V (min)<br>1.2 V (max)                                                                             | .120 V (min)<br>1.2 V (max)                                                                                                                                           |

| Minimum receiver eye width                                                    | $T_{RX-EYE}$                   | For Rev1.1: Eye Width<br>For Rev2: PCI T-TX                    | .40 UI (min)<br>160ps (min)                                                                             | Not Specified                                                                                                                                                         |

| Receiver deterministic jitter – Dj                                            | T <sub>RX_DJ_DD</sub>          | DJ–δδ                                                          | Not Specified                                                                                           | .30 UI (max)<br>60 ps (max)                                                                                                                                           |

| Minimum width pulse at Rx                                                     | Trx-min-pulse                  | PCle Tmin-Pulse                                                | Not Specified                                                                                           | .60 UI (min)<br>120ps (max)                                                                                                                                           |

| Maximum time between the jitter median and maximum deviation from the median. | Ttx-eyemedian-to-<br>maxjitter | PCIe Med-Mx Jitter                                             | .30 UI (max)                                                                                            | Not<br>Specified                                                                                                                                                      |

| Rx AC common mode voltage                                                     | VRX-CM-AC-P                    | Common Mode<br>Rev2/3 : Pk-Pk                                  | 150mV                                                                                                   | 150mV                                                                                                                                                                 |

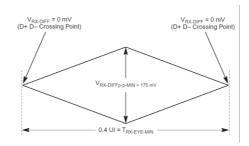

## Differential Receiver (RX) Eye Diagrams

Figure 2 shows the receiver eye mask definitions for the Rev1.1 Base Specification. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications.

Figure 2: Receiver input eye mask

# 2.4 Add-In Card Transmitter Path Compliance Specifications

Table 5 is derived from the Card Electrical Mechanical Specifications (CEM). See the CEM Specification for additional notes and test definitions.

Table 5 – Supported CEM add-in card measurements

| Parameter                                                    | Symbol                        | DPOJET                                                 | 2.5GT/s                                                                         | 5.0 GT/s                                                                                             | 8.0 GT/s                   |

|--------------------------------------------------------------|-------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|

|                                                              |                               | Measurement                                            | Rev1.1/Rev2.0                                                                   | Rev2.0                                                                                               | Rev3.0                     |

| Clock Recovery                                               | NA                            | See Setup by Data<br>Rate >>                           | 1st Order PLL<br>Fc: 1MHz                                                       | 2nd Order PLL CDR<br>w/ .707 Damping<br>Fc: 1.0MHz<br>- And -<br>3rd Order LPF                       | 1st Order PLL<br>Fc: 10MHz |

|                                                              |                               |                                                        | Emulates 1st Order filter at 1.5MHz with 75% edge density of Compliance Pattern | Fc: 1.5MHz Emulates Step Function Filter at 1.5MHz                                                   |                            |

| Unit interval                                                | UI                            | PCIe UI                                                | 399.88 (min)                                                                    | 199.94 (min)                                                                                         | 124.9625 (min)             |

|                                                              |                               | (min/max) SSC filtered with 3rd order LPF: Fc = 198kHz | 402.12 (max)                                                                    | 200.06 (max)                                                                                         | 125.6625<br>(max)          |

| Differential P-P Voltage                                     | VDiff-PP                      | PCIe VTx-Diff-PP                                       | Not Specified                                                                   | Not Specified                                                                                        | 50mV (min)<br>1200mV(max)  |

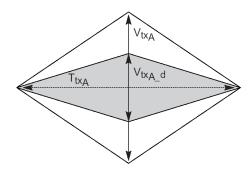

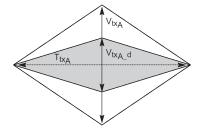

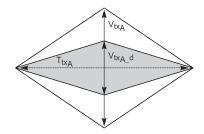

| Eye height of transition<br>bits                             | VTXA                          | Eye Height1                                            | 0.514 V (min)<br>1.2 V (max)                                                    | 3.5dB De-emphasis<br>.380 V (min)<br>1.2 V (max)<br>6.0dB De-emphasis<br>.306 V (min)<br>1.2 V (max) | 50mV (min)<br>1200mV(max)  |

| Eye height of non-<br>transition bits                        | VTXA_d                        | Eye Height2                                            | 0.360 V (min)<br>1.2 V (max)                                                    | 3.5dB De-emphasis .380 V (min) 1.2 V (max) 6.0dB De-emphasis .260 V (min) 1.2 V (max)                | 50mV (min)<br>1200mV(max)  |

| Eye width with sample size of 106 UI                         | TTXA In Rev1.1                | Eye Width                                              | 287 ps (min)                                                                    | Not Specified                                                                                        | Not Specified              |

| Jitter eye opening at<br>BER 10-12                           | TTXA In Rev2.0                | For Rev1.1: Eye<br>Width<br>For Rev2/3: PCle<br>T-TX   | 274 ps (min)<br>Informative                                                     | 123 ps (min)<br>with Crosstalk                                                                       | 45.00ps(min)               |

| Maximum median-max jitter outlier with sample size of 106 UI | JTXA-MEDIAN-<br>to-MAX-JITTER | PCIe Med-Mx Jitter                                     | 56.5 ps (max)                                                                   | Not Specified                                                                                        | Not Specified              |

| Total Jitter at BER 10-12         | Tj at BER 10-12 | TJ@BER | Not Specified | 77 ps (max)   | 80.00 ps(max) |

|-----------------------------------|-----------------|--------|---------------|---------------|---------------|

| Deterministic Jitter at BER 10-12 | Max Dj          | DJ–δδ  | Not Specified | 57 ps (max)   | Not Specified |

| Random Jitter at BER<br>10-12     | Max Rj          | RJ–δδ  | Not Specified | Not Specified | 3.0 ps (max)  |

Specific PCI Express Gen3 measurements derived from SigTest Compliance tool for Add In Card: -

| Parameter              | DPOJET      | 8.0 GT/s      |

|------------------------|-------------|---------------|

|                        | Measurement | Rev3.0        |

| Clock Recovery         | See Setup   | 1st Order PLL |

|                        |             | Fc: 10MHz     |

| Min TBit Voltage(Max)  | Eye Low     | -25mV(max)    |

|                        |             | -600mV(Min)   |

| Min nTBit Voltage(Max) | Eye Low     | -25mV(max)    |

|                        |             | -600mV(Min)   |

| Max TBit Voltage(Min)  | Eye High    | 25mV(max)     |

|                        |             | 600mV(Min)    |

| Max nTBit Voltage(Min) | Eye High    | 25mV(max)     |

|                        |             | 600mV(Min)    |

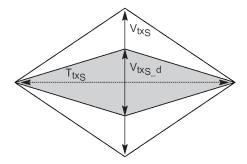

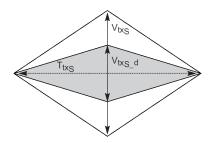

### **Add-In Card Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 5.

Figure 3: Add-in card compliance eye masks

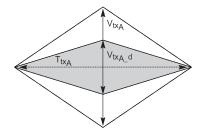

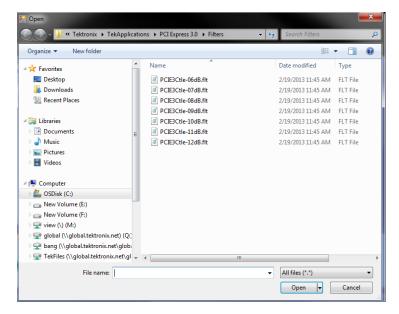

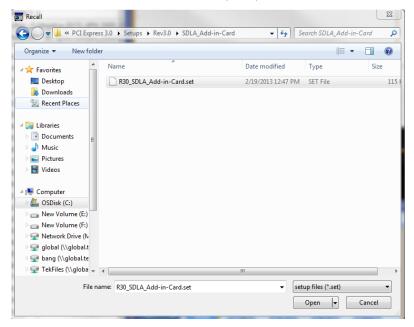

#### **Load the Add-In Card Setup File in DPOJET:**

- 1. In the scope menu, select Analyze->PCI Express

- 2. In the DPOJET standard tab, click the select button to choose the Test Point

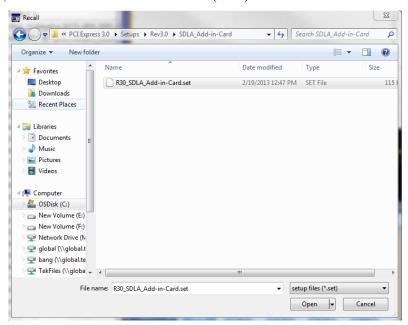

- 3. Select Rev3.0 -->SDLA\_Add-In-Card->R30\_SDLA\_Add-in-Card.set

- 4. In the Math Menu, set Math1 to Channel 1-Channel 2(Data)

Figure 4: Setup File Selection

#### Applying Channel and Behavioral Equalizer from SDLA:

(Note: for Windows XP and 32-bit Win 7 Scopes, go to Appendix A and follow the procedure)

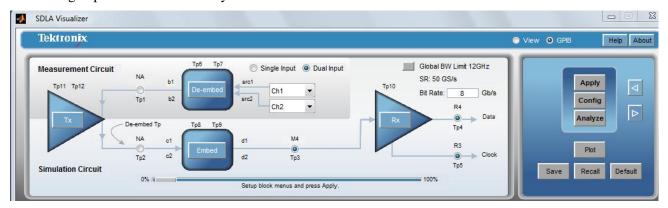

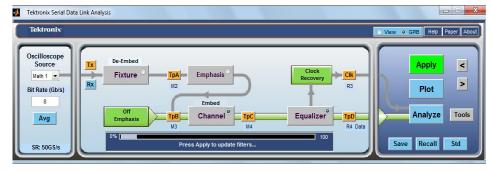

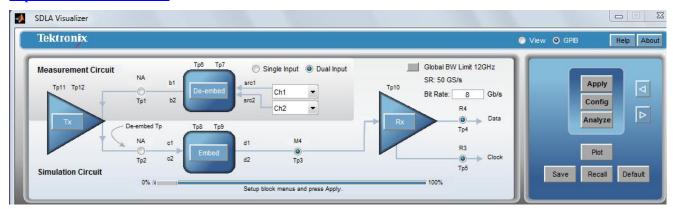

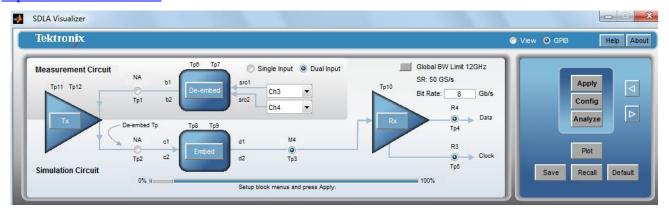

These measurements are done using SDLA (Serial Data Link Analysis) behavioral equalizer and channel embedding. Open SDLA from Analyze menu.

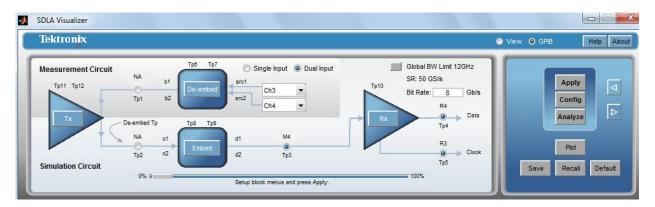

Figure 5: Serial Data Link Analysis window

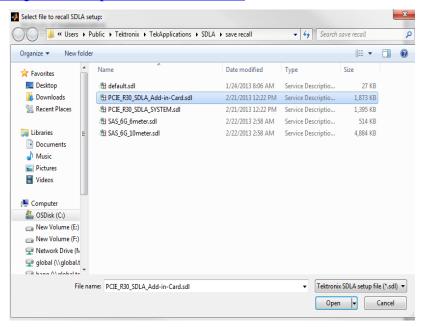

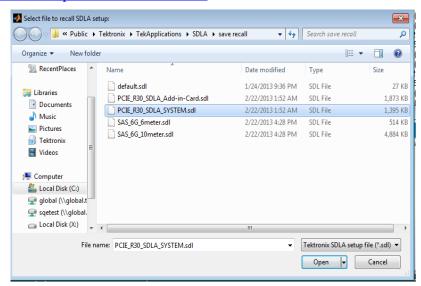

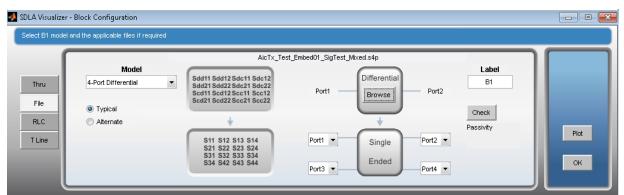

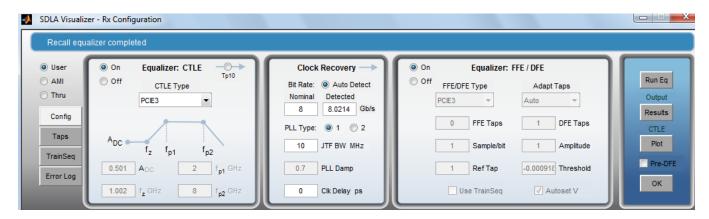

5. Click Recall and select 'PCIE\_R30\_SDLA\_Add-in-Card.sdl'. It will set Equalizer CTLE and DFE values as per the PCI Express 3.0 specification. For details of the PCI Express Gen 3 De-embedding procedure refer to the following document in <a href="http://www.tek.com/method-implementation/pci-express-30-de-embedding-method-implementation-version-10">http://www.tek.com/method-implementation/pci-express-30-de-embedding-method-implementation-version-10</a>

Figure 6: Setup file selection in SDLA

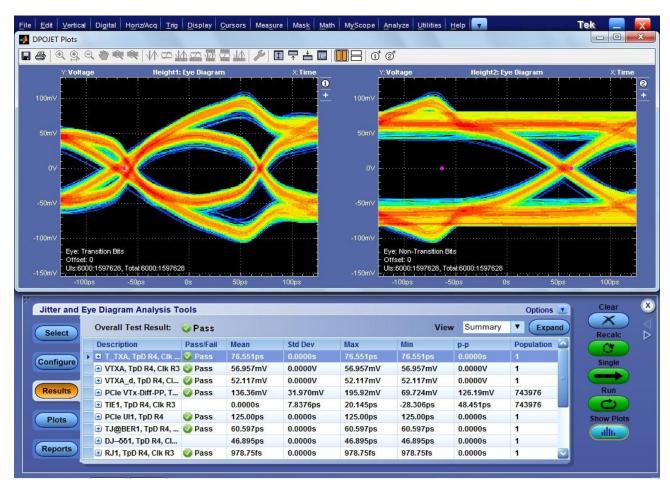

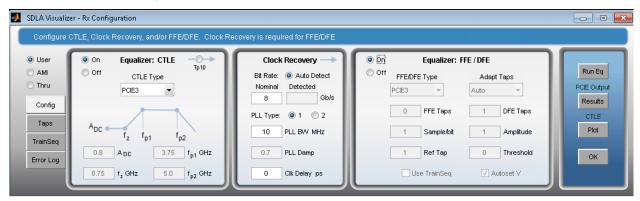

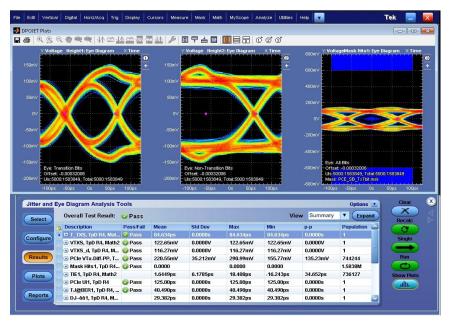

6. Click 'Apply' in SDLA. SDLA will process waveform from DUT by embedding the compliance channel and applying the reference equalizer (CTLE + 1 Tap DFE) and it will also automatically run DPOJET based on the current DPOJET configuration. The resulting waveform is placed in reference memory (Ref4). At the end user can generate a report containing the measurement results and test configuration by selecting the Report tab in DPOJET and clicking the save button.

**NOTE**: It is critical that the DPOJET setup file is recalled as described above before SDLA is ran.

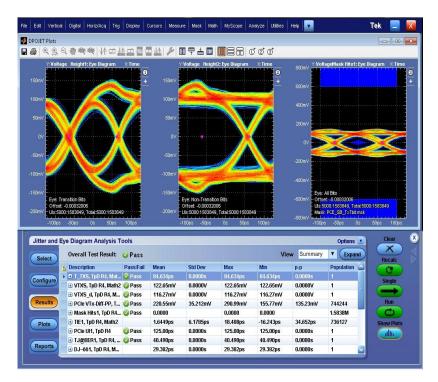

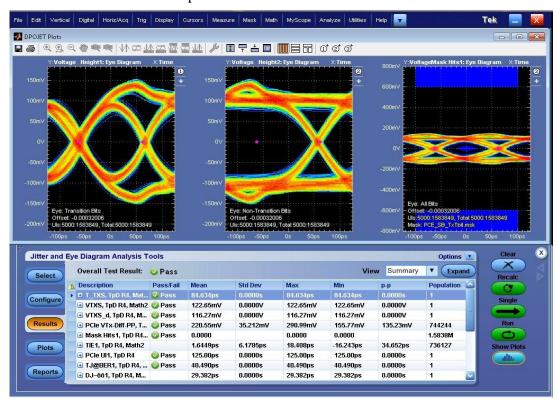

The results will be displayed as below.

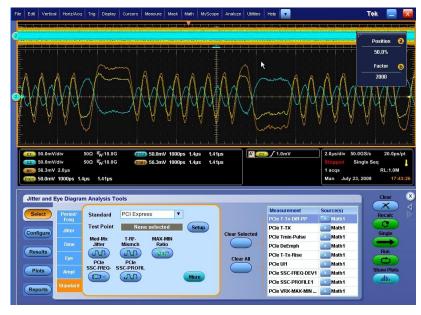

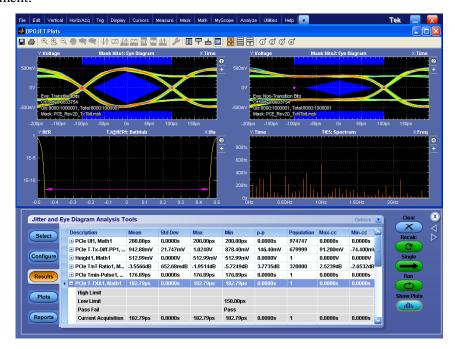

**Figure 7: DPOJET Measurement Results**

7. To configure SDLA manually, follow procedure described in Appendix B.

# 2.5 System Board Transmitter Path Specifications

Table 6 is derived from the Card Electrical Mechanical Specifications (CEM) and PHY Test Specification. See the CEM and Test Specification for additional notes and test definitions.

Table 6 - Supported CEM System Board Measurements

| Parameter                                                                | Symbol                                   | DPOJET                                                                  | 2.5GT/s                                                                                                                                                                            | 5.0 GT/s                                                                                                                 | 8.0 GT/s                                                                                         |

|--------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|                                                                          | ,                                        | Measurement                                                             | Rev1.1/Rev2.                                                                                                                                                                       | Rev2.0                                                                                                                   | Rev3.0                                                                                           |

|                                                                          |                                          |                                                                         | 0                                                                                                                                                                                  |                                                                                                                          |                                                                                                  |

| Clock Recovery                                                           | NA                                       | See Setup by Data Rate >>                                               | 2 <sup>nd</sup> Order PLL<br>CDR w/ .707<br>Damping<br>Fc: 1.0MHz<br>- And -<br>1 <sup>st</sup> Order LPF<br>Fc: 1.5MHz<br>Emulates 3 <sup>rd</sup><br>Order<br>3500:250<br>Method | Explicit Clock 2nd Order PLL Clock Multiplier=50 CDR w/ .707 Damping Fc: 1.0MHz  Emulates Step Function Filter at 1.5MHz | Explicit Clock 2nd Order PLL Clock Multiplier=80 Clock Edge Rising 0.707 Damping Fc(JTF): 2.0MHz |

| Unit interval                                                            | UI                                       | PCIe UI<br>(min/max)<br>SSC filtered with 3rd<br>order LPF: Fc = 198kHz | 399.88 (min)<br>402.12 (max)                                                                                                                                                       | 199.94 (min)<br>201.06 (max)                                                                                             | 124.9625 ps<br>(min)<br>125.6625ps<br>(max)                                                      |

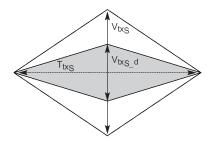

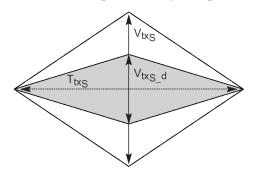

| Eye height of transition bits                                            | V <sub>TXS</sub>                         | Eye Height1                                                             | 0.274 V (min)<br>1.2 V (max)                                                                                                                                                       | 0.250 V (min)                                                                                                            | 46mV (min)<br>1200mV(max)                                                                        |

| Eye height of non-transition bits                                        | $V_{TXS\_d}$                             | Eye Height2                                                             | 0.253 V (min)<br>1.2 V (max)                                                                                                                                                       | 0.250 V (min)                                                                                                            | 46mV (min)<br>1200mV(max)                                                                        |

| Eye width with sample size of 106 UI                                     | T <sub>TXS</sub><br>In Rev1.1            | Eye Width                                                               | 246 ps (min)                                                                                                                                                                       | Not Specified                                                                                                            | Not Specified                                                                                    |

| Jitter eye opening at BER 10 <sup>-12</sup>                              | T <sub>TXS</sub><br>In Rev2.0            | For Rev1.1: Eye Width<br>For Rev2/3: PCle T-TX                          | 233 ps (min)<br>Informative                                                                                                                                                        | 95 ps (min)<br>with Crosstalk                                                                                            | 41.25ps(min)                                                                                     |

| Maximum median-max jitter outlier with sample size of 10 <sup>6</sup> UI | J <sub>TXA</sub> - MEDIAN-to- MAX-JITTER | PCIe Med-Mx Jitter                                                      | 77 ps (max)                                                                                                                                                                        | Not Specified                                                                                                            | Not Specified                                                                                    |

| Total Jitter at BER 10 <sup>-12</sup>                                    | Tj at BER<br>10 <sup>-12</sup>           | TJ@BER                                                                  | Not Specified                                                                                                                                                                      | 105 ps (max)                                                                                                             | 83.75 ps(max)                                                                                    |

| Deterministic Jitter at BER 10 <sup>-12</sup>                            | Max Dj                                   | DJ–δδ                                                                   | Not Specified                                                                                                                                                                      | 57 ps (max)                                                                                                              | Not Specified                                                                                    |

| Random Jitter at BER 10-12                                               | Max Rj                                   | RJ–δδ                                                                   | Not Specified                                                                                                                                                                      | Not Specified                                                                                                            | 3.0 ps (max)                                                                                     |

Specific PCI Express Gen3 measurements derived from SigTest Compliance tool for System: -

| Parameter              | DPOJET      | 8.0 GT/s      |

|------------------------|-------------|---------------|

|                        | Measurement | Rev3.0        |

| Clock Recovery         | See Setup   | 2nd Order PLL |

|                        |             | Fc: 2MHz      |

| Min TBit Voltage(Max)  | Eye Low     | -23mV(max)    |

|                        |             | -600mV(Min)   |

| Min nTBit Voltage(Max) | Eye Low     | -23mV(max)    |

|                        |             | -600mV(Min)   |

| Max TBit Voltage(Min)  | Eye High    | 23mV(max)     |

|                        |             | 600mV(Min)    |

| Max nTBit Voltage(Min) | Eye High    | 23mV(max)     |

|                        |             | 600mV(Min)    |

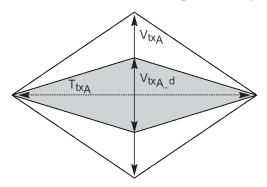

### **System Board Eye Diagrams**

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 6.

Figure 8: System Board Compliance Eye Masks

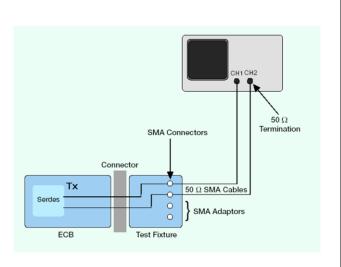

#### **Load the System Setup File in DPOJET:**

- 1. In the scope menu, select Analyze->PCI Express

- 2. In the DPOJET standard tab, click the select button to choose the Test Point

- 3. Select Rev3.0->SDLA\_System->R30\_SDLA\_SYSTEM.set

- 4. In the Math Menu, set Math1 to Channel 3-Channel4(Data) and Math2 to Channel 1-Channel2(Clock)

Figure 9: Setup File Selection

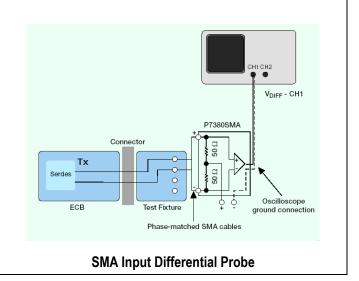

#### **Applying Channel and Behavioral Equalizer from SDLA:**

(Note: for Windows XP, go to Appendix A and follow the procedure)

These measurements are done using SDLA (Serial Data Link Analysis) behavioral equalizer and channel embedding. Open SDLA from Analyze menu.

Figure 10: Serial Data Link Analysis window

5. Click Recall and select 'PCIE\_R30\_SDLA\_SYSTEM.sdl'. It will set Equalizer CTLE and DFE values as per the PCI Express 3.0 specification. For details of the PCI Express Gen 3 De-embedding procedure refer to the following document in <a href="http://www.tek.com/method-implementation/pci-express-30-de-embedding-method-implementation-version-10">http://www.tek.com/method-implementation/pci-express-30-de-embedding-method-implementation-version-10</a>

Figure 11: Setup file selection in SDLA

6. Click 'Apply' in SDLA. SDLA will process waveform from DUT and it will also process DPOJET analysis. At the end user will get a complete report of System Board.

The results will be displayed as below.

**Figure 12: DPOJET Measurement Results**

**Note:** Nominally the PCIe Rev3.0 bit rate is 8 Gb/s. But if a signal with SSC is tested, the bit rate should be set to 7.98 Gb/s. (0.25% lower). Alternatively, use the Auto Detect bit rate feature in SDLA Visualizer that will determine the exact clock frequency near the specified rate.

To repeat measurements, you can clear previous results by pressing Clear in DPOJET and press Apply in SDLA. New acquisition and calculations will be completed automatically. This is necessary when testing different presets.

#### To configure SDLA manually, follow procedure described in Appendix B.

When measuring systems with short channels, or when doing exploratory testing, CTLE equalization may be sufficient. Then use R30\_SYSTEM.set in R30\_SYSTEM folder. This setup does not require SDLA and sets up a CTLE with -7dB gain as an ArbFilter. It does not embed the channel. Press Single to acquire waveforms and calculate measurements. In this mode Free Run is possible.

To change the CTLE filter, follow the procedure described below:

- 1. Load R30\_SYSTEM.set file from R30\_SYSTEM folder.

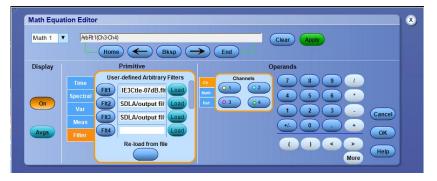

- 2. Click on Math menu and go to 'Editor' in Math subsystem.

#### Figure 13: Filter settings in Math menu

3. Select 'Filter' tab and click 'Load' button in 'Flt1' section. It will guide to the desired filters location. Select any of seven filters(-6dB to -12dB CTLE filters) and click Open. It will apply the desired filter to differential data.

Figure 14: Selecting CTLE Filter

4. Click 'Single' in DPOJET.

### 2.6 Reference Clock Specification

Table 7 is derived from the PCI Express Card Electromechanical Specification for Gen1 Clock and PCI Express Base Specification Rev 3.0 for Gen2 and Gen3.

Gen 1 Clock Setup files

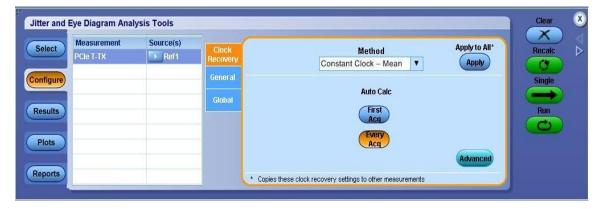

Clock Recovery

Edge

Limit

T -RCLK

Constant Clock(Mean)

Rising

86ps(pk-pk)

Table 7A – Supported Ref Clock Rev1.1 Measurements

Table 7B - Supported Ref Clock Rev2.0 Measurements

| Gen 2 Clock Setup files |                      |        |             |  |

|-------------------------|----------------------|--------|-------------|--|

|                         | Clock Recovery       | Edge   | Limit       |  |

| T-HF-RMSCC-RCLK         | Constant Clock(Mean) | Rising | 3.1 ps(RMS) |  |

| T-LF-RMSCC-RCLK         | Constant Clock(Mean) | Rising | 3.0 ps(RMS) |  |

| T-HF-RMSDC-RCLK         | Constant Clock(Mean) | Rising | 4.0 ps(RMS) |  |

| T-LF-RMSDC-RCLK         | Constant Clock(Mean) | Rising | 7.5 ps(RMS) |  |

| SRNS                    | Constant Clock(mean) | Rising | 2 ps(RMS)   |  |

| SRIS                    | Constant Clock(mean) | Rising | 2 ps(RMS)   |  |

Table 7C - Supported Ref Clock Rev3.0 Measurements

| Gen 3 Clock Setup files |                      |        |             |  |

|-------------------------|----------------------|--------|-------------|--|

|                         | Clock Recovery       | Edge   | Limit       |  |

| T-RMSCC-RCLK            | Constant Clock(mean) | Rising | 1 ps(RMS)   |  |

| T-WST-RMSCC-RCLK        | Constant Clock(mean) | Rising | 1 ps(RMS)   |  |

| T-RMSDC-RCLK            | Constant Clock(mean) | Rising | 1 ps(RMS)   |  |

| T-WST-RMSDC-RCLK        | Constant Clock(mean) | Rising | 1 ps(RMS)   |  |

| Gen3_SRIS               | Constant Clock(mean) | Rising | 0.5 ps(RMS) |  |

| Gen3_SRNS               | Constant Clock(mean) | Rising | 0.5 ps(RMS) |  |

Table 7D - Supported Ref Clock Rev4.0 Measurements

| Gen 4 Clock Setup files |                      |        |             |  |

|-------------------------|----------------------|--------|-------------|--|

|                         | Clock Recovery       | Edge   | Limit       |  |

| PCIE4_T-RMSCC-RCLK      | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

| PCIE4_T-WST-RMSCC-RCLK  | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

| PCIE4_T-RMSDC-RCLK      | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

| PCIE4_T-WST-RMSDC-RCLK  | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

| PCIE4_SRIS              | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

| PCIE4_SRNS              | Constant Clock(mean) | Rising | 0.7 ps(RMS) |  |

Table below shows the various requirements from the specification for the reference clock:

| Symbol                                | Description                                                         | Limits |           | Units  | Note |

|---------------------------------------|---------------------------------------------------------------------|--------|-----------|--------|------|

|                                       | Description                                                         | Min    | Max       |        |      |

| T <sub>REFCLK-HF-RMS</sub>            | > 1.5 MHz to Nyquist RMS<br>jitter after applying<br>Equation 4.3.3 |        | 3.1       | ps RMS | 1    |

| T <sub>REFCLK-SSC-RES</sub>           | SSC residual                                                        |        | 75        | ps     | 1    |

| T <sub>REFCLK-LF-RMS</sub>            | 10 kHz - 1.5 MHz RMS jitter                                         |        | 3.0       | ps RMS | 2    |

| T <sub>SSC-FREQ-DEVIATION</sub>       | SSC deviation                                                       |        | +0.0/-0.5 | %      |      |

| T <sub>SSC-MAX-PERIOD</sub> -<br>SLEW | Maximum SSC df/dt                                                   |        | 0.75      | ps/UI  | 3    |

#### Notes:

- TREFCLK-HF-RMS is measured at the far end of the test circuit illustrated in Figure 4-89 after the filter function defined in Table 4-30 for Common Refclk Rx for >1.5 MHz jitter components has been applied.

- T<sub>REFCLK-SSC-RES</sub> and T<sub>REFCLK-LF-RMS</sub> are measured after the filter function defined in Table 4-30 for Common Refclk Rx for >1.5 MHz jitter components has been applied.

- 3. Defined for a worst case SSC modulation profile such as Lexmark.

Table 7d: Refclk Parameters for Common Refclk Rx Architecture at 5.0 GT/s (spec Table 4-32)

| Symbol                               | Description                                                | Limits |           | Units  | Note |

|--------------------------------------|------------------------------------------------------------|--------|-----------|--------|------|

| Symbol                               | Description                                                | Min    | Max       |        |      |

| T <sub>REFCLK-HF-RMS</sub>           | 1.5 - Nyquist MHz RMS jitter after applying Equation 4.3.5 |        | 4.0       | ps RMS | 1    |

| T <sub>REFCLK-SSC-FULL</sub>         | Full SSC modulation corresponding to +0 – 0.5%             |        | 20        | ns     | 1    |

| T <sub>REFCLK-LF-RMS</sub>           | 10 kHz - 1.5 MHz RMS jitter                                |        | 7.5       | ps RMS | 2    |