入門書:高変換効率パワー設計の測定

電力測定の基礎からLPDDR、PCI Expressのローパワー・モード検証まで

# 目次

| 設計エンジニア、消費者、環境に優しいエネルギーの節約3<br>エネルギー効率に優れた設計例: |

|------------------------------------------------|

| 携帯電話3                                          |

| 電力変換4-10                                       |

| スイッチング損失の測定                                    |

| 正確な電力測定:                                       |

| プローブで考慮する点                                     |

| 電圧プローブと電流プローブ間のスキュー調整6                         |

| プローブ・オフセットの除去6                                 |

| 磁気電力損失の測定                                      |

| 磁気電力損失                                         |

| 磁気特性·······                                    |

| 電力ライン測定                                        |

| 電源品質                                           |

| 電流高調波                                          |

| 消費電力11-27                                      |

| 低消費電力のためのコンポーネントレベルでの最適化 1 ]                   |

| LVDS (Low Voltage Differential Signaling,      |

| 小振幅差動シグナリング)                                   |

| シングルエンド信号と差動信号 12                              |

| 差動信号のプロービング                                    |

| 液晶ディスプレイのLEDバックライト                             |

| LEDバックライトのドライブ                                 |

| バックライト電力の測定                                    |

| ン人テムレヘルでのエネルキー管理                       | 16 |

|----------------------------------------|----|

| デジタル回路における電力消費                         | 16 |

| ダイナミック・パワー・マネージメント(DPM)                | 17 |

| 動的な電圧/周波数スケーリング                        | 18 |

| 通信バスのエネルギー損失                           | 18 |

| PCI Expressのロー・パワー・モード                 | 19 |

| アクティブ・ステート電力管理                         | 19 |

| リンク・スピードとリンク幅の変更                       | 21 |

| LPDDR (Low Power Double Data Rate) メモリ | 22 |

| LPDDRのパワー・セーブ・モード                      | 23 |

| アクティブ動作時のパワー・セーブ・モード                   | 23 |

| インタラクティブ動作時のパワー・セーブ・モード                | 23 |

| LPDDR DRAMデバイスの検証                      |    |

| 待機電力·····                              |    |

| ACの待機電力/電流測定                           |    |

| ナノアンペアのDC電流測定                          | 27 |

| まとめ                                    | 27 |

| 44 +V -L + h                           | -  |

# 設計エンジニア、消費者、 環境に優しいエネルギーの節約

今日、モバイル・エレクトロニクスは家庭、病院、学校、バッグ、ポケットなど、いたるところで見ることができます。また、ポータブル・アプリケーションは、携帯電話やノートPC、デジタル・カメラやMP3プレーヤ、携帯ゲーム・システムなど、ほとんど無限にあるように思われます。携帯性の急速な進化/普及と共に、バッテリ寿命の長時間化が要求されるようになってきました。10年前、一般的な携帯電話は1回の充電で使用できる時間はせいぜい4時間でした。今では、1回の充電で数日使うこともできます。

エネルギー効率に優れた設計の技術革新により、バッテリ寿命は 延びました。設計が単純な場合、少ない電力損失で高い性能を実 現するためには、電源を含む、それぞれのハードウェア・コンポー ネントの最適化が重要でした。

携帯電子機器が、1台で高い性能、優れた機能を実現するようになると、この製品をドライブする組込みシステムはさらに高性能になります。このようなシステムは1つのコンポーネントに比べてより複雑であり、互いに通信し合う、さまざまなコンポーネントで構成されています。最新のエネルギー管理技術はすべての組込みシステムを監視し、全体の電力消費を抑えます。

サーバやパソコンなど、AC電源を使用する電子機器もこれらの技術を統合しており、事業者、消費者、行政などによって低電力消費が求められています。電源プラグを差し込み、電子機器の電源を入れる人の数が増え、一人あたりの電子機器の数が増えると、消費者や事業者の負担する電気料金も大幅に増加します。世界の電力消費量は年間で約2%増加しており、各国政府は高まる需要に対応するため、送電網の容量増加を迫られています。エネルギー効率の改善は、エネルギー有効利用のための最も短時間で、クリーンに、低コストで実現できる方策です。

急増する電力需要/ニーズに対し、新しい方法、材料によって同じ機能を低電力で実現したり、新しい方法で電力使用を管理したりするなど、エンジニアは技術革新でこれに応えています。

# エネルギー効率に優れた設計例:携帯電話

エネルギー効率に優れた設計で使用されているさまざまな技術の 例が、携帯電話です。携帯電話は何年もかけて、音声のみのデバイスから、インターネット閲覧、ゲーム、写真、音楽のシェア、ナビゲーションなど、さまざまな機能を備えたマルチメディア・デバイスへと変容しています。

携帯電話に新しい機能が追加されると、限られたエネルギー・バジェットの一部が必要になりますが、今日のほとんどの携帯電話は音声のみの設計の頃と似たようなバッテリ容量に頼っています。このような数多くの機能を実現するためには、エンジニアは新しい低電力設計を構築する必要があります。

携帯電話で使用されるさまざまな回路は、異なった電源電圧を必要とすることがあり、回路ごとに異なったDC/DCコンバータが必要になります。従来のコンバータはリニア・レギュレータや損失の多いコンポーネントを使用しており、電力変換効率は50%以下でした。現在ではスイッチング電源が一般的となっており、最大効率は90%にもなります。

設計全般にわたり、コンポーネントは低電力で使用されるように 最適化されています。特殊なバックライトLEDを使用するディス プレイは、最大で80%もの電力を節約します。データ転送のため のLVDS(Low Voltage Differential Signaling)により、電力 を抑えながらデータのインテグリティ(品位)を保ちます。

設計がますます複雑になるにしたがって、システムレベルでエネルギーを管理する技術が進化してきました。プロセッサと通信バスの周波数は実際のニーズにしたがって上がり、パワー・マネージメントにより周波数とともに電圧は低下することにより、エネルギー消費は大幅に低減されます。

さらに、待機電力も削減されています。電源がオフになっていても 消費され続けるわずかな電力である待機電力は、家庭で使用される 電力需要の10%にもなると推定されています。携帯電話などのバッ テリ駆動の製品の場合、待機電力は明るいディスプレイ表示、バッ クライト・ボタン、高速起動の電源スイッチのために用意されるも のです。低電圧のロジック、マイクロプロセッサのスリープ・モー ドの電力管理であっても、待機電力はバッテリ寿命、携帯電話の使 いやすさに大きく影響します。

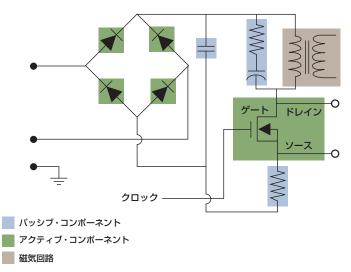

図1. スイッチング電源の概略図

携帯電話全体において、エネルギー効率を考慮した設計技術が実装され、さまざまな機能を実現しつつ、優れたバッテリ寿命を可能にしています。同様のトレンドは、他の携帯電子機器、AC電源を使用する機器にも当てはまります。この変化に伴い、テスト/測定技術も進化しました。この入門書では、エネルギー効率に優れた設計技術と、新規設計で影響する検証、デバッグ、特性評価について説明します。

## 電力変換

従来、電子機器で最も大きなエネルギー損失は、電力変換時に発生していました。AC電源を使用するどのような電子デバイスもAC/DCコンバータ電源を持っており、電力をAC(Alternating Current、交流)からDC(Direct Current、直流)に変換します。また、AC電源、またはバッテリ駆動による多くの電子機器はDC/DCコンバータを持っており、DC電圧を、回路ごとに必要となる異なったDC電圧に変換します。従来のリニア電源の変換効率は50%以下であり、この変換過程において大きなエネルギー損失になっていました。

今日ではスイッチング電源(SMPS、Switching Mode Power Supply)が電源の主流であり、変換効率は80~90%にもなります。スイッチング電源では、抵抗、リニアモード・トランジスタなどの電力損失があるコンポーネントの使用を極力抑え、理想的には電力損失のないコンポーネントを重視しています。これらのコンポーネントには、スイッチング用のトランジスタ、コンデンサ、磁気コンポーネントなどがあります(図1を参照)。スイッチング電源の検証と特性評価では、スイッチング損失と磁気電力損失を測定してスイッチング電源の効率を求め、電源品質と高調波を測定してスイッチング電源が電源ラインに及ぼす影響を理解する必要があります。

## スイッチング損失の測定

スイッチング電源に使用されているスイッチング・トランジスタは、スイッチング時間を高速にすることでエネルギー損失を最小にしています。トランジスタのオンまたはオフの状態でも非常にわずかな電力が消費されますが、スイッチング電源の最も大きなエネルギー損失はスイッチング時に発生します。スイッチング時のトランジションにおけるエネルギー損失は、ダイオードに蓄積された電荷の放電、および寄生インダクタンス/寄生キャパシタンスに蓄積されたエネルギーの放出によって生じます。

「ターンオフ損失」は、スイッチング・デバイスのオンからオフへのトランジション時のエネルギー損失を意味します。「ターンオン損失」は、スイッチング・デバイスのオフからオンへのトランジション時のエネルギー損失を意味します。トランジションにおけるエネルギー損失は、次の式で表わされます。

$$E_{transition} = \int_{t_0}^{t_1} v_a(t) \cdot i_a(t) \cdot dt$$

ここで、

- E<sub>transition</sub> はトランジションにおけるエネルギー損失

- v₂(t) はスイッチの瞬時電圧

- *i<sub>a</sub>*(*t*) はスイッチを流れる瞬時電流

- t<sub>1</sub>はトランジションが完了する時間

- to はトランジションが開始する時間

すべてのスイッチング・サイクルのトータル・エネルギー損失は、 スイッチング・トランジスタのターンオン損失、ターンオフ損失、 導通損失の合算になります。 総損失は次の式で定義されます。

$$E_{{\scriptscriptstyle Loss}} = E_{{\scriptscriptstyle turn-on}} + E_{{\scriptscriptstyle on}} + E_{{\scriptscriptstyle turn-off}}$$

ここで、

- $\blacksquare$   $E_{Lock}$  はスイッチング・サイクルにおけるエネルギー損失

- $E_{turn-on}$  と  $E_{turn-off}$  はスイッチング損失

- *E*<sub>on</sub> は導通損失

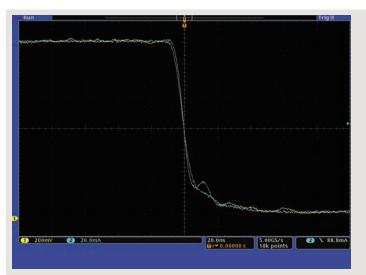

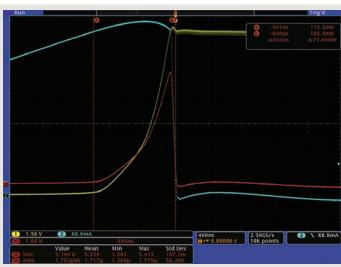

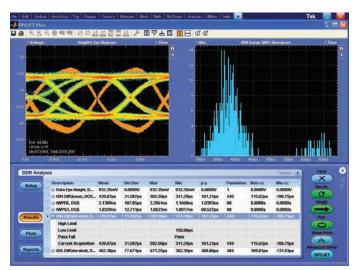

**図2.** MSO/DP04000シリーズ・オシロスコープとDP04PWRパワー解析ソフトウェアによる、スイッチング損失/統計値の測定例

電源の評価、効率の評価においては、これらの損失を正しく解析することが不可欠です。図2は、オシロスコープによるスイッチング損失測定の例です。オシロスコープとパワー解析ソフトウェアを使用することで、複数のスイッチング・サイクルにおけるスイッチング損失と導通損失を測定することができ、時間とともに変化するデバイスの動作を知ることができます。また、測定値の統計から、測定結果の変化を簡単に知ることができます。

ターンオン損失、ターンオフ損失の測定で最も難しいのは、これらの損失がスイッチング・サイクルのごく短時間に発生し、その他の大部分の時間で発生する損失は非常に小さいということです。したがって、電圧波形と電流波形間のタイミングは非常に正確である必要があり、測定系のオフセットも最小である必要があります。また、正確な電力測定のためには、プロービングについても充分注意を払う必要があります。

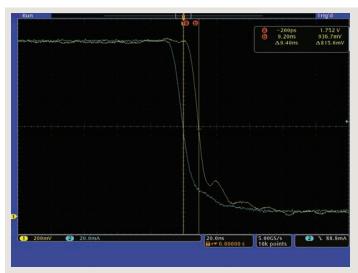

図3. 電圧信号と電流信号間の9.4nsのスキュー

図4. スキューがある場合、電力波形のピーク振幅は5.141Wとなる

# 正確な電力測定:プローブで考慮する点 電圧プローブと電流プローブ間のスキュー調整

デジタル・オシロスコープで電力を測定する場合、MOSFETスイッチング・デバイスのドレイン、ソース間の電圧と電流を測定する必要があります。IGBTの場合は、コレクタ、エミッタ間の電圧とコレクタ電流を測定する必要があります。この測定には、高電圧差動プローブと

電流プローブが必要になります。どちらのプローブにも伝播遅延特性があり、これらの遅延により「スキュー」として知られる時間差が発生し、電力、タイミングの測定確度が低下します。

最大ピーク・パワーと電力損失測定では、プローブの伝播遅延による影響を理解することは非常に重要になります。電力は、電圧と電流の掛け算です。掛け合わされる2つの値の時間的スキューが正しくとれていないと、正確な測定にはなりません。2本のプローブのスキューが正しくとれていないと、スイッチング損失などの測定確度が低下することになります。

プローブのスキューによる影響を、図3~6に示します。図3は電 圧プローブと電流プローブ間にスキューがあることを示しており、 スキューがある状態での測定結果(5.141W)を図4に示してい ます。

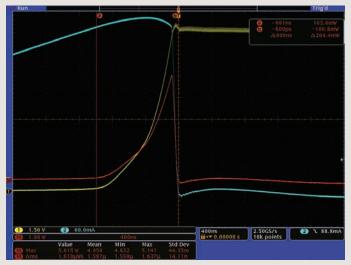

図5は、プローブがデスキューされている(スキューがとれている)ことを示しています。2本の波形は重なっており、遅延が解消されていることがわかります。図6は、デスキューを正しく行った場合の測定結果です。この例でわかるように、スキューにより5.3%の測定誤差が発生しています。正確なデスキューにより、ピーク・ピーク間の電力損失測定による誤差を低減することができます。

パワー測定ソフトウェアの中には、選択したプローブの組合せにおいて自動的にデスキューを実行するものもあります。このようなソフトウェアでは、デスキュー・フィクスチャとライブ信号を使用して電圧チャンネルと電流チャンネルの間の遅延を調整し、プローブ間の伝播遅延を除去します。

また、電圧プローブ、電流プローブは固有の伝播遅延を持つことから、便利なスタティック・デスキュー機能も装備しています。 当社のプローブを使用した場合、プローブ型名をテーブルから選択するだけで、組込まれた伝播遅延表に基づいて遅延を自動的に調整します。これにより、簡単に、しかもすばやくスキューを最小限に抑えることが可能になります。

## プローブ・オフセットの除去

差動プローブ、電流プローブは、微小な電圧オフセットを持つ傾向があります。このオフセットは測定確度に影響を及ぼすため、測定前に取り除く必要があります。プローブによっては、このオフセットを自動的に除去する機能を内蔵しているものもあります。

図5. デスキュー処理後の電圧信号と電流信号

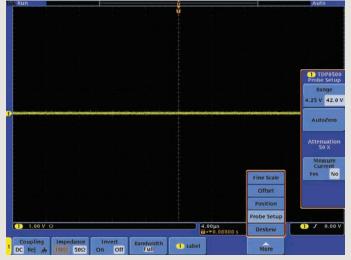

**図7.** TekVPIのプローブ・メニューに表示されるAutoZero機能

当社TekVPIプローブ・インタフェースを備えたプローブとオシロスコープを使用すると、信号経路にあるDCオフセットを除去することができます。TekVPIプローブのMENUボタンを押すと、オシロスコープにはプローブ・コントロール・ボックスが表示され、その中にAutoZero機能が表示されます(図7を参照)。プローブの先端を短絡した状態、あるいは電流がゼロの状態でAutoZeroのボタンをクリックすると、測定システムにあるDCオフセット誤差を自動的にキャンセルします。

**図6.** デスキュー後、ピーク振幅は5.415Wに増加(5.3%増加)

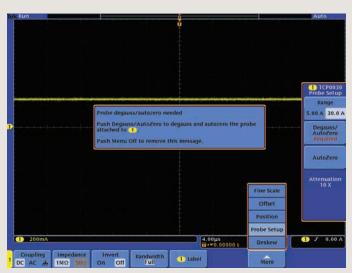

図8. TekVPIの電流プローブによるデガウス警告のポップアップ表示

TekVPI電流プローブには、さらにプローブ本体にDegauss/AutoZeroボタンがあります。AutoZeroボタンを押すと、測定システムのDCオフセット誤差を除去することができます。デガウスでは、大きな入力電流によって発生する内蔵変圧器コアの残留DC磁束を除去します。TekVPIの電流プローブには図8に示すようなデガウス・メッセージ機能があり、デガウスの実行を促しますで、時間経過に伴うドリフト、測定確度への影響を抑えることができます。

図9. DPO7000シリーズ・オシロスコープとDPOPWRパワー解析ソフトウェアによる、単巻線インダクタの電力損失測定の例

## 磁気電力損失の測定

一般に、インダクタと変圧器は電力損失が小さいため、スイッチング電源ではフィルタリングのためにインダクタが、電圧レベルの変更のために変圧器が使用されています。

周波数が高くなるとインダクタのインピーダンスは増加するため、 低い周波数より高い周波数が通りにくくなります。このため、イン ダクタは電源の入力と出力において、フィルタとして使用されます。

変圧器は、一次巻線と二次巻線の間でACの電圧と電流を磁気結合させることにより、信号のレベルを増減させます(電圧または電流のいずれか一方)。例えば、一次側に120Vを入力すると、二次側では12Vが出力されます。このとき二次側では、逆の比率で電流が増加します。信号の総電力は増加しないため、これは「増幅」とは考えられないことにご注意ください。変圧器の一次側と二次側は電気的に接続されていないため、回路要素間の絶縁として使用することもできます。

#### 磁気電力損失

磁気電力損失は、電源の効率、信頼性、温度性能に影響を及ぼします。磁気部品に関連する電力損失には、フェライト・コアの鉄損と銅線の銅損があります。

#### 磁気電力損失= 鉄損 + 銅損

ここで、

- 鉄損は、ヒステリシス損失と渦電流損失からなります。

- 銅損は、銅巻線の抵抗によるものです。

総電力損失と鉄損は、鉄芯メーカのデータ・シートとオシロスコープのパワー測定ソフトウェアの結果から、すばやく導き出すことができます。この2つの値から銅損を計算することができます。電力損失要素の違いがわかると、磁気コンポーネントにおける電力損失の原因を特定することが可能になります。

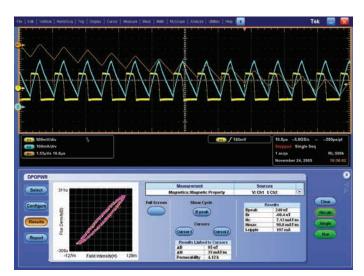

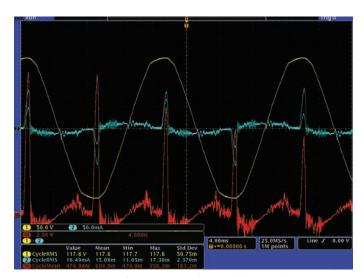

磁気コンポーネントのトータル電力損失を計算する方法は、測定するコンポーネントの種類によって異なります。テストするデバイスは、単巻線のインダクタ、複巻線のインダクタ(または変圧器)となります。図9に、単巻線インダクタの測定結果を示します。

チャンネル1(黄色の波形)はインダクタでの電圧で、チャンネル2(青の波形)は非接触型電流プローブを使用して測定したインダクタの電流です。パワー解析ソフトウェアは、電力損失の値を自動的に計算して表示します。ここでは、278.1mWと表示されています。

図10. DPO7000シリーズ・オシロスコープとDPOPWRパワー解析ソフトウェアによる、単巻線インダクタのB-H曲線測定の例

# THE PART OF THE PA

図11. DP07000シリーズ・オシロスコープとDP0PWRパワー解析ソフトウェアによる、変圧器のB-H曲線の例

#### 磁気特性

最適な性能を得るため、設計エンジニアは製造メーカのB-H(ヒステリシス)曲線を使って磁気コンポーネントを決定します。この曲線は、磁性物質であるコア材質の性能の概要を示しています。ヒステリシス曲線のリニア領域で電圧、電流を動作させるためには、スイッチング電源の磁気コンポーネントの特性を評価する必要があります。

専用のパワー解析ソフトウェアを使用することで、オシロスコープによる磁気特性測定が大幅に簡素化できます。多くの場合、電圧と磁化電流のみを測定するだけでよく、ソフトウェアが磁気特性を計算します。図10は、単巻インダクタにおける磁気特性測定

を示します。変圧器の一次および二次電流ソースも同様に測定できます。

図11では、チャンネル1 (黄色の波形) は変圧器にかかる電圧、チャンネル2 (青の波形) は一次側を流れる電流、チャンネル3 (赤紫の波形) は二次側を流れる電流です。ソフトウェアは、チャンネル2とチャンネル3のデータから磁化電流を計算します。

パワー解析ソフトウェアの中には、図10、11に示すように、磁気コンポーネントの正確なB-H曲線を描いたり、性能を評価したりするものもあります。パワー測定/解析ソフトウェアでB-H曲線を計算するには、コイルの巻数、磁路長、コアの断面積を入力する必要があります。

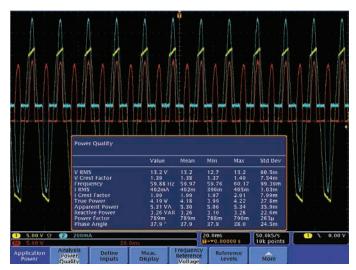

図12. MSO/DP04000シリーズ・オシロスコープとDP04PWRパワー解析ソフ トウェアによる電力品質測定例

## 電力ライン測定

電源品質や電源高調波などのAC/DC電源、電力ライン測定は、ス イッチング電源とそのサービス環境が及ぼす特性を評価するため に重要です。実際の電力ラインは理想的な正弦波ではなく、ライン 上にいくらかの歪みやノイズが存在します。スイッチング電源は、 電力ラインに対して非線形な負荷となります。このため、電圧と 電流の波形は同じにはなりません。電流は、入力サイクルの一部 のみに流れるため、入力電流波形では高調波が発生します。これ らの歪みの影響を見極めることは、電力エンジニアリングの重要 な仕事です。

#### 電源品質

電力ラインの消費電力と歪みを求めるには、入力部で電源品質を 測定します。オシロスコープに組込まれたパワー解析ソフトウェ アでほとんどの電力品質測定を自動化することができ、これまで 長時間かかっていた手順を数秒で実行できます。手動による計算 の数を減らすことで、オシロスコープは非常に多機能で効率的な 電力メータとして動作します。図12に、パワー解析ソフトウェア による測定例を示します。

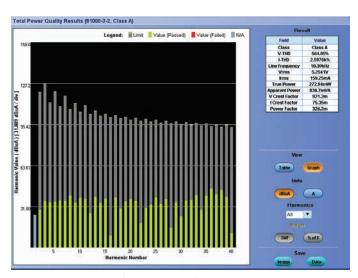

図13. DP07000シリーズ・オシロスコープとDP0PWRパワー解析ソフトウェア による電流の高調波解析例

#### 電流高調波

スイッチング電源は奇数次の高調波を発生する傾向があり、それ が電力網に戻ってしまうことがあります。この傾向は蓄積され、 電力網に接続されるスイッチング電源の数が増えるほど(例えば、 オフィス内で使用されるPCの数が増えると)、電力網に戻るトー タルの高調波歪みは増えることになります。この高調波歪みは電 力網のケーブルや変圧器の過熱の原因となるため、高調波歪みを 最小限に抑える必要があります。EN/IEC61000-3-2などの規格 では、特定の非直線性負荷の電源品質を規定しています。

パワー解析ソフトウェアを備えたオシロスコープにとっては、高 調波の解析は通常の波形測定と同じくらいに簡単です。図13は、 電源の負荷電流の高調波解析例を示しています。この例では、ソ フトウェアは電流高調波を自動的に計算し、基本波に対するTHD (Total Harmonic Distortion、全高調波歪み) やRMS (Root-Mean-Square、二乗平均平方根)などの重要な値を表示します。 この測定は、EN/IEC61000-3-2、MIL-STD-1399などの規格 の適合性解析に有効です。ソフトウェアの中には、測定値と規格 を比較し、デバイスの適合性をすばやく判定するものもあります。

## 消費電力

電力変換効率は今では90%台に達しつつあり、これ以上の効率改 善は難しくなっています。変換効率が頭打ちになる中、組込みシス テムで消費される電力を最小にすることに注目が集まっています。

消費電力を低減させる一つの方法は、設計内の各機能のエネルギー 効率を上げることです。多くの電子機器で最も電力を消費するの が、ディスプレイです。バックライトにLEDを使用する新しいディ スプレイ技術は、エネルギー節約に大いに貢献します。信号伝送 時の消費電力を抑える技術も、もう一つの例です。

システムレベルのエネルギー管理では、システム動作のアイドル 時間を有効に利用することで消費電力をさらに下げ、デジタル・ システムの性能を下げますが、結果としてエネルギーを節約しま す。このようなエネルギー管理技術は、今ではマイクロプロセッサ、 その他のプロセス要素、さらには通信バスまで利用できるように なっています。PCI Express®、Low Power DDR、MIPI® D-PHY、 M-PHY, USB 3.0, Mobile PCI Express® Module (MXM) などの規格の最新の仕様にも、低パワー・モードがあります。

エネルギー効率を考慮した最新設計の検証、デバッグ、特性評価で は、時には、新しい独自のテスト方法が必要になります。これらの テストについては、以降のセクションで詳しく説明します。

## 低消費電力のための コンポーネントレベルでの最適化

## LVDS (Low Voltage Differential Signaling, 小振幅差動シグナリング)\*

信号伝送時の消費電力を抑えるための技術として広く採用されて いるのがLVDSであり、通信ネットワーク、コンピュータ、医療、 自動車、工業アプリケーションなどで使用されています。

従来、負荷インピーダンスを下げ、ロジック・デバイスのドライ ブ電流を増やすことで転送速度を上げていました。これにより、 ドライバは寄生容量/インダクタンスの負荷効果に打ち勝ち、ス テートを高速に切り替えていました。

\* 本来、LVDSはANSI/TIA/EIA-644-Aで規格化され、平面パネルなどで使用されているデジタル伝 送技術を指しますが、ここではCML(Current Mode Logic)やTMDS(Transition Minimized Differential Signaling)などの小振幅・差動信号伝送技術をも含めてLVDSと称します。

消費電力を抑えつつ転送速度を上げる方法として、特に数十MHz から5Gbps程度までのデータ・レートにおいてLVDSは一般的に なりました。LVDSには、以下のような利点があります。

#### ■ 低電圧による優れたノイズ耐性

デジタル回路のノイズ耐性を改善する最もシンプルな方法は、 大きな電圧のシグナリングを使用することです。信号対ノイズ 比の観点から言えば、RS-232、CMOS、TTLロジックによる 大きな電圧スイングは、周辺の雑音レベルの感受性を下げるこ とになります。しかし、低電力が求められている中にあっては、 特にバッテリ駆動の回路設計では、多くの回路はより低い電源 電圧で動作する必要があります。しかも、製品の性能や信頼性 を犠牲にすることはできません。RS-422、RS-485、CAN、 FlexRayなどの規格で使用されている差動モード・シグナリン グは、非常に優れた耐コモンモード・ノイズと十分に小さな電 圧スイングを可能にしています。LVDSは、小さな電圧スイング の差動信号により、低消費電力と優れたノイズ耐性を可能にし ています。

#### ■ 高速動作時における低いEMI

#### (Electro-Magnetic Interference、電磁妨害)

電界強度は電圧スイングに比例するため、EMIの規制または低減 の要求の面からも低電圧電源へのトレンドが求められています。 干渉する帯域は、信号の立上り/立下り時間をコントロールす ることで下げることができます。EMIは、シールドによってもコン トロールできます。LVDSなどの差動シグナリングでは、一般的 にほとんどのシングルエンドのロジック・ファミリに比べて低 い電圧スイングを使用しています。エッジ速度は、通常制限さ れています。反対の極性を持った、等しい信号電流を流す信号 ペアは、基板上に平行に、またはツイスト・ペア・ケーブルで 配線されることで、遠方界での干渉を抑えています。

#### ■ ローコストによる高性能

製品が複雑になり回路密度が増してくると、シンプル、低コス トで実装しつつ、優れたシステム性能のニーズが増えてきます。 LVDSは、1つの抵抗負荷終端とDCカップリングにより、シン プルな回路実装を可能にしています。また、信号電流は常にオン になっており、差動ライン間で動作しているため、大きな電圧 でスイッチング・トランジェントする回路に比べ、電源供給回 路はシンプルになります。

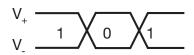

図14. 差動シグナリング

#### シングルエンド信号と差動信号

シングルエンドのデータ転送では、1本の信号ラインを各情報 チャンネルに、もう1本をコモン・グランドのリターン経路として 使用します。シングルエンドのレシーバは、グランドに対する入 力信号の電圧をもとにして、信号の論理状態を解釈します。この 方法の主な欠点は、入力信号に入り込むノイズ、コモン・グラン ド基準にのるノイズによる比較的貧弱なノイズ性能です。

差動シグナリングでは、図14に示すようなV+とV-の等しい振幅 の反対極性の信号ペアを使用してデジタル信号を伝送します。

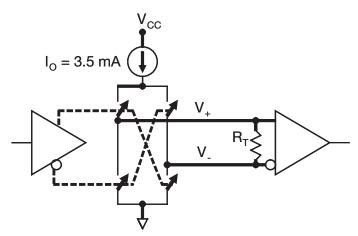

簡略化したLVDS回路(ANSI/TIA/EIA-644-A)を図15に示し ます。ここでは、トランスミッタ・スイッチのスイッチング・デ バイスが、双方向にある終端抵抗に流れる3.5mAの電流ソースを どのように切り替えるかを示しています。受信コンパレータは大 きな入力インピーダンスになっているため、終端抵抗R<sub>T</sub>(通常は 100Ω) に流れるすべての電流により、レシーバ入力では± 350mVの電圧になります。この回路では、約1.2mWの電力が負 荷に供給されます。

LVDSのレシーバは、信号間の電圧差( $V_+ - V_-$ )を測定し、 $O\sim$ 2.4Vのコモンモード電圧レンジに対してOV±100mVのスレッ ショルドで電圧差信号を比較するため、優れたノイズ・マージン

図15. LVDS差動トランスミッタ/レシーバの簡略回路図

とコモンモード除去が可能になります。差動信号(V+とV-)はペ アで配線されるため、一般に同じノイズがのります。2つの入力電 圧間で差をとるため、レシーバでは信号のコモンモード・ノイズ をキャンセルできます。

差動回路では、一定の電流が常に流れており、トランジスタの オン/オフによるスイッチング・スパイクが無いため、シングル エンドの回路に比べると放射ノイズは十分に小さくなります。こ のため、結果として大電流トランジスタからのEMIがなくなりま す。信号振幅も小さく、しかも、しっかりと結合された差動伝送 路のため、伝送路から放射される電磁ノイズも抑えられます。

さらに、信号リターン・パスに流れるコモンモード電流循環も抑 えられるため、伝導ノイズも同様に抑えられます。

図16. MSO4000シリーズ・オシロスコープで測定したLVDSのクロック信号の例

#### 差動信号のプロービング

情報は、単にグランドに対する信号の電圧というのではなく、2つ の物理レイヤ信号間の演算差分に符号化されているため、シング ルエンドのデジタル・ロジックにはない差動測定技術が必要にな ります。

2つの信号をグランド基準で測定し、差分を計算することで差動信 号は測定できます。この方法では、プローブ、オシロスコープの チャンネル・ゲイン、電圧オフセット、伝搬遅延、立上り時間/ 周波数帯域のマッチングで注意が必要になります。そのどれにお いても相違があると、差動信号の振幅とタイミングに誤差が発生 します。

アクティブ差動プローブでは、より正確で信頼性の高い方法が使 われています。差動プローブは、プローブ先端近くに差動アンプ を配置しており、電圧差分がオシロスコープに送られます。オシ ロスコープに接続するチャンネル数は1つで済むため、差動プロー ブを使用すると、オシロスコープで測定できる信号の数が2倍にな ります。

図16は、Ch1(黄) とCh2(シアン) にグランド基準のTAP1500 型シングルエンド・アクティブ・プローブで測定したV+とV-信号 を、Ch3(マゼンタ)はTDP1000型アクティブ差動プローブで 測定した差動信号を示しています。

LVDSなどの低電力デジタル技術は高速データ通信の数多くのア プリケーション要件に適合しており、製品サイズ、コスト、消費 電力を抑えることが可能になります。しかし、この技術では、正 しく測定するために考慮しなければならないことがあります。テ クトロニクスのTDPシリーズなど、独自に設計された差動プロー ブを使用すると、差動シグナリングに簡単にプロービングできま す。これにより、信号経路の差異を手作業で調整することなく、 LVDS信号を正確に測定できます。

## 液晶ディスプレイの LED バックライト

液晶ディスプレイ (LCD) の最も大きな改善の一つに、LED (Light Emitting Diode) バックライトを使用した消費電力の低下があり ます。従来、バックライトはパネルのサイド、上部、背面から LCDパネルを照射していました。

つい最近まで、ほとんどのLCDディスプレイはCCFL(Cold Cathode Fluorescent、冷陰極管)バックライトを使用していま した。この設計では、一般的なディスプレイ・システムにおいて、 アーク発生のためにまず数千ボルトにもなるAC高電圧を発生させ るためのパワー・インバータ回路を持っていました。次に、数百 ボルトを発生してランプのガスに連続的に電流を流し、UV (ultraviolet、紫外線)を放射します。UVエネルギーは管内部に 塗布された蛍光塗料に吸収され、可視光として再放射します。

一方、LEDのバックライトでは光源として、直列接続したLEDを 並列に配置します。高品位のディスプレイでは、白のバックライ トはレッド、グリーン、ブルー (RGB) のLEDで構成されます。 ロー パフォーマンスのアプリケーションでは、白の光はリンを封入し たUV LEDで、またはブルーLEDとカラー・フィルタで白い光を 再放射します。

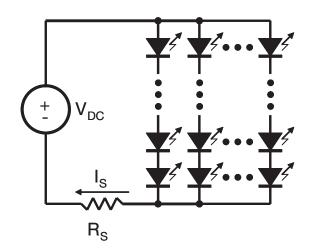

図17. 電流制限抵抗によるバックライトLEDドライバ

LEDバックライトは、以下に示すようにCCFLバックライトに比 べて数多くの利点があります。

#### ■ 薄く、軽いLEDディスプレイ

LEDはCCFLに比べると小型であるため、より薄いガイド・プレー ト、デフューザが使用できます。このため、ディスプレイが薄く、 軽くできます。

#### ■ 機械的なショック、振動に強い

CCFLはガラス管であり、振動によりデバイス寿命が大きく損な われる可能性があります。

#### ■ 低消費電力

ルーメン/ワットで測定されるLEDとCCFLの発光効率は同程度 ですが、LEDは一方向のみに発光するため、光はより効率的に ディスプレイに届きます。したがって、LEDバックライトは同 じ明るさでも低電力で済みます。また、LEDバックライトはディ スプレイの領域ごとにバックライトの明るさを(RGBのLEDを 使用すればバックライトの色も)変化させることができるため、 さらに電力効率に貢献できます。

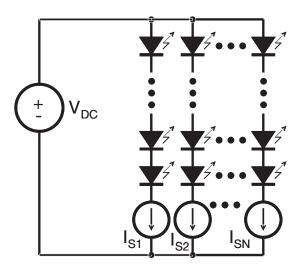

図18. 定電流ソースによるバックライトLEDドライバ

#### ■ 低電圧と少ないEMI

(Electro-Magnetic Interference、電磁妨害)

一般的なLEDバックライトはDC-DC電源で30~40V DCで済 みますが、CCFLバックライトでは300~400V ACのパワー・ コンバータが必要になります。シールドのないケーブル、低い DC電圧で済むため、EMI放射が抑えられます。

#### LEDバックライトのドライブ

LEDバックライトは、電気的にはLEDの順方向電圧(デバイス、 色によって異なりますが、一般的にLEDごとに2.5~3.5V)に等 しい固定電圧降下とモデル化でき、明るさはデバイスを流れる電 流量で制御できます。

最もシンプルな方法は、図17に示すように、電流制限抵抗とDC 電圧でバックライトをドライブします。LEDによって順方向電圧 は大きく異なるため、図18に示すように、シンプルな抵抗の代わ りに、直列接続したLEDごとに定電流ソースを入れることでこれ を改善することができます。

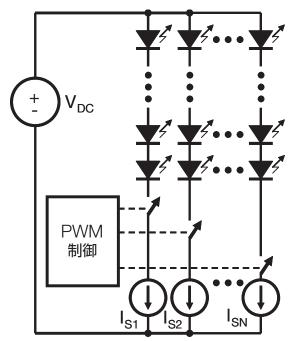

図19. 変調電流ソースによるバックライトLEDのドライブ

非常に明るいディスプレイ、小さな消費電力、非常に広いレンジ での光量制御などが求められるアプリケーションでは、別の方法 が必要になります。

人間の視覚システムの2つの特性を利用すると、DC電流はAC電流 に置き換えることができます。スイッチング周波数が約100Hz(ち らつきレート)を超えると、バックライトはちらつきとして認識 されなくなります。また、人間の目にはある程度の残像があるため、 時間に伴う平均光量に応答するのではなく、短時間における明る さのピークを覚える傾向にあります。このため、ピーク電流の デューティ・サイクルを調整することで、認識される明るさを制 御することができます。

図19に示すようなパルス幅変調(PWM)またはデューティ・サ イクル電流制御は、単純な定電流法に比べていくつかの利点があ ります。比較的大きなピーク電流でLEDを動作させて平均パワー・ レベルを抑えると、高い輝度として認識されます。LED電流の

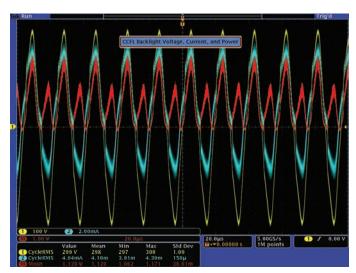

図20. MS04000シリーズで測定したCCFLバックライトのパワー測定例

デューティ・サイクルを調整することで輝度はコントロールでき るため、電源電圧を変化させることなく輝度をコントロールでき ます。これにより、設計エンジニアは回路のDC-DCコンバータの 効率を最適化できます。さらに、ピーク電流は変化しないため、 LEDは同じ電流レベル(例えば、白のLEDでは15~20mA)で 動作し、同じ色になります。

#### バックライト電力の測定

CCFL回路とLED回路ではバックライト・ドライバの電圧および 電流に大きな違いがあるため、異なる測定機器が必要になります。

図20に、オシロスコープを使用してCCFLバックライト回路を測 定した例を示します。AC電圧(黄色の波形)は約900V。っである ため、高電圧差動プローブが必要になります。この例では、テク トロニクスのP5200シリーズ高電圧差動プローブを使用していま す。電流レベル(シアンの波形)はmAレンジであるため、感度の 高い電流プローブが必要になります。この例では、テクトロニク スのTCPシリーズ電流プローブを使用しています。CCFL管の瞬 時消費電力は赤の波形で示され、平均で約1.1Wになります。

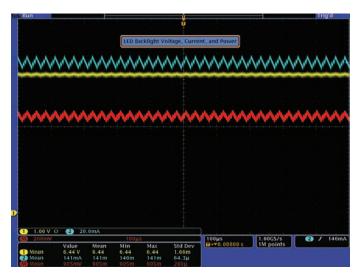

図21. MSO4000シリーズで測定したLEDバックライトのパワー測定例

一方、図21はLEDのバックライト回路の性能検証をオシロスコー プで行った例です。DC電圧(黄色の波形)は約6.4Vです。この 信号は、テクトロニクスのTDPシリーズ差動プローブで測定して います。電流レベル(シアンの波形)は数百mAのレンジです。 LEDの瞬時消費電力は赤の波形で示され、平均で約900mWにな ります。CCFLのバックライト回路に比べると、約200mWの節 約になっています。

ポータブル、バッテリ駆動のトレンドは継続しているため、LED ベースの液晶ディスプレイはCCFL方式に比べて大きなアドバン テージとなります。LEDのバックライトは、製品設計がシンプル になり、堅牢で軽いディスプレイにすることができ、電力を大幅 に抑えることができます。オシロスコープはLEDバックライトの 性能検証に必要なツールであり、測定値の統計から時間によるデ バイス性能の変化を観測することができ、電圧、電流のわずかな 変化を測定するための十分な感度も備えています。

## システムレベルでのエネルギー管理

DPM (Dynamic Power Management), DVS (Dynamic Voltage Scaling)、DFS (Dynamic Frequency Scaling) な どのエネルギー管理技術は、設計のシステムレベルにおける動作 を監視して消費電力を抑えます。システム動作におけるアイドル 時間の活用やケース・シナリオの使用により、アイドル状態のコン ポーネントをシャットダウンしたり (DPM)、個々のコンポーネン トのパフォーマンスを下げたり(DVS、DFS)して、特定のタス クに必要な最小限のパフォーマンスを提供することで消費電力を 抑えます。このようなエネルギー管理技術は、CPU、FPGA、 ASICなどの個々の処理回路デバイスだけでなく、デバイス間で データ伝送を行う通信バスにも適用されます。

## デジタル回路における電力消費

処理回路デバイスで消費する電力(PPE)は、処理回路デバイスがオン 状態にある時に常に発生する静的な電力消費(Pstatic)と、実際に 処理を実行するときに発生する動的な電力消費(Pdynamic)の2種類 があります。

$$P_{PE} = P_{static} + P_{dynamic}$$

静的な電力消費は、計算処理などが実行されていない場合でも発 生します。静的な電力使用には、リーク電流による電力消費Pleak とバイアス電流による電力消費Pbiasという、大きく分けて2種類の 要因があります。

動的な電力消費は、短絡回路(導通)電力消費Pscとスイッチング 電力消費Pswからなります。短絡回路の電力消費Pscは、電源電圧 に比例します。スイッチング電力消費Pswは、トランジスタのゲー トの寄生容量が充電され、計算処理などのタスクで放電されると きの消費です。

$$P_{PE} = \underbrace{P_{leak} + P_{bias}}_{P_{static}} + \underbrace{P_{sc} + P_{sw}}_{P_{dynamic}}$$

現在では、スイッチング電力消費Pswが電力使用のほとんどを占め ており、メインストリーム・プロセッシング回路で消費される約 90%になります。1つの処理回路のスイッチング電力消費は、一 般的に次の式で計算されます。<sup>2</sup>

$$P_{SW} = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f$$

ここで、

- α は、計算処理などのタスクで必要となるスイッチング・アク ティビティを表す係数

- C, は、設計の複雑さと回路技術で決まる定数で、想定される実 効回路負荷容量1

- V<sub>dd</sub>は、電源電圧

- fは、クロック周波数

上記の式は、スイッチング電力消費を抑える2つの方法を示唆して います。一つは処理回路の動作周波数を下げること、もう一つは 電源電圧を下げることです。スイッチング電力は $V_{

m dd}^2$ に比例するた め、回路の電源電圧を下げることが最も大きなエネルギー節約に なります。

場合によっては、電源電圧だけでなく、動作周波数も下げること でさらにエネルギーを節約することが可能になります。ただし、 動作周波数を下げると計算などの処理時間が長くなるため、注意 が必要になります。エネルギー消費は電力消費の時間累積である ため、タスク完了に要する時間が長くなるとエネルギーの節約に はなりません。しかし、周波数と電圧のスケールを適切に調整す ることにより、電圧スケールのみの場合に比べてより大きなエネ ルギー節約が可能になります。4

電源電圧を下げるとリーク電力消費も減るため、静的な電力消費3 の改善につながります。

#### ダイナミック・パワー・マネージメント (DPM)

DPMでは、演算などの処理回路と通信バスは、アイドルになって いる場合には常にスタンバイまたはスリープ・モードになります。 再度アクティブな状態にするには時間とエネルギーがかかるため、 DPMはシステム動作に違反しないよう、または再度アクティブに することで電力損失が増えないように注意を払います。たとえコン ポーネントがスタンバイ・モードでも、コンポーネントの静的電 力(P<sub>static</sub>)を消費します。

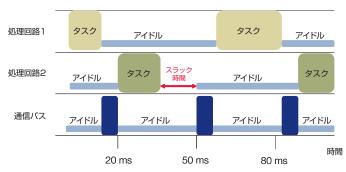

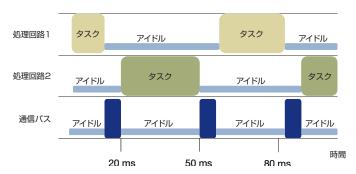

図22. 組込みシステム設計のシステム・スケジュールの例。このスケジュールの処 理回路2のスラック時間(余分な時間)では動的な電圧スケールを下げ、システム 性能に影響を及ぼすことなくエネルギー消費を抑えることができる。DPMは、アイ ドル時間でエネルギーを節約することができる

図23. 動的な電圧スケーリングでは、処理回路の動作周波数と電源電圧を下げるこ とで処理回路2のスラック時間をなくすことにより、エネルギー損失を抑える

#### 動的な電圧/周波数スケーリング

DVS、DFSでは、処理回路の電源電圧と動作周波数の下げる(ス ケールダウンする)ことで、スイッチング電力(Psw)消費を抑え ることができます。

DVSとDFSの例を図22に示します。この例では、システム・ス ケジュールは処理回路2がタスクを30msで完了することを許可し ています。しかし、処理回路2は過度の性能により15msでタスク を完了しており、15msのスラック時間ができてしまいました。 図23のように、タスクが30msで完了するように、この処理回路 の電源電圧と動作周波数を下げ、システム・スケジュールに合わ せます。これにより、処理回路2で消費されるエネルギーは抑えら れます。

DPMもまた、設計で利用することでエネルギー効率の改善につな がります。すべてのコンポーネントにDVS、DFSが適用され、シ ステム・スケジュールの実際の要求に性能を適合させたとしても、 まだアイドル時間があります。このような場合にDPMを使用する と、特定の時間アイドル状態のコンポーネントをシャットダウン することで、さらなるエネルギーの節約になります。

#### 通信バスのエネルギー損失

複数の処理回路を持つ組込みシステムでは、要素間の通信が重要 になります。通信バスでデータが転送されるごとにライン・コン デンサは充放電され、要素のI/Oピンから電流が流れます。この電 流による電力消費は、次の式で求められます。」

$$P_{CL} = \beta \cdot C_{bus} \cdot f_{bus} \cdot V_{tr}^2$$

ここで、

- B・Cは、バスの切り替えられる負荷容量

- f<sub>bus</sub>は、バスの動作周波数

- V<sub>r</sub> は、伝送電圧

通信バスでは、ノイズの問題があるため、低減できる伝送電圧は それほど大きくありません。低電圧の通信バスは、ノイズのため に信頼性問題の原因となることがあります。

DFSの場合と同様、バスの動作周波数またはデータ伝送レートは、 バス通信においてシステム・スケジュールにスラック時間がある 場合はスケール・ダウンすることができます。DPM同様、アイド ル時間ではバスはスタンバイ・モードにすることもできます。

| リンク・ステート                            | 概要                                     |

|-------------------------------------|----------------------------------------|

| LO - アクティブ・ステート                     | すべてのトランザクションは有効であり、リンクはノーマル・モードで動作している |

| LOs - 低いレジューム・レイテンシ、エネルギー・セーブ待機ステート |                                        |

|                                     | すべての電源とリファレンス・クロックはアクティブ               |

| L1 - 高いレイテンシ、低電力待機ステート              | TLPとDLLPの転送は無効                         |

| L2/L3 Ready - L2またはL3へのトランジション準備    | TLPとDLLPの転送は無効                         |

| L2 - Aux電源リンク、深いエネルギー・セーブ・ステート      | 主電源とリファレンス・クロックはオフ                     |

| L3 - リンク・オフ・ステート                    | 電源がない場合、リンクはこの状態にある                    |

表1. PCI Expressのパワー・ステート

Low Power DDR DRAMデバイスや、PCI Express®、MIPI® D-PHY/M-PHY、USB 3.0、Mobile PCI Express® Module (MXM)などの通信バスには、ロー・パワー・モードがあります。 以下に説明するように、適切な測定ツールがないとこれらのバス のデバッグ作業は難しいものになります。

## PCI Express のロー・パワー・モード

PCI Expressは、コンピュータや高性能電子機器で主流となって いるI/Oインターコネクト規格です。すでに第3世代に入っており、 PCI、PCI-X、AGPの3種類のI/Oバスと置き換わっています。 PCI Expressの仕様にはアクティブ・ステート電力管理機能があ り、バスをパワー・セーブ・リンク・ステートにしたり、システ ム要件にしたがって、任意の時点でリンク幅またはリンク・スピー ドを動的に設定したりすることで節電します。

この機能があるため、PCI Expressバスの機能検証はより複雑に なります。システムがパワー・セーブ・リンク・ステートに入っ たり、復帰したり、またはシステム要件にしたがってリンク幅や リンク・スピードが急激に変化する場合に問題が発生することが あります。

#### アクティブ・ステート電力管理

PCI Expressの仕様は、システム要件にしたがってリンク・パワー・ ステートを管理します。表1に、リンクがとり得るさまざまなパ ワー・ステートを示します。

トランスミッタとレシーバの同期を維持するためには、転送すべ きデータがない場合はIDLEシンボルをリンクに転送する必要があ ります。レシーバはこのIDLEシンボルをデコードして捨てます。 この期間のパワーを節約するには、リンクをパワー・セーブ・ステー トにします。セーブされる電力とLOに復帰するまでの時間は、リン ク·トランジションがLOからL3ステートになるにつれて増えます。

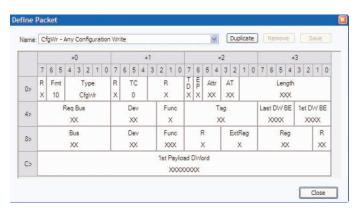

リンクの機能検証にアクティブ・ステート電力管理が加わること による複雑さを理解するため、PCI ExpressのリンクがLOsから LOの状態に遷移する場合を考えてみます。トランジション直後、 レジスタに間違った値を書き込むTLP Configuration Writeが発 生し、システムがクラッシュしました。この問題をデバッグする ため、LOsからLOステートまでのトランジションで発生したすべ てのトランザクションを取込む必要があります。

図24. PCI Express規格の定義と同様なレイアウトによる、TLAシリーズ・ロジッ ク・アナライザのトリガ機能

図26. TLAシリーズのフィルタ機能による、不要なデータのリアルタイム除去

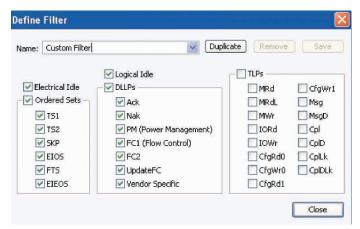

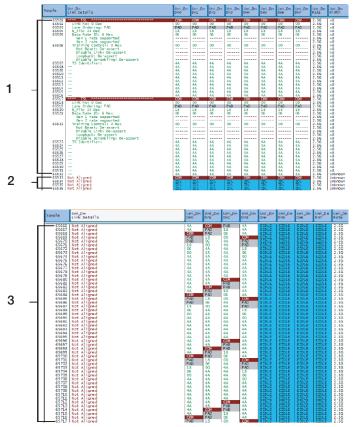

この例では、テクトロニクスのTLAシリーズ・ロジック・アナラ イザを使用して問題をトラブルシュートします。TLA7SAシリー ズ・モジュールのトリガ機能は、PCI Express仕様の定義と同様 なレイアウトになっています。これにより、特定のイベントに対 してロジック・アナライザのトリガをすばやく、簡単に設定でき ます。例えば、図24に示すように、バス、デバイス、機能番号に 基づくTLP Configuration writeでトリガするようロジック・ア ナライザを設定できます。

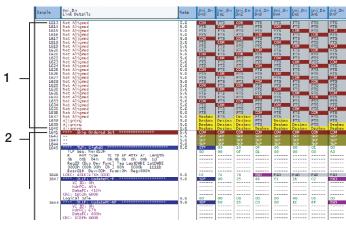

図25. テクトロニクスTLAシリーズによるバスのすべてのレーンのデータを関連付ける 1. TLAシリーズは、リンクが電気的アイドル状態を抜けるときのFTSパケットを表

- 2. データはSkip Ordered Setでレーン間スキューが調整される

- 3. リンクはElectrical Ordered Setを発行し、LOsに入る

トリガを設定すると、図25に示すように、TLA7SAシリーズは リンクがLOsステートを抜け、LOステートに入る際、約12の FTS (Fast Training Sequence) パケット内で、バスのすべて のレーンのデータにすばやくビット・ロックし、アラインするこ とができます。TLAはリンク・ステートの変化をすばやくトラッ クできるため、バスがLOステートに入った直後に発生するすべて のトランザクションを取込んで、システム・クラッシュの原因を 解析することができます。

TLAは、不要なデータをリアルタイムにフィルタリングすること もできるため、問題の部分のデータ取込みに集中することができ ます (図26を参照)。フィルタリングの一般的な用途は、PCI ExpressがIDLEステートにある場合です。IDLEシンボルをリア ルタイムにフィルタするようにフィルタ設定できるため、必要な データのみが保存でき、ロジック・アナライザのメモリを有効に 使い、問題のデバッグに関連したデータをより効率的に取込むこ とができます。

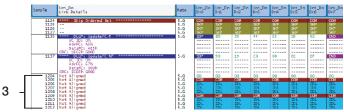

図27. TLAシリーズは、リンク・スピードまたはリンク幅の変化で発生するトレー ング・シーケンスにトリガし、取込むことが可能

- 1. リンク幅の変更に先立つトレーニング・シーケンスの終わり

- 2. リンクはアイドル状態に入る

- 3. トレーニング・シーケンスでリング幅の変更を完了

#### リンク・スピードとリンク幅の変更

PCI Expressの仕様では、電力の節約または状況に応じた性能に 対応するために、リンク幅またはリンク・スピードをダイナミッ クに変更できます。このようなリンク条件のダイナミックな変更 は、デバッグが難しくなります。

図28. トレーニング・シーケンスにトリガするための設定例

リンク幅がx8からx4に変更する例を考えてみます。TLAシリーズ・ ロジック・アナライザは、図27に示すようにリンク・スピード、リン ク幅のネゴシエーション・プロセスで発生するトレーニング・シー ケンスにトリガし、取込むことができるため、リンクが正しい幅 でトレーニングしていることを検証できます。

図28は、トレーニング・シーケンスにトリガするためのセットアッ プ例を示しています。リンクのエラーのために、必要なトリガ条 件が見つからない場合があります。このような場合は、最大16シン ボルのカスタム・シーケンスをトリガとして構築、任意のレーン で設定できます。このトリガ機能により、リンクにある問題を解 決するためにマニュアルでデータを検索する必要がありません。

図29. 物理レイヤのエラーを特定するためのリンク・イベント・トリガ・ダイアロ グの例

物理レイヤのエラー特定のため、TLAにはリンク・イベント・ト リガがあります。このトリガを使えば、ディスパリティ、 8B/10Bエラー、またはDLLPまたはTLPのフレーム・エラーが イベントとして検出できます。

PCI Expressの第2世代以降にはパワー・マネージメント機能が あり、パワー・セーブ・ステートやリンク幅/スピードをダイナミッ クに変化させる機能があります。この新しい機能のため、PCI Expressリンクのデバッグ、検証は難しくなっています。テクト ロニクスのTLAシリーズが持つエンハンスト・トリガ機能、フィ ルタ機能は、今日のPCI Expressリンクのアクティブ・ステート・ マネージメントにおける問題を簡単に検出します。

## LPDDR (Low Power Double Data Rate) メモリ

メモリは、設計のエネルギー・バジェットのほとんどの部分を消 費します。MDDR (Mobile DDR) とも呼ばれるLPDDR (Low Power Double Data Rate) メモリは、より効率的なデバイス動 作でこの問題に対処しています。このタイプのSDRAM (Synchronous Dynamic Random Access Memory) は、従 来の2.5Vではなく1.8Vで動作するため、省エネルギーに大きく 貢献します。

LPDDR DRAMは今日のポータブル電子機器で広く使用されてお り、低い動作電圧のためにバッテリ寿命に大きく貢献します。し かし近年、低消費電力が求められるAC電源を使用する電子機器の 設計エンジニアにとって、低パワーのDRAMデバイスはバッテリ 駆動のモバイル機器以上のアプリケーションとして魅力的になり ました。

動作電圧の低電圧化は、LPDDRだけでなく、メインストリームの メモリ技術におけるトレンドでもあります。当初、DDR2の仕様 では2.5Vでしたが、その後の開発により1.8Vになりました。同 様に、DDR3の発表時の電源電圧は1.5Vでしたが、新しいコンポー ネントでは1.35Vになっています。最新の低消費電力トレンドで は、LPDDR2の電源電圧はわずかに1.2Vです。

電源電圧を下げることは、メモリ・デバイスの消費電力を抑える 近道です。デバイスのパフォーマンスを最適化させることで、さ らなるエネルギーの節約が可能になります。LPDDRやその他の DDR規格では、システム要件にしたがってパフォーマンスを最適 化する、さまざまなパワー・セーブ・モードが規定されています。

#### LPDDRのパワー・セーブ・モード

LPDDR DRAMは、パワー・セーブ機能において大きく2種類の グループがあります。一つはデバイスがデータを維持する場合に 使用されます。もう一つのグループは、デバイスがデータ維持を 求められていない場合です。

#### アクティブ動作時のパワー・セーブ・モード

DRAMのセルはコンデンサであり、データは充電という形で保存 されます。コンデンサの電荷は放電されるため、データを維持す るためには、動作モードにおいて定期的に内容をリフレッシュす る必要があります。

LPDDR DRAMの仕様では、必要なデータ・ステートを維持しな がら電力損失を抑えるための3種類のリフレッシュ・モードが求め られています。

- ■「セルフ・リフレッシュ」は最も基本的なリフレッシュ・モード であり、低周期内蔵クロックを生成してDRAMの内容を保持し

- 温度補償型セルフ・リフレッシュは、LPDDR DRAMデバイス の温度に応じて内部のリフレッシュ・クロック周波数を自動的 に変更します。動作温度が低い場合は、リフレッシュ時間を延 して電力をセーブします。

- ■「パーシャル・アレイ・セルフ・リフレッシュ」は、DRAMの一 部のみのデータを保持します。

#### インタラクティブ動作時のパワー・セーブ・モード

LPDDR DRAMデバイスの内容保持が不要で、数秒間はDRAMへ のアクセスがない場合は、パワー・ダウン・モードが使用できます。

先にも説明したように、システムで消費される電力は $V_{td}^2$ と、クロッ クが遷移する周波数に比例します。LPDDR規格で規定されている 多くのパワー・セーブ・モードは、この電力式の周波数成分を利 用しています。パワー・セーブのリフレッシュ・モードは、クロッ ク周波数を落として消費電力を抑えます。パワー・ダウン・モー ドはDPMであり、非アクティブ期間においてDRAMをスタンバイ・ モードにします。これらすべてのパワー・セーブ・モードは、主 に静的な電力消費に影響します。

データ・スループットを最適化し、システムの性能要件に適合さ せながらデバイスの動作周波数を下げることで、動的な消費電力 を抑えることができます。この能力が、さまざまなLPDDR DRAAMデバイスにおける差別化につながります。

図30. JEDEC仕様適合性に対するリファレンス・レベル測定

#### LPDDR DRAMデバイスの検証

メモリ・デバイスの検証で必要となるジッタ、タイミング、電気的 な信号品質テストの詳細は、JEDEC (Joint Electron Device Engineering Committee) で規定されています。それぞれのメ モリ技術のJEDEC仕様で規定されているテストには、クロック・ ジッタ、セットアップ/ホールド時間、信号のオーバーシュート、 アンダーシュート、トランジション電圧などのパラメータなどの測 定が含まれています。規定されているテストの項目数が多いだけで なく、汎用のツールでは測定が複雑なものになります。

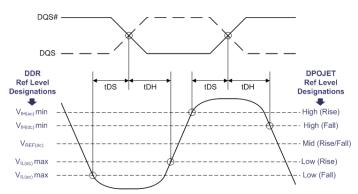

その一例が測定リファレンス・レベルです。JEDECの仕様では、 タイミング測定におけるリファレンス電圧レベルが規定されていま す。図30は、データ信号のタイミング測定で使用されるV<sub>1</sub>とV<sub>1</sub>レ ベル(ACおよびDC)を図示しています。立上りエッジと立下りエッ ジで使用するレベルが異なっていることにご注意ください。

JEDECで規定されている測定方法、リファレンス・レベル、パス/ フェイル・リミットなどは複雑であるため、DDRテストなどのア プリケーションに特化した測定ユーティリティがあると非常に便利 です。このような測定ユーティリティがあれば、汎用の計測ツール だけでは何時間もかかる測定セットアップが正しく行え、大幅な時 間短縮につながります。

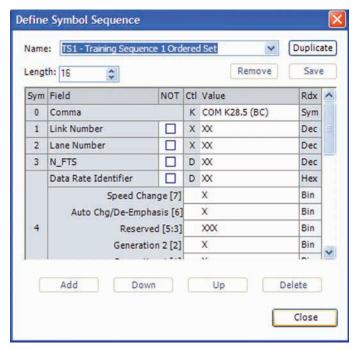

**図31**. DDRAセットアップ画面 - 手順1 (DDRの世代とスピードの選択)

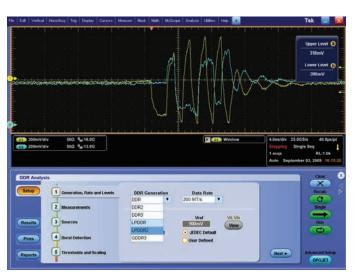

テクトロニクスのリアルタイム・パフォーマンス・オシロスコー プ用のOpt. DDRAは、DDRデバイスをテストするための専用自 動測定ソフトウェアです。DDRAには、JEDEC規格に準拠した数 多くの測定機能があるだけでなく、規格にないデバイスやシステ ムの実装の測定用にセットアップをカスタマイズできる機能も備 えています。

DDRAのメニュー・インタフェースには、選択形式による5つの ステップがあります。インタフェースのステップ1を図31に示し ます。ここでは、テストするDDRの種類(DDR、DDR2、 LPDDRなど)とメモリのスピードを選択します。デフォルトの選 択肢の他に独自のスピードを設定することができ、オーバークロッ キング・アプリケーションなど、将来の技術革新にもこのソフト ウェアによって簡単に対応できます。DDRの種類とデータ・レー トを選択すると、DDRAは測定のためのリファレンス電圧を自動 的に設定します。ここでも「User Defined」が選択でき、 JEDECのデフォルトを書き換え、必要に応じてV<sub>dd</sub>、V<sub>ref</sub>を任意の 値に設定することができます。

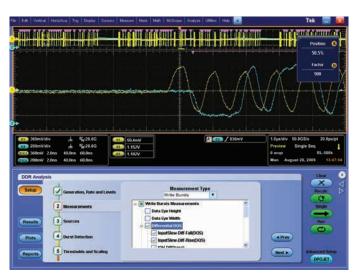

図32. DDRAのセットアップ画面 - ステップ2 (測定項目の選択)

ステップ2では、図32に示すように測定項目を選択します。測定 できる項目は、信号の種類、必要なプロービング接続にまとめら れてドロップダウン・メニューに表示されます。例えば、Clockラ インで実行する測定項目は、Clockドロップダウン・メニューにま とめられています。リードに関する測定、ライトに関する測定、 アドレス/コマンドに関する測定も同様にそれぞれのドロップダ ウン・メニューにまとめられているため、特定のプローブ接続を 必要とするすべての測定項目が1回でテストできるように選択でき ます。

DDRAメニュー・インタフェースの残りのステップ3と4では、必 要な信号にどのようにプロービングするかが示され、また測定リ ファレンス・レベルなどのパラメータのカスタム化、調整が行え ます。

設定を完了するとオシロスコープは信号取込みを開始し、データ・ バーストを識別し、必要に応じてマークを付け、選択された測定 を実行します。DDRAのResultsパネル(図33)には、統計値、 仕様のリミット値、パス/フェイルの結果、その他データなど、 すべての測定結果が表示されます。必要に応じて印刷形式のレポー トも作成でき、測定で使用した波形データを保存することもでき ます。

図33. 2つのグラフ表示を含むDDRAの測定結果画面

測定結果の元となる取込んだすべての波形データは保持されてい るため、さまざまな利用方法があります。仕様のリミット値から 外れた場合は、波形レコードのどこでフェイルになったかを特定 することができ、特定された領域をズーム表示することでフェイ ル時の信号の詳細とその特性を調べることができます。ソフトウェ アにはさまざまなツールが用意されており、取込んだデータが簡 単に解析でき、注目したい領域をピンポイントで特定することが できます。

最新のDDR DRAMは、消費電力を抑えるように、低い電源電圧 で使用されるように進化しています。このようなデバイスを検証 するためには、JEDECの仕様で規定されている数多くのテストを 実行する必要がありますが、時間がかかり、複雑な作業になります。 テクトロニクスのパフォーマンス・オシロスコープ用DDRAソフ トウェアには数多くの自動測定機能があるため、JEDEC仕様の適 合性が確認でき、メモリ・デバイスの検証が簡素化できます。電 圧のリファレンス・レベルなどの測定パラメータもカスタマイズ できるため、次世代の低電力デバイスもテストできます。

図34. MSO4000シリーズ・オシロスコープによる待機電力の測定例

## 待機電力

待機電力は、電源がオフになっていても消費され続けるわずかな 電力です。待機電力は、高速起動機能、時計が常に表示される民 生家電、バッテリ充電器などの電力変換デバイスなどにおける副 産物といえます。エネルギーは電力と時間の掛け算になるため、 待機電流が小さい場合でも長時間では大きなエネルギーを消費す ることになります。待機電力消費は、AC電源製品の電力消費、バッ テリを消耗させるという、2つの影響があります。

待機電力を抑えるためには、高効率のコンポーネントを使って慎 重に製品を設計し、瞬時の電源オン機能などを持たせつつ、独自 の電力モニタリング・ソフトウェアを使用して常に電力消費を抑 える必要があります。設計の検証、デバッグで待機電力を測定す るには低レベルの信号を長時間観測しなければならず、適切な測 定ツールがないと難しい作業になります。

## AC の待機電力/電流測定

待機状態に入る、または待機状態から抜けるときのデバイス電流 の測定にはオシロスコープを使用し、電流プローブでACライン電 流を直接測定するか、またはACラインのシャント抵抗の電圧降下 を差動プローブで測定します。AC入力電圧は、高電圧差動プロー ブまたはフローティング・オシロスコープを使用することで安全 に測定できます。

#### PCモニタの待機電流

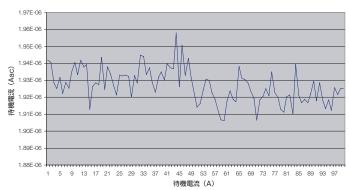

図35. Microsoft Excelで表示した、DMMシリーズ・マルチメータによる待機電

オシロスコープは、電流と電圧の波形を掛け算することで瞬時電 力を計算します。高いサンプル・レートとロング・メモリのオシ ロスコープを使用し、テクトロニクスのオシロスコープが持つ HiRes (ハイレゾ) ボックスカー・アベレージングなどのデジタ ル信号処理機能を使うと、長時間にわたる高分解能測定が可能に なります。図34は、コンピュータのLCDディスプレイの入力を測 定した例であり、電圧(黄色の波形)と電流(青の波形)が測定 されています。赤の波形は、計算で求められた瞬時電力です。オ シロスコープは、波形の各サイクルの実効値による電圧、電流、 平均電力を計算します。測定の統計値には、これらの測定のワー ストケースによる変動、平均、標準偏差が含まれ、さらには32種 類の測定も実行できます。

待機モードの信号は低レベルなため、DMM (デジタル・マルチメー 夕)を使用する場合は、高分解能な静的電流測定が必要になります。 ACライン電流は、DMMを回路に直列に接続して測定するか、直 列に接続した外付シャント抵抗の電圧降下を測定することで求め ます (図35)。待機モードの電流波形形状は、正弦波からはかけ 離れているため、真の実効値を測定できるDMMやパワーアナライ ザが必要です。AC実効値電圧は安定する傾向にあるため、AC電 流が正確に測定できれば、待機電力が予測できます。

DMMは実効値電流など、通常は単一の数値表示に使用されます。 しかし、テクトロニクスのDMMシリーズなどの高性能ベンチ DMMは繰り返し測定した値をログしたり、エクスポートしたりす ることができます。さらにTrendPlot™機能により、時間ととも に変化する測定値のグラフをDMMのディスプレイに表示できるも のもあります。

図36. DMMシリーズ・マルチメータによる、ナノアンペアの電流測定手法

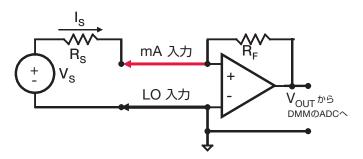

## ナノアンペアの DC 電流測定

待機バッテリ電流などの最も感度が必要とされる電流測定では、マ イクロアンペア以下のレンジが必要になることがありますが、テク トロニクスのDMMシリーズにはナノアンペアのDC電流測定レン ジ設定があり、非常に小さな信号を高い分解能で測定できます。

回路にシャント抵抗を加えることで生ずる電流測定誤差を防ぐた め、図36に示すように、2000 $\mu$ Aと200 $\mu$ Aのレンジでは電流 - 電圧コンバータ回路が使用されます。回路の入力部には仮想(フ ローティング)グランドがあり、電圧は電流 $I_s$ ( $V_{OUT} = -I_s \times R_F$ ) に比例するため、InAまでの分解能による正確な測定が可能にな ります。

製品の仕様検証、業界規格のプリコンプライアンス・テスト、ま たはバッテリ寿命の予測など、待機電力の測定は難しい作業です。 設計した回路の待機モードにおける消費電力を正確に測定するた めには、低レベルの信号を長時間測定する必要があります。ロング・ メモリ、高いサンプル・レート、優れた信号処理機能を備えたオ シロスコープがあれば、時間の変化に伴う設計性能の数多くのパ ラメータをトラックすることができます。焦点を絞った解析では、 デジタル・マルチメータやパワーアナライザを使用することで高 分解能の静的電流測定が行えます。これらを組み合せることで、 待機電力測定の総合測定ツールとなります。

図37. 高効率エネルギー設計をテストするための優れたツールである、オシロス コープ、ロジック・アナライザ、リアルタイム・スペクトラム・アナライザ、TDR (Time Domain Reflectometer)、信号ジェネレータ、デジタル・マルチメータ、 プローブ、解析ソフトウェア

## まとめ

エネルギー効率の良い設計技術では、新しく、難しいテスト課題 があり、設計エンジニアは数多くの難しい測定を行い、高速に変 化する信号、複雑なプロトコル、微小電圧/電流をトラブルシュー トしなければなりません。

このような設計を検証、デバッグ、特性評価するためには、強力 で総合的な測定ツールが必要になります。オシロスコープ、ロジッ ク・アナライザ、プローブ、信号ジェネレータ、マルチメータ、 パワーアナライザがこれにあたります。自動測定ソフトウェア・ パッケージも、複雑な測定を簡素化するために重要となるツール の一つです。

昨今の設計は高いレベルのエネルギー効率に達していますが、適 切な測定ツールを使用することで、最新の設計検証、デバッグの ための複雑な作業を簡素化でき、迅速に実行できます。

## 参考文献

- Marcus T. Schmitz, Bashir M. Al-Hashimi and Petru Eles. System-level Design Techniques for Energy-Efficient Embedded Systems. Kluwer Academic Publishers, 2004.

- Anantha P. Chandrakasan and Robert W. Brodersen. Low Power Digital CMOS Design. Kluwer Academic Publisher, 1995.

- 3. S. Martin, K. Flautner, T. Mudge, and D. Blaauw.

Combined Dynamic Voltage Scaling and Adaptive Body

Biasing for Lower Power Microprocessors under

Dynamic Workloads. In Proceedings IEEE/ACM

International Conference Computer-Aided Design

(ICCAD-02), pages 721 725, 2002.

- 4. J. Taylor. Maximize Processor Energy Savings in Media-intensive Mobile Devices with Adaptive Voltage Scaling. Mobile Handset DesignLine, 2007.

- 5. L. Ternullo. Maximizing a Low-Power Memory Interface IP Subsystem. Chip Design Magazine, 2009.

- 6. M. Greenberg. LP-DDR: How Much power Will a Low-Power SDRAM Save You? Denali Application Note, 2009.

ASEAN/オーストラリア・ニュージーランドと付近の諸島 (65) 6356 3900 ベルギー 00800 2255 4835\* 中央・東ヨーロッパ、パルト海諸国 +41 52 675 3777 フィンランド・41 52 675 3777 香港 400 820 5835 日本 0120 441 046 中東、アジア、北アフリカ +41 52 675 3777 中国 400 820 5835 諸国 001 800 8255 2835 スペイン 00800 2255 4835\* 台湾 886 (2) 2722 9622

オーストリア 00800 2255 4835\* ブラジル +55 (11) 3759 7627 中央ヨーロッパ ギリシャ +41 52 675 3777 ブランス 00800 2255 4835\* インド 000 800 650 1835 ルクセンブルク +41 52 675 3777 オランダ 00800 2255 4835\* ボーランド +41 52 675 3777 ロシアン(515 +7 (495) 7484900 スウェーデン 00800 2255 4835\* イギリス/アイルランド 00800 2255 4835\*

\* ヨーロッパにおけるフリーダイヤルです。ご利用になれない場合はこちらにおかけください。+41 52 675 3777 Updated 10 February 2011 バルカン諸国、イスラエル、南アフリカ、その他SE諸国 +41 52 675 3777 カナダ 1 800 833 9200 デンマーク +45 80 88 1401 ドイツ 00800 2255 4835\* イタリア 00800 2255 4835\* メキシユ、中央・南アメリカ、カリブ海諸国 52 (55) 56 04 50 90 ノルウェー 800 16098 ボルトガル 80 08 12370 南アフリカ +41 52 675 3777 スイス 00800 2255 4835\* アメリカ 1 800 833 9200

〒108-6106 東京都港区港南2-15-2 品川インターシティ B棟6階 ヨッlgい オシロテクトロニクス お客様コールセンター TEL:0120-441-046電話受付時間/9:00~12:00~13:00~18:00(土・日・祝・弊社休業日を除く)

# jp.tektronix.com