## MIPI Physical Layer Test Solutions D-PHY and M-PHY

#### KE Lee Application Engineer Manager

### Agenda

- MIPI<sup>®</sup> Technologies

- D-Phy testing

- Tx

- Scopes-Decode: CSI, &DSI

- Rx

- M-Phy testing

- Tx (New update Mar'12)

- Scopes-Decodes:, 8b-10b, DigRF, LLI (New), & UniPro (New)

- Rx

- Summary, Q&A

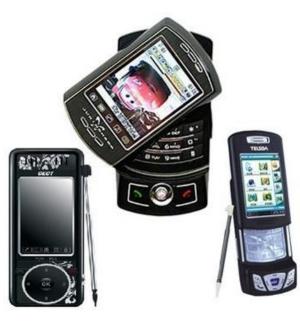

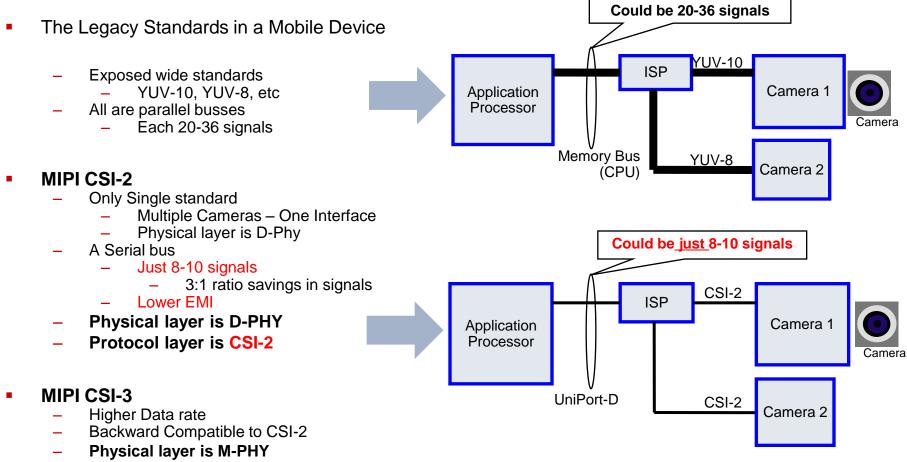

#### MIPI Technologies Overview Example of a Mobile Platform

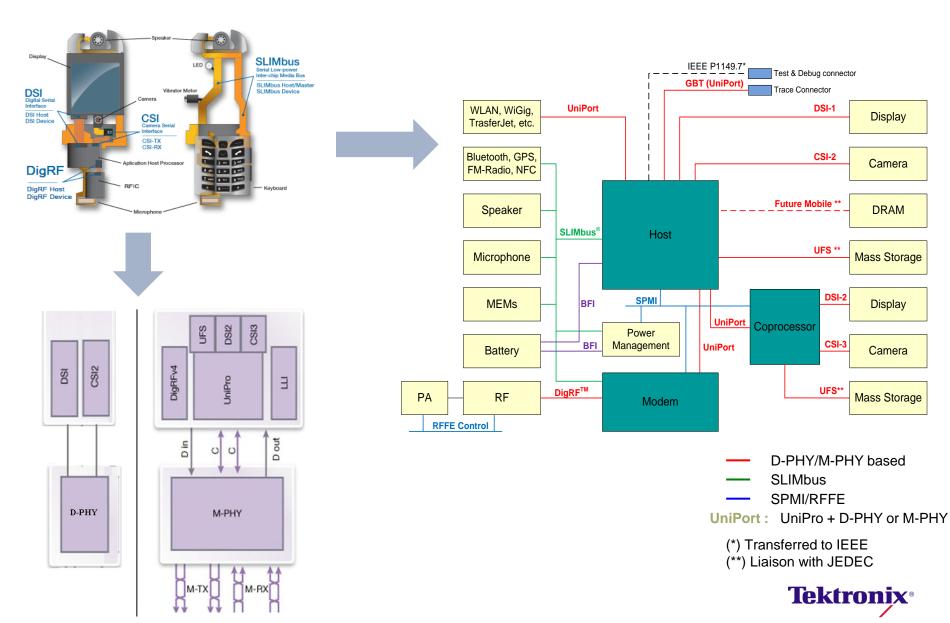

### What is D-PHY ?

- It's a PHY standard for interfacing Camera (CSI) & Display (DSI)

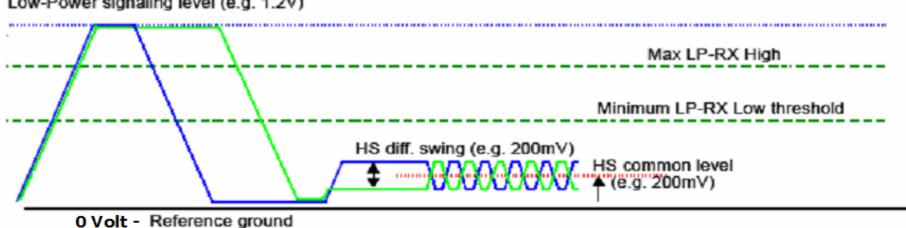

- Two modes of transmission

- High Speed (HS) and Low Power (LP)

- Modes are mixed during the operation

- Transitions from LP to HS and back to LP on the fly

- Maximum Data Rate

- High Speed mode: 80 Mbps 1 Gbps, Typically at ~500 Mbps.

- Low Power mode: Up to 10 Mbps

- **Bus termination**

- 50 ohms in HS

- Hi-7 in I P

Tektronix

Low-Power signaling level (e.g. 1.2V)

#### **D-PHY Testing Challenges**

- Logo testing is not required, but Optional.

- MIPI is Chip-to-Chip/ Chip-to-Peripheral interface, similar to a DDR bus.

- Mobile Phones do not need compliance logo, unlike USB/SATA devices

- No two MIPI devices are the same

- Variable Data Rates

- Up to 4 lanes of Data traffic,

- Multiple different data formats

- Specification enables custom limits.

- Characterization is significantly important

- Mobile OEMs select the suppliers based on characterization reports.

Tektron

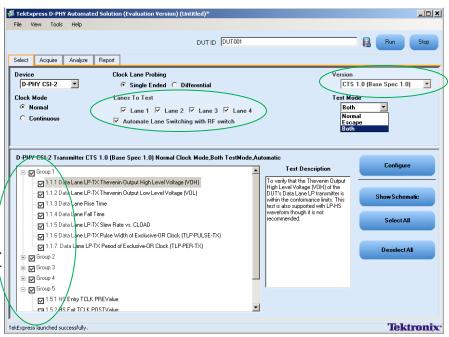

#### Many measurements – 49

- Clock Lane

- Data Lane

- Clock data Timing

- Test Equipment & Setups need to be Very Flexible

#### D-PHY Tx : Opt.D-PHYTX Conformance Test Solution

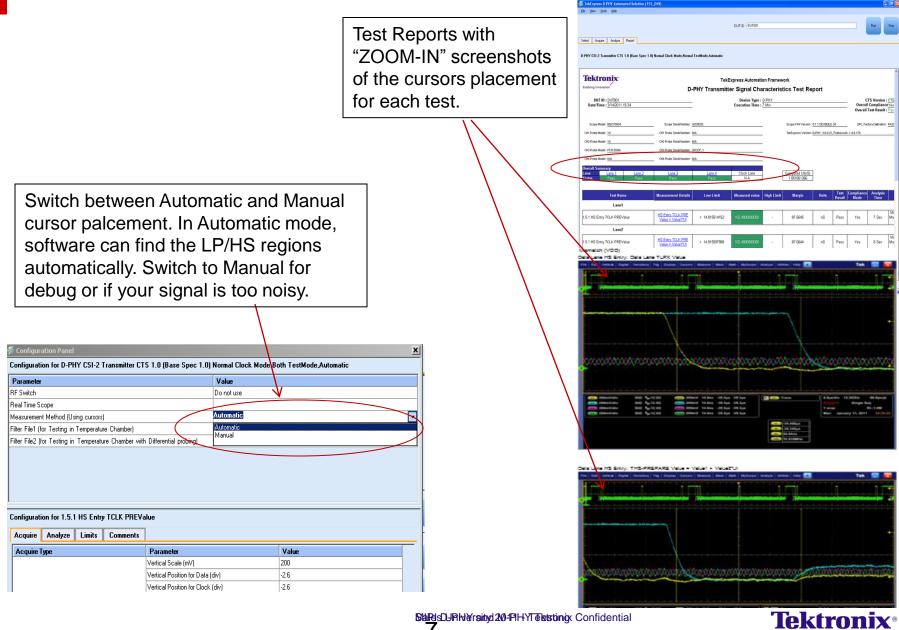

#### Opt.D-PHYTX : D-PHY Automated Solution

- TekExpress option for Fully-Automated testing

- Provides Conformance and Characterization Testing

- Based on Latest D-PHY Base Spec <u>v1.0</u> and UNH's Conformance Test Suite <u>v1.0</u>.

- Runs on 7K/C and 70K/B/C scopes

- Opt.TEKEXP is Pre-Requisite

- Differentiation

- <u>**Un-parallel**</u> Automation (Auto-Cursors)

- 100% Widest Test Coverage

- Conformance to Latest CTS (v1.0)

- Based on Latest Base spec (v1.0)

- Fully-Automated for Multi-lane DUTs

- Fully-Automated Temperature Chamber

- Value proposition

- Custom-limits/ Limits-Editing

- Test Reports with Pass/Fail summary, margins, & "Zoom-in" Waveform Captures

- Tek 3.5GHz scope is the minimal configuration for accurate testing

- D-PHY extension spec (1.5G) ready

Tektronix

#### D-PHY Tx : Opt.D-PHYTX Features

#### D-PHY Tx : New 1.5G Data Rate Extension Spec v1.01 Spec Draft is Ready. Expected to be released for adaption in late-CY11

- Both Opt.D-PHYTX and Opt.D-PHY are Fully-Supported.

- All Measurement Algorithms remain same

- Only "Limits" vary for following Five parameters for 1.5G datarate.

- 1. HS rise/fall time (tr, tf),

- 2. VOD mismatch (dVOD),

- 3. TX data to clock skew (TSKEW[TX]),

- 4. RX setup and hold times (TSETUP[RX], THOLD[RX]),

- 5. TX/RX return loss (SddTX, SddRX).

- Both Opt.D-PHYTX and Opt.D–PHY support Limits Editing today.

- Tektronix is involved in the D-PHY 1.5G Extension discussions.

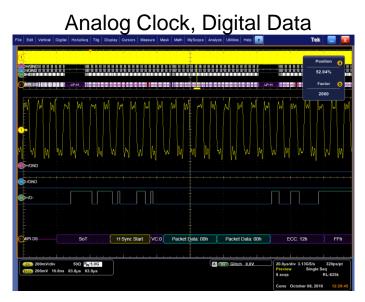

#### D-PHY Decode: Opt.SR-DPHY for DSI/ CSI-2 Decode Simultaneous Acquisition

- Probe using Analog, Digital or Mixed Channels

- Simultaneous probing of DSI &CSI using MSO channels

- Working on multi-lane support, using high performance MSO digital channels

- Supported on all 7KC, 70KC and MSO70K scopes. (Win7-OS only)

- Option key bit #25

- Software installed as part of TekScope firmware v6.1.2.4 or later.

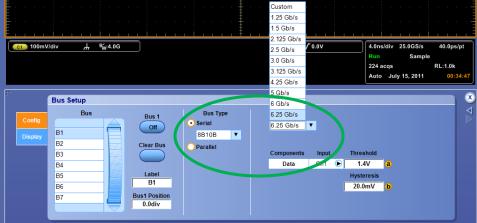

- Browse to TekScope Menu --> Vertical --> Bus Setup --> Select Bus Type as Serial-- > Select MIPI DSI or CSI from the drop down list.

Probe using Mixed Channels

Digital Clock, Analog Data

**Tektronix**<sup>®</sup>

#### D-PHY Tx & Decode: Recommended Test Setup www.tek.com/MIPI

- Scope

- DPO7354 or DPO/DSA/MSO70404/B/C or higher for rise time accuracies

- Probes

- For 7Ks: 4x TAPxx/ P6245/ P6249, or 4x TDP3500 (clock is noncontinuous), or 3x TDP3500 (clock is continuous).

- For 70Ks: 4xP7240, or 4xP73xx (clock is non-continuous), or 3xP73xx (clock is continuous).

- Scope Software

- Opt.D-PHYTX on TEKEXP for Conformance Test

- Opt.D-PHY on DPOJET for Debug, Analysis & Characterization

- Opt.SR-DPHY for Decode of CSI &DSI traffic

- Fixtures

- As MIPI is a chip-to-chip interface, most DUT setups are LIVE with Master Slave Receiver-end connected.

- For live-setups: No Fixtures required.

- For non-live setups:

- No standard fixture is defined.

- We recommend following UNH-IOL Termination boards:

www.iol.unh.edu/services/testing/mipi/MIPI Test Fixture Order Form.doc

P7380 probe used with a probe-tip

0 probe used with a probe-tip **Tektronix**

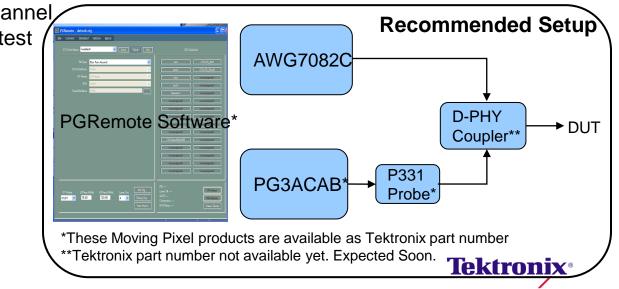

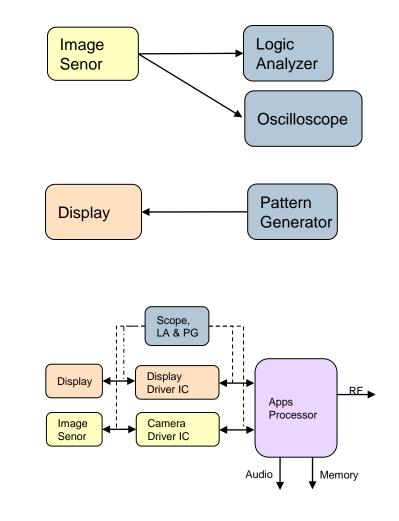

### **D-PHY Rx : Test Solution Overview**

Simple, Quick, Easy and Re-usable

- 100% Coverage to Rx CTS

- Meets all the requirements in UNH-IOL CTS document (v0.98)

- Quick and Easy setup

- No complex VXI system, just stand alone instruments, and a probe.

- Cost effective solution

- 70% Lower list price vs Competition

- Re-usable for Protocol tests

- PG3A is the Only 4 channel solution for CSI &DSI test

- PG3A Pattern Generator

- Controls clock and signaling to establish link with DUT

- Adjusts voltage levels, packet type, etc to stress test receiver

- AWG7082C Generator

- Adds jitter and interference to the D-PHY signals

#### D-PHY Rx : Test Solution Overview 100% Test Coverage

| Group 1 LP - RX voltage and timing requirements |                                                                                    |      |                            |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------|------|----------------------------|--|--|--|--|--|--|

| Test                                            | Title                                                                              | Page | Equipment                  |  |  |  |  |  |  |

| 2.1.1                                           | LP - RX Logic 1 Input Votage (V <sub>IN</sub> )                                    | 108  | PG                         |  |  |  |  |  |  |

| 2.1.2                                           | LP - RX Logic 0 input Voltage, non-ULP State (V <sub>1</sub> )                     | 110  | PG                         |  |  |  |  |  |  |

| 2.1.3                                           | LP - RX Logic 0 input Voltage, ULP State (VLCLPS)                                  | 112  | PG                         |  |  |  |  |  |  |

| 2.1.4                                           | LP - RX Minimum Pulse Width Response (T <sub>MMX</sub> )                           | 113  | PG                         |  |  |  |  |  |  |

| 2.1.5                                           | LP - RX Input Hysteresis (Tevas)                                                   | 114  | PG                         |  |  |  |  |  |  |

| 2.1.6                                           | LP - RX Input Pulse Rejection (epse)                                               | 116  | PG + AWG + DC Power Supply |  |  |  |  |  |  |

| 2.1.7                                           | LP - RX Interference Tolerance (V_{tot} and $f_{tot})$                             | 120  | PG + AWG                   |  |  |  |  |  |  |

| 2.1.8                                           | LP - CD Logic Contention Thresholds $(V_{\text{HCD}} \text{ ans } V_{\text{LCD}})$ | 122  | PG + AWG                   |  |  |  |  |  |  |

#### Group 2 LP - RX Behavioral Requirements

| Test  | Title                                                                   | Page | Equip |

|-------|-------------------------------------------------------------------------|------|-------|

| 2.2.1 | LP - RX Initialization Period (T <sub>NR</sub> )                        | 125  | PG    |

| 2.2.2 | ULPS Exit: LP - RX T <sub>maxin</sub> , Timer Value                     | 126  | PG    |

| 2.2.3 | Clock Lane LP - RX Invalid/Aborted ULPS Entry                           | 127  | PG    |

| 2.2.4 | Data Lane LP - RX Invalid Aboted Escape Mode Entry                      | 128  | PG    |

| 225   | Data Lane LP - RX Invalid/Aboted Escape Mode Command                    | 130  | PG    |

| 2.2.6 | Data Lane LP - RX Escape Mode Invalid Exit (Informative)                | 132  | PG    |

| 2.2.7 | Data Lane LP - RX Escape Mode, ignoring Post Trigger-Command Extra Bits | 134  | PG    |

| 2.2.8 | Data Lane LP - RX Escape Mode Unsopported/Unassigned Commands           | 136  | PG    |

| Group 3: HS - RX Voltage and Setup/Hold Requirements |                                                                  |      |           |  |  |  |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------|------|-----------|--|--|--|--|--|--|

| Test                                                 | Title                                                            | Page | Equipment |  |  |  |  |  |  |

| 2.3.1                                                | H8 - RX Common Mode Voltage Tolerance (V <sub>cNRX(pc</sub> )    | 139  | PG        |  |  |  |  |  |  |

| 2.3.2                                                | H8-DX Differential Input High Threshold (V <sub>pre</sub> )      | 141  | PG        |  |  |  |  |  |  |

| 2.3.3                                                | H8-DX Differential Input Low Threshold (View)                    | 143  | PG        |  |  |  |  |  |  |

| 2.3.4                                                | H8 - RX Single-Ended input High Voltage (V <sub>HH8</sub> )      | 144  | PG        |  |  |  |  |  |  |

| 2.3.5                                                | H8 - RX Single-Ended Input Low Voltage (VL+s)                    | 146  | PG        |  |  |  |  |  |  |

| 2.3.6                                                | H8 - RX Common Mode Interference S0MHz - 450MHz (deta VCMRX(LF)) | 148  | PG + AWG  |  |  |  |  |  |  |

| 2.3.7                                                | H8 - RX Common Made Interference Beyond 450MHz (delts VCMRX(HF)) | 150  | PG + AWG  |  |  |  |  |  |  |

| 2.3.8                                                | H8 - RX SetupHold and Jiter Tolerance                            | 151  | PG + AWG  |  |  |  |  |  |  |

| Group A: I                                           | U.C., DV Timor Poquiromente                                      |      |           |  |  |  |  |  |  |

#### Group 4: HS - RX Timer Requirements

| Test No. | Title                                                                        | Page | Equipment |

|----------|------------------------------------------------------------------------------|------|-----------|

| 2.4.1    | Data Lane H8 - RX To-mexes Value                                             | 156  | PG        |

| 2.4.2    | Data Lane HS - RX T <sub>KS + KS + KS</sub> + T <sub>KS + KS</sub> Tolerance | 158  | PG        |

| 2.4.3    | Data Lane HB - RX T <sub>HMATTA</sub> Value                                  | 160  | PG        |

| 2.4.4    | Data Lane HB - RX T <sub>KE-WAL</sub> Tolerance                              | 162  | PG        |

| 2.4.5    | Data Lane HB - RX T <sub>KI4KP</sub> Value                                   | 164  | PG        |

| 2.4.6    | Clock Lane H8 - RX T <sub>CLK BANAN</sub> Value                              | 166  | PG        |

| 2.4.7    | Clock Lane H8 - RX T <sub>CLK#REALE</sub> + T <sub>CLKGRO</sub> Tolerance    | 167  | PG        |

| 2.4.8    | Clock Lane H8 - RX T <sub>currana</sub> Value                                | 169  | PG        |

| 2.4.9    | Clock Lane H8 - RX T <sub>ELKMAL</sub> Tolerance                             | 171  | PG        |

| 2.4.10   | Clock Lane H8 - RX T <sub>CLKMB3</sub> Value                                 | 173  | PG        |

| 2.4.11   | Clock Lane H8 - RX T <sub>cukees</sub> + T <sub>cukees</sub> Tolerance       | 175  | PG        |

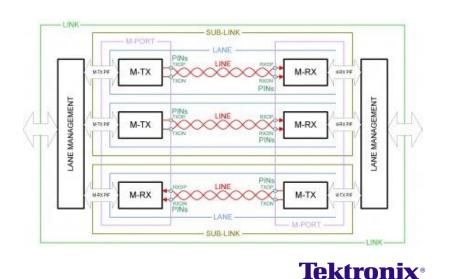

### What is M-PHY ?

- M-PHY is a high-speed serial interface to the DigRFv4, UniPro, LLI, CSI-3 and DSI-2 interconnect standards of the MIPI Alliance, and the UFS and SSIC protocol standards of JEDEC and USB-IF respectively.

- M-PHY is a flexible architecture that allows the implementer to support high data rates at minimal power, cost & I/O redesign, for applications such as High Definition Video

- A Fast, Scalable, Serial Communications Architecture

- Link Connects M-PHY Transmitter to an M-PHY Receiver

- Sub-link Manage one or more lanes

- Lane Operation defined in the protocol (DSI, CSI, UniPro, DigRF)

### **M-PHY Testing Challenges**

| M-PHY Signal Characteristics |       |            |            |                              |                                                            |                             |                |  |  |  |

|------------------------------|-------|------------|------------|------------------------------|------------------------------------------------------------|-----------------------------|----------------|--|--|--|

| Signaling mode               |       | Datarate   | es         | Amplit                       | udes                                                       | Impedance                   |                |  |  |  |

|                              | Gears | A (Gbps)   | B (Gbps)   | Large                        | Small                                                      | <b>Resistive Terminated</b> | Non Terminated |  |  |  |

|                              | G1    | 1.25       | 1.45       |                              |                                                            |                             |                |  |  |  |

|                              | G2    | 2.5        | 2.91       |                              |                                                            | 50 ohms                     | -              |  |  |  |

| High Speed (HS)              | G3    | 5          | 5.83       |                              |                                                            |                             |                |  |  |  |

|                              | Gears | Min (Mb/s) | Max (Mb/s) |                              | Terminated: 100-<br>130mV,<br>Non-Terminated:<br>200-260mV |                             |                |  |  |  |

|                              | G0    | 0.01       | 3          |                              |                                                            |                             |                |  |  |  |

|                              | G1    | 3          | 9          | Terminated:                  |                                                            |                             |                |  |  |  |

|                              | G2    | 6          | 18         | 160-240mV,                   |                                                            |                             |                |  |  |  |

|                              | G3    | 12         | 36         | Non-Terminated:<br>320-480mV |                                                            | 50 ohms                     | 10k ohms       |  |  |  |

|                              | G4    | 24         | 72         | 520-460III v                 |                                                            |                             |                |  |  |  |

|                              | G5    | 48         | 144        |                              |                                                            |                             |                |  |  |  |

|                              | G6    | 96         | 288        |                              |                                                            |                             |                |  |  |  |

| PWM (ie. TYPE-I)             | G7    | 192        | 576        |                              |                                                            |                             |                |  |  |  |

| SYS (ie. TYPE-II)            |       |            | 576 (Mb/s) |                              |                                                            | 50 ohms                     | 10k ohms       |  |  |  |

- Higher data rate will increase importance of Signal Integrity of links

- More emphasis on timing/jitter and noise (signal integrity)

- Receiver testing will be needed to stress-test resulting BER

- Number of Measurements

- Termination Restive or not Terminated.

- LS mode can operate either of them

- HS mode it is always terminated, so swings are halved.

- Type-I and Type-II are Low speed modes, and are NOT interoperable

- Type-I operates on independent local clocks. Type-II requires a shared Ref-clock.

Tektroniz

DUTs may support both

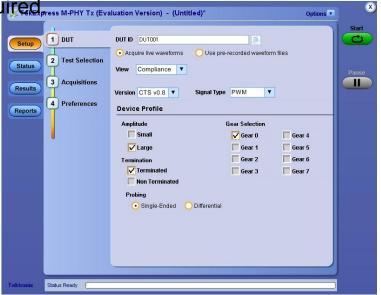

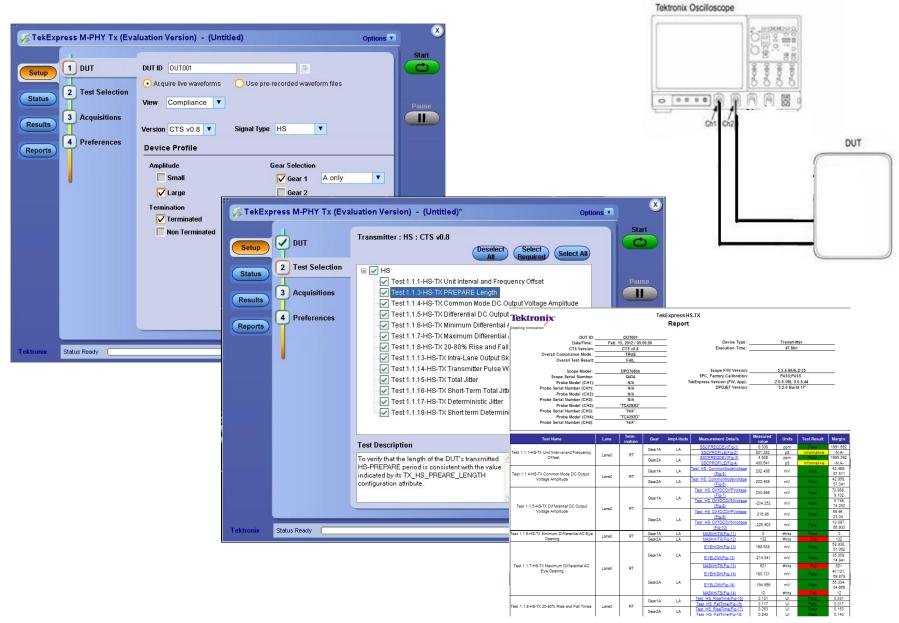

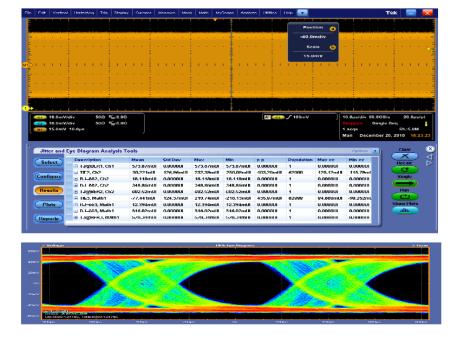

#### M-PHY Tx : New Opt.M-PHYTX Automated Solution

#### • Opt.M-PHYTX

- TekExpress (2.0) option for Single-button Automated transmitter testing

- Provides Conformance & Debug Testing to the latest M-PHY Base Spec v1.0 &UNH's Conformance Test Suite.

- Runs on DPO/DSA70KB/C/D or MSO70K/C scopes (6GHz and above)

- TekExpress framework &license is included.

- Opt.DJA is pre-requisite. Opt.M-PHY not required, press M-PHY Tx (Evaluation Version) (Untitled)

- Differentiation

- Most Complete Test coverage

- (95% HS, 74% PWM).

- Seamless Debug on failures.

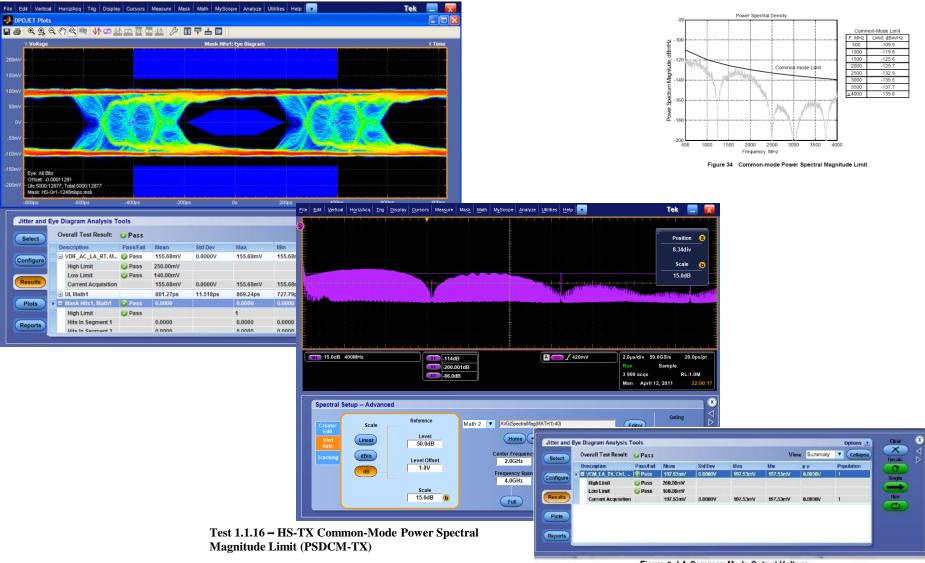

- Scope-based Power-Spectral Density tests

- Value proposition

- For Gear2 M-PHY Tx testing, Tek 8GHz oscilloscope is sufficient. Where as, competition recommends a 12GHz or 13GHz oscilloscope.

- For Gear3 M-PHY Tx testing, Tek 20G oscilloscope is sufficient. Where as, competition recommends a 25GHz oscilloscope.

Tektronix

### M-PHY Tx : New Opt.M-PHYTX Automation Features

| Key Feature                     | Benefit                                                                                                                                                                                                                                                                          |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automated<br>Testing            | <ul> <li>Reduces the complexity of testing transmitter tests</li> <li>Reduces testing time, and enables you to test devices faster</li> <li>Automates apprx 700 tests in regression, in different combinations of Gears,<br/>Sub-Gears, Terminations, Amplitudes, etc</li> </ul> |

| Most Complete<br>Tests coverage | <ul> <li>Automates 95% of High Speed, and 75% of PWM tests</li> </ul>                                                                                                                                                                                                            |

| Highly Optimized<br>Setup       | <ul> <li>Performs Power Spectral Density (PSD) Tests using Oscilloscope-integrated<br/>Algorithms Uniquely,</li> <li>Does not require an External Spectral Analyzer or Extra Hardware to<br/>Perform PSD Measurements</li> </ul>                                                 |

| Seamless Debug                  | <ul> <li>Allows Pause on a Test while in Automation, and Switch to DPOJET<br/>Analysis Tool for Detailed Debug of failures</li> </ul>                                                                                                                                            |

| Setup<br>Configuration          | <ul> <li>Allows Selecting Different Gears and Sub-gears of HS and PWM Signals,<br/>Large/Small Amplitudes, Impedance Termination/Un-termination</li> </ul>                                                                                                                       |

| Test reports                    | <ul> <li>Provides Single Printable Report, across Different Combinations</li> <li>Provides Pass/Fail Summary Table, along with Margin Details, Optional Waveform Captures, and Eye Diagrams</li> </ul>                                                                           |

#### M-PHY Tx : New Opt.M-PHYTX Automation Features

**Tektronix**<sup>®</sup>

# M-PHY Tx: Opt.M-PHYTX/ Opt.M-PHY Testing Solution Eye Diagram, Power Spectral Density & Common Mode Meas. Examples

Figure 9: LA Common Mode Output Voltage

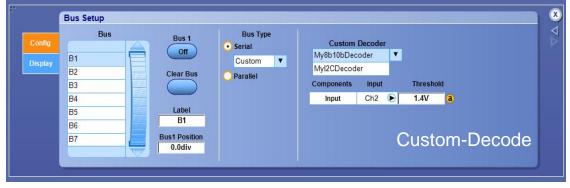

#### M-PHY Decode: Opt.SR-810B for 8b-10b Decode

- Decode into Symbols or 10-bit Characters

- Decode upto 6.25Gb/s Datarate

- Trigger & Search on

- Any Control Character

- Character/ Symbol

- Pattern

- Error (Character Error & Disparity E

- Custom-Decode upto 6.25Gb/s datarate

- Supported on all 70KC and MSO70K scopes.

- Software installed as part of TekScope firmware

**Tektronix**<sup>®</sup>

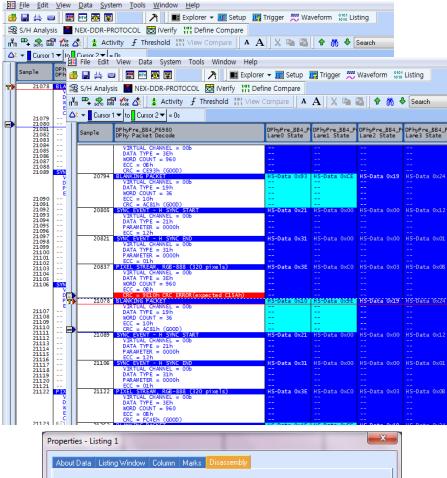

### M-PHY Decode: Opt.MPHYVIEW for DigRFv4 Decode

- Automated Decoding:

- Automatically recognizes data speeds, disassembles, and displays the decoded data in different readable-data formats

- 4 Lanes Decoding:

- Acquires up to 4 lanes of data traffic at a time.

- On-line, Offline and Remote Analysis:

- Uses TekVisa to connect to a scope.

- Remote execution through LAN network.

- Filter Tab, Search and Options Tab:

- Fillter the records in the listing based on user criteria.

- Searching & highlight records that satisfy given criteria

- Set display, disassembly, and configuration options.

| -              |            |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1000 | and in | inter a | <u>a</u> | one)   |     |

|----------------|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------|----------|--------|-----|

| iren.          | Tree.      | Magazi              | met.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 244  | Deal   | 06      |          | 100    | -   |

|                |            | Selder              | Stated at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 244  | 1044   | 14      | 1        | 111    | 1   |

| 15444          | 41,000-14  |                     | 509                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1941 | 84     | 14      | 181      | 426    | -1  |

| 19182          | 41.010.00  |                     | Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80   | 38     | 1       | . 8      | 1620.2 | 81  |

| THEFT          |            | Parent fore: 874    | 1000.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49   | .53    | 1.1     |          | 15.2   | 1   |

| 18474          | 40.008-ist |                     | CON.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 190  | 95     | 8       | 1.1      | 0.8    | 1   |

| 1000           | 41.078.00  |                     | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81   | . 85   | 1.1     | 11/      | 2026   | 81  |

| TRAFE          | 43.936-sq  |                     | 2840                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87.  | 18.    | 11      |          | 2428.5 | 1   |

| 76250          | 41201-10   |                     | Picked Spec 188.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 28.    | 11      |          | 08.2   | 1   |

| 10000          |            | Painted Bird, 4104  | Darloted Rotal: Elli-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -0.8 | -11    |         | 4        | 0+0    | 81  |

| 1468.02        |            | Part of Rev. CO.    | Palent Steel 1981                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10.0 | 114    | 1.      | 1.       | 101.0  | - 1 |

| TILLES         | 33.20 m    | Fastured Born (10h) | Plant of free 105-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 111  | .18    | 1.1.    | π.       | lin.d  | -   |

|                | Inet       | Options 1 1 1       | Person 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |        |         |          | 21     |     |

| Cased<br>Video |            |                     | and the second se |      | 1      |         |          | -      |     |

| 1              |            | A REAL PROPERTY.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        | Ĩ       |          |        |     |

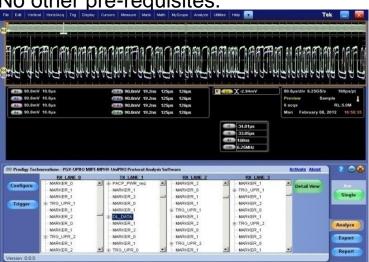

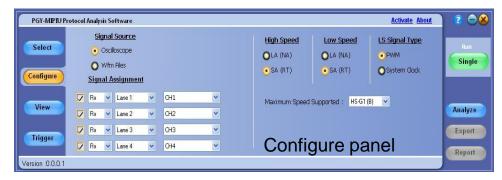

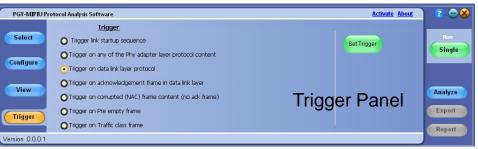

#### M-PHY Decodes: New PGY-UPRO and PGY-LLI UniPro and LLI Scope-Decodes

- PGY-UPRO and PGY-LLI are Decode Software re-sell from Prodigy Technovations.

- Provides M-PHY UniPro and M-PHY LLI Protocol Decode and Analysis.

- Runs on DPO/DSA/MSO70000/B/C/D models (6GHz and above)

- License mechanism is same as scope options TEK-PGY-HDMI-PA-SW, or PDI-R.

- Opt. ST6G Serial trigger is optionally required. No other pre-requisites.

- Differentiation

- SW Leverages ST6G serial trigger features

- SW is First-to-Market

- Value proposition

- SW Seamless Integration with all 70K scopes.

- SW enables system level protocol debugging.

- 4-Lane Automated Decoding, and Verifies CRC

### M-PHY Decodes: New PGY-UPRO and PGY-LLI

- Decode Table with Messages &Time stamp

- Overlay of decoded messages on waveform

- Packet content details, with description

- Error packets

- State diagram shows Sequence of messages

- → ACK frame/NACK frame with time stamp.

- Trigger on UniPRO message contents (Optional)

- Trigger PA layer message

- Trigger on Data link layer packet message

|          | UNIPro Layer |                   | High Level Frame Content Time |                       |            |                 |          |             |         |

|----------|--------------|-------------------|-------------------------------|-----------------------|------------|-----------------|----------|-------------|---------|

| Select   |              | TRG_UPR0 = 0x7C40 |                               |                       |            |                 | 8.536 mS | Detail View | Run     |

|          |              | TRG_UPR0 = 0x7C40 |                               |                       |            |                 | 11.86 mS |             | Single  |

|          | LSS Phase2   | TRG_UPR1 = 0x7C83 |                               |                       |            |                 | 18.19 mS |             | Singi   |

| onfigure |              | TRG_UPR1 = 0x7C83 |                               |                       |            |                 | 21.52 mS |             |         |

|          |              | TRG_UPR1 = 0x7C83 |                               |                       |            |                 | 24.93 mS |             |         |

| View     | LSS Phase3   | TRG_UPR2 = 0x7CC0 |                               |                       |            |                 | 29.68 mS |             | Analyze |

|          |              | TRG_UPR2 = 0x7CC0 |                               |                       |            |                 | 33.01 mS |             | Analyze |

|          |              | TRG_UPR2 = 0x7CC0 |                               |                       |            |                 | 36.44 mS |             | Export  |

| Trigger  | PA           | ESC_PA = 0xFE     | PACP_BEGIN = 0x01             | PACP_CAP_ind = 0x0306 | Parameters | CRC-16 = 0x1111 | 41.41 mS |             |         |

|          | PA           | ESC PA = 0xFE     | PACP BEGIN = 0x01             | PACP PWR reg = 0x010E | Parameters | CRC-16          | Suits    | Panel       | Report  |

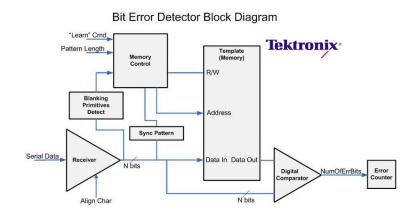

#### M-PHY Rx : Based on Scope built-in Error Detector Scope-Integrated M-PHY BER using Opt.ERRDT Shipping Today

• 8B/10B Data:

rates.

- Hardware Serial trigger: 1.25 Gb/s to 6.25 Gb/s

- BER covers PRBS 312Mbs and above data

MIPI M-PHY Receiver - TEKTRONIX MOI

#### RX ERROR DETECTOR

#### Overview:

This section of tests verifies the M-PHY receiver error detection mechanism as defined in the M-PHY Specification.

#### **GROUP 1: M-RX Error Detection Requirements**

#### Overview:

This group of tests verifies various requirements of error detection on MIPI M-PHY receiver. Scope error detector is used for this purpose. For M-PHY error detector, ERRDT and STU option should be enabled in scope and Tekscope firmware v6.1.1.32 or later is required.

#### Status

The test descriptions contained in this group are considered to be in initial draft form. Additional modifications to both the test descriptions and implementations are expected.

Pay Load:

Continuous PRBS 7/PRBS 9 Pattern with NRZ signaling (HS-Gear1, HS-Gear2 and DigRF data rates) Custom burst pattern with 8b/10b encoded with NRZ/PWM/SYS signaling.

Note: Please refer to the MPHY specification ver .90

MIPI M-PHY Rx MOI Measurements Version 0.5 Draft

38

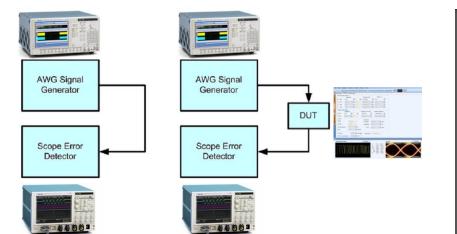

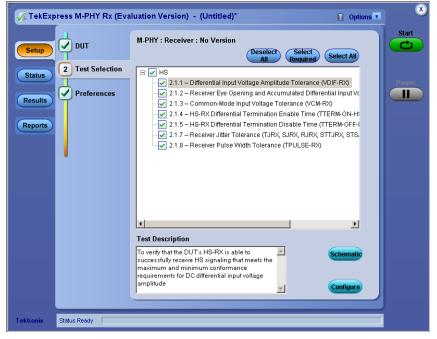

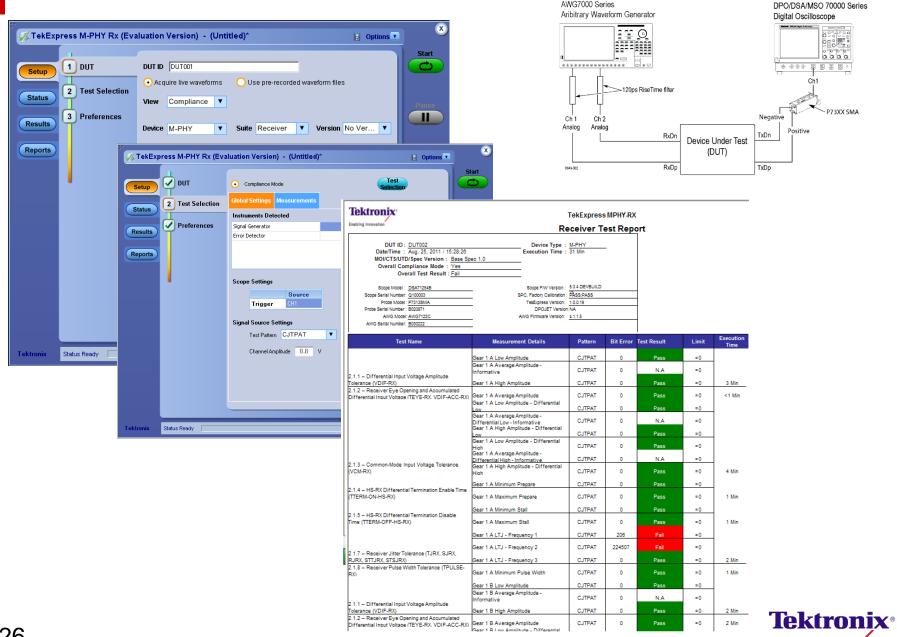

#### M-PHY Rx : Opt.M-PHYRX Automated Solution

#### Opt.M-PHYRX

- TekExpress (2.0) option for Fully-Automated receiver testing

- Provides Conformance and Characterization Testing

- Based on Latest M-PHY Base Spec v1.0 &UNH's Conformance Test Suite

- Runs on DPO/DSA70KB/C or MSO70K/C scopes

- TekExpress framework is included.

- Differentiation

- Simply 2-box setup.

- Built upon Scope ErrorDetecror ERRDT.

- Wide HS test coverage

- Value proposition

- Test Reports with Pass/Fail summary, with Bit-Error counts

#### M-PHY Rx : Opt.M-PHYRX Features

| Feature                | Benefit                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automated<br>Testing   | <ul> <li>Reduces the complexity of executing receiver tests</li> <li>Reduces testing time</li> <li>Enables you to test devices faster</li> </ul>                                                                                                                                                                                                                                |

| Tests coverage         | Automated test setup has comprehensive coverage of high speed Rx tests                                                                                                                                                                                                                                                                                                          |

| Simple setup           | <ul> <li>Simple Scope+AWG setup for a complete Receiver as well as Transmitter testing of M-PHY.</li> <li>No other instrument is needed.</li> </ul>                                                                                                                                                                                                                             |

| Integrated BER         | <ul> <li>Leverages Bit-Error-Rate or Error-Count testing using Scope-Integrated ERRDT software in the background.</li> <li>Scope Integrated ERRDT enables easy and quick setup, saves resource time and costs.</li> <li>Scope ERRDT testing supports PRBS 312Mbps &amp; above for all Gears.</li> <li>No external/ extra hardware is required to perform BER testing</li> </ul> |

| Setup<br>Customization | <ul> <li>Modify the test setup as per the DUT configurations such as the high speed<br/>Gear, test time or loop-back duration, etc</li> </ul>                                                                                                                                                                                                                                   |

| Test reports           | <ul> <li>Provides a Pass/Fail summary for all tests.</li> <li>Provides additional information such as test setup hardware and software details, Signal type selected, Bit Error, Execution time and User-comments.</li> </ul>                                                                                                                                                   |

#### M-PHY Rx : Opt.M-PHYRX Features

26

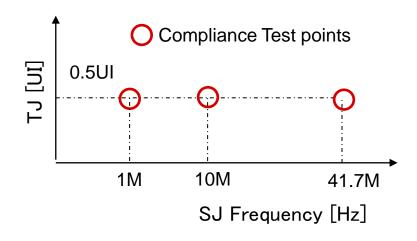

#### M-PHY Rx Test Setup: Test Impairments using AWG Manual Setup/ Capabilities

- Supports Flexible signal impairments using Serial Express (optionally) for Characterization.

- Supports Jitter insertion and Pulse Width Modulation (PWM) as per the base specification v1.0.

- Supports testing the DUT in both loopback and non-loopback mode.

**Tektronix**

Example Jitter generation using AWG & Cable impairments, as per the specs.

1. Long Term Jitter based pattern for PRBS7 continuous Pattern • Sinusoidal Jitter Frequency (Sj1) =1 MHz

#### M-PHY Tx &Rx Recommended Test Setup www.tek.com/MIPI

#### Scopes

- DPO70604/B/C or above, for HS-Gear1 Only (Tx &Rx).

- DPO70804/B/C or above, for HS-Gear1&2 Only (Tx &Rx)

- DPO71254/B/C or above, for All HS-Gears (Rx Only)

- DPO72004/B/C or above, for All HS-Gears (Tx &Rx).

#### Probes

- 2x P73xxSMA/P73xx, for Tx HS upto Gears2, or 2x P75xx with P75LRST for Tx HS upto Gear3.

- 2x P73xxSMA/P73xx, for Tx PWM All Gears.

- 1x P73xxSMA, for Rx.

- Signal Generators for Rx

- AWG7082C, AWG7102 or above, for HS-Gear1 Only.

- AWG7122C <u>without</u> Interleave, for HS-Gear1&2 Only.

- AWG7122C with Interleave (option 06), for All HS-Gears.

#### Software

- New Opt.M-PHYTX Transmitter Automated Solution (Opt.DJA is pre-requisite).

- New PGY-UPRO Protocol Decode (Opt.ST6G optionally required).

- New PGY-LLI Protocol Decode (Opt.ST6G optionally required).

- Opt.M-PHYRX Receiver Automation (Opt.ERRDT is pre-requisite).

- Opt.SR-810B, for 8b-10b Decode

- MPHYVIEW, for DigRFv4 Protocol Decode

- Optional: Opt.M-PHY Essentials based on DPOJET

- Optional: SerialXpress for custom-patterns using AWG

#### Fixtures

As MIPI is chip-to-chip interface, most DUT setups are LIVE with Master-Slave/ Receiver-end connected. For live-setups: No Fixtures required. For non-live setups UNH-IOL Termination boards expected to be available soon

P7380 probe used with a probe-tip

#### **Tektronix M-PHY Testing Solution**

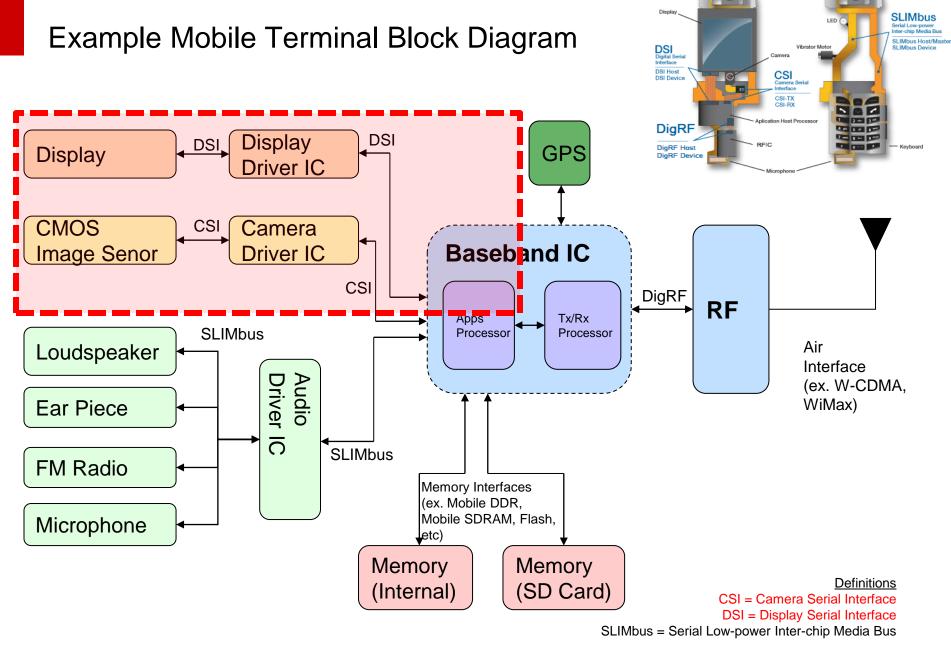

- Industry 1<sup>st</sup> tools

- Tektronix announced M-PHY Measurements & Decode tools, in September 2010, during MIPI Alliance Athens F2F.

- Simply "2-Box" Solution : Just a Scope + AWG needed for Tx &Rx.

- PSD (Power Spectral Density) measurements on Scope are IP-Patented

Cf.us.biz.yahoo.com/iw/100927/0666379.html?.v=1&printer=1

**Press Release**

Source: Tektronix

#### Tektronix Introduces Industry's First Test Tools for MIPI M-PHY **Debug and Validation**

Monday September 27, 9:00 am ET

Support for New High-Speed M-PHY Specification Includes DPOJET toolset, and M-PHY DigRFv4 Decode for Tektronix Oscilloscopes

BEAVERTON, OR--(Marketwire - 09/27/10) - Tektronix, Inc., the world's leading manufacturer of oscilloscopes, today introduced the industry's first testing tools for the MIPI® Alliance M-PHY standard, allowing customers to immediately get started with performance verification and debug for this important new specification using Tektronix DPO/DSA/MSO70000B Series oscilloscopes.

The announcement was made in conjunction with the MIPI Alliance All-Members meeting taking place this week in Athens, Greece. The M-PHY specification is an essential part of the MIPI Alliance's vision for more efficient high-speed at MIPI-Alliance F2F, Athens, Sept'10 and Osaka, March'11 interfaces on mobile devices. Compared to the current D-PHY specification, M-PHY supports faster chip-to-chip

# MIPI DSI/CSI2 Protocol solution

Woo, Jun Hyung Application Engineer

#### Agenda

- Introducing MIPI<sup>®</sup> Protocol Layer

- What is MIPI DSI ?

- What is MIPI CSI ?

- MIPI Protocol Validation Solution

- MIPI Stimulus Test using Pattern Generator

- MIPI Protocol decode solution using TLA

- Summary, Q&A

**Tektronix**<sup>®</sup>

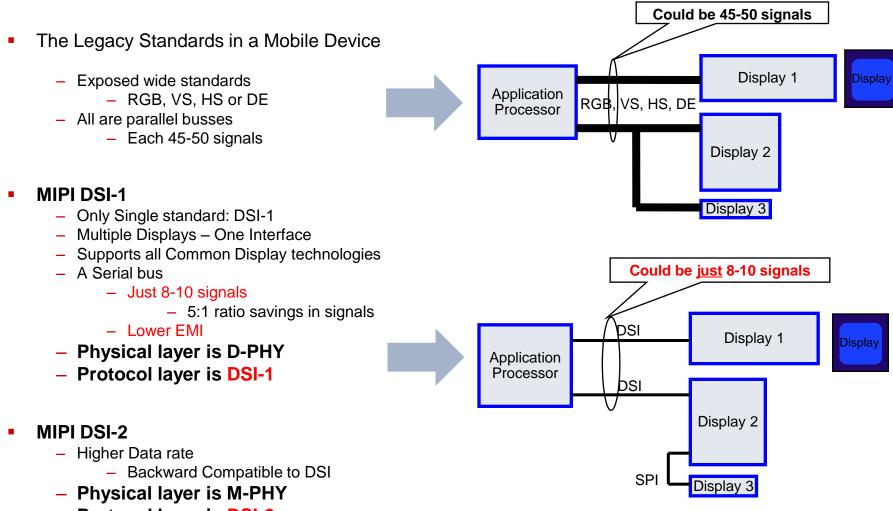

### What is MIPI DSI ?

**DSI** is the specification for processor-to-display interconnect in handheld platforms

Tektronix

- Protocol layer is DSI-2

### What is MIPI CSI ?

CSI is the serial interface specification

for Camera/ imaging peripherals and host processors

**Tektronix**<sup>®</sup>

Protocol layer is CSI-3

#### **MIPI Protocol Stacks**

(source: mipi.org)

|           | CAMERA              | DISPLAY             | Uniport<br>D           | Uniport<br>M             | Audio/<br>Data / ctrl | CONTROL                                               | BB-RF<br>3G | BB-RF<br>4G         | IPC  | Mass<br>storage          | Trace       | Gigabit<br>Trace         |

|-----------|---------------------|---------------------|------------------------|--------------------------|-----------------------|-------------------------------------------------------|-------------|---------------------|------|--------------------------|-------------|--------------------------|

| Software  |                     |                     |                        | IMF                      |                       |                                                       |             |                     |      | NAND<br>SW               |             |                          |

|           |                     |                     | DD                     | В                        |                       |                                                       |             |                     |      |                          |             |                          |

| App-      |                     | DCS                 |                        |                          |                       |                                                       | ICLC        | ICLC                |      |                          |             |                          |

| App-data  | CSI-2               | DSI-1               | App-data               | App-data                 |                       | SPMI :<br>Power<br>Managt.<br>RF-FE:<br>RF<br>Control | DigRF<br>3G | DigRF<br>4G         |      |                          | OST Fra     | meWork                   |

|           |                     |                     | PIE                    | Conf                     | SlimBus               | Control                                               | 3G          | 40                  |      | Conf                     | OST         | TWP                      |

| Transport |                     |                     | UniPro<br>1.0          | UniPro<br>1.5 and<br>2.0 |                       |                                                       |             |                     | HSI  | UniPro<br>1.5 and<br>2.0 | STP         | UniPro<br>1.5 and<br>2.0 |

| РНҮ       | D-PHY<br>serial I/F | D-PHY<br>serial I/F | D-PHY<br>serial<br>I/F | M-PHY<br>serial<br>I/F   | CMOS-<br>based        | CMOS-<br>based                                        |             | M-PHY<br>serial I/F | CMOS | M-PHY<br>serial<br>I/F   | PTI<br>CMOS | M-PHY<br>serial<br>I/F   |

**Tektronix**®

#### **MIPI DSI Layered Architecture**

Lane N - High Speed Unidirectional Data

MIPI D-PHY Test Solutions

> Protocol Stimulus Analog @ (Q.O) 0 **Component Level Testing** System Level Debug **HW/SW Integration** Characterization Compliance

Tools to cover all your test needs for today and in future

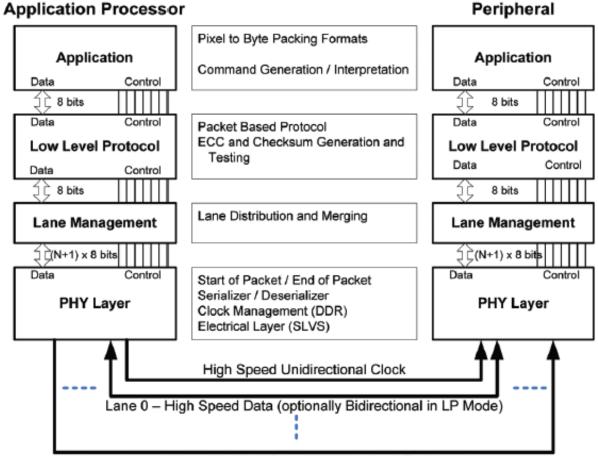

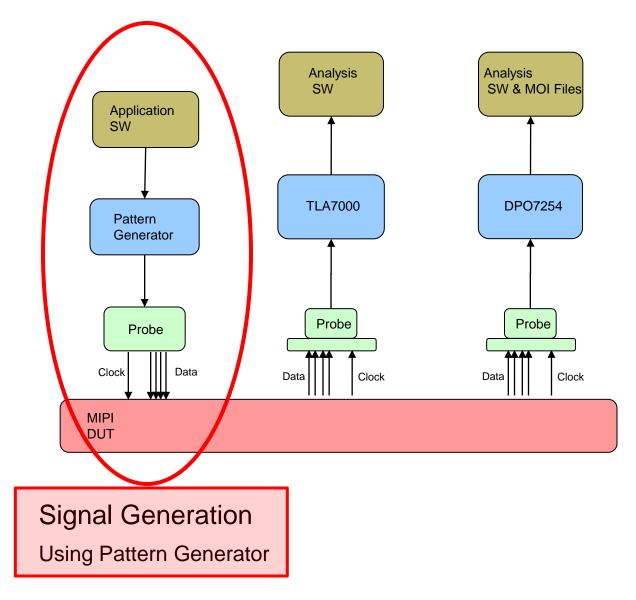

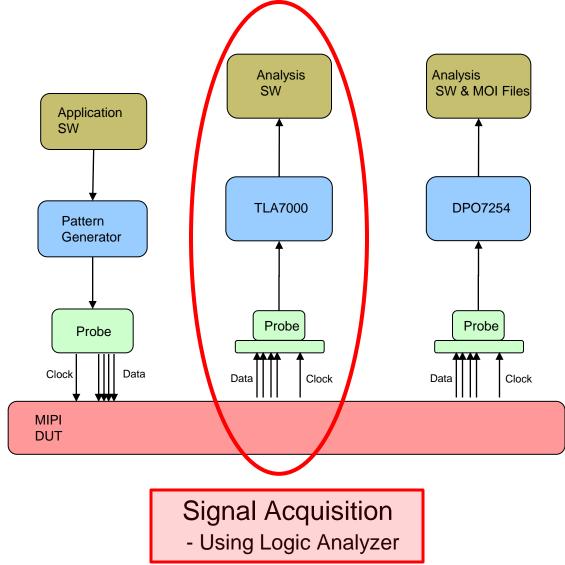

# **MIPI Solutions and Techniques**

- Oscilloscope

- Signal Integrity

- D-PHY Physical Layer Test

- Logic Analyzer

- Validation and debug of the MIPI protocol

- Pattern Generator

- MIPI Signal Generation

- Stimulating Driver ICs, Devices, and Processors

- Oscilloscope, Logic Analyzer and Pattern Generator

- System level Validation & Debug

- Testing fully integrated mobile handset platforms

### **Typical Protocol Validation Test Setup**

**Tektronix**®

# **Stimulus**

### **Test Environment**

**Tektronix**<sup>®</sup>

### Stimulus Setup

### Stimulus

- Protocol Testing Stimulating buses with known good data packets or packets with intentional errors tests the system's adherence to a specified protocol

- Infrequent Events System bugs that only appear when infrequent events occur can be quickly reproduced with a pattern generator by repeatedly stimulating the system with the key external event

- Automated Test Production line test setups can utilize the PG3A as a general purpose digital I/O source with a large number of channels

### **Digital Pattern Generators**

|                                          | PG3AMOD                                                               | PG3ACAB     | PG3L                |  |  |  |

|------------------------------------------|-----------------------------------------------------------------------|-------------|---------------------|--|--|--|

| Max clock rate                           | 300MHz                                                                |             |                     |  |  |  |

| # of Channels                            | 6                                                                     | 4           | 32                  |  |  |  |

| Memory                                   | 32M Vectors                                                           |             |                     |  |  |  |

| Data models                              | Flat or block based                                                   |             |                     |  |  |  |

| Output levels                            | External Probes dete MIPL Applications                                |             |                     |  |  |  |

| Form factor                              | Plug-in module<br>for TLA7K                                           |             | orare not supported |  |  |  |

| PGApp (Win XP, WIN7)                     | Convenient pattern entry with multiple pattern file, important export |             |                     |  |  |  |

| Ref In/Out, Ext Trig In/Out              | Yes                                                                   | Yes         | No                  |  |  |  |

| External events                          | 9                                                                     | 9           | 8                   |  |  |  |

| Width Expandable                         | To 256 bits                                                           | To 256 bits | No                  |  |  |  |

| P300 Inputs Probe                        | Yes                                                                   | Yes         | No                  |  |  |  |

| Probe Cables                             | 4                                                                     | 4           | 1                   |  |  |  |

| Delay Line Range on a<br>Group of 8 Bits | 500ns                                                                 | 500ns       | 7.5ns               |  |  |  |

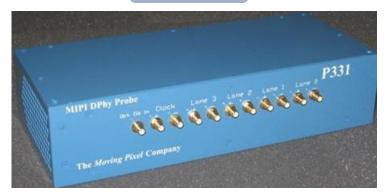

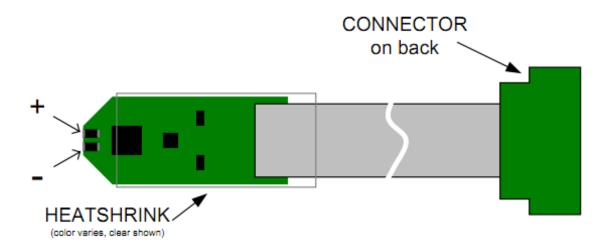

### P332 MIPI D-PHY Probe for PG3A

### **Key Features**

- MIPI D-PHY Probe for use with PG3AMOD and PG3ACAB

- Generate CSI2 and DSI data over D-PHY

- 4-Data Lanes and 1-Clock lane

- 1.5Gbps / Lane data rate

- SMA outputs for each lane

- LP and HS Voltage and Timing adjustable on a each lane separately

### P332 MIPI D-PHY Probe

#### **Key Features**

- Optional external clock input port suitable for impaired clock testing (e.g. jitter, noise, etc)

- Ability to insert simple commands into vertical blanking while in continuous video mode

- Proper BTA response handshaking when DUT returns control back to PG

- LP contention detection

Noise injection setup for D-PHY Rx Testing

Preserve your investment with the ONLY 4 lane, 1.5Gbps stimulus solution in the market.

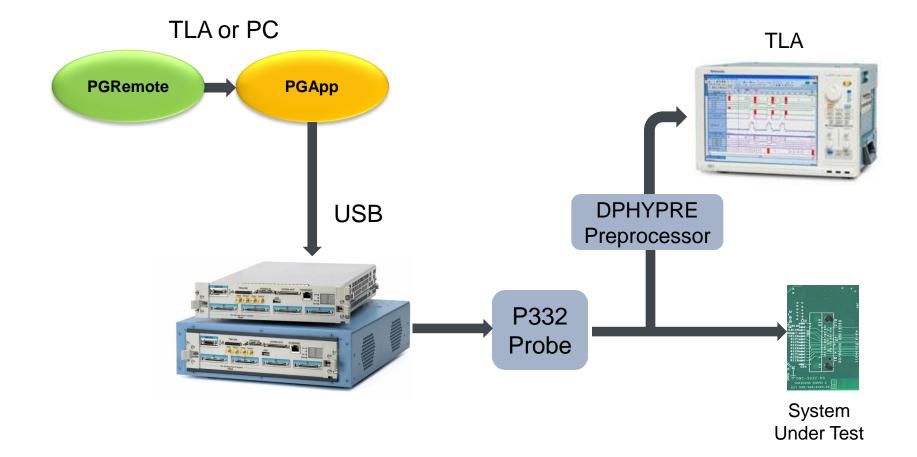

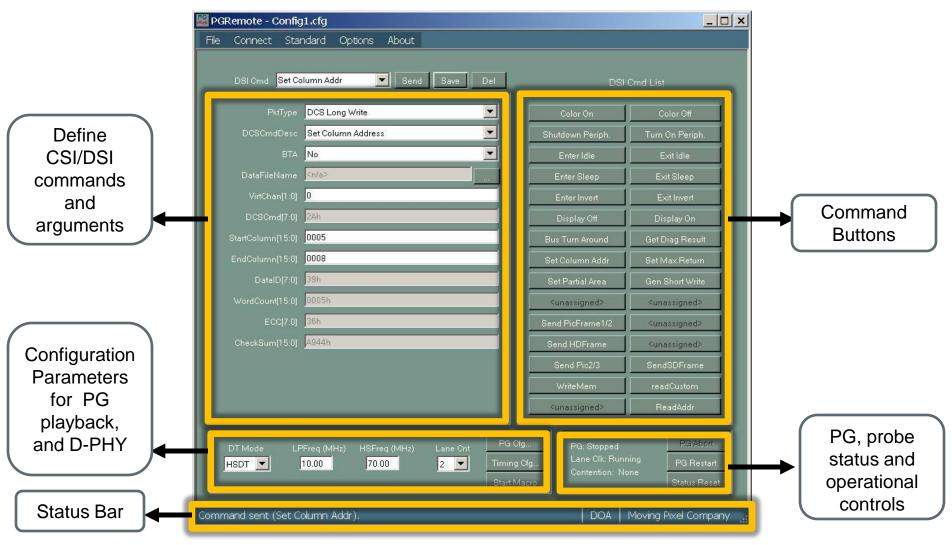

### PGRemote

Push Button Interface to generate CSI2 / DSI Vectors

#### **PGRemote Main Window**

**Tektronix**®

### PGRemote

- Push Button User interface to generate CSI2 or DSI vectors and probe control

- Adjust frequency, voltage and delay in HS and LP modes

- Adjust D-PHY state timing parameters

- Adjust frame timing and generate looping video

- Enter and exit Low power states

- Create custom commands, Macros and assign them to buttons

- Save restore a configuration

- Ability to use P332 as a generic high-speed serial probe

- The PG can be operated in several modes

- Pushbutton Mode using the PGRemote software

- Macro Mode using the PGRemote software

- Scripting

- Full remote control mode

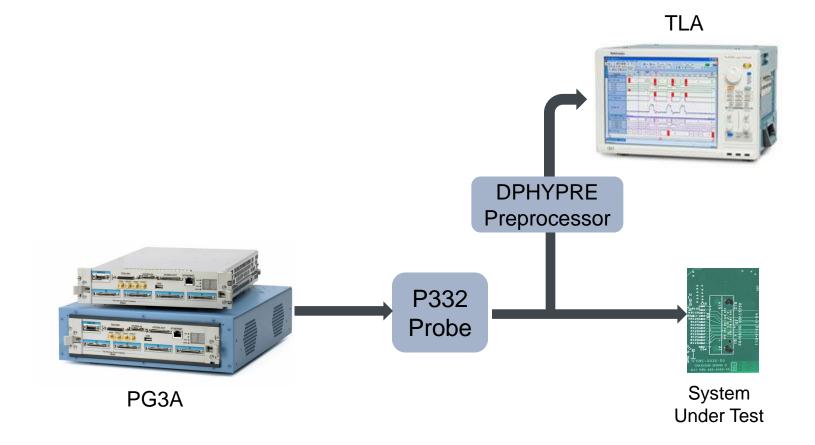

# **Protocol Validation**

### **Test Environment**

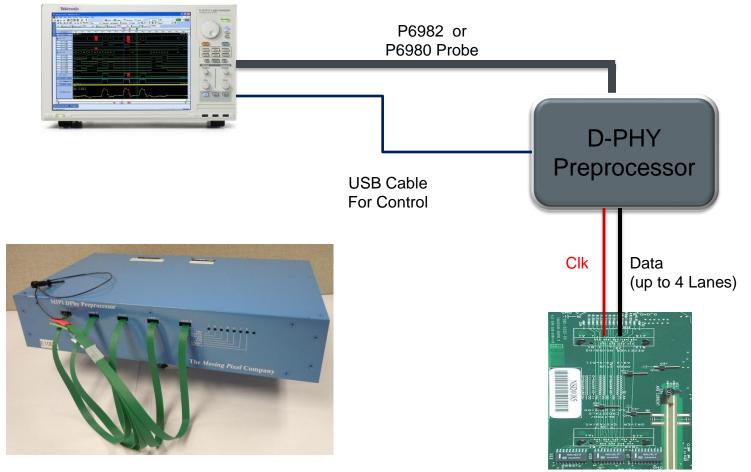

### **CSI2/DSI** Protocol validation

Solution Overview

**D-PHY Preprocessor**

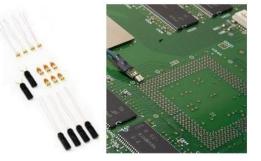

## Probing

- D-PhyPreprocessor has Solder-Down Probes

- Each Data Lane and the Clock Lane has a separate probe

- Probes are color coded for easy identification

- Can support Data Rates of up to 1.5Gb/s on each lane

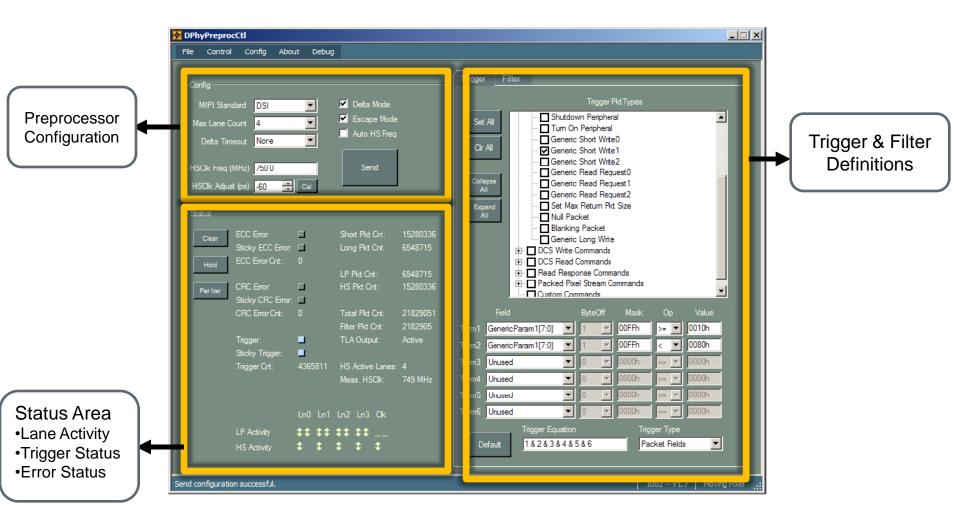

# **D-PHY Preprocessor**

- Support 1.5Gbps per lane

- Support for up to 4 Lanes of D-PHY data

- Color coded solder down probes for easy identification

- Support CSI2/DSI Protocols

- Advanced Packet Level Triggering

- Real Time Filtering

- Lane activity and Error Status

- Simultaneous Low Power and High Speed Data Acquisition

- 8x improvement in TLA Memory usage

- Image Export

- Compatible with both TLA6k and TLA7k

Preserve your investment with the ONLY 4 lane, 1.5Gbps protocol solution in the market.

### **D-PHY Preprocessor control UI**

**Tektronix**®

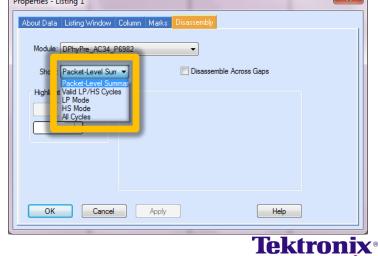

## **D-PHY Decode**

- Supports from 1 to 4 lanes of D-PHY data

- Decode and Display

- All LP and HS state transitions

- LP commands and data

- LP and HS Data in Byte Format

- All types of Short and Long packets

- DCS Command decode

- Supports different RGB and YUV Schemes

- Supports ECC and Checksum verification.

- selectively view the decoded information at different levels of hierarchy

## **Protocol Support**

- Packets extracted & stored for further analysis

- Image rendering

- Rendering with Partial Data supported

- Different RGB export options

| Properties - P                     | rotocol 2                             |                |       |       | X               |  |  |

|------------------------------------|---------------------------------------|----------------|-------|-------|-----------------|--|--|

| About Data                         | Protocol Window                       | Column         | Color | Marks | Framing Options |  |  |

| Erame A                            | cross Gaps                            |                |       |       |                 |  |  |

|                                    |                                       |                |       |       |                 |  |  |

| Samples To Analyze                 |                                       |                |       |       |                 |  |  |

| Start: 0 Number of Samples: 131072 |                                       |                |       |       |                 |  |  |

| Sample R                           | Sample Range: 0-131071                |                |       |       |                 |  |  |

| DSI_A_Solder_In Controls           |                                       |                |       |       |                 |  |  |

| Numb                               | Number of Lanes: x2                   |                |       |       |                 |  |  |

|                                    | Save File: C:\\My Documents\image bmp |                |       |       |                 |  |  |

| Save Image File                    |                                       |                |       |       |                 |  |  |

|                                    |                                       |                |       |       |                 |  |  |

|                                    |                                       |                |       |       |                 |  |  |

|                                    | ок                                    | <u>C</u> ancel | Appl  |       | Help            |  |  |

### Data Formats supported

### **CSI** Formats

- YUV420 8-bit (legacy)

- YUV420 8-Bit

- YUV420 10-bit

- YUV422 8-bit

- YUV422 10-Bit

- RGB888

- RGB666

- RGB565

- RGB555

- RGB444

### **DSI Formats**

- RGB888

- RGB666 Packed

- RGB666 Loosely Packed

**Tektronix**®

RGB 565

### System Configuration

| Protocol Decode                                                                                                                                                                             | Stimulus                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Option - 1         <ul> <li>DPHYPRE (1ea)</li> <li>P6982 (2ea)</li> <li>TLA6K or TLA7ACx (1ea)</li> <li>TLA7012/TLA7016 (1ea)</li> <li>For use with TLA7ACx</li> </ul> </li> </ul> | <ul> <li>Option - 1         <ul> <li>PG3AMOD (1ea)</li> <li>P332 (1ea)</li> <li>PGRemoteSW (1ea)</li> <li>TLA7012/TLA7016 (1ea)</li> <li>For use with PG3AMOD</li> </ul> </li> </ul> |

| <ul> <li>Option - 2</li> <li>DPHYPRE (1ea)</li> <li>P6980 (1ea)</li> <li>TLA7BBx (1ea)</li> <li>TLA7012/TLA7016 (1ea)</li> <li>For use with TLA7BBx</li> </ul>                              | <ul> <li>Option - 2</li> <li>PG3ACAB (1ea)</li> <li>P332 (1ea)</li> <li>PGRemoteSW (1ea)</li> </ul>                                                                                  |

### Summary

- Stimulus

- Only 4 Lane stimulus solution that can support 1.5Gbps

Data rate / lane.

- Provides the flexibility to control link level timing parameters as well as PHY level timing and voltage parameters

- Supports both the DSI and CSI2 protocols

- Protocol

- Only 4 Lane Protocol validation solution that can support 1.5Gbps Data Rate / Lane

- Provides sophisticated Packet level Triggering, real time filtering, Status Monitoring and LED indicators

- Supports both the DSI and CSI2 protocols