**Test Time to Minutes**

rity™ test

erbend

istance

que, crush &

tection with

LOG IN GIVEAWAYS TECH COMMUNITIES The Newest Products for Your Newest Designs®

JOIN JITX Aims to Provide Superpo... 0:00 / 0:00 **PODCAST LATEST SUBSCRIBE**

FC15M MEDICAL CAPACITOR CHARGING AND AC/DC POWER SUPPLY Excelsys FLEXICHARGE FC1500 Up to 2300w total power designed to provide the system power needs for medical laser applications Advanced Energy LEARN MORE

MOORE'S LOBBY PODCAST

Clarity™ test cables offer ste overbend protection with abrasion resistance

Ampheno

October 25, 2022 by Jeff Child By creating a new class of test instrument, Tektronix touts its PCI Express (PCIe) margin tester as a tool that reduces PCIe link testing times from hours down to just minutes. FC15M MEDICAL CAPACITOR CHARGING

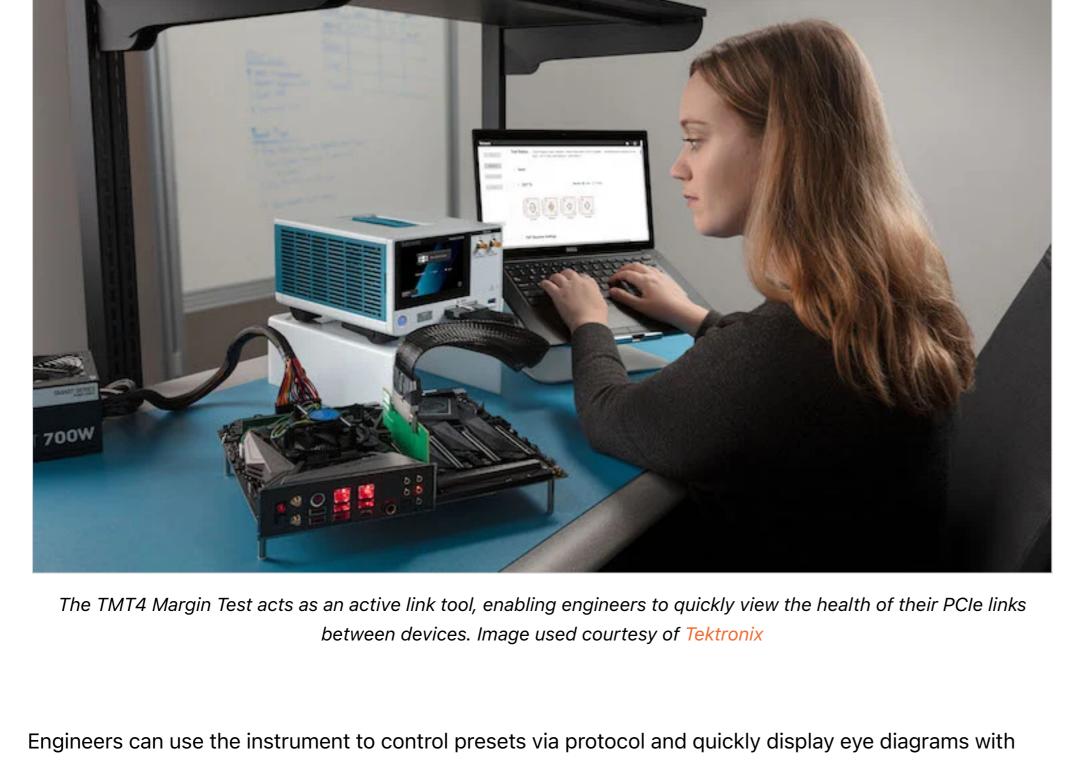

Offering a new approach to that process, today Tektronix announced its TMT4 Margin Tester. The company claims it as the industry's first dedicated Transmit/Receive (Tx/Rx) lane margining tool, enabling engineers to evaluate the link health of their PCIe Gen 3 and 4 systems in just minutes, rather than hours

or days. In this article, we examine the key details of the TMT4 Margin Tester, we review the problem that the new margin tester system is designed to solve, and we share insights from our interview with Michael Seaholm, Product Manager at Tektronix. Seaholm is the project lead on the TMT4 Margin Tester.

Margin Tester Acts as Active Link Partner

In contrast to traditional PCIe testing methods, the TMT4 functions as an "active link partner" with your

device under test (DUT).

their associated link training parameters. In this way, they can view potential design flaws on a lane-bylane or preset-by-preset basis.

includes two methods. One is a combination of an oscilloscope and a Bit Error Tester (BERT). The other is using on-chip Lane Merging (LM) tools provided by chip manufacturers. Each has its trade offs. The scope/BERT approach is a comprehensive method, and it can achieve all the validation and compliance testing necessary for PCIe compliance. But it is an expensive method that not all system

As Seaholm explains, today's traditional approach for testing design margins on a technology like PCIe

days to do this kind of PCIe testing," says Seaholm. "And full testing of 16-lane PCIe links can even take weeks." Meanwhile, LM tools are certainly less expensive than a scope/BERT setup, but they have limitations. For

instance, LM tools can only do lane merging of their own receivers. That means that engineers can only

use them to analyze the DUT receive paths, but not the transmitter path, says Seaholm.

developers can afford. Then there is the time it takes. "Even very experienced engineers can need several

A PCIe Solution for a Broad Set of EEs In contrast to the traditional methods of PCIe testing as explained above, the TMT4 Margin Tester was

created to be used by a broad set of users without requiring specialized expertise. According to Tektronix,

TMT4 enables engineers at all levels of experience to evaluate the health of transmitter and receiver links

Unlike the other PCIe testing alternatives, the TMT4 is fast and versatile enough that engineers can

## faster, in minutes instead of hours or days.

perform PCIe links at the board- or system-level more often. Likely any development process will still need to use a scope/BERT method to do the full validation and compliance testing. But the TMT4 makes it possible to tackle PCIe link issues earlier on in the design process.

factors by means of 11 adapters available for CEM, M.2, U.2, and U.3. Using a single 16-lane ribbon cable with high density PCIe connectors, the TMT4 connects to any of the adapters. The only exception is the M.2 edge adapter, which has its own integrated cable to accommodate different insertion loss specifications, says the company.

motherboards, add-in cards, and systems. The TMT4 Margin Tester supports most common PCIe form

EEs can use the TMT4 as they design and validate PCIe Gen 3 and Gen 4 subsystems such as

**Quan Scan and Custom Scan**

The user interface for TMT4 is intended to be simple and easy to use. Users can control the TMT4 Margin

Tester using the front panel, a web browser, or the Rest API. The platform offers two options: Quick Scan

and Custom Scan. In Quick Scan, the Margin Tester and the DUT engage in a natural link negotiation to

## determine the presets they will communicate over. Meanwhile, Custom Scan provides engineers with more parameters to adjust for specific tests. It essentially forces the DUT into specific presets for tests. Tektronix offers a demo video that explains the

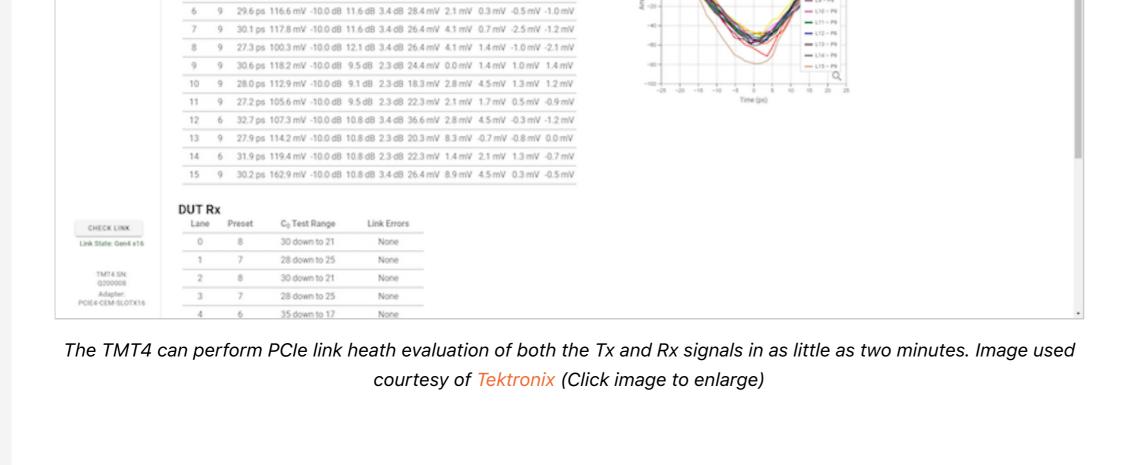

Lane Preset EW EH ATT CTLE GAIN DFE(1) DFE(2) DFE(3) DFE(4) DFE(5)

0 9 30.1 ps 130.0 mV -10.0 dB 12.1 dB 4.6 dB 38.6 mV 2.1 mV 0.7 mV -4.0 mV -3.1 mV 6 33.2 ps 111.7 mV -10.0 dB 11.6 dB 2.3 dB 28.4 mV 3.4 mV -1.0 mV -0.3 mV -1.4 mV

2 9 27.1 ps 104.8 mV -10.0 dB 12.5 dB 3.4 dB 32.5 mV 4.8 mV 1.0 mV -2.0 mV -0.2 mV 3 6 31.9 ps 97.9 mV -10.0 dB 10.8 dB 2.3 dB 28.4 mV -0.7 mV 1.4 mV -0.5 mV 0.0 mV 4 9 31.1 ps 114.2 mV -10.0 dB 10.4 dB 2.3 dB 22.3 mV 4.8 mV 1.7 mV -2.0 mV 0.0 mV 5 9 31.5 ps 104.8 mV -10.0 dB 12.5 dB 4.6 dB 36.6 mV -3.4 mV 0.7 mV -2.0 mV -1.9 mV

RESULTS

SAVE / RECALL

UTILITY

scan options and other TMT4 features in more detail. Test Status:

within an expected range of operation, before errors are returned.

**PCIe Margin Testing: Huge Customer Implications**

The test determines how far the transmitted signal amplitude from the Margin Tester can be decreased,

• The associated receiver training values the Margin Tester used to open the eye that is displayed

Also shown in the screenshot above, the DUT Rx test is a functional evaluation of the DUT's receiver path.

As shown in the screenshot above, the DUT Tx test provides two key pieces of data:

• Eye diagrams for each lane-preset combination measured at the receiver of the TMT4

By creating essentially a new class of test instrument, Tektronix has opened up new options for engineering teams that want to analyze their PCIe links as they develop their designs. This fills an important need because the stakes of a PCIe device's reliability are higher than ever these days. When PCIe devices don't work well together, it becomes a real problem for customer support, explains Seaholm.

Tektronix's new TMT4 is perhaps the best approach to mitigating such issues before they become a problem. CONTENT FROM PARTNERS

Surge Protection Solutions

Content from Sager Electronics

For those reasons, analyzing the design margins for PCIe boards and systems working together is critical.

"When two products do not work together, who is to blame?" says Seaholm, "Is it the system

board manufacturer? The add-in-card manufacturer? Both? Who does the consumer go to when

**RELATED CONTENT**

there is a problem?"

## • Multimedia Chipset Design and Testing Solutions • Interfaces for Computer-Controlled Test Systems

**Learn More About:**

**TEST INSTRUMENT**

• How to Use Thevenin's Theorem

**TEKTRONIX** PCIE

**0 Comments** Please log in before you can comment.

COMMENTS ^

YOU MAY ALSO LIKE

**Chip to Enhance** Metaverse In Partnership with Autodesk by Jake Hertz

**PCB Design**

**APPLICATIONS**

AI/Neural Networks

**Cloud Computing**

Consumer Electronics

Audio

Automotive

by Jake Hertz

**SERIAL INTERFACES**

**PCI EXPRESS**

CONTENT

**About Decibels But**

Were Afraid to Ask...

by Rohde & Schwarz

**Point2 Extends the**

**WHO WE ARE**

**CONNECT WITH US**

More about us  $\rightarrow$

**EDA Tools** Electromechanical Embedded IC Design Memory

**PRODUCTS**

Latest

Analog

Cybersecurity / Identification Digital Signal Processing **Industrial Automation** IOT IT / Networking Lighting

Medical & Fitness Military / Aero / Space **Motor Control** Smart Grid / Energy Telecom View All >

Virtual Workshops

**BOM Tool**

Calculators

Datasheets

Giveaways

**Industry Articles**

Industry Tech Days

**Industry Webinars** IC Design Center **New Products** News Part Search **Podcast** Projects **Tech Chats Tech Communities** Technical Articles Test Equipment Video Lectures

(0)

mikrocontroller.net Register Enter your email address

© EETech Media, LLC. All rights reserved

Optoelectronics Passives PCB's Power RISC-V Sensors Test & Measurement Wireless/RF View All >

Textbook Worksheets

MORE FROM OUR NETWORK **EE POWER** MAKER MAKER

Privacy Policy · Terms of Service · User Agreement

SIGN UP

Log in to comment