# **Instruction Manual**

# **Tektronix**

DAS 92DM72A Am29000 & Am29050 Microcontroller Support 070-8477-00

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

Please check for change information at the rear of this manual.

First Printing: November 1991 Revised Printing: March 1993 Online Document: April 1997

#### **Instrument Serial Numbers**

Each instrument manufactured by Tektronix has a serial number on a panel insert or tag, or stamped on the chassis. The first letter in the serial number designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

B010000 Tektronix, Inc., Beaverton, Oregon, USA E200000 Tektronix United Kingdom, Ltd., London

J300000 Sony/Tektronix, Japan

H700000 Tektronix Holland, NV, Heerenveen, The Netherlands

Instruments manufactured for Tektronix by external vendors outside the United States are assigned a two digit alpha code to identify the country of manufacture (e.g., JP for Japan, HK for Hong Kong, IL for Israel, etc.).

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

Printed in U.S.A.

Copyright © Tektronix, Inc., 1991. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. The following are registered trademarks: TEKTRONIX, TEK, TEKPROBE, and SCOPE-MOBILE.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### SOFTWARE WARRANTY

Tektronix warrants that this software product will conform to the specifications in the documentation provided with the product, when used properly in the specified operating environment, for a period of three (3) months. The warranty period begins on the date of shipment, except that if the program is installed by Tektronix, the warranty period begins on the date of installation or one month after the date of shipment, whichever is earlier. If this software product does not conform as warranted, Tektronix will provide remedial services as described in the documentation provided with the product. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that operation of the programs will be uninterrupted or error-free or that all errors will be corrected.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for such service in accordance with the instructions received from Tektronix. If Tektronix is unable, within a reasonable time after receipt of such notice, to provide remedial services, Customer may terminate the license for this software product and return this software product and any associated materials to Tektronix for credit or refund.

This warranty shall not apply to any software product that has been modified or altered by Customer. Tektronix shall not be obligated to furnish service under this warranty with respect to any software product a) that is used in an operating environment other than that specified or in a manner inconsistent with the User Manual and documentation or b) when the software product has been integrated with other software if the result of such integration increases the time or difficulty of analyzing or servicing the software product or the problems ascribed to the software product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THE LISTED PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO PROVIDE REMEDIAL SERVICE WHEN SPECIFIED, REPLACE DEFECTIVE MEDIA, OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **TABLE OF CONTENTS**

| Preface:   | GUIDE TO DAS 9200 DOCUMENTATIONGENERAL SAFETY SUMMARY | vi<br>vii |

|------------|-------------------------------------------------------|-----------|

| Section 1: | OVERVIEW                                              |           |

|            | BASIC INFORMATION                                     | 1-1       |

|            | DAS 9200 System Software Compatibility                | 1-1       |

|            | About This Manual                                     | 1-2       |

|            | Other Necessary Manuals                               | 1-3       |

|            | DAS 9200 Configuration                                | 1-3       |

|            | DIFFERENCES BETWEEN THE 92A96 AND                     |           |

|            | 92A60/90 MODULES                                      | 1-5       |

|            | Am29000/050 SYSTEM REQUIREMENTS AND                   |           |

|            | RESTRICTIONS                                          | 1-5       |

| Section 2: | QUICK START                                           |           |

|            | CONFIGURING THE DAS 9200                              | 2-1       |

|            | INSTALLING SOFTWARE                                   | 2-2       |

|            | CONFIGURING THE PROBE ADAPTER                         | 2-2       |

|            | CONNECTING THE DAS 9200 TO THE                        |           |

|            | Am29000/050 SYSTEM                                    | 2-3       |

|            | SETTING UP THE DISASSEMBLER                           | 2-10      |

|            | ACQUIRING AND DISPLAYING DATA                         | 2-11      |

| Section 3: | INSTALLATION AND CONNECTIONS                          |           |

|            | CONFIGURING THE MODULES                               | 3-1       |

|            | INSTALLING SOFTWARE                                   | 3-2       |

|            | Viewing the Refmem File                               | 3-3       |

|            | Setting Up Disassembler Software                      | 3-4       |

|            | Single Module Setup                                   | 3-4       |

|            | Multimodule Setup                                     | 3-5       |

|            | Restoring and Using a Multimodule Setup               | 3-5       |

|            | Creating Multimodule Setups                           | 3-6       |

|            | What You Can Change During Setup                      | 3-9       |

|            | Channel Groups and Assignments                        | 3-9       |

|            | Symbol Tables                                         | 3-9       |

|            | Copying and Editing Predefined Symbol Tables          | 3-14      |

|            | LABELS                                                | 3-15      |

|            | CONFIGURING THE PROBE ADAPTER                         | 3-16      |

|            | Setting the Byte-Order Jumper                         | 3-16      |

|            | Setting the Disassembly/Timing Jumper                 | 3-17      |

|            | CONNECTING THE DAS 2200 TO THE                        |           |

|            | Am29000/050 SYSTEM                                    | 3-18      |

|            | CONNECTING THE INTERFACE HOUSINGS                     | 3-19      |

|             | CONNECTING THE PROBE ADAPTER                         |  |  |  |  |  |  |  |  |  |  |

|-------------|------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|             | Connecting the Probes to the Probe Adapter           |  |  |  |  |  |  |  |  |  |  |

|             | Placing the Probe Adapter in the SUT                 |  |  |  |  |  |  |  |  |  |  |

|             | Alternate Connections                                |  |  |  |  |  |  |  |  |  |  |

|             |                                                      |  |  |  |  |  |  |  |  |  |  |

| Section 4:  | ACQUIRING AND VIEWING DISASSEMBLED DATA              |  |  |  |  |  |  |  |  |  |  |

|             | Am29000/050 DISASSEMBLER OPERATION                   |  |  |  |  |  |  |  |  |  |  |

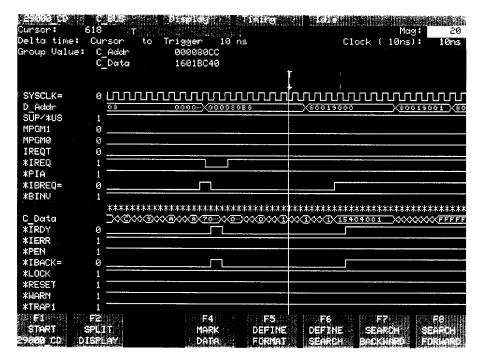

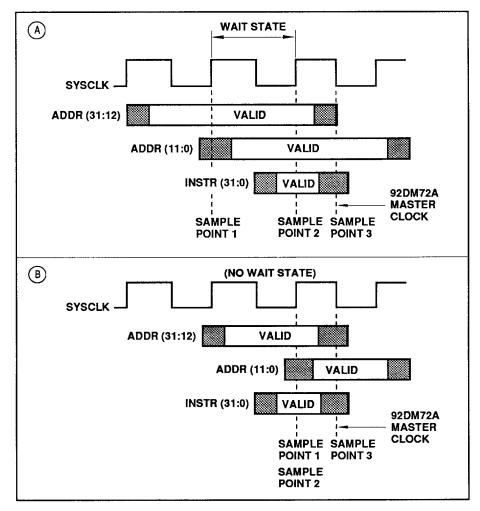

|             | CLOCKING                                             |  |  |  |  |  |  |  |  |  |  |

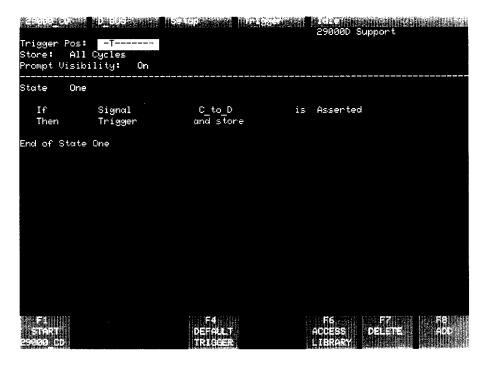

|             | TRIGGERING                                           |  |  |  |  |  |  |  |  |  |  |

|             | ACQUIRING DATA                                       |  |  |  |  |  |  |  |  |  |  |

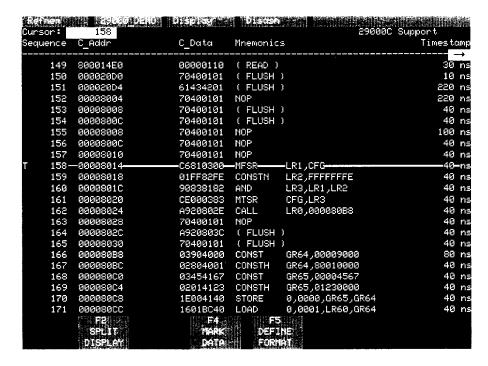

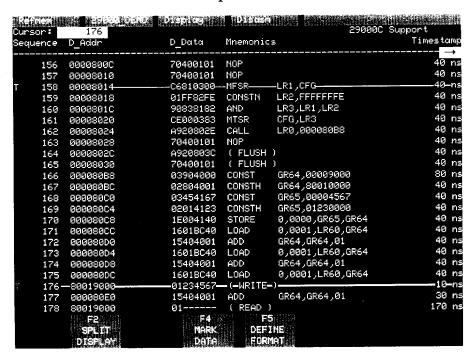

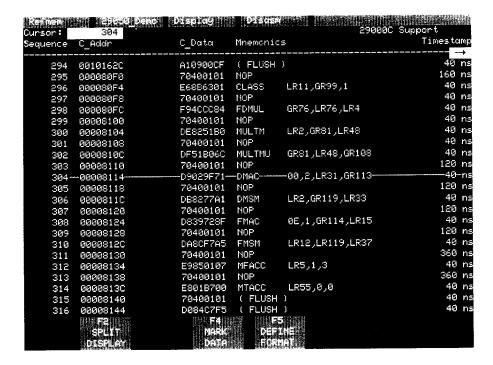

|             | DISPLAYING DISASSEMBLED DATA                         |  |  |  |  |  |  |  |  |  |  |

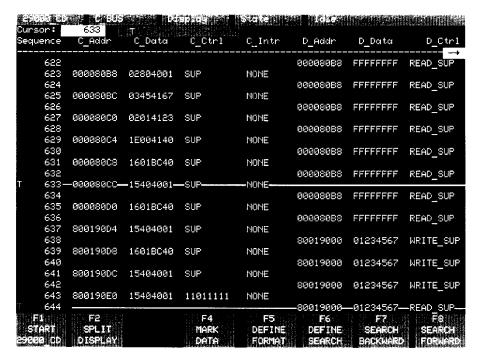

|             | Display Formats                                      |  |  |  |  |  |  |  |  |  |  |

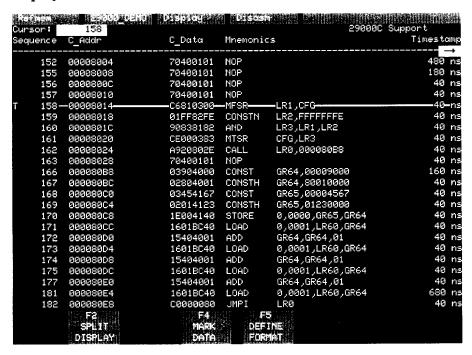

|             | Hardware Display Format                              |  |  |  |  |  |  |  |  |  |  |

|             | Software Display Format                              |  |  |  |  |  |  |  |  |  |  |

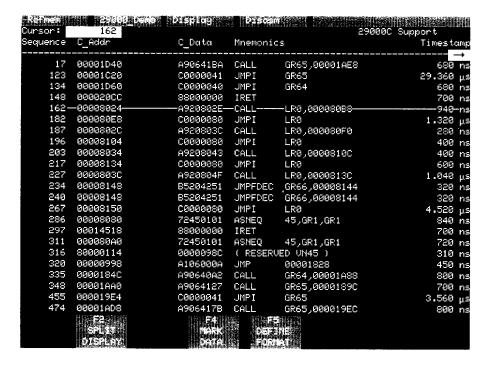

|             | Control Flow Display Format                          |  |  |  |  |  |  |  |  |  |  |

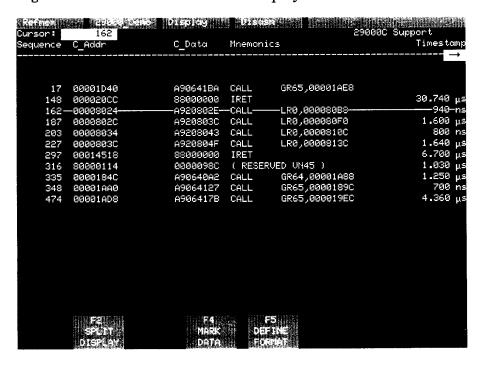

|             | Subroutine Display Format                            |  |  |  |  |  |  |  |  |  |  |

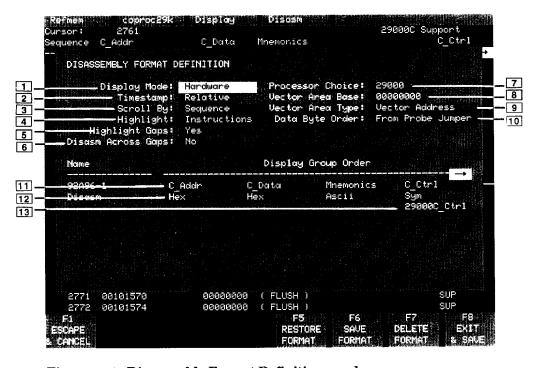

|             | Disassembly Format Definition Overlay                |  |  |  |  |  |  |  |  |  |  |

|             | Bus Cycle Types                                      |  |  |  |  |  |  |  |  |  |  |

|             | Byte Ordering                                        |  |  |  |  |  |  |  |  |  |  |

|             | Branch Target Cache                                  |  |  |  |  |  |  |  |  |  |  |

|             | Burst Mode and Address Signals, A0 – A11             |  |  |  |  |  |  |  |  |  |  |

|             | NOP Opcode                                           |  |  |  |  |  |  |  |  |  |  |

|             | Floating Point Instructions                          |  |  |  |  |  |  |  |  |  |  |

|             | Displaying the C_Addr and D_Addr Groups Symbolically |  |  |  |  |  |  |  |  |  |  |

|             | Defining and Using the Vector Area                   |  |  |  |  |  |  |  |  |  |  |

|             | Moving the Cursor to a Suppressed Sequence           |  |  |  |  |  |  |  |  |  |  |

|             | Marking Cycles                                       |  |  |  |  |  |  |  |  |  |  |

|             | Manually Overriding Disassembled Instructions        |  |  |  |  |  |  |  |  |  |  |

|             | Marking a Data Sample                                |  |  |  |  |  |  |  |  |  |  |

|             | Searching Through Data                               |  |  |  |  |  |  |  |  |  |  |

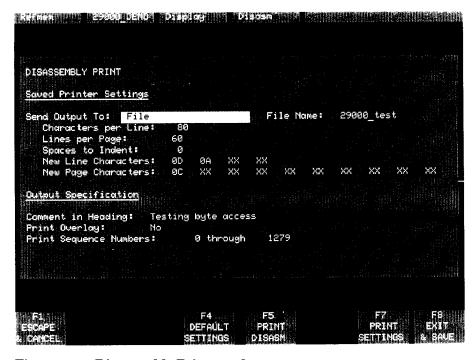

|             | PRINTING DATA                                        |  |  |  |  |  |  |  |  |  |  |

|             | THINTING DATA                                        |  |  |  |  |  |  |  |  |  |  |

| Section 5:  | HARDWARE ANALYSIS                                    |  |  |  |  |  |  |  |  |  |  |

| Section 6.  | CLOCKING                                             |  |  |  |  |  |  |  |  |  |  |

|             | Custom Clocking                                      |  |  |  |  |  |  |  |  |  |  |

|             | Internal Clocking                                    |  |  |  |  |  |  |  |  |  |  |

|             | External Clocking.                                   |  |  |  |  |  |  |  |  |  |  |

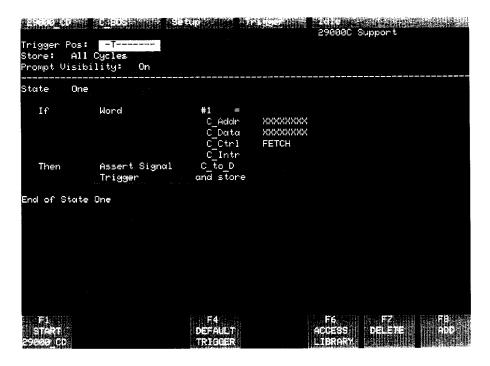

|             | TRIGGERING.                                          |  |  |  |  |  |  |  |  |  |  |

|             | ACQUIRING DATA                                       |  |  |  |  |  |  |  |  |  |  |

|             | DISPLAYING DATA                                      |  |  |  |  |  |  |  |  |  |  |

|             | Timing Menu                                          |  |  |  |  |  |  |  |  |  |  |

|             | State Menu                                           |  |  |  |  |  |  |  |  |  |  |

|             | VIEWING AND SEARCHING THROUGH DATA                   |  |  |  |  |  |  |  |  |  |  |

|             | PRINTING DATA                                        |  |  |  |  |  |  |  |  |  |  |

|             | TIMITING DATA                                        |  |  |  |  |  |  |  |  |  |  |

| Appendix A: | ERROR MESSAGES AND DISASSEMBLY PROBLEMS              |  |  |  |  |  |  |  |  |  |  |

| Tippendix M | MODULE ERROR MESSAGES                                |  |  |  |  |  |  |  |  |  |  |

|             | OTHER DISASSEMBLY PROBLEMS                           |  |  |  |  |  |  |  |  |  |  |

|             |                                                      |  |  |  |  |  |  |  |  |  |  |

| Appendix B: | HOW DATA IS ACQUIRED                                    |   |

|-------------|---------------------------------------------------------|---|

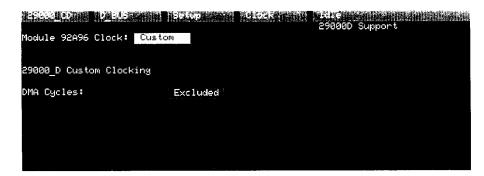

|             | C_BUS MODULE CUSTOM CLOCKING                            |   |

|             | D_BUS MODULE CUSTOM CLOCKING                            |   |

|             | CUSTOM CLOCKING                                         |   |

|             | DMA Cycles Excluded                                     |   |

|             | DMA Cycles Included                                     |   |

|             | SIGNALS                                                 |   |

|             | Synthesized Signals                                     |   |

|             | Signals Not Used for Disassembly                        |   |

| Appendix C: | SERVICE INFORMATION                                     |   |

|             | SERVICING SAFETY INFORMATION                            |   |

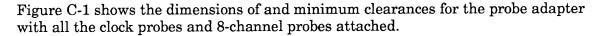

|             | PROBE ADAPTER DESCRIPTION                               |   |

|             | CARE AND MAINTENANCE                                    |   |

|             | SPECIFICATIONS                                          |   |

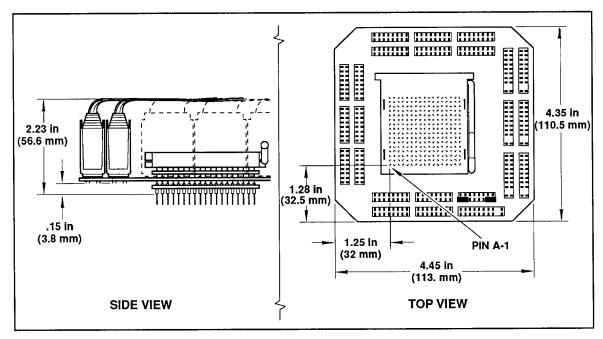

|             | DISCONNECTING CLOCK AND 8-CHANNEL PROBES                | ( |

|             | REMOVING AND REPLACING PODLETS                          | ( |

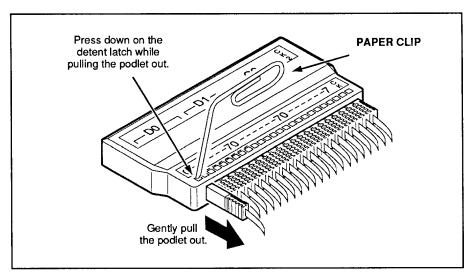

|             | Removing a Clock Probe or 8-Channel Probe Podlet        |   |

|             | from the Interface Housing                              | ( |

|             | Replacing a Clock Probe                                 | ( |

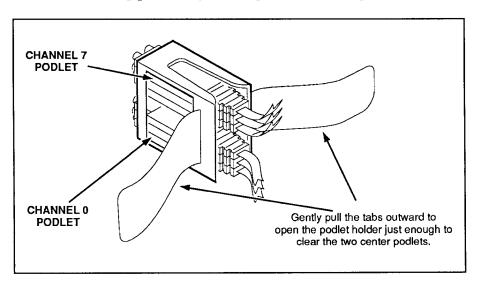

|             | Removing 8-Channel Probe Podlets from the Podlet Holder | ( |

|             | Replacing 8-Channel Probe Podlets                       | ( |

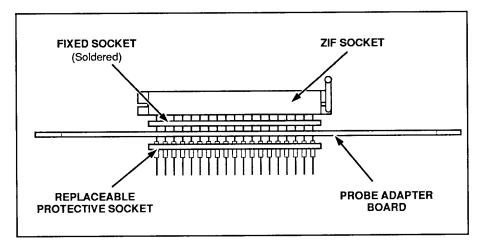

|             | REMOVING AND REPLACING SOCKETS                          | ( |

|             | ZIF Socket                                              | ( |

|             | Replaceable Protective Socket                           | ( |

|             | REPLACEABLE ELECTRICAL PARTS LIST                       | ( |

|             | REPLACEABLE MECHANICAL PARTS LIST                       | ( |

# **LIST OF FIGURES**

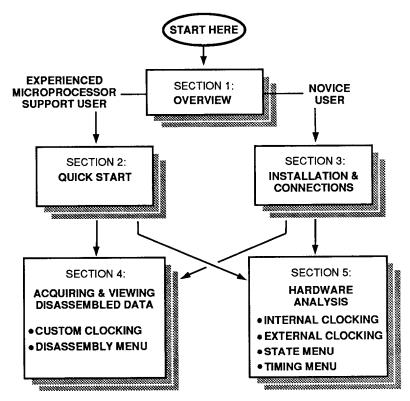

| Figure 1-1.  | How to proceed through this manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-2  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

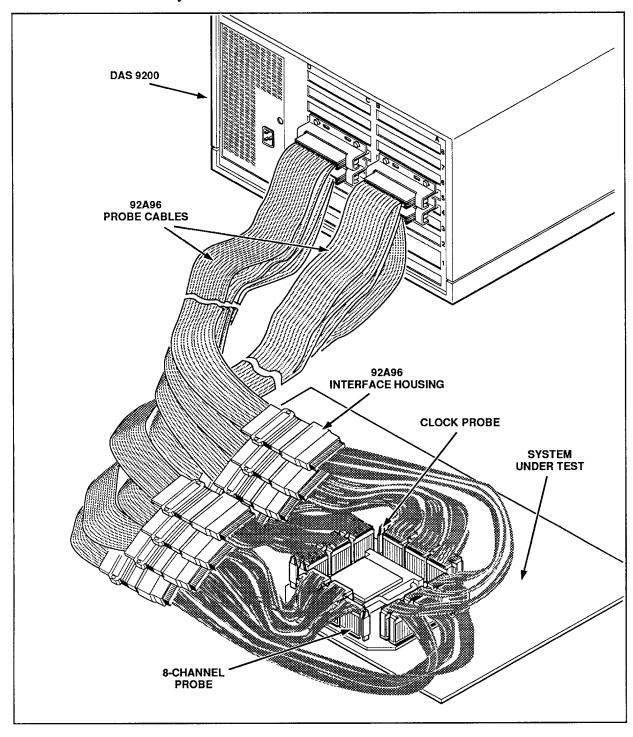

| Figure 1-2.  | connected to an Am29000/050 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-4  |

| 771 0.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.1  |

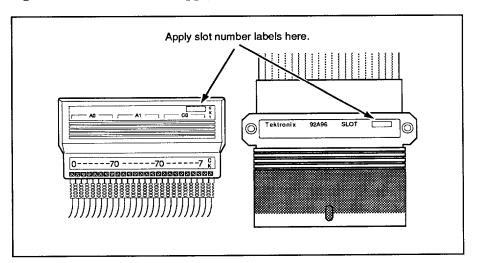

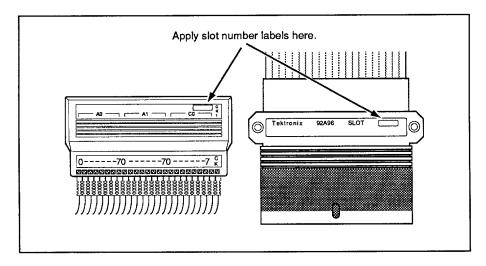

| Figure 2-1.  | Applying slot number labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1  |

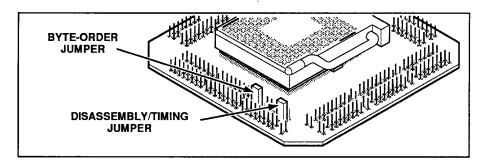

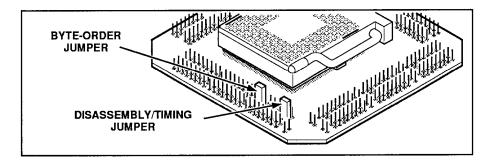

| Figure 2-2.  | Location of the byte-order and disassembly/timing jumpers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|              | on the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-3  |

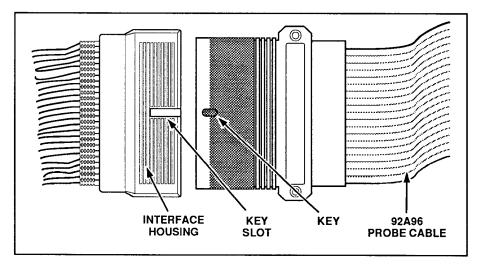

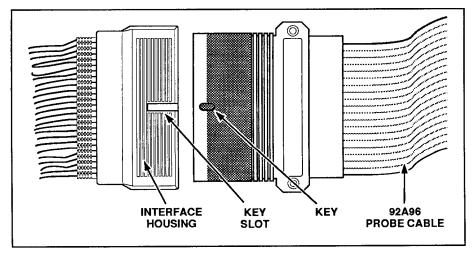

| Figure 2-3.  | Connecting the interface housing to the 92A96 probe cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-4  |

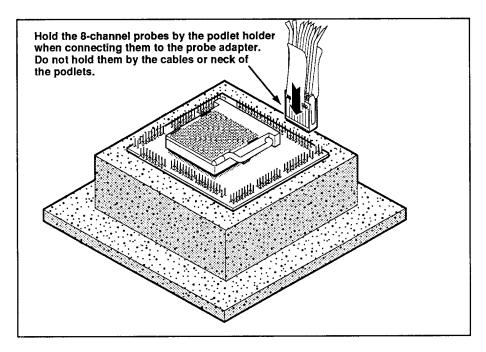

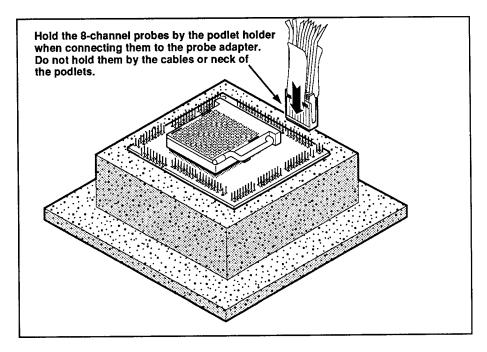

| Figure 2-4.  | Connecting clock and 8-channel probes to the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-5  |

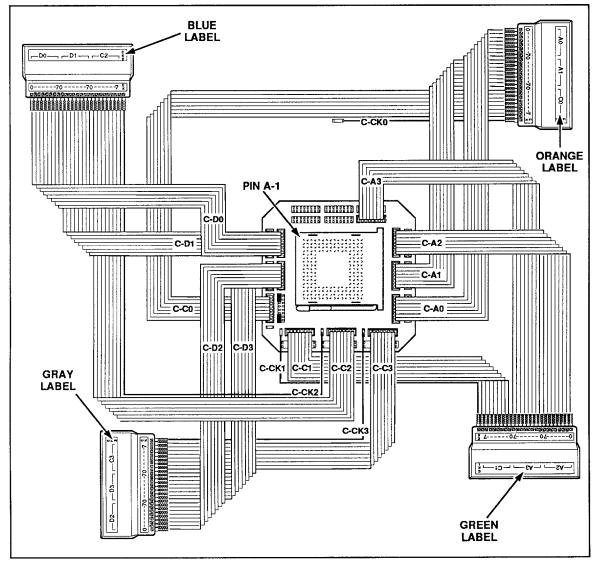

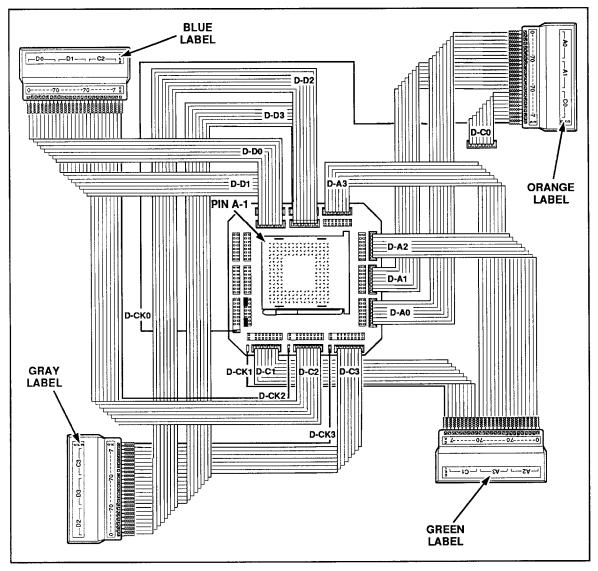

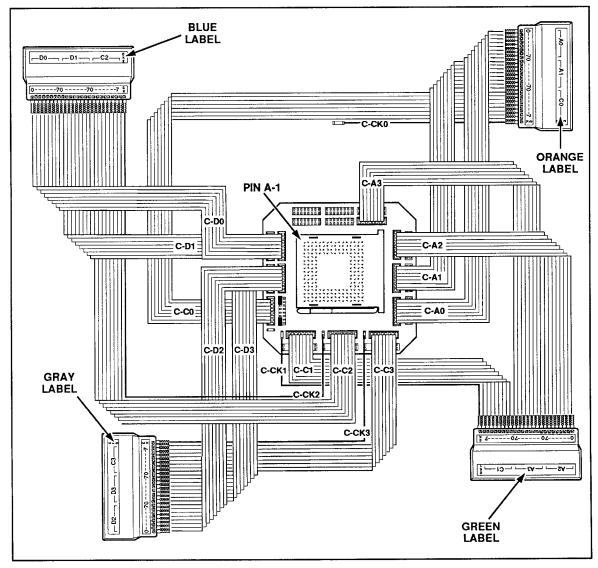

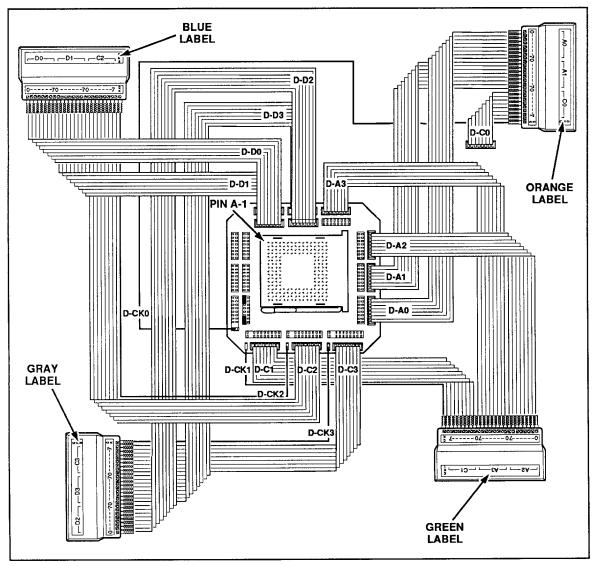

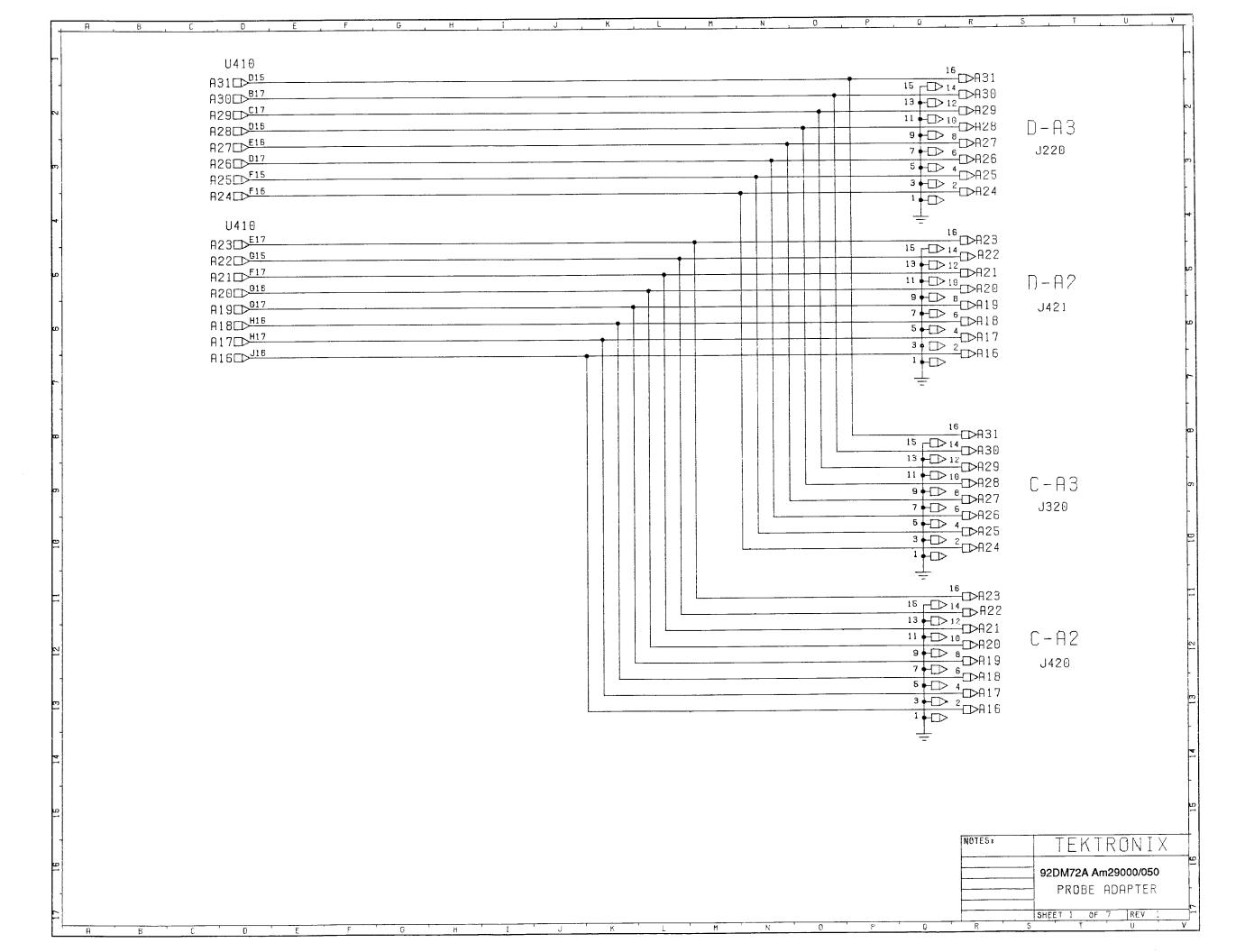

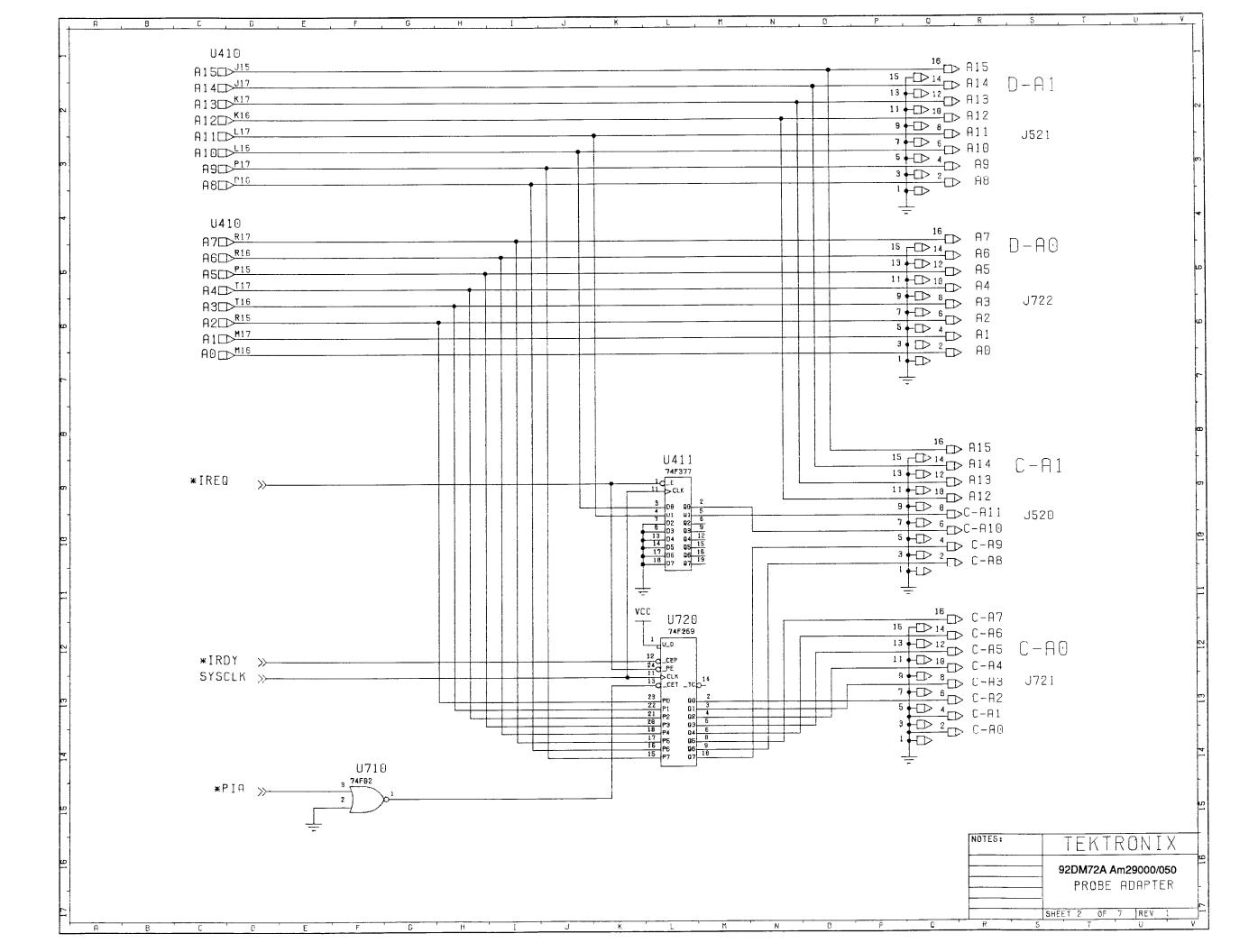

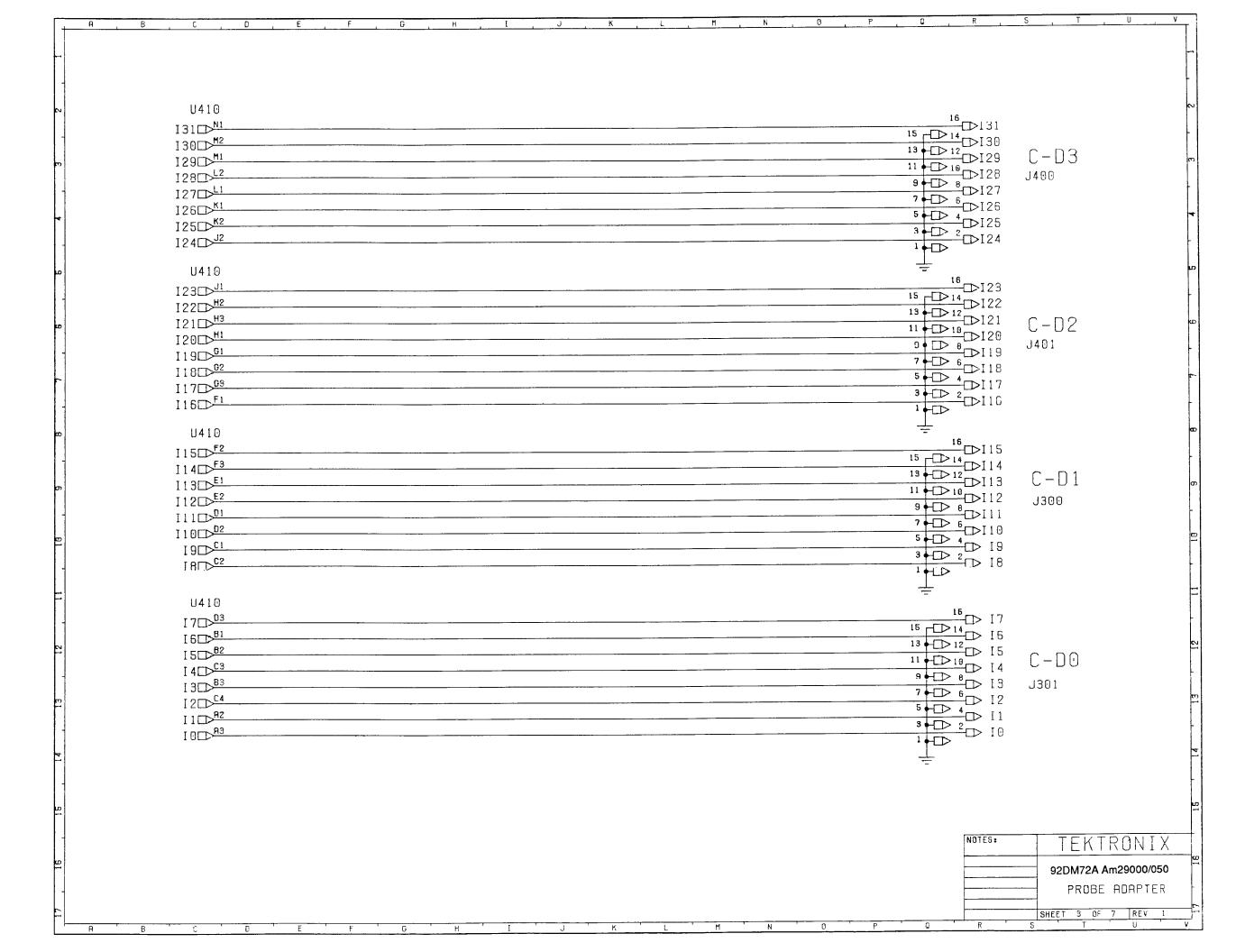

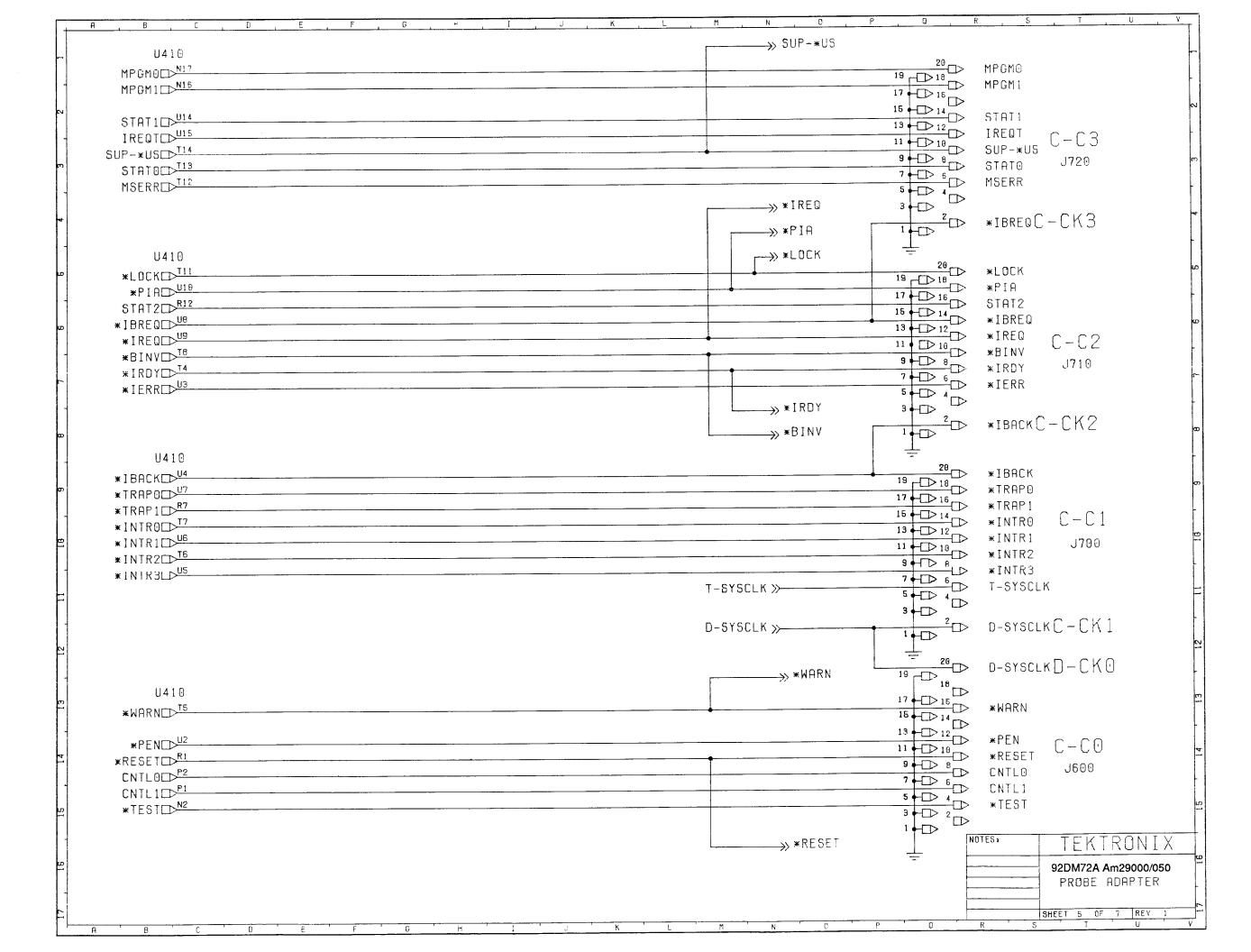

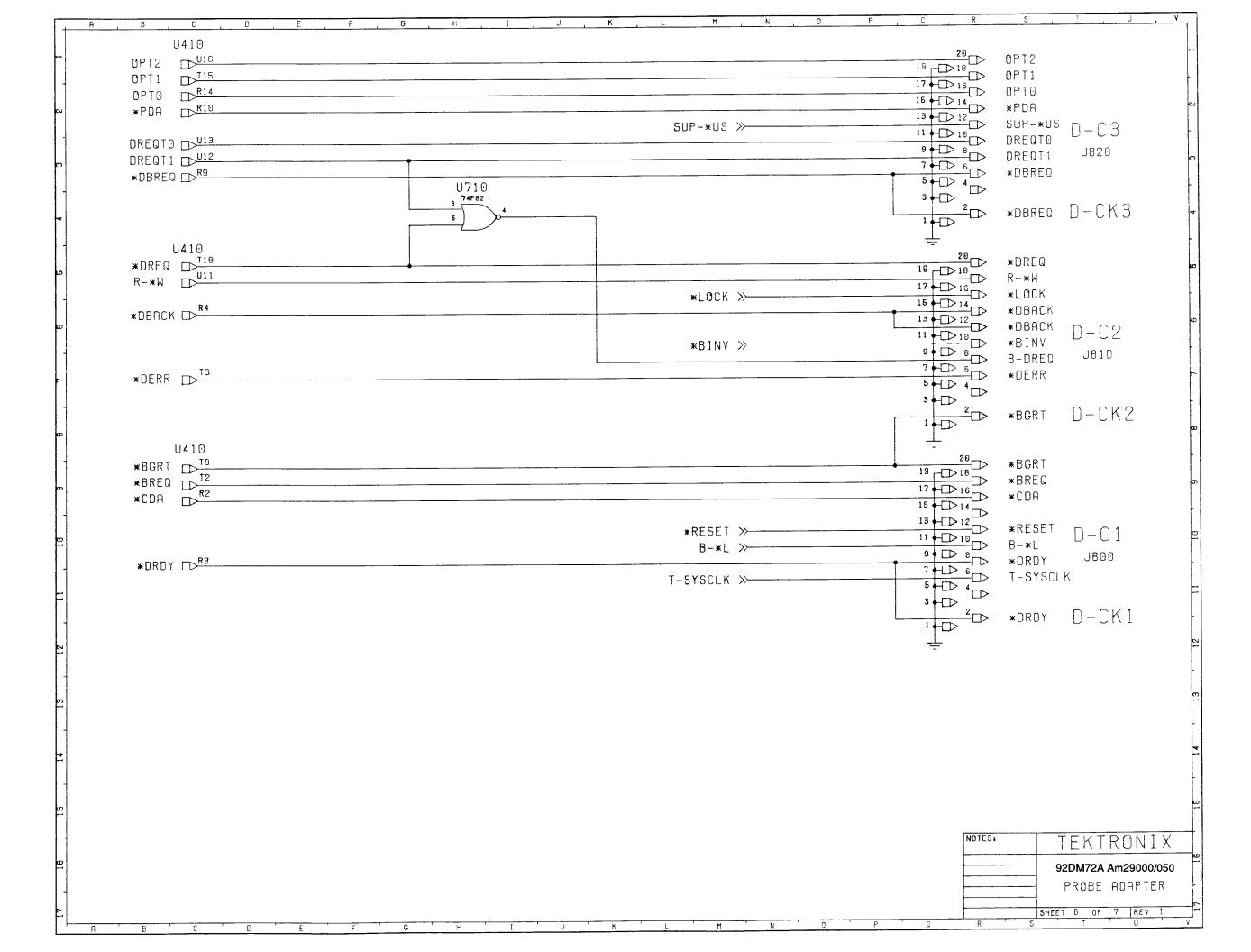

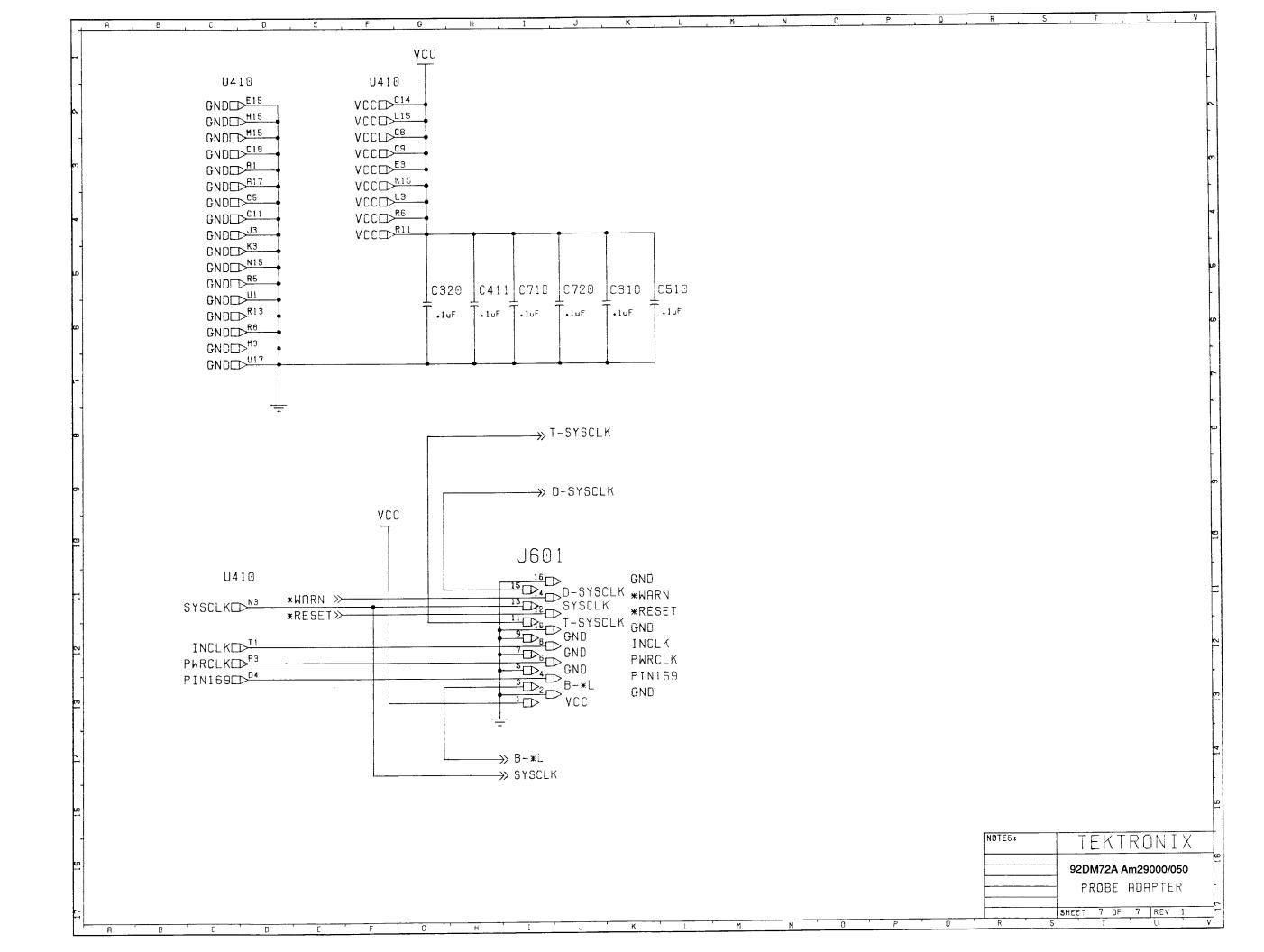

| Figure 2-5.  | Connections from the C_Bus module probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|              | to the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-6  |

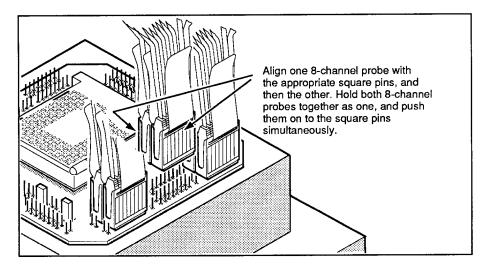

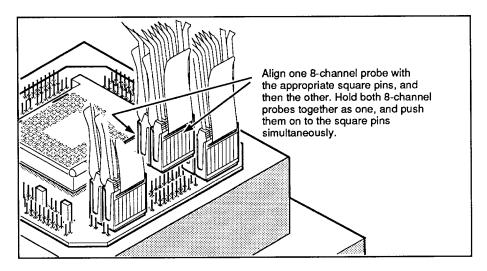

| Figure 2-6.  | Connecting six adjacent 8-channel probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-7  |

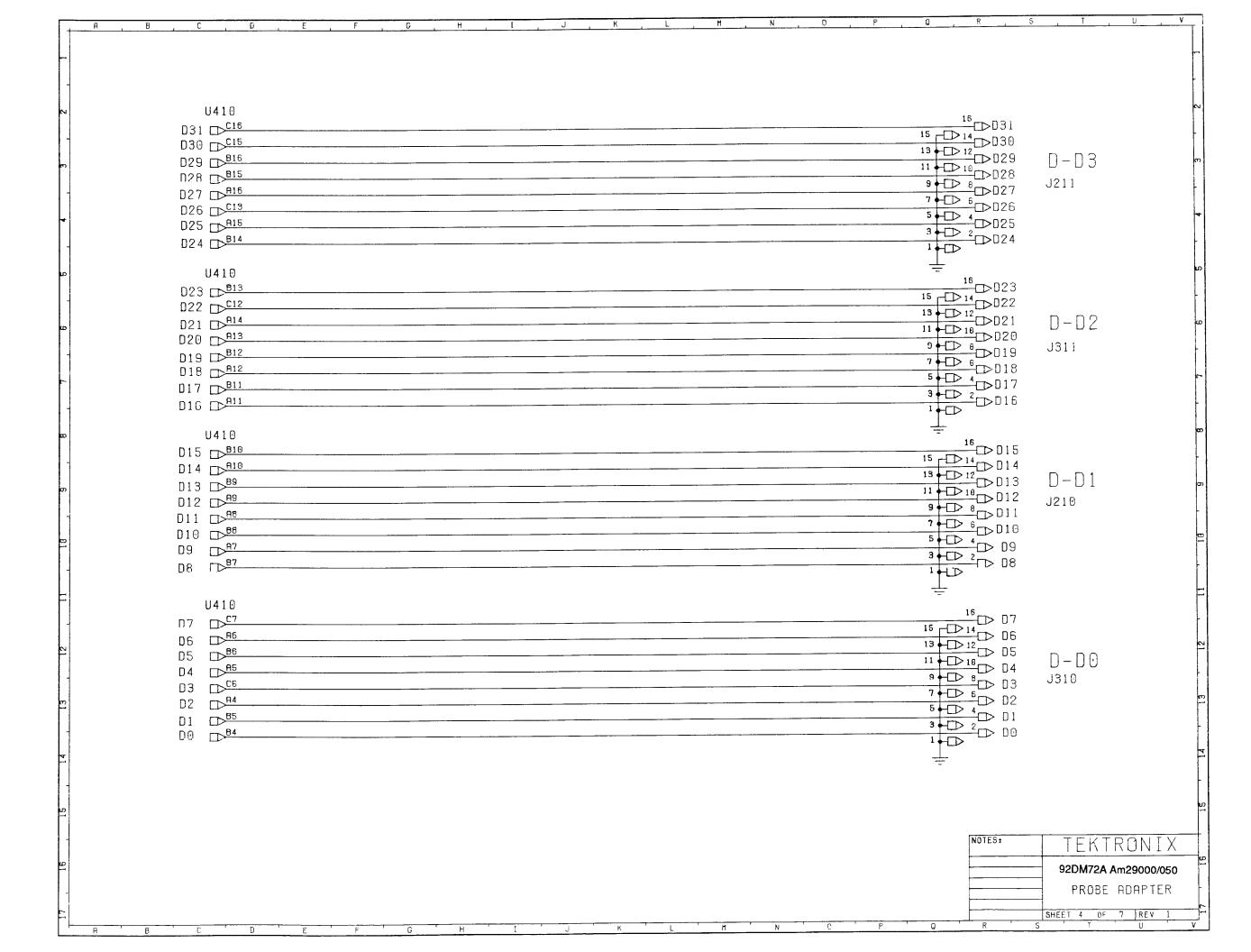

| Figure 2-7.  | Connections from the D_Bus module probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| _            | to the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-8  |

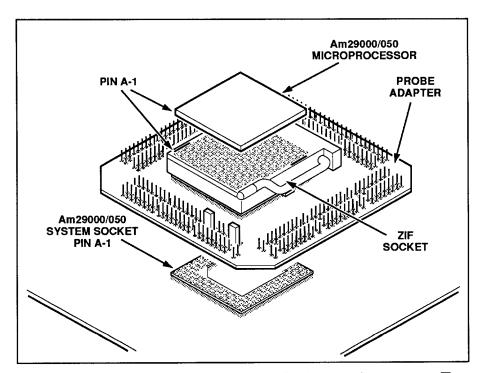

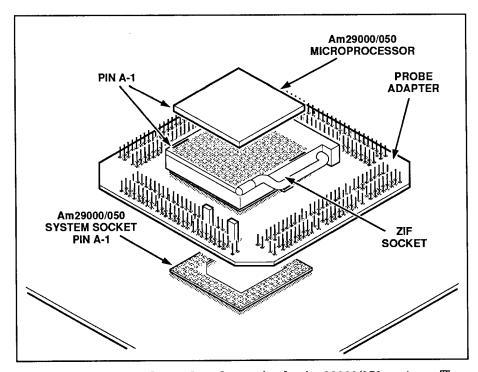

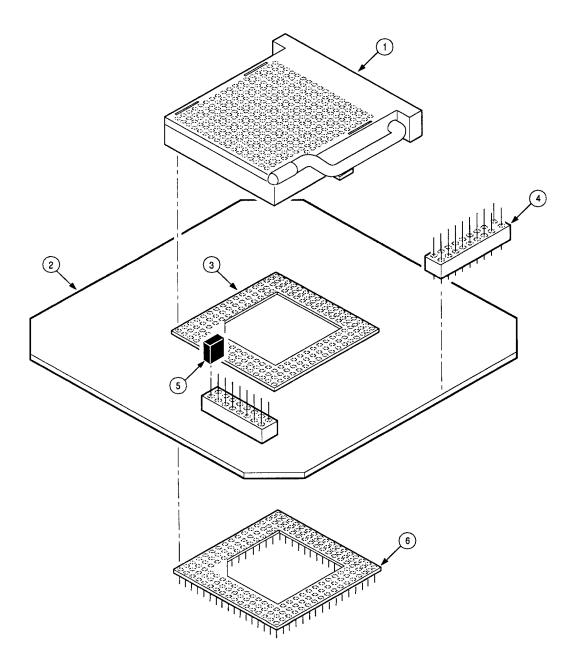

| Figure 2-8.  | Placing the probe adapter in the Am29000/050 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-9  |

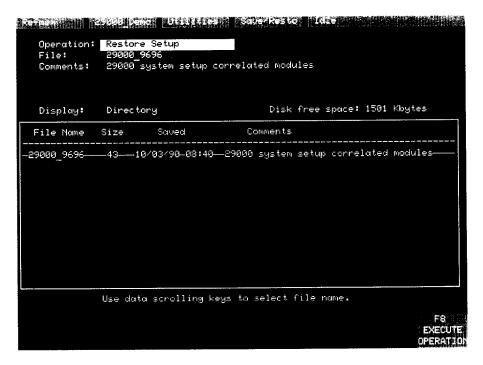

| Figure 3-1.  | Save/Restore menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-6  |

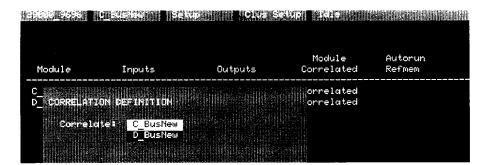

| Figure 3-2.  | Correlation Definition overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-7  |

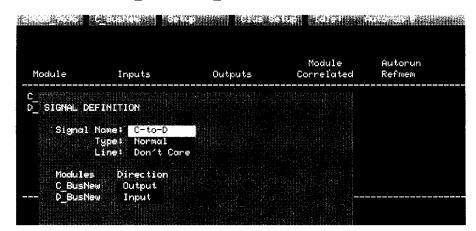

| Figure 3-3.  | Signal Definition overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-8  |

| Figure 3-4.  | Applying slot number labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-15 |

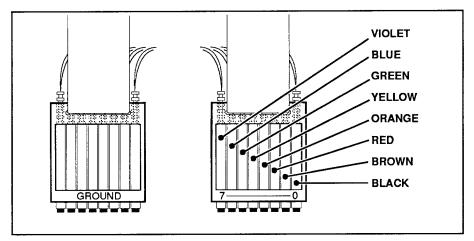

| Figure 3-5.  | Probe channel color and labels on an 8-channel probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-16 |

| Figure 3-6.  | Location of the byte-order and disassembly/timing jumpers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| rigure o o.  | on the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-17 |

| Figure 3-7.  | Connecting the interface housing to the 92A96 probe cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-19 |

| Figure 3-7.  | Connecting clock and 8-channel probes to the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-20 |

| Figure 3-8.  | Connections from the C_Bus module probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 20 |

| rigure 3-3.  | to the probe adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-21 |

| Dia 2 10     | Connecting six adjacent 8-channel probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-22 |

| Figure 3-10. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0-22 |

| Figure 3-11. | Connections from the D_Bus module probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 04 |