## **Instruction Manual**

# **Tektronix**

P6467 High-Speed Probe Adapter 070-9176-00

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

Copyright © Tektronix, Inc. 1995. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Tektronix will provide such service at Customer's site without charge during the warranty period, if the service is performed within the normal on-site service area. Tektronix will provide on-site service outside the normal on-site service area only upon prior agreement and subject to payment of all travel expenses by Customer. When or where on-site service is not available, Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

|                   | General Safety Summary                                                                                                                   | •                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                   | Service Safety Summary                                                                                                                   | vi                               |

|                   | Preface  Definition of Terms  Related Documentation                                                                                      | ix<br>ix                         |

| Getting Started   |                                                                                                                                          |                                  |

|                   | Product Description Accessories Installation Configuration Functional Check                                                              | 1<br>2<br>2<br>10<br>12          |

| Operating Basics  |                                                                                                                                          |                                  |

|                   | Probe Operation                                                                                                                          | 17<br>20<br>22                   |

| Reference         |                                                                                                                                          |                                  |

|                   | P6467 Acquisition Data Commands P6467 Reference Memory Commands LA–OffLine Applications                                                  | 26<br>28<br>29                   |

| Specifications    |                                                                                                                                          |                                  |

| Performance Verif | ication                                                                                                                                  |                                  |

|                   | Equipment Required                                                                                                                       | 37<br>38                         |

| Adjustment Proce  | dures                                                                                                                                    |                                  |

| Maintenance       |                                                                                                                                          |                                  |

|                   | Service Strategy Preparation Inspection and Cleaning Removal and Replacement Instructions Troubleshooting Procedures Theory of Operation | 51<br>51<br>52<br>52<br>53<br>54 |

| Replacable Parts |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                  | Parts Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55<br>56 |

| Appendicies      | Comp are repractate that she is the control of the | 50       |

|                  | Appendix A: P6467 High-Speed Probe Adapter Input Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63       |

|                  | Appendix B: P6467 Test Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65       |

| Index            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

# **List of Figures**

| Figure 1: Probe Connections and Clock Jumpering for Two Single-Card |    |

|---------------------------------------------------------------------|----|

| Modules                                                             | 3  |

| Figure 2: Probe Connections and Clock Jumpering for Two Two-Card    |    |

| Modules                                                             | 4  |

| Figure 3: Probe Connections and Clock Jumpering for Two Three-Card  |    |

| Modules                                                             | 5  |

| Figure 4: Clock Jumper Locations on the P6467 Probe                 | 6  |

| Figure 5: Connecting the Power Cable to the Probe                   | 7  |

| Figure 6: Disconnecting the Power Cable from the Probe              | 8  |

| Figure 7: Connecting the Probe to the System-Under-Test             | 9  |

| Figure 8: Sample Trigger Menu (First Module)                        | 11 |

| Figure 9: Sample Trigger Menu (Second Module)                       | 12 |

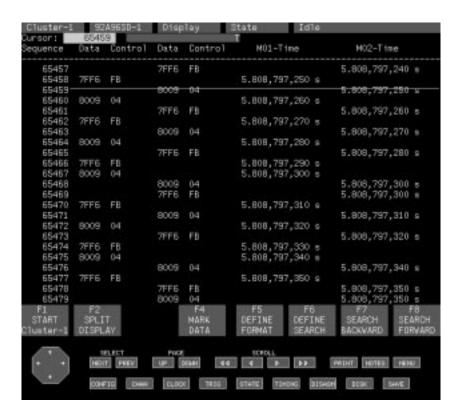

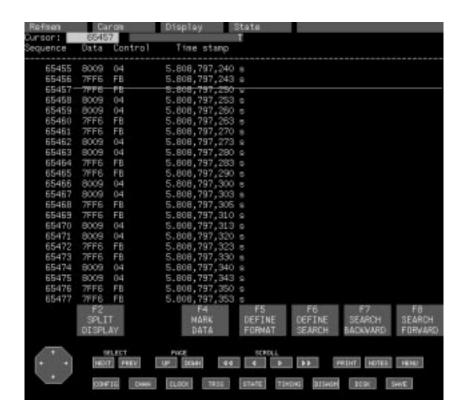

| Figure 10: Acquired Raw Data                                        | 19 |

| Figure 11: Saved Data from Figure 10                                | 20 |

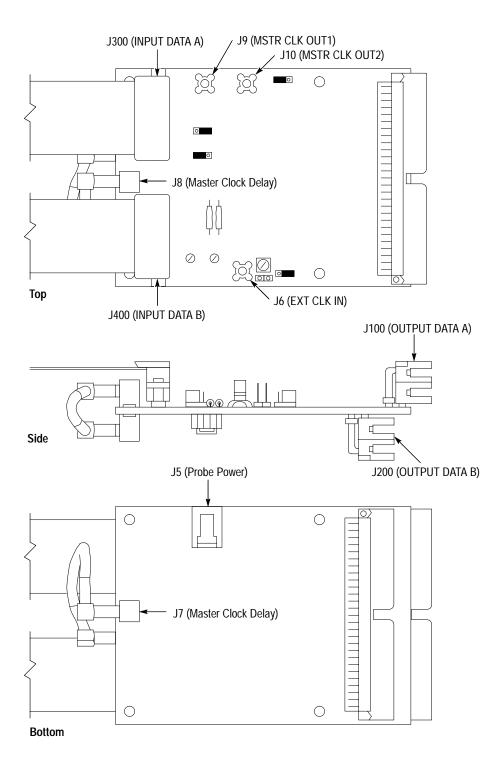

| Figure 12: P6467 Probe Connectors                                   | 21 |

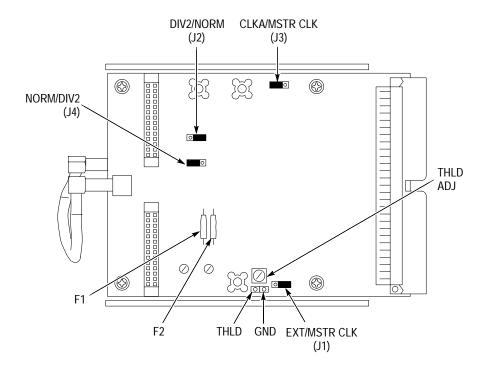

| Figure 13: P6467 Clock Jumpers and Clock Threshold Adjustment       |    |

| Locations                                                           | 23 |

| Figure 14: Trigger Menu Setup                                       | 40 |

| Figure 15: P6467 Test Board                                         | 65 |

## **List of Tables**

| Table 1: Factory Default Jumper Positions                          | 6  |

|--------------------------------------------------------------------|----|

| Table 2: Jumper Positions for Functional Checks                    | 13 |

| Table 3: Functional Check Data                                     | 15 |

| Table 4: 92A96 Fields                                              | 26 |

| Table 5: Signal Acquisition System                                 | 31 |

| Table 6: Power Distribution System                                 | 32 |

| Table 7: Environmental                                             | 32 |

| Table 8: Mechanical                                                | 33 |

| Table 9: HFS 9003 Stimulus System Menu Setups                      | 41 |

| Table 10: HFS 9003 Stimulus System to P6467 Test Board Connections | 42 |

| Table 11: Jumper Positions for the Setup & Hold and Maximum        |    |

| Operating Frequency Check                                          | 44 |

| Table 12: Test Setups for the NORM Operating Mode                  | 45 |

| Table 13: Test Setups for the DIV2 Operating Mode                  | 46 |

| Table 14: Jumper Positions and Clock Cable Connections             | 47 |

| Table 15: P6467 Probe Pinouts                                      | 64 |

## **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

## **Injury Precautions**

**Do Not Operate Without** To avoid electric shock or fire hazard, do not operate this product with covers or

**Covers** panels removed.

**Use Proper Fuse** To avoid fire hazard, use only the fuse type and rating specified for this product.

**Do Not Operate in**To avoid electric shock, do not operate this product in wet or damp conditions.

Wet/Damp Conditions

**Do Not Operate in an**To avoid injury or fire hazard, do not operate this product in an explosive **Explosive Atmosphere**To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.

**Avoid Exposed Circuitry** To avoid injury, remove jewelry such as rings, watches, and other metallic

objects. Do not touch exposed connections and components when power is

present.

### **Product Damage Precautions**

**Provide Proper Ventilation** To prevent product overheating, provide proper ventilation.

**Do Not Operate With**Suspected Failures

If you suspect there is damage to this product, have it inspected by qualified service personnel.

**Do Not Immerse in Liquids** Clean the probe using only a damp cloth. Refer to cleaning instructions.

## **Safety Terms and Symbols**

#### Terms in This Manual

These terms may appear in this manual:

**WARNING**. Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

#### **Terms on the Product**

These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

#### Symbols on the Product

The following symbols may appear on the product:

DANGER High Voltage

Protective Ground (Earth) Terminal

ATTENTION Refer to Manual

Double Insulated

#### **Overvoltage Category**

Overvoltage categories are defined as follows:

CAT III: Distribution level mains, fixed installation

CAT II: Local level mains, appliances, portable equipment

CAT I: Signal level, special equipment or parts of equipment, telecommunication, electronics

## **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone** Do not perform internal service or adjustments of this product unless another

person capable of rendering first aid and resuscitation is present.

With Power On

With Power On

Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

## **Preface**

The P6467 Instruction Manual is intended to help you setup and use the P6467 High-Speed Probe Adapter to acquire data from a system-under-test through a DAS/NT, DAS/XP, or a TLA 520 logic analyzer. The manual contains the following sections:

- Getting Started provides an overview of the P6467 adapter assembly, a list of accessories, installation and configuration instructions and a brief function check procedure.

- Operating Basics provides functional overview of the P6467 adapter assembly. It describes the connectors and clock jumpers on the probe.

- Reference provides reference information on acquiring data and using software commands to transfer acquired data to a host and saving acquired data in a reference memory.

- Specifications describes the specifications of the P6467 Probe.

- Performance Verification provides procedures for verifying the performance requirements of the P6467 Probe.

- Maintenance describes procedures for inspecting, cleaning, and servicing the P6467 Probe. It also includes troubleshooting procedures and a brief theory of operation.

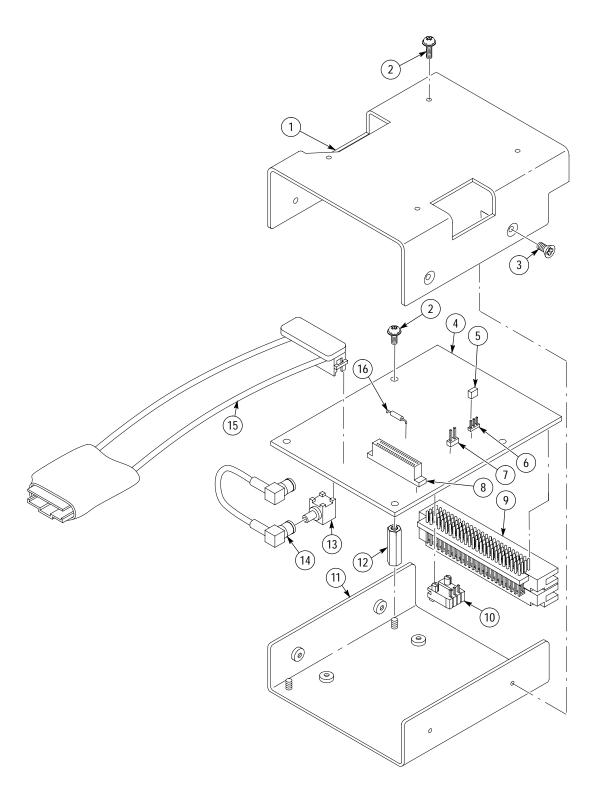

- Replaceable Parts lists the replaceable parts of the P6467 Probe and the probe accessories. It also provides an exploded view of the probe.

- The Appendix provides pinout tables of the P6467 Probe and brief information on the P6467 Test Board.

### **Definition of Terms**

You may encounter the following terms throughout this manual:

- 92A96 Module. The 92A96 Data Acquisition Module is a 96-channel, 100 MHz data acquisition module. It is available is different memory depths. the 92A96 Module is part of the DAS or TLA logic analyzer family.

- 92C96 Module. The 92C96 Data Acquisition Module is a variation of the 92A96 Module. The 92C96 Modules can be easily upgraded for more memory through upgrade kits.

The terms 92A96 and 92C96 are used interchangably throughout this manual.

- Logic Analyzer. The term logic analyzer is used with either DAS/NT, DAS/XP, or TLA 520 Logic Analyzers.

- Two-Card Module. A two-card module refers to a 92A96 Module with two individual 92A96 circuit boards or modules. The two cards form a 192-channel wide data acquisition module.

- Three-Card Module. A three-card module refers to a 92A96 Module with three individual 92A96 circuit boards or modules. The three cards form a 288-channel wide data acquisition module.

#### **Related Documentation**

In addition to this manual you may need to refer to the following documents while using the P6467 adapter assemblies:

- 92A96 & 92C96 Module User Manual. This manual describes the 92C96 and 92A96 Modules and how to set up, acquire, and display data with the acquisition module.

- DAS System User Manual. This manual describes how to use the DAS/NT or DAS/XP digital analysis systems to acquire data with the 92A96 Data Acquisition Modules.

- *TLA 510 & TLA 520 User Manual*. This manual describes how to use the Tektronix Logic Analyzers to acquire and display data with the 92A96 Data Acquisition Modules.

- DAS 9200 Programmatic Command Language User Manual. This manual describes how to use the Programmatic Command Language through GPIB or 92LAN to control the DAS from a remote location.

- 92LANP Instruction Manual. This manual describes how to communicate with a DAS mainframe through a local area network (LAN).

- DAS 9200 Acquisition and Pattern Generation Files User Manual. This manual describes the structure of acquisition data files. You may need to access this information if you intend to manipulate acquired data on a host computer.

- *LA-Offline User Manual*. This manual describes how to use the LA-Offline application software to analyze logic analyzer data on a host computer.

## **Getting Started**

This chapter provides an overview of the P6467 High-Speed Probe Adapter. It also describes the accessories available with the P6467 Probe as well as installation and configuration instructions.

### **Product Description**

The P6467 High-Speed Probe Adapter is designed for the DAS/NT, DAS/XP, or TLA 500 series logic analyzers with the 92A96 or 92C96 Data Acquisition Modules. The probe provides high-speed data acquisition and logic analysis for synchronous clocking applications. The probe has the following key features:

- Synchronous data acquisition of speeds of up to 195 MHz (DIV2 mode)

- Synchronous and asynchronous acquisition of data of speeds up to 100 MHz (NORM mode)

- Quick connection of data and clock signals

You can configure the probe to operate in one of two modes, DIV2 and NORM. When you use the probe in the DIV2 mode, the probe effectively doubles the speed and memory depth of a 92A96 Module. The NORM mode lets you acquire data synchronously and asynchronously in speeds up to 100 MHz.

Each probe connects to the system-under-test through two connectors. Each probe acquires 48 data signals and two clock signals through two flexible circuit board cables.

The probe comes with application software that lets you create a reference memory from the acquired data and transfers the data to a host. The data that is acquired by a pair of 92A96 modules is merged into a single column for analysis on the host. You control the application software using the EXEC Programmatic Command Language (PCL) command from a host through GPIB or 92LANP.

The application software also contains sample setups that you can use to help set up the logic analyzers. These setups can help you reduce the amount of time required to set up menus for certain applications.

In addition to viewing the data on a host from the logic analyzer, you can also view the data on the host with the Tektronix LA-OffLine software for off-line data analysis.

#### **Accessories**

The following standard accessories come with the P6467 High-Speed Probe Adapter (refer to *Replaceable Parts* on page 55 for part number information):

- Probe Power cable

- Clock Distribution cable

- Master Clock Delay cable

- P6467 Instruction Manual

- P6467 Support Software

- 92LANP Application Software and manual

#### Installation

This section provides installation information for the probe. This section does not provide installation instructions for the 92A96 Modules. If you purchased a 92A96 Module with your P6467 probe, refer to the *DAS System User Manual* or to the *92A96 and 92C96 Module User Manual* for instructions to install a 92A96 Module in a DAS mainframe. Then return to this manual for instructions to complete the installation of your P6467 probe.

If you have a TLA 520 logic analyzer, the 92A96 Modules are already installed in the mainframe (system unit).

#### **System Requirements**

Before using the probe you must meet the following hardware and software requirements on your DAS or TLA systems:

- A DAS or TLA mainframe with System Software Release 3, Version 1.51 or higher.

- The *Remote Operation Support* optional system software.

- Two or more 92A96 Data Acquisition Modules installed in the mainframe

- The 92LANP application software or a DAS mainframe with a 92C02 GPIB/Expansion Module.

## Configure and Install the Probes

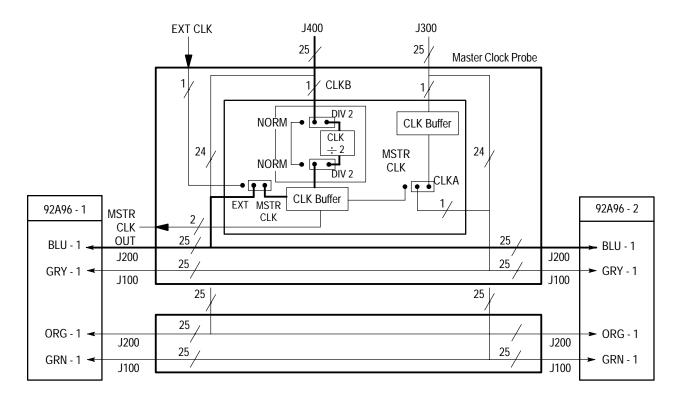

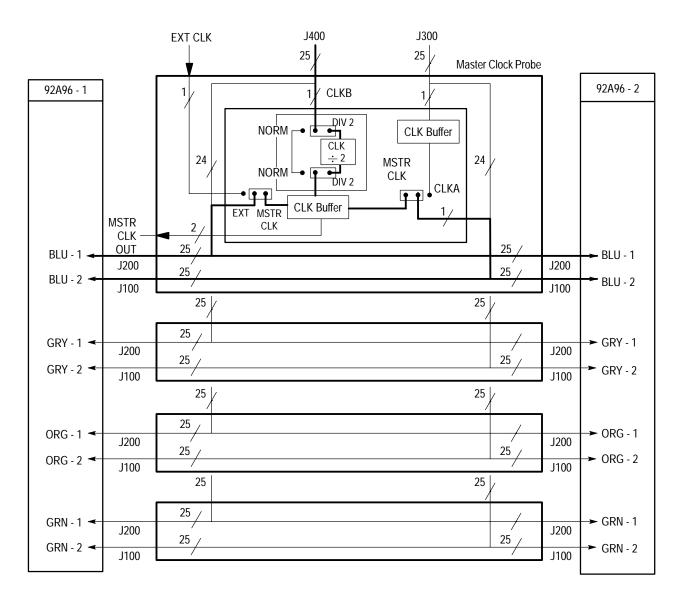

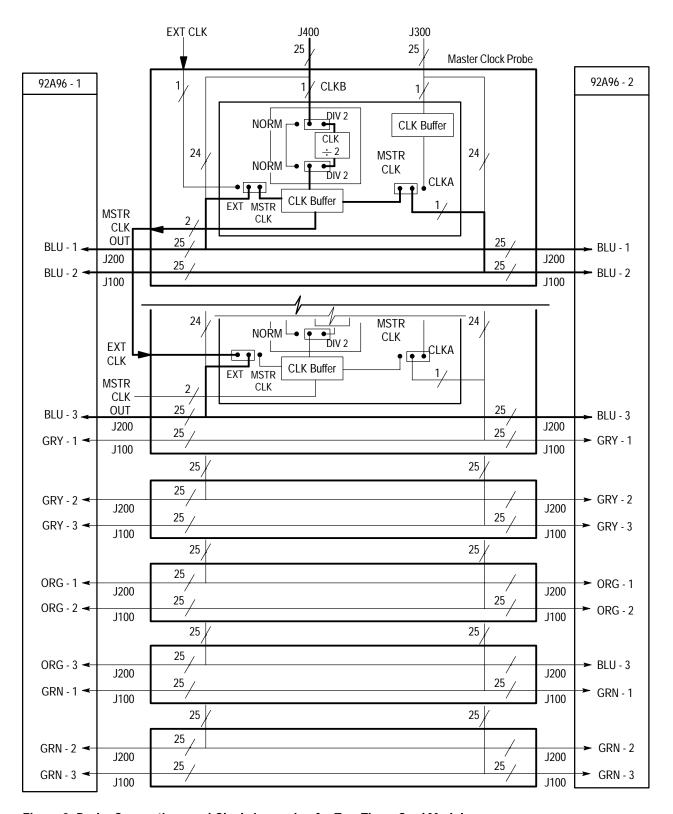

Before you use the P6467 probe you must determine the operating mode and the clocking requirements for your application. The clocking requirements depend on the number of cards in your 92C96 modules. You must specify one P6467 probe as the Master Clock probe and set the jumpers accordingly. Figures 1 through 3 show the clock jumpering and probe connections for two single-card modules, two two-card modules, and two three-card modules respectively. The clock signals are shown in bold in the illustrations. Table 1 on page 6 shows the jumper settings when the probe is shipped from the factory.

Note that in each of the examples, the P6467 probe connected to the blue-labeled probe cables is defined as the Master Clock probe; your application may call for a different color-coded probe label.

If you have the module configuration as shown in Figure 1, the position of the MSTR CLK/CLK A jumper can be in either the MSTR CLK or the CLK A position. However, the jumper must be in MSTR CLK position for the Master Clock probe in two- and three-card modules as shown in Figures 2 and 3.

Figure 1: Probe Connections and Clock Jumpering for Two Single-Card Modules

Figure 2: Probe Connections and Clock Jumpering for Two Two-Card Modules

Figure 3: Probe Connections and Clock Jumpering for Two Three-Card Modules

**Table 1: Factory Default Jumper Positions**

| P6467 Probe Jumper  | Jumper Position |

|---------------------|-----------------|

| J1 (EXT/MSTR CLK)   | MSTR CLK        |

| J2 (NORM/DIV2)      | DIV2            |

| J3 (CLK A/MSTR CLK) | CLK A           |

| J4 (DIV2/NORM)      | DIV2            |

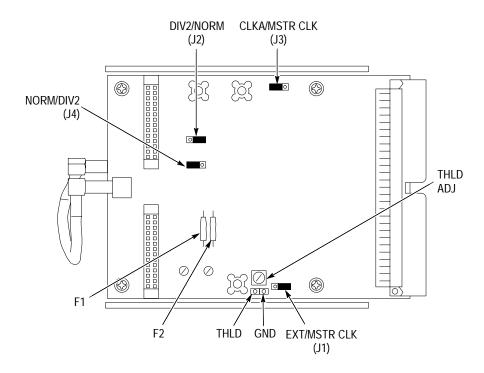

To set the clock jumpers on the Master Clock probe, you must remove the cover from the probe. To remove the cover, remove the two screws on each side of the probe. Figure 4 shows the locations of the jumpers on the probe. Note that it is only necessary to configure the jumpers on the Master Clock probe.

Figure 4: Clock Jumper Locations on the P6467 Probe

After determining the jumper locations on the probe, replace the probe cover and continue with the following steps:

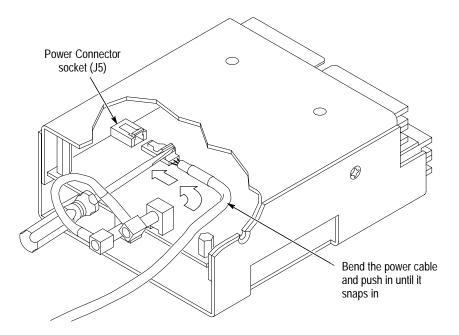

- **1.** Refer to Figure 5 and connect the probe power cable to the probes (each 92A96 Module can power two P6467).

- **a.** Bend the power cable near the connector as shown.

- **b.** Insert the power connector into the connector socket.

**c.** Use the tip of a pen or a small flat blade screw driver to push and lock the connector in place.

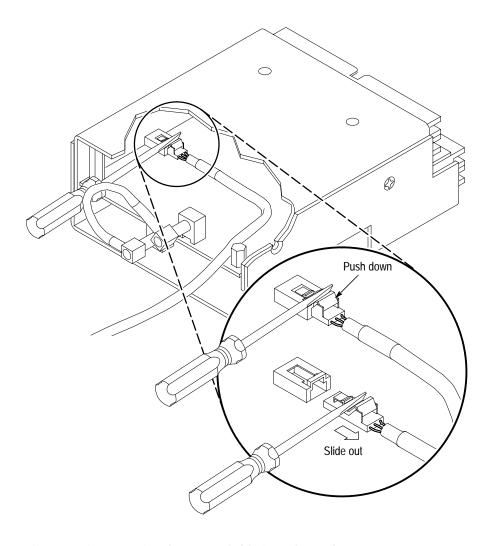

Refer to Figure 6 to disconnect the power cable from the probe.

- **2.** Repeat steps 1a through 1c to connect the power cable to reach remaining P6467 probe.

- **3.** Connect the power cable to the power connector on one of the 92A96 Modules in the logic analyzer.

Figure 5: Connecting the Power Cable to the Probe

Figure 6: Disconnecting the Power Cable from the Probe

- **4.** Connect the P6467 Probes to the 92A96 Probe Cables; if necessary, refer to Figures 1 through 3 on pages 3 through 5 respectively.

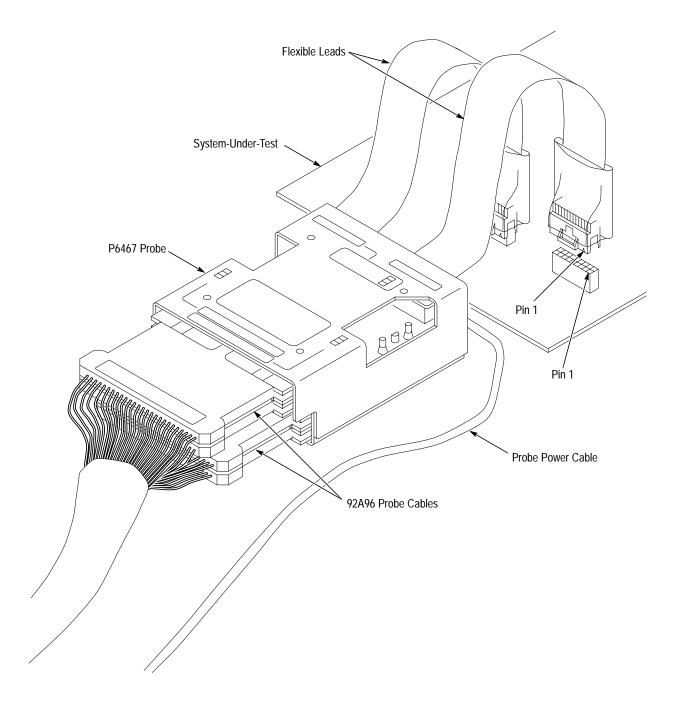

- **5.** Connect the flexible leads of the probe to the system-under-test. Refer to Figure 7 to ensure that you properly connect the probe to the system-undertest (pin 1 of the probe to pin 1 of the probe connector).

Figure 7: Connecting the Probe to the System-Under-Test

Install the Software

Install the P6467 support software from the floppy disk using the Install Application selection from the Disk Services menu. Insert the floppy disk in the disk drive and follow the on-screen instructions to load the support software.

If you intend to use the 92LANP application software with the P6467 Support software, refer to the software installation instructions in the 92LANP Instruction Manual to install the 92LANP software on the logic analyzer.

## Configuration

Before you can acquire data with the P6467 probe you must determine how you want to use the probe, adjust the clock threshold voltage, and then set up logic analyzer to acquire data.

#### Configure the Probe Hardware

If you have not already done so, configure the clock jumpers on the probe following the instructions under *Configure and Install the Probes* beginning on page 3.

#### Adjust the Probe Threshold Voltage

You can adjust the threshold voltage of the clock inputs on the P6467 probe to meet the needs of your application. You only need to adjust the threshold voltage on the Master Clock probe. When shipped from the factory, the theshold voltage is set to 2 V.

To adjust the threshold voltage connect a digital voltmeter from test point THLD and the adjacent ground pin. The location of test point THLD is shown in Figure 4 on page 6. Adjust the threshold control (THLD ADJ) for a reading between -1.6 V and +2.6 V.

#### Set Up the Logic Analyzer

Setting up the logic analyzer consists of defining the Setup menus. The P6467 software contains an example of a setup file that you can restore from the hard disk.

The following steps summarize the basic setups, if necessary, refer to the 92A96 & 92C96 Module User Manual for detailed information on using the Setup menus of the logic analyzer.

- 1. Use the System Configuration menu to define the cluster setups.

- **a.** Separate the 92A96 Modules into two separate, one-card, two-card, or three-card modules.

- **b.** Specify a cluster for the modules.

- **2.** Use the Cluster Setup menu to correlate the two modules and to define the signals between the two modules.

- **3.** For each module, use the 92A96 Configuration menu to specify the acquisition memory depth.

- **4.** For each module, use the 92A96 Channel menu to define the channel setups and the data and clock threshold voltages. Set the clock threshold voltage to **VAR** –**1.85 V** and the data threshold voltage to **VAR** +**1.90 V**.

- 5. For each module, use the Clock menu to define the clocking requirements. If you setup the probe for use in the DIV2 operating mode, set the Clock menu to **External**. Set up one module to clock on the rising edge of the clock (with no qualification) and set up the second module to clock on the falling edge of the same clock as the first module.

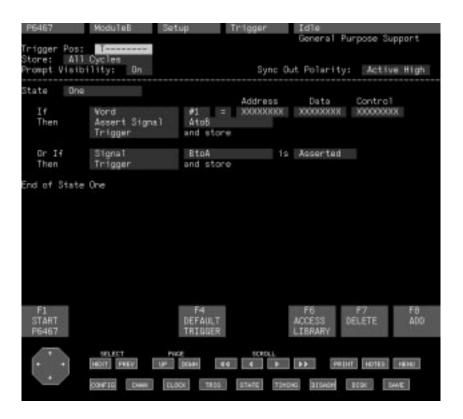

- **6.** For each module, use the Trigger menu to define the data you want to acquire and to assert and monitor the signals defined in the Cluster Setup menu. Figure 8 shows an example of one of the Trigger menus (the Trigger menu must be the same for both modules in the module pair with the exception of the definition of the signals used between the two modules).

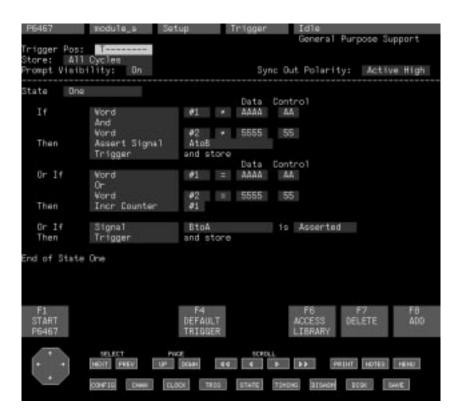

Figure 8: Sample Trigger Menu (First Module)

Figure 9 shows an example of the second Trigger menu of the module pair. The main difference between the two Trigger menus is the use of signals between the two modules. One module asserts the first signal and receives the second signal, while the other module receives the first signal and asserts the second signal.

Figure 9: Sample Trigger Menu (Second Module)

### **Functional Check**

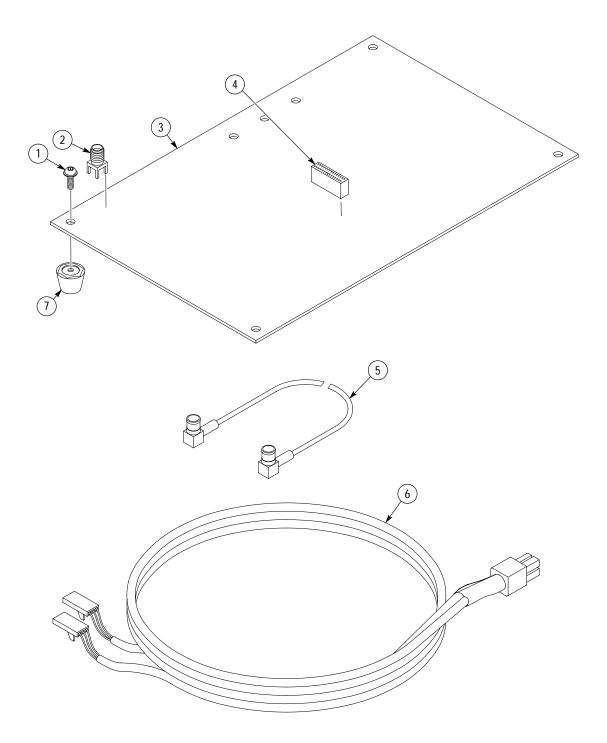

You can verify the basic functionality of the probe by acquiring data and viewing it on the logic analyzer. You can use the following checks as an incoming inspection to determine if further testing or repair is necessary. The checks consist of connecting the probe to the P6467 Test Board and acquiring data through individual channels.

#### **Equipment List**

You will need the following equipment to perform the functional checks:

- TLA 520 Logic Analyzer, DAS/NT, or DAS/XP Logic Analyzer with two 92A96 or 92C96 Data Acquisition Modules

- Two sets of coaxial probe cables (Tektronix part number 198-5761-XX) or two sets of standard 92A96 probe cables

- One P6467 High—Speed Probe Adapter with Probe Power Cable

- P6467 Test Fixture (Tektronix part number 067-0262-XX)

- A pulse generator capable of supplying a 20 MHz, 0 to 3 V signal into 50  $\Omega$ , a 50% duty factor, a 1 to 4 ns rise time, and a complementary output

- One 42-inch 50  $\Omega$  coaxial cable (Tektronix part number 012-0057-01)

- One 20-inch 50  $\Omega$  coaxial cable (Tektronix part number 012-0076-00)

- Two 3 mm male-to-female BNC adapters (Tektronix part number 015-1018-XX)

#### **Functional Check Setups**

The following steps describe the setups necessary to perform the functional checks. The procedures assume that you are starting the checks with the probes disconnected from the logic analyzer and that the logic analyzer is powered off. The procedures also assume that you will use the setups stored on the hard disk from the P6467 Support Software.

1. Remove the cover from the P6467 Probe and set jumpers to the positions indicated in Table 2.

Table 2: Jumper Positions for Functional Checks

| P6467 Probe Jumper  | Jumper Position |

|---------------------|-----------------|

| J1 (EXT/MSTR CLK)   | MSTR CLK        |

| J2 (NORM/DIV2)      | DIV2            |

| J3 (CLK A/MSTR CLK) | CLK A           |

| J4 (DIV2/NORM)      | DIV2            |

2. Connect the blue-labeled probe cables from the two 92A96 modules in the logic analyzer and connect them to top pair of connectors (OUTPUT DATA A) on the P6467 Probe.

- **3.** Connect the Probe Power cable from the power connector of one of the 92A96 Modules on the logic analyzer to the power connector on the P6467 Probe (if necessary refer to Figure 5 on page 7 for information on connecting the Power cable).

- **4.** Power on the logic analyzer and the display terminal.

- **5.** After the logic analyzer completes the power-on diagnostics, select the Save/Restore menu and restore the setup named P6467-PVD

The restored setup has the menus already programmed for the functional checks. If the predefined setup does not match your hardware configuration, you will need to further modify the menus for your configuration (if necessary, refer to the 92A96 & 92C96 Module User Manual for information on using the setup menus).

- **6.** Connect the two 50  $\Omega$  cables to the outputs of the pulse generator.

- 7. Connect one of the 3 mm (SMA male-to-female BNC adapters to J1 and J13 of the P6467 Test Board.

- **8.** Connect the two BNC cables to the 3 mm (SMA male-to-female BNC adapters.

- **9.** Connect the shorter BNC cable from the complement output of the pulse generator to the clock connector (J13) on the P6467 Test Board.

- **10.** Connect the longer BNC cable from the output of the pulse generator to the J1 connector on the P6467 Test Board.

- **11.** Connect the INPUT DATA A flex lead of the probe to the 30-pin connector on the P6467 Test Board.

- **12.** Set the pulse generator for a 20 MHz 0 V to +3 V output signal with a 50% duty factor and a 1 to 4 ns rise time (if necessary, use an oscilloscope to verify the setup).

- **13.** Start the logic analyzer by selecting function key F1: START on the logic analyzer.

**NOTE**. If the logic analyzer displays a SLOW CLOCK message, check that all of the jumpers are in the correct positions on the probe and that you have correctly connected the clock signal from the pulse generator to the P6467 Test Board.

**14.** The logic analyzer should trigger and display the State Display menu. The displayed data should resemble the following data:

| 0000 | A0 |      |    |

|------|----|------|----|

| 0000 | 40 | 0000 | 00 |

| 0000 | AU | 0000 | 00 |

| 0000 | A0 | 0000 | 00 |

| 0000 | A0 | 0000 | 00 |

|      |    | 0000 | 00 |

The check verifies the functionality of the clock signal and the one data channel. You can verify the functionality of the remaining data channels by moving the pulse generator connection from J1 of the P6467 Test Board to one of the other channels and repeating the test. The acquired data in the State Display menu should track the data channel as you connect each data channel to the pulse generator output. Table 3 shows the expected data with respect to the data channel connection on the P6467 Test Board.

**Table 3: Functional Check Data**

| P6467 Test Board<br>Connection | INPUT DATA A or<br>INPUT DATA B<br>NORM Mode Data | INPUT DATA B<br>DIV2 Mode Data |

|--------------------------------|---------------------------------------------------|--------------------------------|

| J1                             | 0000 A0<br>0000 00                                | 0000 A0<br>0000 A0             |

| J2                             | 0000 50                                           | 0000 50<br>0000 50             |

| J3                             | 0000 0A<br>0000 00                                | 0000 0A<br>0000 0A             |

| J4                             | 0000 05                                           | 0000 05<br>0000 05             |

| J5                             | A000 00<br>0000 00                                | A000 00<br>A000 00             |

| J6                             | 5000 00 0000 00                                   | 5000 00 5000 00                |

| J7                             | 0A00 00<br>0000 00                                | 0A00 00<br>0A00 00             |

| J8                             | 0500 00 0000 00                                   | 0500 00<br>0500 00             |

| J9                             | 00A0 00<br>0000 00                                | 00A0 00<br>00A0 00             |

Table 3: Functional Check Data (Cont.)

| P6467 Test Board<br>Connection | INPUT DATA A or<br>INPUT DATA B<br>NORM Mode Data | INPUT DATA B<br>DIV2 Mode Data |

|--------------------------------|---------------------------------------------------|--------------------------------|

| J10                            | 0050 00 0000 00                                   | 0050 00<br>0050 00             |

| J11                            | 000A 00<br>0000 00                                | 000A 00<br>000A 00             |

| J12                            | 0005 00 0000 00                                   | 0005 00 0005 00                |

- **15.** Disconnect the INPUT DATA A flex lead from the P6467 Test Board and connect the INPUT DATA B flex lead.

- **16.** Disconnect the blue-labeled probe cable from the top connector of the P6467 Probe and connect them to the bottom connector (OUTPUT DATA B).

- **17.** Repeat steps 13 through 14 to check the functionality of the second half of the probe. The acquired data in the State Display menu should resemble the following data when you connect the data signal to J1:

After completing the checks, return the clock jumpers to their original positions and replace the cover on the probe.

## **Operating Basics**

This chapter provides basic operating information for the P6467 High Speed Probe Adapter. The following information is included in this chapter:

- Probe operation

- Descriptions and locations of connectors

- Descriptions and locations of jumpers

### **Probe Operation**

There are two basic operating modes for the P6467 probe that you can set by jumpers J2 and J3, NORM and DIV2. The following sections describe the operating modes and the clock distribution.

#### **NORM Operating Mode**

The NORM operating mode lets you acquire data synchronously and asynchronously at speeds up to 100 MHz. The NORM mode acquires data in a similar matter as the standard 92A96 probes. The main difference is that the P6467 probe does not have individual podlet connectors. A 30-pin connector is used to connect to a mating connector on the system-under-test. You can connect the flex cables to one of two mating connectors available from AMP Inc. The two connectors and the pinout information is described in *Appendix A: P6467 High-Speed Probe Adapter Input Connector*.

When you use the probe in the NORM operating mode, the flex cable defined as the Master Clock channel passes the signals from the probe to J200 (bottom two connectors). Jumper J1 (MSTR CLK/EXT) must be in the MSTR CLK position.

You only need to connect one of the probe cables to either of the top two or bottom two probe cable connectors.

#### **DIV2 Operating Mode**

The DIV2 mode (divide-by-two) operating mode lets you acquire synchronous data at speeds greater than 100 MHz. If you choose to use the probe in the DIV2 mode, you must be aware of the following limitations of this operating mode:

- Only synchronous acquisitions are allowed.

- You can only use one clock signal with no clock or data qualifications.

- Data is sampled only on the rising edge of the supplied clock.

If you use the DIV2 mode, your logic analyzer must have two 92A96 Modules. Each module must contain one, two, or three 92A96 acquisition cards. One of the 92A96 Module samples data on the rising edge of the clock while the other samples data on the falling edge of the clock.

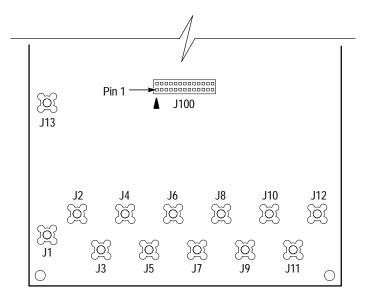

You must connect two probe cables to each of the J100 and J200 connectors on the P6467 probe. Each pair of probe cables must connect to the same relative position and color-coded connector of each 92A96 Module.

You must also define which P6467 probe acquires the Master clock signal. The flex cable assembly connecting to J400 of that probe is defined as the Master Clock channel and acquires the clock signal.

You can only acquire one clock signal in the DIV2 operating mode. This clock signal is distributed to each of the acquisition cards in the module. If your application requires three-card modules, you must use a clock distribution cable to connect from the Master Clock probe to a second P6467 probe as shown in Figure 3 on page 5. The second P6467 probe provides the clock for the last acquisition card in the module.

In addition to the hardware and clocking requirements, the following setup requirements exist:

- Both modules need to be set to the same trigger program and assert a signal that the other module monitors. (See Figure 8 on page 11 for an example of a sample trigger program.)

- The Clock menu setup requires that each module uses the same clock with one module sampling data on the rising edge of the clock while the other module samples data on the falling edge of the clock.

#### **Clock Distribution**

When you use the clock from the Master Clock channel, the clock distribution is essentially the same in the NORM and DIV2 operating modes.

For single-card modules, you must place the MSTR CLK/EXT jumper in the MSTR CLK position. When the jumper is in the MSTR CLK position, the clock drivers connect the Master clock to the probe cables connected to J200.

For two-card modules, you must place the CLK A/MSTR CLK jumper in the MSTR CLK position.

For three-card modules, you must use two P6467 Probes to properly distribute the clock signal on the probe. Place the CLK A/MSTR CLK jumper in the MSTR CLK position on the Master Clock probe. Use one of the external clock connectors, J9 or J10, to drive a second P6467 Probe. Connect a clock cable from J9 or J10 of the Master Clock probe to the EXT CLK IN connector on the second P6467 Probe. You must also place the MSTR CLK/EXT jumper of the second probe in the EXT position.

# Transferring Data to the Host

The P6467 Probe acquires data from two acquisition modules on alternate clock edges. In many cases the resultant data may be difficult to use and interpret. The P6467 Probe comes with support software to transfer the acquired data to a host computer and to save the data in a manner that is easier to analyze. You can work with the acquired data directly with host computer applications, or you can save the data in a reference memory for use with the logic analyzer.

Use the CARDATA command to transfer the acquired data to a host computer for use with host computer applications. Use the CARSTORE command to save the acquired data in a reference memory. Both these commands and examples of their use are describe in the *Reference* chapter beginning on page 25.

Figure 10 shows an example of acquired data before using the application software to make the data more readable. Figure 11 shows the same data aligned and saved in a reference memory after executing the CARSTORE command on the host computer.

Figure 10: Acquired Raw Data

Figure 11: Saved Data from Figure 10.

## **Descriptions and Locations of Connectors**

The P6467 Probe acquires data from a system-under-test and sends the data to the logic analyzer. One probe can aquire data from two 92A96 probe cables from two acquisition modules (one module pair). Figure 12 shows the connectors on the probe (probe covers removed).

Figure 12: P6467 Probe Connectors

The purpose of each connector on the probe follows:

- J6 (EXT CLK IN). Use this clock input connector when you derive the clock from another P6467 Probe that has been defined as the master clock.

- J7, J8 (MASTER CLOCK DELAY). Use these two connectors to delay the clock transition with longer lengths of 75  $\Omega$  cables relative to the data signal transitions (if needed) to meet the setup and hold timing requirements for the logic analyzer.

- J9 (MSTR CLK OUT1), J10 (MSTR CLK OUT2). Use these two connectors if your logic analyzer module needs more than two acquisition cards. These connectors distribute the clock to other P6467 Probes while preserving the timing relationship between the master clock and data on other probes. Use only the clock cable that came with your probe, otherwise the timing relationship can not be guaranteed.

- J300 (INPUT DATA A). This connector is the Data A clock and data input flex connector. The flex cable directs the signals from the system-under-test to the J100 Output Data connector (top two probe connectors) The clock signal from this connector is designated as the CLK A signal at J3.

- J400 (INPUT DATA B). This connector is the Master clock and data input flex connector. This flex cable assembly is designated as the Master clock input for the probe; only the clock input on this flex cable can be designated as the Master clock. The flex cable directs the signals from the system-under-test to the J200 Output Data connector (bottom two probe connectors).

- J100 (OUTPUT DATA A). This connector is the Data A clock and data output connector. The top two 50-pin connectors connect to the 92A96 ribbon or coaxial cable connectors.

- J200 (OUTPUT DATA B). This connector is the Master clock and data channel output connector. The bottom two 50-pin connectors connect to the 92A96 ribbon or coaxial cable connectors.

- J5 (Probe Power). The probe power cable connects to the probe at J5. The probe receives its power from the power connector of the acquisition module in the logic analyzer.

### **Descriptions and Locations of Jumpers**

Figure 13 shows the locations of the jumpers on the P6467 probe. The jumper positions determine the operating mode and clocking of the probe. The probe defined as the Master Clock probe must have the jumpers in the correct positions to operate correctly; the jumper positions have no impact on probes not acquiring clock signals.

Figure 13: P6467 Clock Jumpers and Clock Threshold Adjustment Locations

A description of each clock jumper follows:

- J1 (MSTR CLK / EXT). This jumper connects either the Clock B Master clock or an external clock from another P6467 probe to the 92A96 probe cables connected to J200 (bottom two connectors) on the probe.

- J2, J3 (NORM/DIV2). These two jumpers determine the operating mode of the probe. Both jumpers *must* be in the same position. The NORM position connects the input Master clock directly to the output drivers. The DIV2 position divides the clock frequency by two before sending the clock signal to the output dividers.

- J4 (CLK A/MSTR CLK). This jumper selects the clock source for the 92A96 probe cables connected to J100 (top two connectors) on the probe.

Use the Clock Threshold Adjustment (THLD ADJ) to set the threshold for the clock inputs. Connect a digital voltmeter to test point THLD and ground and adjust the THLD ADJ control for the desired threshold voltage. Figure 13 shows the location of the THLD ADJ control and the THLD test point.

## Reference

This chapter contains information for using the P6467 support software with the High-Speed Probe Adapter with host computer applications. You will find the following information in this chapter:

- P6467 acquisition data commands

- P6467 reference memory commands

- LA-OffLine application examples

The P6467 support software consists of commands to transfer acquired data to a host and to create reference memories. This chapter does not include an exhaustive list of commands and information about using the acquired data with host computer applications. Nor does this chapter provide information on the structure of acquired data files. For information on the content and structure of acquisition data files, refer to the DAS 9200 Acquisition & Pattern Generation Files User Manual.

To use the commands in this chapter, you must use the EXEC? Programmatic Command Language (PCL) command with the logic analyzer using either the 92LANP application software or GPIB. For information on using the EXEC? command and other related commands, refer to the *DAS 9200 Programmatic Command Language User Manual*. You should also refer to that manual for a description of the PCL command syntax.

The commands in this chapter follow the PCL command syntax. Refer to the DAS 9200 Acquisition & Pattern Generation Files User Manual for details on the command syntax. Some of the more common syntax usage follow:

- Information enclosed by square brackets ([]) is optional.

- Information enclosed by angle brackets (<>) must be supplied by you.

- Arguments for the EXEC? query must be enclosed by single or double quotes.

The following example shows how to use the CARDATA command with the EXEC? query. All the commands described in this section should be used with the EXEC? query in a similar manner.

exec? "cardata 92C96-1 92C96-2"

## **P6467 Acquisition Data Commands**

The CARDATA command transfers acquired data or information about the data to a host. Several variations of the command are described in the following paragraphs.

# Send Acquired Data to the Host

To send acquired data to a host use the CARDATA command with the following syntax:

cardata <moduleA> <moduleB> [<first sequence>[<count>[<field>]]]

The <moduleA> and <moduleB> arguments define the pair of 92A96 Modules containing the acquired data. The <first sequence> argument specifies the first data sequence to return (the default sequence number is 0). The <count> argument is an integer that specifies the total number of data sequences to return (the default value is 0 for all sequences). Specifying a count of 0 returns all data starting with the <first sequence> and ending at the last data record. The <field> argument specifies the 92A96 data field to return (the default value is 0 for all fields). Table 4 lists the valid 92A96 fields.

Table 4: 92A96 Fields

| Field | Description               |

|-------|---------------------------|

| 0     | All fields                |

| 1     | Data fields               |

| 3     | Timestamps                |

| 15    | User specfic <sup>1</sup> |

For information using field 15, refer to the Tektronix Application Note number 57W-7194-1. Contact your local Tektronix representative for information on obtaining application notes.

Data records returned by the command are in the same format as the data records returned by the PCL ACQDATA? query.

The following example transfers 500 sequences of acquired data to the host and redirects the data into the file test1. The example uses the 92LANP pclconnect software that supports file redirection (refer to the 92LANP Instruction Manual for details on using the pclconect software).

exec? "cardata ModuleA ModuleB 00 500 0" > test1

# Reporting the Amount of Data to Return

Use the CARDATA command with the –r switch to report how much data can be returned.

cardata -r <moduleA> <moduleB>

The <moduleA> and <moduleB> arguments define the pair of 92A96 Modules containing the acquired data. The response to the query is a text string separated commas indicating the first sequence number, sequence count, and the trigger position.

#### Returning the Acquisition Header Information Only

Use the CARDATA command with the –h switch to return the acquisition data header that is a combination of the headers of both modules. When you use the –h switch, the command returns only the header information.

cardata -h <moduleA> <moduleB>

The <moduleA> and <moduleB> arguments define the pair of 92A96 Modules containing the acquired data. The channel name information is taken from <moduleA>. The acquisition memory depth is the total number of correlated sequences. The data format of the header is identical to the header returned by the PCL ACQHDR? query.

#### Returning the Acquisition Header and Data

By default the CARDATA command returns acquired data only. There may be times when you want to return both the header and data information. In this case you can use the CARDATA command with –hd switch.

cardata -hd <moduleA> <moduleB>

# Returning Data Without Timestamp Adjustments

The CARDATA command returns timestamp information. While executing the CARDATA command, there may be duplicate timestamp values. To keep the timestamp values unique, the CARDATA command adjusts the timestamp values by adding 3 ns to the first duplicate timestamp value, 5 ns to the second duplicate timestamp value, and 8 ns to the third duplicate timestamp value. The timestamp corrections are determined for each data record.

Use the optional –t switch with the CARDATA command if you do not want to adjust the timestamp values. If you use the –t switch, duplicate timestamp values can appear in the resultant output.

cardata -t <moduleA> <moduleB>

The –t switch can be helpful while debugging code for the system-under-test.

## **P6467 Reference Memory Commands**

The CARSTORE command is similar to the MSTORE PCL command. The command provides the additional ability to correlate the data as it is saved.

The CARSTORE command creates a reference memory that contains all of the data in a set of modules that are clustered and correlated. The cluster will include module1 through moduleN as members. Module pairs will be combined and stored as a single module data source. If the cluster contains other correlated data streams not listed on the command line, the data streams will be saved as standard data streams.

The CARSTORE command has the following syntax:

carstore [-t] <refmem name> <moduleA> <moduleB> [ -m <moduleA-n2> <moduleB-n2> [...]]

The optional –t switch turns off timestamp corrections. The –t switch works similar to the –t switch in the CARDATA command.

The <refmem name> argument specifies the name of the reference memory to be created. This reference memory will be placed in the Reference\_Mem directory on the hard disk of the logic analyzer. You can display the reference memory in the State or Timing display menus.

The <moduleA> and <moduleB> arguments specify a pair of 92A96 Modules. The data from these modules will be combined as the reference memory is saved.

The -m <moduleA-n2> <moduleB-n2> are additional 92A96 Module pairs that will be combined and saved as unique data streams. All modules must be clustered and correlated with <moduleA>. You can only use each module once.

You can also use the –t switch to turn off timestamp adjustments in the reference memory. However, you should avoid using the –t switch when you create a reference memory for more than one pair of 92A96 Modules. Doing so can cause inconsistent results when you display the data in the State menu.

## **LA-OffLine Applications**

If you have the LA-OffLine application installed on the host, you can also view the acquired data of a host file after executing the CARDATA command. Use the following steps to view acquired data with the LA-OffLine application.

- 1. Use the CARDATA command to transfer data from the logic analyzer to a host file. Use the –hd switch to create a file containing the header and data components of the acquired data.

- **2.** Remove the PCL command header and file-transfer format information from the file to return the file to its raw data form.

- **3.** Convert the raw data file to a LA-OffLine file using the CONVERT command available with the LA-OffLine application.

The following example shows how to transfer data from a logic analyzer using the 92LANP application software. All of commands shown in this example are available with the 92LANP and LA-OffLine application software packages.

1. Use the PCLSEND command to send the acquired data from the logic analyzer named Alpha to the host file test1.

```

pclsend Alpha "exec? 'cardata -hd moduleA moduleB'" > test1

```

**2.** Use the PCLSTRIP command to remove the PCL command header and file-transfer format information.

```

pclstrip test1

```

**3.** Convert the raw data file to a LA-OffLine file named acq.tst1.

```

convert test1 acq.tst1

```

**4.** Delete the raw data file.

rm test1

# **Specifications**

This chapter contains the complete specifications for the P6467 High-Speed Acquisition Probe. Within each section the specifications are arranged in the following functional groups: *Signal Acquisition System, Power Distribution System, Environmental, and Mechanical.*

All specifications are warranted unless they are designated *typical*. Warranted characteristics are checked by procedures in the *Performance Verification* chapter beginning on page 37; these characteristics are listed in **boldface** under the Characteristics column.

If the characteristic is noted as *typical*, the characteristic is not warranted. Typical characteristics describe typical or average performance and provide useful reference information.

**Table 5: Signal Acquisition System**

| Characteristic                                      | Description                             |

|-----------------------------------------------------|-----------------------------------------|

| Number of Input Channels                            | 24 Data, one Clock                      |

| Clock Input                                         |                                         |

| Maximum Clock Frequency                             | 195 MHz, DIV2 Mode<br>100 MHz NORM Mode |

| Maximum Differential Input<br>Voltage, typical      | 3.7 V <sub>P-P</sub>                    |

| Maximum Input Common<br>Mode Voltage Range, typical | -2.0 V to +3.0 V                        |

| Minimum Input Voltage<br>Swing                      | 800 mV <sub>P-P</sub>                   |

| Input Load, typical                                 | ≤ 6 pF Input Capacitance                |

| Clock Input Threshold<br>Adjustment Range           | -1.6 V to +2.6 V                        |

| Data Input                                          |                                         |

| Maximum Data Frequency                              | 97.5 MHz, DIV2 Mode<br>50 MHz NORM Mode |

| Input Voltage Levels                                |                                         |

| Vin High                                            | +2.0 V Minimum                          |

| Vin Low                                             | +0.8 V Maximum                          |

| Input Load, typical                                 | ≤8 pF Input Capacitance                 |

| · · · · · · · · · · · · · · · · · · ·               | <u> </u>                                |

Table 5: Signal Acquisition System (Cont.)

| Characteristic  | Description                                                       |

|-----------------|-------------------------------------------------------------------|

| Data Setup Time | 2 ns with coaxial probe cables<br>2.3 ns with ribbon probe cables |

| Data Hold Time  | 1.9 ns with coaxial probe cables 2.2 ns with ribbon probe cables  |

**Table 6: Power Distribution System**

| Characteristic           | Description                       |

|--------------------------|-----------------------------------|

| Power Consumption        | < 9 W                             |

| External DC Power Source |                                   |

| Connector Type           | Tektronix Part Number 131-5254-XX |

| Source Voltage           |                                   |

| Connector Pin 1          | −15 V to −20 V at < 0.4 A         |

| Connector Pin 2          | Ground                            |

| Connector Pin 3          | +4.75 V to + 5.25 V at < 0.5 A    |

**Table 7: Environmental**

| Characteristic             | Description                                                         |

|----------------------------|---------------------------------------------------------------------|

| Atmospherics               |                                                                     |

| Temperature                | Class 7 Limits except as noted                                      |

| Operating                  | +10° C to +50° C                                                    |

| Nonoperating               | -55° C to +75° C                                                    |

| Humidity                   | Class 7 Limits                                                      |

| Operating                  | +30° C to +40° C, 70% to 75% Relative Humidity                      |

| Nonoperating               | +30° C to +60° C, 90% to 95% Relative Humidity                      |

| Dynamics                   |                                                                     |

| Mechanical Shock           | Class 7 Limits                                                      |

| Operating and Nonoperating | Half sine, 100 g, 11 ms duration, three axis, three drops each axis |

**Table 8: Mechanical**

| Characteristic                    | Description                            |

|-----------------------------------|----------------------------------------|

| Weight                            |                                        |

| Standalone Probe                  | 0.25 kg (0.56 lbs)                     |

| Packaged for Domestic<br>Shipment | 1.47 kg (3.25 lbs)                     |

| Physical Dimensions               |                                        |

| Height                            | 43 mm (1.7 in)                         |

| Width                             | 88 mm (3.45 in)                        |

| Depth                             | 274 mm (10.8 in), includes flex cables |

| Cooling Method                    | Convection                             |

| Construction Material             | Aluminum Covers                        |

WARNING

The following servicing instructions are for use only by qualified personnel. To avoid injury, do not perform any servicing other than that stated in the operating instructions unless you are qualified to do so. Refer to all Safety Summaries before performing any service.

## **Performance Verification**

This chapter provides performance verification procedures for the P6467 High-Speed Acquisition Probe. It does not include verification procedures for the 92A96 or 92C96 Data Acquisition Modules. Refer to the system service manuals for the DAS or the TLA 500 series logic analyzer for performance verification procedures of the 92A96 and 92C96 Modules.

The functional check procedures are included in the *Getting Started* chapter beginning on page 12. Use the functional check to verify the basic operation of the P6467 Probe.

The following performance specifications are included in this chapter:

- Maximum Clock Frequency

- Minimum Input Voltage Swing

- Clock Input Threshold Adjustment Range

- Input Voltage Levels (Vin High and Vin Low)

- Data Setup and Hold Time

## **Equipment Required**

You will need the following test equipment to complete the performance verification checks in this chapter:

- A TLA 520 Logic Analyzer, DAS/NT, or DAS/XP Logic Analyzer with two 92A96 or 92C96 Data Acquisition Modules

- One or more P6467 High-Speed Probe Adapters with a Probe Power cable

- One Tektronix HFS 9003 Stimulus System with one HFS 9DG1 Data Generator and two HFS 9DG2 Data Generators

- Two sets of coaxial probe cables (Tektronix part number 198-5761-XX) or two sets of standard 92A96 probe cables

- One Digital Voltmeter, 3.5 digit with 0.1% accuracy

- One P6467 Test Fixture (Tektronix part number 067-0262-XX)

- Thirteen 20-inch long 3 mm coaxial cables (Tektronix part number 174-1427-XX)

- Oscilloscope with FET probes with bandwidth sufficient to measure relative time delays of approximately 5 ns

- 50  $\Omega$  Termination (Tektronix part number 011-0049-01)

- One 42-inch 50  $\Omega$  coaxial cable (Tektronix part number 012-0057-01)

#### **Performance Verification Procedure**

Before attempting any of the procedures in this section, allow a minimum of a 20 minutes to warm up all test equipment. These instructions assume that you perform the performance verification check while abiding by the environmental conditions as described in Table 7 on page 32.

The following procedures are designed to test one P6467 Probe at a time. Repeat the procedures for each additional probe.

#### **Test Equipment Setups**

The following steps describe the test equipment setups for the logic analyzer and for the HFS 9003 Stimulus System. These steps assume that your DAS or TLA logic analyzer already have the 92A96 Modules installed and that the Probe Cables are properly connected to the 92A96 Modules. These steps also assume that you have installed the P6467 Application Support software on the logic analyzer.

**Logic Analyzer Setups.** The following steps describe how to connect the probes to the logic analyzer and how to set up the logic analyzer menus for the performance verification checks.

**NOTE**. The following procedures assume that the 92A96 Modules are located in slots two and three of the logic analyzer. If your logic analyzer has the 92A96 Modules in different slots, you must adjust these procedures accordingly.

- **1.** Remove the cover from each P6467 Probe that you are testing and set the cover aside.

- 2. Connect the probe power cable from one of the 92A96 Modules in the logic analyzer to the power connector on the P6467 Probe (if necessary, refer to Figure 5 on page 7 for connection information). Leave the unused end of the probe power cable disconnected.

- **3.** Connect the blue-labeled coaxial probes from the logic analyzer to the OUTPUT DATA A Connector (top or J100) of the P6467 Probe.

- **4.** Power on the logic analyzer and wait for the Menu Selection overlay to display.

**NOTE**. The P6467 Application Support software includes a predefined setup that you can restore and use with the following setups. To use the predefined setups, select the Save/Restore menu and restore the setup file named P6467\_PVD. Otherwise continue with the following steps to manually set up the logic analyzer.

- 5. Select the **Sys Config** menu and perform the following steps:

- **a.** Select a Module formation with two individual 92A96 Modules.

- **b.** Change the module names to **module\_a** (module\_a should be the 92A96 module in the lowest numbered slot in the logic analyzer) and **module\_b**.

- **c.** Select **F6: DEFINE CLUSTER** and define a cluster named P6467 containing the two 92A96 Modules.

- **6.** Select the **Clus Setup** menu and perform the following steps:

- a. Select F4 DEFINE CORRELATN and correlate the two 92A96 Modules (select module\_a in the Correlate field, select F7: ADD COR, select module\_b in the new field, and save the changes).

- b. Select F2: DEFINE SIGNAL and select F7: ADD SIGNAL.

- **c.** Define a signal **AtoB** with the module\_a Direction field set to **Output** and the module\_b Direction field set to **Input**.

- **d.** Select **F7: ADD SIGNAL** and define a second signal **BtoA**.

- **e.** Set the module\_a Direction field to **Input** and the module\_b Direction field to **Output**.

- **f.** Save and close the overlay and verify that the Clus Setup menu displays the signal definitions.

- 7. Select the module\_A Config menu and set the Acquisition Memory field to 32768 cycles.

- **8.** Select the Channel menu and perform the following steps:

- **a.** Select F5: DEFINE THRESHOLD to call the Threshold Definition overlay.

- **b.** Change the Clock Threshold field to **VAR –1.85 V**.

- c. Change the Data Threshold field to **VAR** +1.95 **V**.