# **Service Manual**

# **Tektronix**

MPEG Test System Compaq Prosignia Platform 071-0152-01

#### Warnin

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

|                              | General Safety Summary                                        | ix   |

|------------------------------|---------------------------------------------------------------|------|

|                              | Service Safety Summary                                        | xi   |

|                              | Preface                                                       | xiii |

|                              | Introduction                                                  | XV   |

| Specifications               |                                                               |      |

| •                            | Specifications                                                | 1–1  |

|                              | Performance Conditions                                        | 1-1  |

|                              | Electrical Characteristics, Data Store System                 | 1-2  |

|                              | Electrical Characteristics, Real-Time Analyzer                | 1–13 |

|                              | Electrical Characteristics, Synchronous Serial Interface      | 1–16 |

|                              | Test System Power Specifications                              | 1–19 |

|                              | Mechanical (Physical) Characteristics                         | 1–19 |

|                              | Environmental Characteristics                                 | 1–19 |

| <b>Operating Information</b> | l                                                             |      |

|                              | Operating Information                                         | 2–1  |

|                              | Installation                                                  | 2-1  |

|                              | Connecting the Data Store System Input and Outputs            | 2–2  |

|                              | Connecting the Real-Time Analyzer (RTA) Input and Outputs     | 2-6  |

|                              | Connecting the Synchronous Serial Interface Input and Outputs | 2-8  |

|                              | First Time Operation                                          | 2–11 |

| Theory of Operation          |                                                               |      |

|                              | Theory of Operation                                           | 3–1  |

|                              | Data Store                                                    | 3–3  |

|                              | Real-Time Analysis                                            | 3–5  |

|                              | SSI Format Converter (MTS200 Ontion SS)                       | 3_6  |

# **Performance Verification**

|                      | Performance Verification, Data Store System 4–                |

|----------------------|---------------------------------------------------------------|

|                      | Verification Interval 4–                                      |

|                      | Incoming Inspection Test                                      |

|                      | Prerequisites                                                 |

|                      | Equipment Required                                            |

|                      | Definitions 4–                                                |

|                      | Test Record                                                   |

|                      | Procedure Structure 4–                                        |

|                      | Power On/Log In Procedure 4–                                  |

|                      | Loading Data Files                                            |

|                      | Internal Clock Test                                           |

|                      | G.703 I/O Port Tests                                          |

|                      | TTL 50 Ohm Port Tests                                         |

|                      | 10 Mbps (RS-422) Port Tests                                   |

|                      | ECL Parallel Port Tests                                       |

|                      | ECL Serial Port Tests                                         |

|                      | Performance Verification, Real-Time Analyzer 4-6              |

|                      | Equipment Required                                            |

|                      | Test Record                                                   |

|                      | Definitions 4–6                                               |

|                      | RTA Verification Procedures                                   |

|                      | Oscilloscope Setups                                           |

|                      | Loading the Test Files Onto the Reference System 4–9          |

|                      | Creating the Reference System Configuration Profile "test1"   |

|                      | Performance Verification, SSI System4-9'Equipment Required4-9 |

| Adimeter and Dua and |                                                               |

| Adjustment Procedu   | ares                                                          |

|                      | A director out Dropped areas                                  |

|                      | Adjustment Procedures                                         |

|                      | Equipment Required                                            |

|                      | 1 , ,                                                         |

|                      | Bit Rate Frequency (VCO) Adjustment                           |

|                      | 551 Output Signal Amphitude Adjustinent                       |

| Maintenance          |                                                               |

|                      | Maintenance                                                   |

|                      | Preparation 6–                                                |

|                      | Handling Static-Sensitive Components 6–                       |

|                      | Cleaning and Inspection                                       |

|                      | Removal and Replacement Instructions                          |

|                      | Server Diagnostics                                            |

|                      | Data Store System Troubleshooting                             |

|                      | Real-Time Analyzer Troubleshooting                            |

|                      | SSI Troubleshooting                                           |

|                      | Panaskaging 6.2                                               |

# **Options**

|                   | Options                                                                                                                                                                                                                                                                                                                                                                         | 7–1                                                                      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Replaceable Parts |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                          |

|                   | Replaceable Parts  Parts Ordering Information  Module Servicing  Using the Replaceable Parts List                                                                                                                                                                                                                                                                               | <b>8–1</b><br>8–1<br>8–2                                                 |

| Appendices        |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                          |

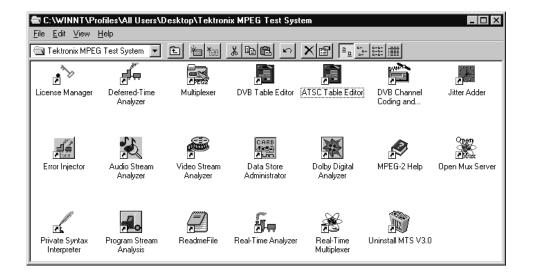

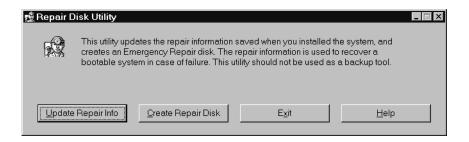

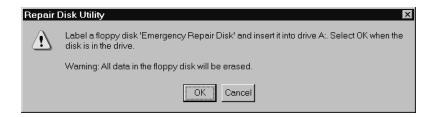

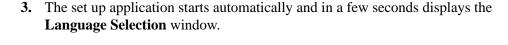

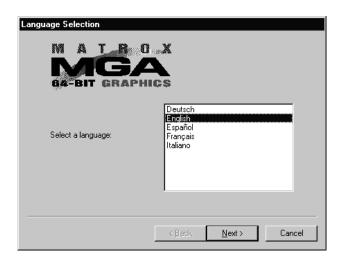

|                   | Appendix A: Software Repair  If an Application Locks Creating and Using an Emergency Repair Disk Installing the Software on a New System Disk Reinstalling the MPEG Test System Software Uninstalling Software Installing Software Entering the General License Password Installing SNMP Service Installing Windows NT 4.0 Service Pack 5 Upgrading Real-Time Analyzer Firmware | A-1<br>A-2<br>A-3<br>A-5<br>A-14<br>A-15<br>A-20<br>A-22<br>A-24<br>A-25 |

|                   | Appendix B: MPEG Test System Application Software                                                                                                                                                                                                                                                                                                                               | B-1                                                                      |

|                   | Software Version 2.0 Software Version 2.1 Software Version 2.2 Software Version 2.5 Software Version 3.0                                                                                                                                                                                                                                                                        | B-1<br>B-4<br>B-7<br>B-19                                                |

# **List of Figures**

| Figure 1–1: Pulse specification for a G.703 8.448 MHz pulse        | 1–3          |

|--------------------------------------------------------------------|--------------|

| Figure 1–2: Pulse specification for G.703 34.368 MHz               | 1–5          |

| Figure 1–3: Parallel data timing                                   | 1–7          |

| Figure 1–4: Parallel data timing, 204-byte packets                 | 1–8          |

| Figure 1–5: Timing diagram for the ECL serial port                 | 1–9          |

| Figure 1–6: ECL Timing diagram with control port                   | 1–10         |

| Figure 1–7: Timing for the TTL port and the separate               |              |

| clock input                                                        | 1–11         |

| Figure 1–8: Timing diagram for the 10 Mbit Serial port             | 1–12         |

| Figure 1–9: Parallel data timing, 188-byte packets                 | 1–14         |

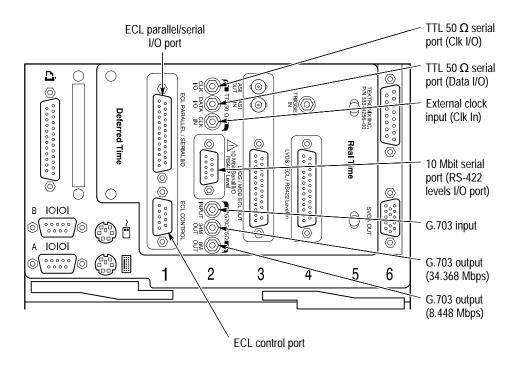

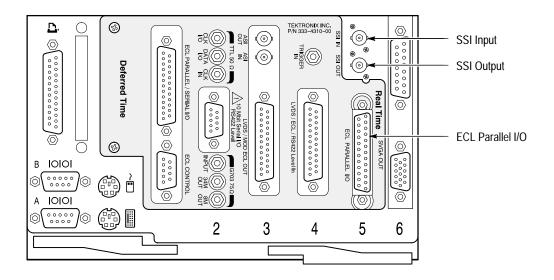

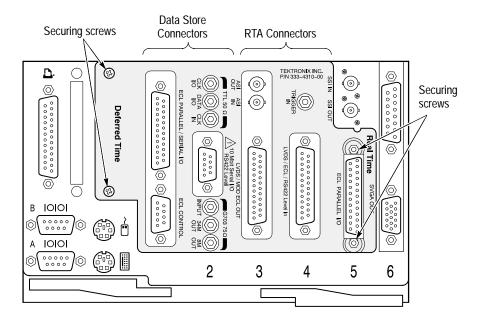

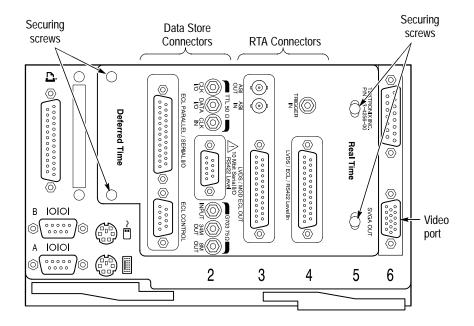

| Figure 2–1: Rear panel showing Data Store input and output ports   |              |

| (non-Option SS)                                                    | 2–2          |

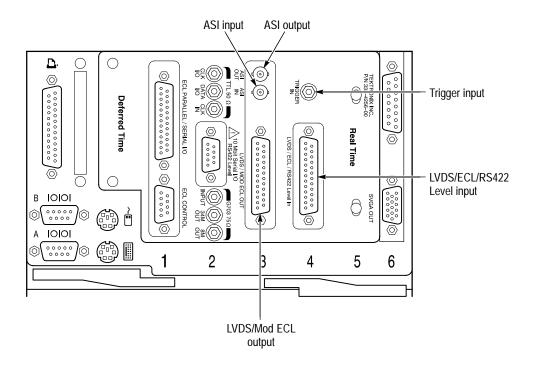

| Figure 2–2: Real-Time Analyzer input and output ports              | 2.6          |

| (computer rear)                                                    | 2–6          |

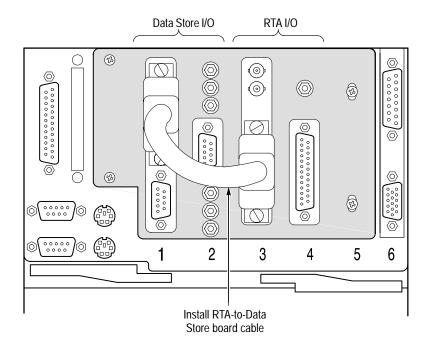

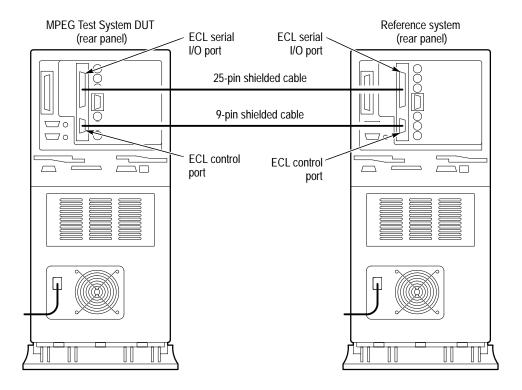

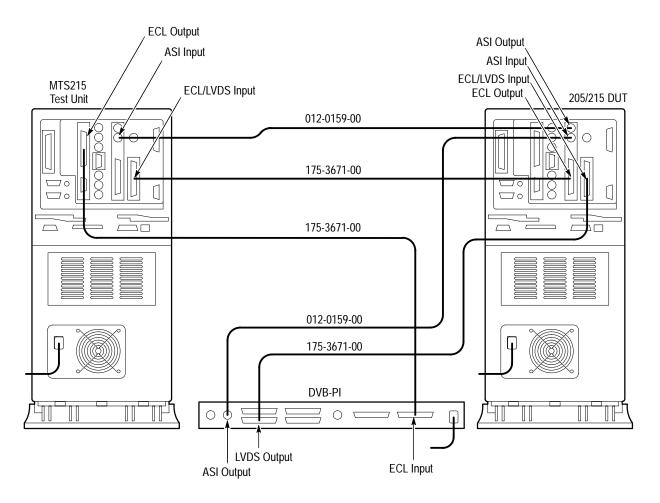

| Figure 2–3: RTA output to Data Store input connection              | 2–7          |

| Figure 2–4: SSI inputs and outputs, computer rear                  | 2–8          |

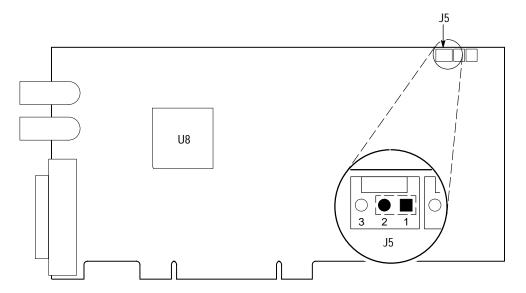

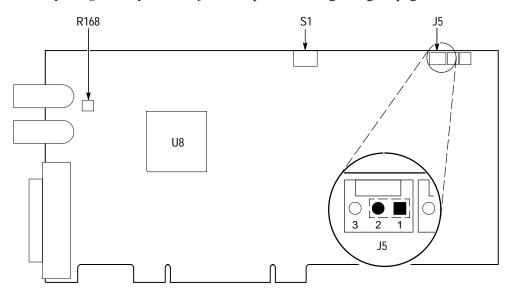

| Figure 2–5: SSI circuit board showing location J5                  | 2–10         |

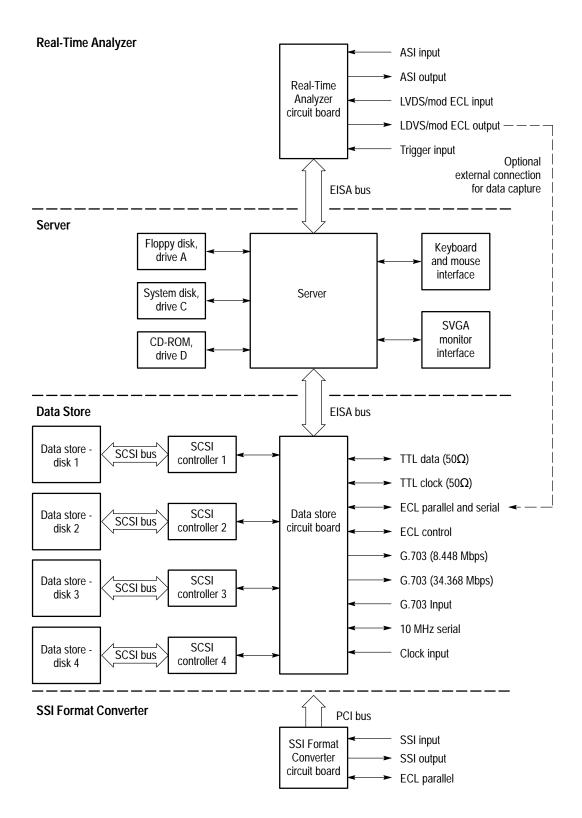

| Figure 3–1: Test System block diagram                              | 3–2          |

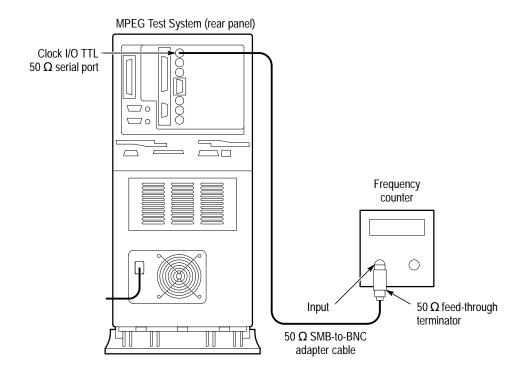

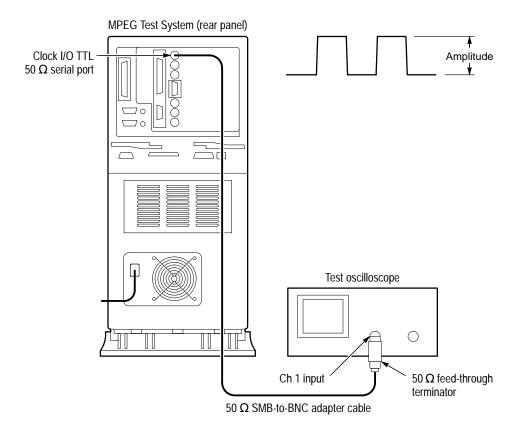

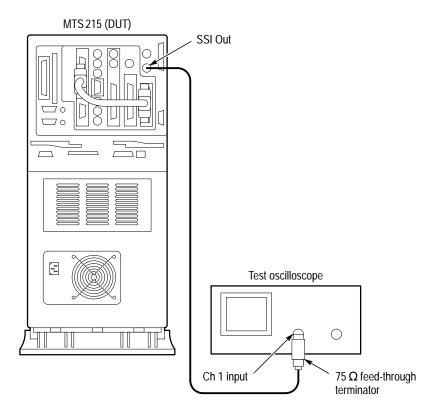

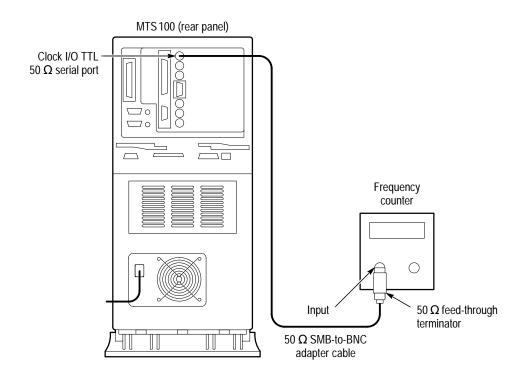

| Figure 4–1: Setup for measuring internal clock output accuracy     | 4–8          |

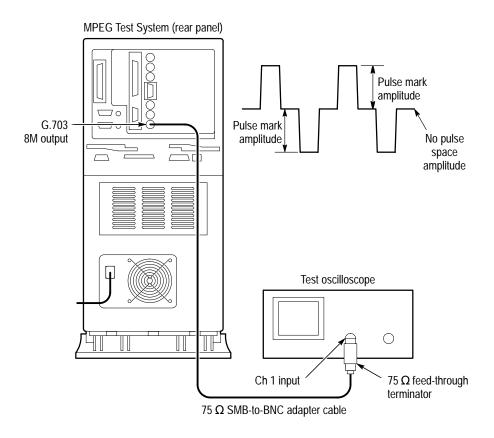

| Figure 4–2: Setup for measuring 8.448 Mbps signal parameters       | 4–10         |

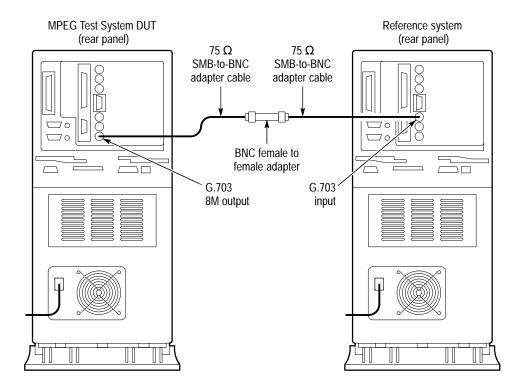

| Figure 4–3: Setup for testing G.703 8.448 Mbps slave               |              |

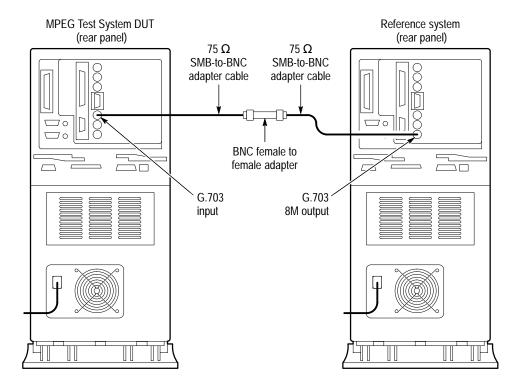

| acquisition                                                        | 4–12         |

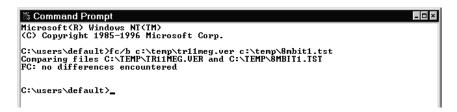

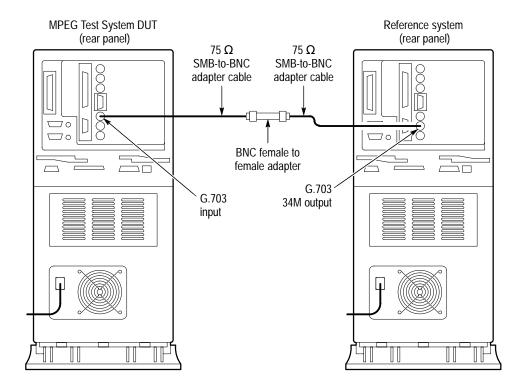

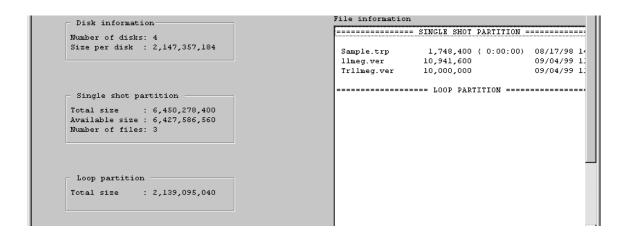

| Figure 4–4: Example file comparison results                        | 4–14         |

| Figure 4–5: Setup for testing G.703 8.448 Mbps master generation   | 4–14         |

| Figure 4–6: Example file comparison results                        | 4–16         |

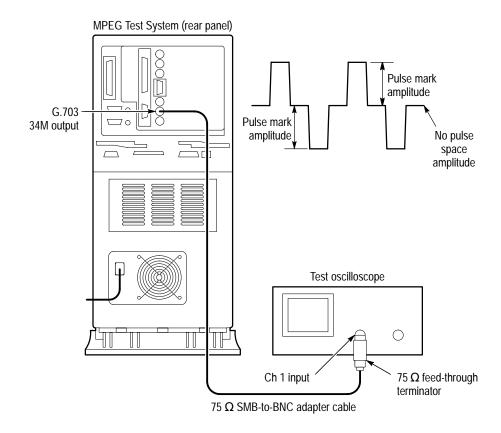

| Figure 4–7: Setup for measuring 34Mbps signal parameters           | 4–10<br>4–17 |

| Figure 4–8: Setup for testing G.703 34.368 Mbps slave              | <b>4</b> -17 |

| acquisition                                                        | 4–18         |

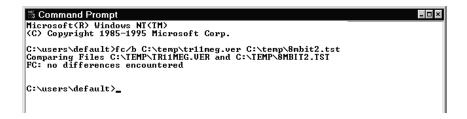

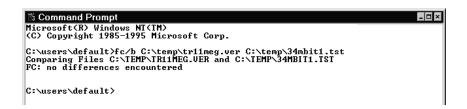

| Figure 4–9: Example results                                        | 4–20         |

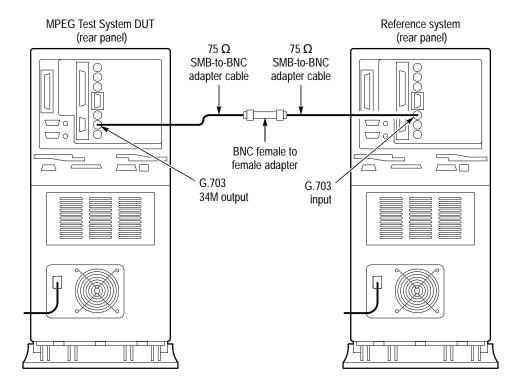

| Figure 4–10: Setup for testing G.703 34.368 Mbps master generation | 4–21         |

| Figure 4–11: Setup for measuring TTL 50 ohm clock pulse            |              |

| amplitude                                                          | 4_23         |

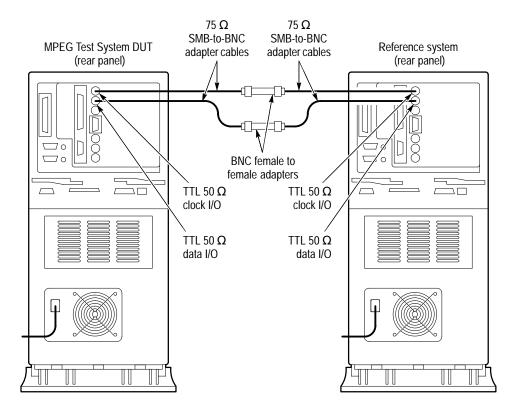

| Figure 4–12: TTL 50 ohm slave acquisition and master                                                         |       |

|--------------------------------------------------------------------------------------------------------------|-------|

| generation setup                                                                                             | 4–25  |

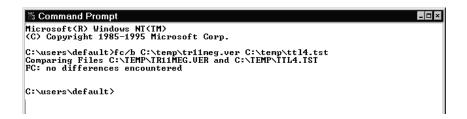

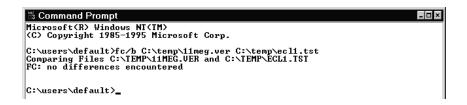

| Figure 4–13: Example Command Prompt comparison results                                                       | 4–31  |

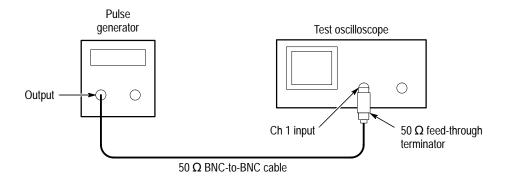

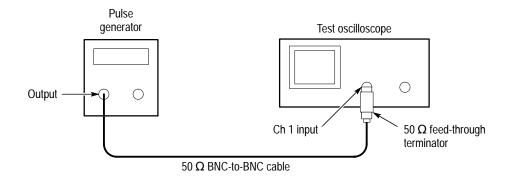

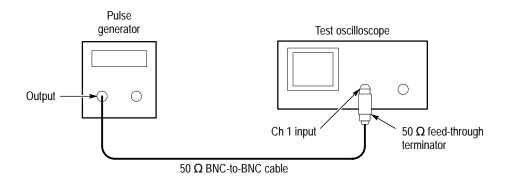

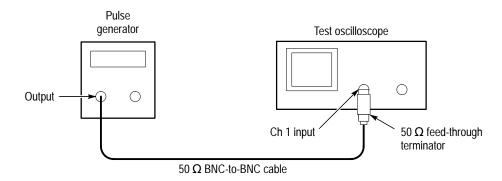

| Figure 4–14: Setup for measuring the pulse generator output                                                  | 4–32  |

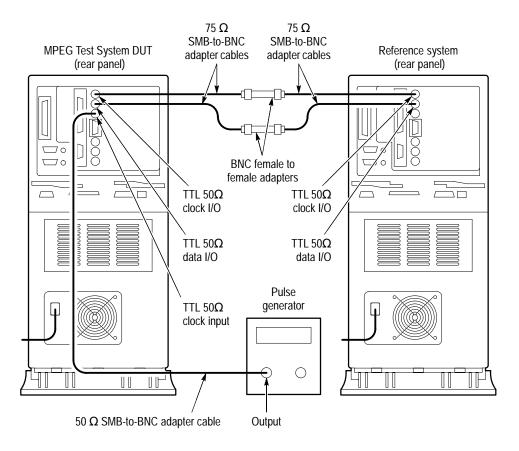

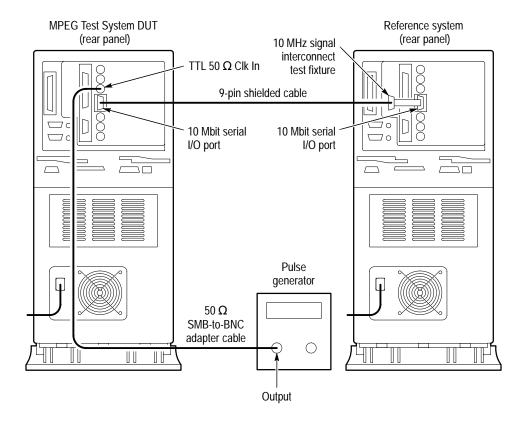

| Figure 4–15: Setup for checking 50 ohm external                                                              |       |

| clock generation                                                                                             | 4–32  |

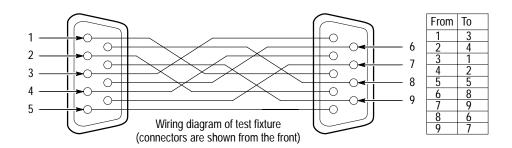

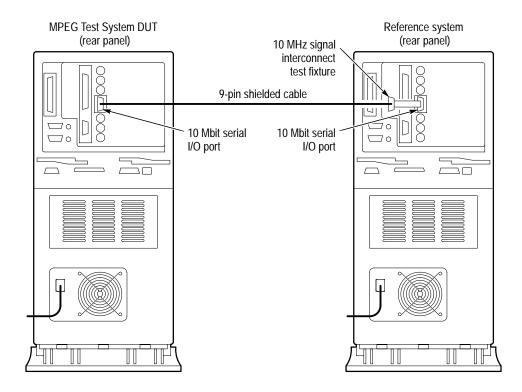

| Figure 4–16: 10 MHz signal interconnect fixture                                                              | 4–35  |

| Figure 4–17: Setup for checking 10 Mbit serial port high speed clock slave acquisition and master generation | 4–35  |

| Figure 4–18: Setup for measuring the pulse generator output                                                  | 4–42  |

| Figure 4–19: Setup for checking 10 Mbit external clock                                                       |       |

| generation                                                                                                   | 4–43  |

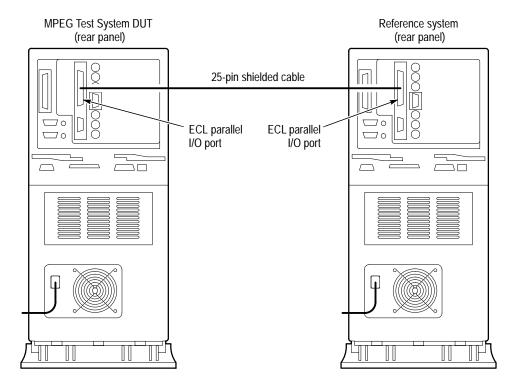

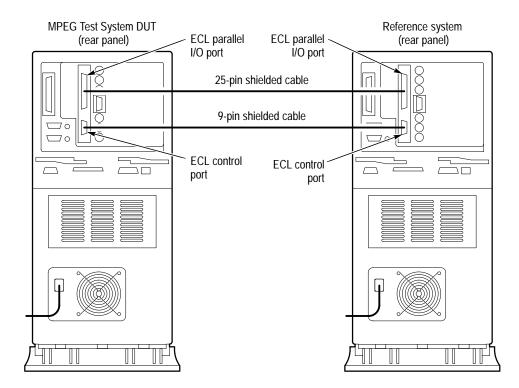

| Figure 4–20: Setup for checking ECL parallel port data transfer                                              | 4–45  |

| Figure 4–21: Example file comparison results                                                                 | 4–47  |

| Figure 4–22: Setup for measuring the pulse generator output                                                  | 4–49  |

| Figure 4–23: Setup for checking ECL parallel port generation with an                                         |       |

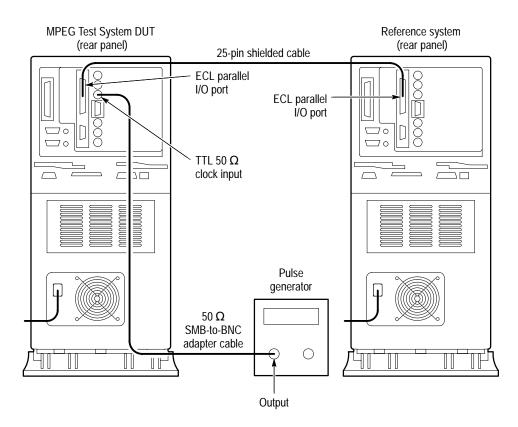

| external clock                                                                                               | 4–50  |

| Figure 4–24: Setup for checking ECL parallel port master acquisition                                         | 4–52  |

| and slave generation                                                                                         | 4-54  |

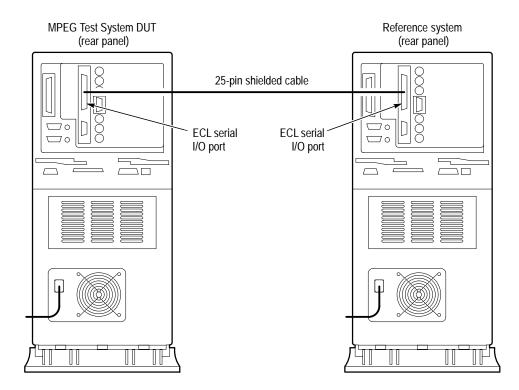

| Figure 4–25: Setup for checking ECL serial port slave acquisition and master generation                      | 4–56  |

| Figure 4–26: Example file comparison results                                                                 | 4–58  |

| Figure 4–27: Setup for measuring the pulse generator output                                                  | 4–60  |

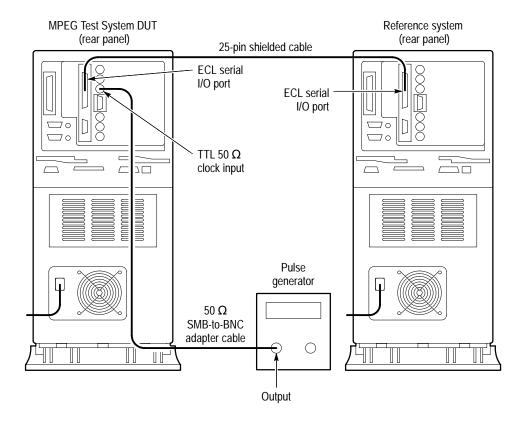

| Figure 4–28: Setup for checking ECL serial port generation with                                              |       |

| an external clock                                                                                            | 4–61  |

| Figure 4–29: Setup for checking ECL serial port slave generation                                             | 4–63  |

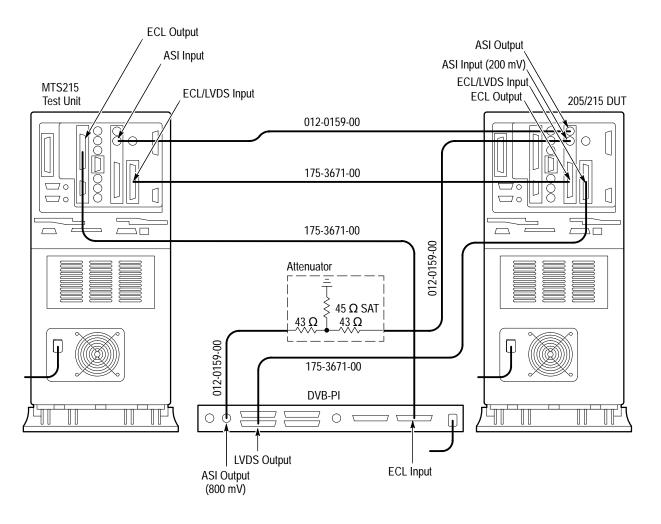

| Figure 4–30: Initial Real-Time Analyzer verification setup                                                   | 4–70  |

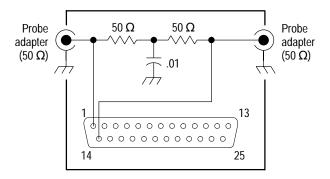

| Figure 4–31: Breakout box for LVDS port tests                                                                | 4–72  |

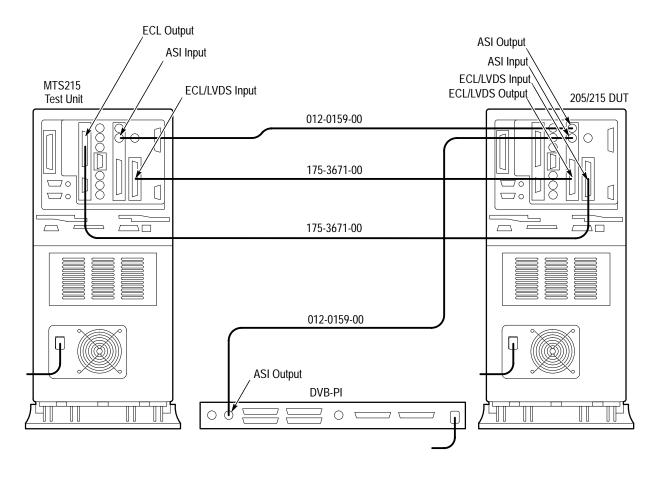

| Figure 4–32: Interconnections for verifying ASI Inputs                                                       | 4–82  |

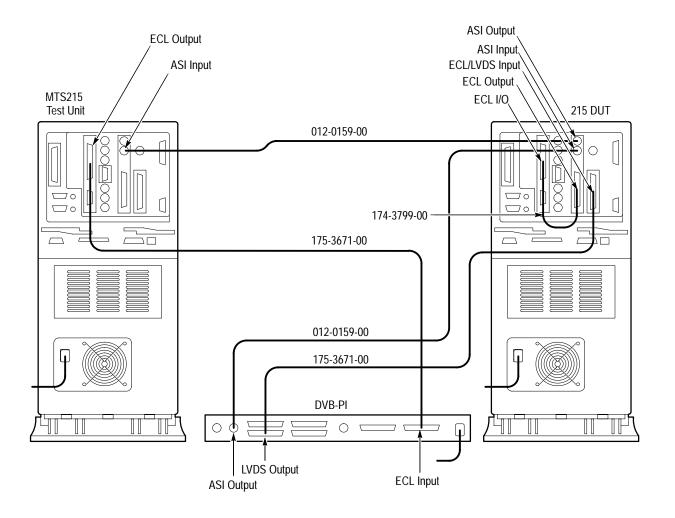

| Figure 4–33: Interconnections for verifying Modified ECL input                                               | 4–85  |

| Figure 4–34: Interconnections for verifying data capture                                                     | 4–87  |

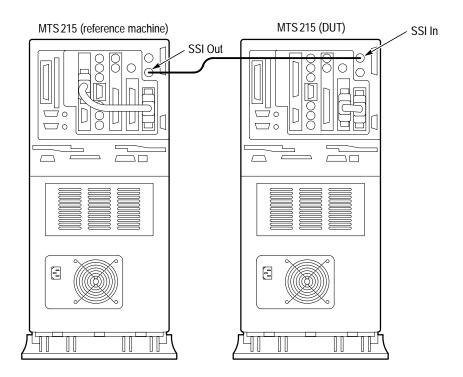

| Figure 4–35: Interconnections for testing an SSI board as an SSI generator                                   | 4–98  |

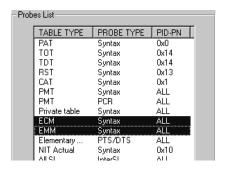

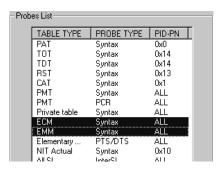

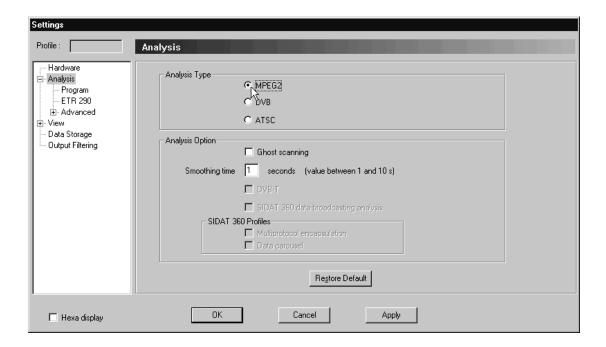

| Figure 4–36: Analysis panel of the Settings dialog box                                                       | 4–100 |

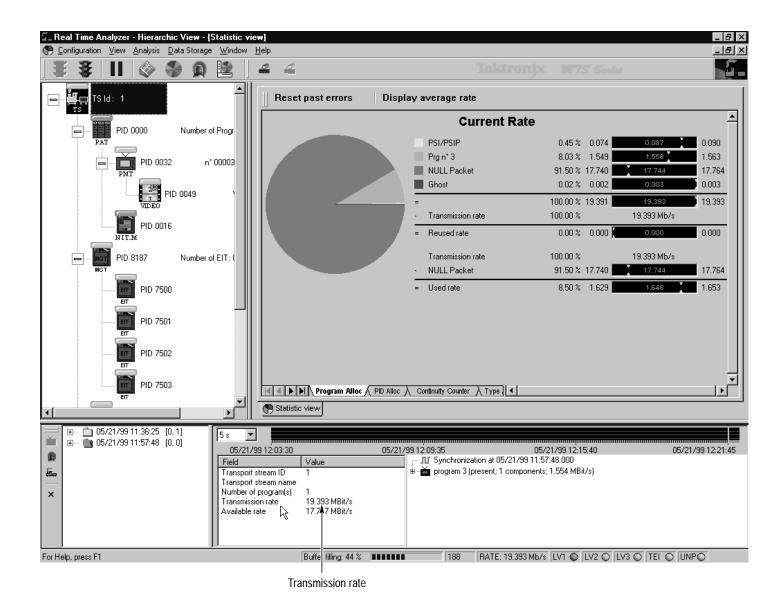

| Figure 4–37: Real-time analyzer showing the transmission rate                                                | 4–101 |

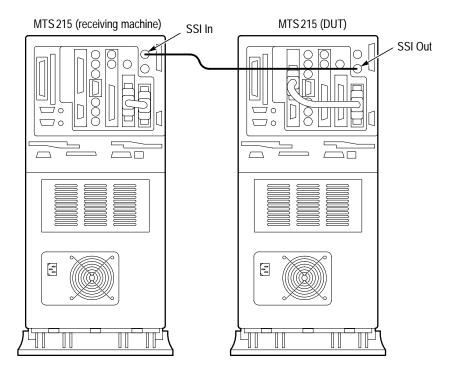

| Figure 4–38: Interconnections for testing an SSI board as an                                                 |       |

| SSI generator                                                                                                | 4–103 |

| Figure 4–39: Interconnections for measuring SSI output                                                       |       |

| signal amplitude                                                                                             | 4–106 |

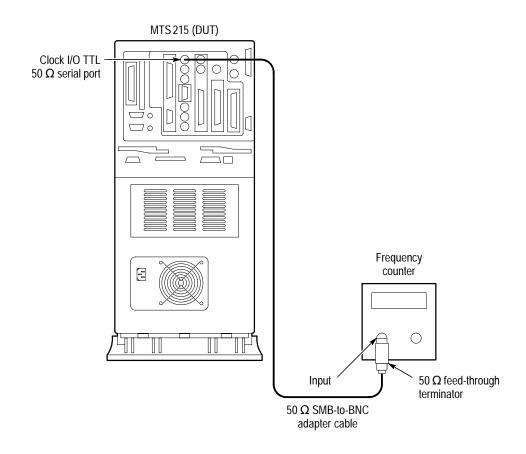

| Figure 4–40: Interconnection for measuring bit rate accuracy                                                 | 4-108 |

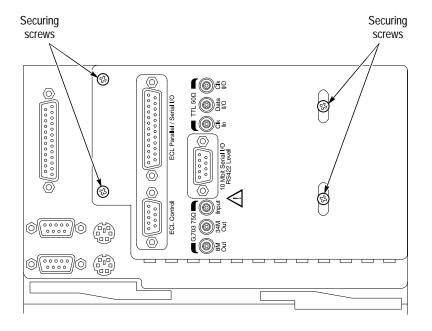

| Figure 5–1: Rear panel securing screws (MTS205 shown)                                                           | 5–3  |

|-----------------------------------------------------------------------------------------------------------------|------|

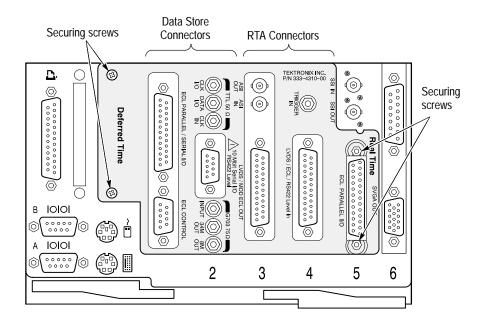

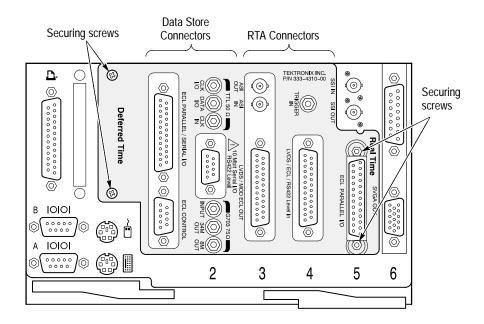

| Figure 5–2: MTS215 rear panel securing screws                                                                   | _    |

| (SSI option installed)                                                                                          | 5–4  |

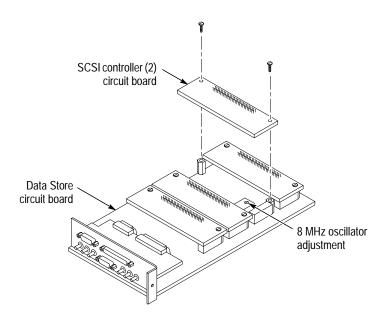

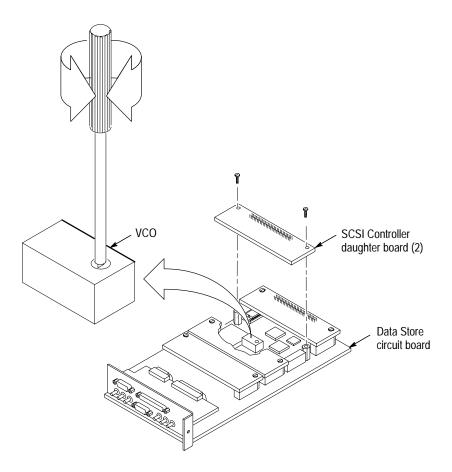

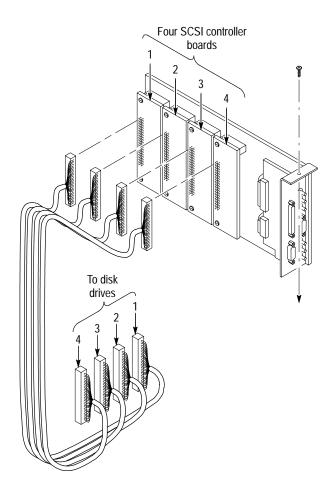

| Figure 5–3: Removing the Data Store circuit board                                                               | 5–5  |

| Figure 5–4: Location of the 8.448 MHz oscillator adjustment                                                     | 5–6  |

| Figure 5–5: The Service menu                                                                                    | 5–7  |

| Figure 5–6: Setup for adjusting the clock frequency                                                             | 5–8  |

| Figure 5–7: MTS215 rear panel securing screws (SSI option installed)                                            | 5–11 |

| Figure 5–8: Removing the Data Store circuit board                                                               | 5–12 |

| Figure 5–9: Location of VCO on the Data Store circuit board with SCSI Controller Daughter circuit board removed | 5–13 |

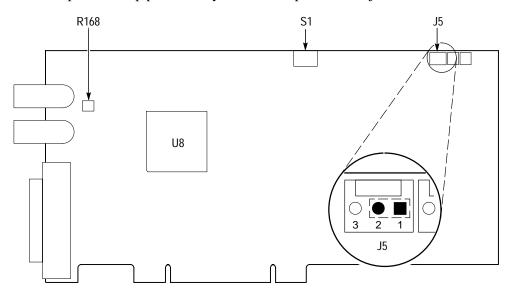

| Figure 5–10: SSI circuit board showing location of S1, J5, and                                                  |      |

| R168                                                                                                            | 5–16 |

| Figure 6–1: Top view of the server                                                                              | 6-5  |

| Figure 6–2: MPEG Test System rear panel securing screws                                                         | 6–7  |

| Figure 6–3: MPEG Test System rear panel securing screws                                                         |      |

| (SSI option installed)                                                                                          | 6–7  |

| Figure 6–4: Removing the Data Store circuit board                                                               | 6-9  |

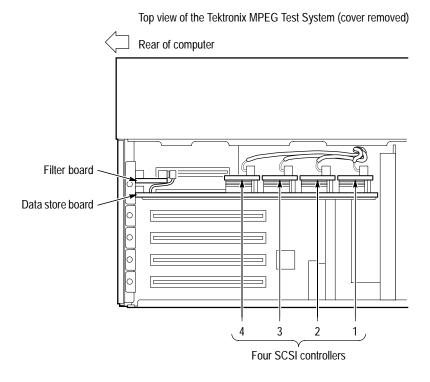

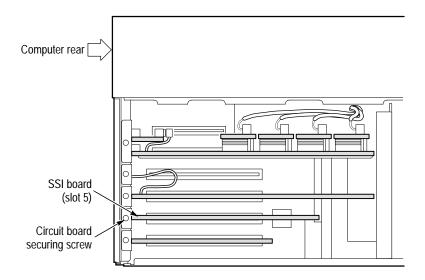

| Figure 6–5: Top view of the Proliant computer (MTS215 shown)                                                    |      |

| showing SSI board location                                                                                      | 6–12 |

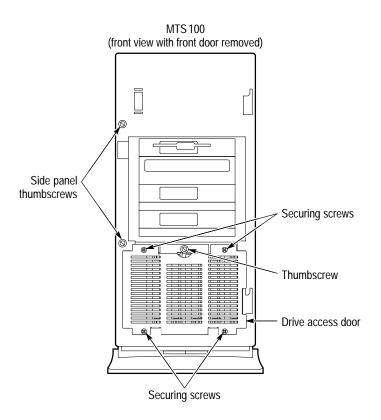

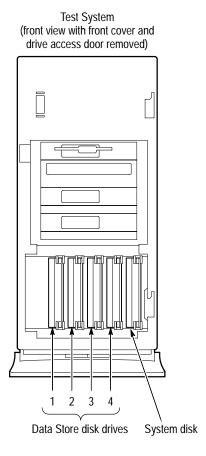

| Figure 6–6: Front of server shown disk drive access                                                             | 6–13 |

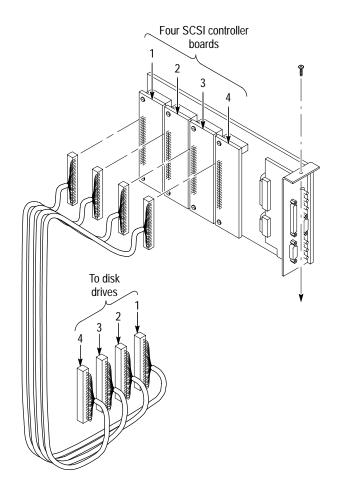

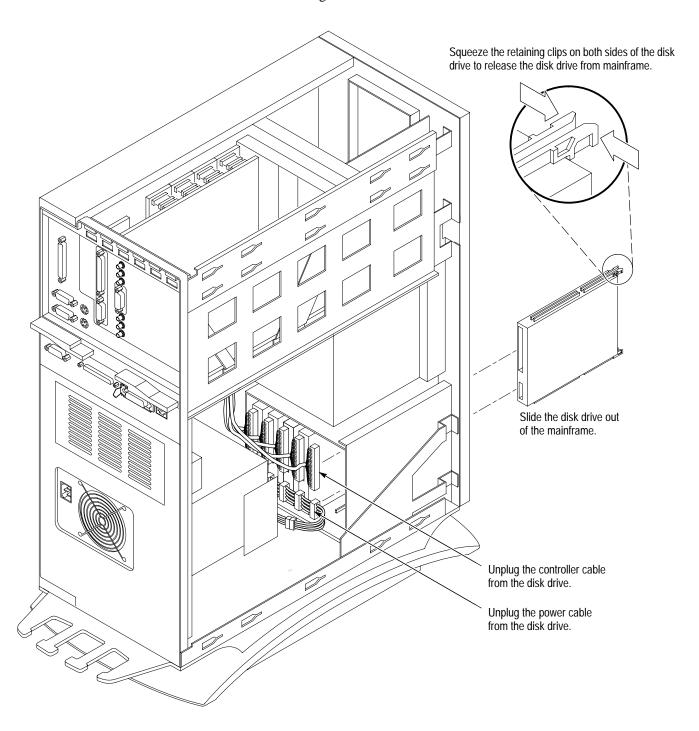

| Figure 6–7: Removing Data Store hard disk drives                                                                | 6–14 |

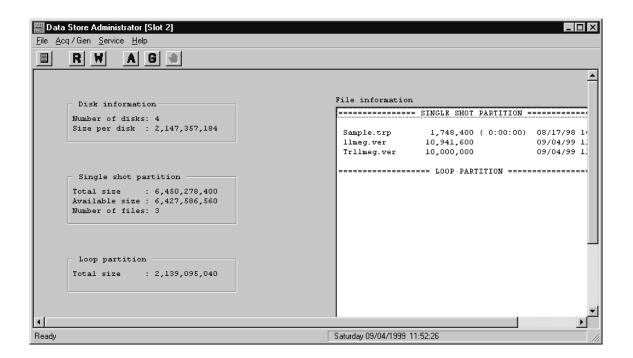

| Figure 6–8: The Data Store Administrator application window                                                     | 6–18 |

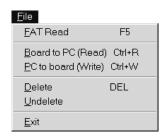

| Figure 6–9: The Data Store Administrator File menu                                                              | 6–19 |

| Figure 6–10: FAT Information                                                                                    | 6–19 |

| Figure 6–11: The Partitioning dialog box                                                                        | 6–20 |

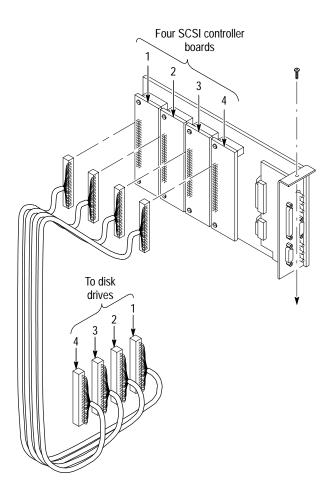

| Figure 6–12: Data Store disk drive order                                                                        | 6-21 |

| Figure 6–13: SSI circuit board showing the location of S1 and J5                                                | 6-23 |

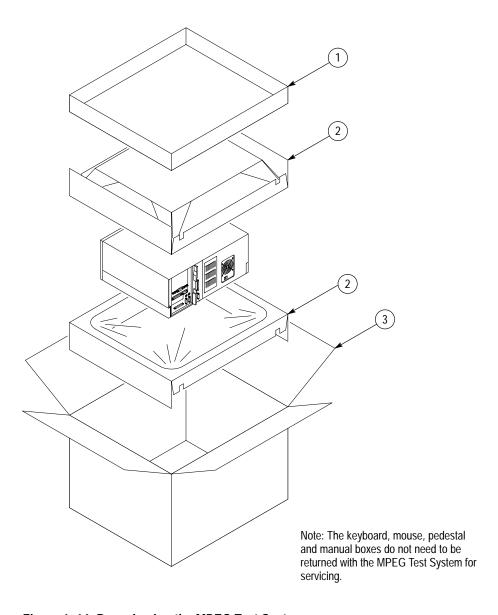

| Figure 6–14: Repackaging the MPEG Test System server                                                            | 6–25 |

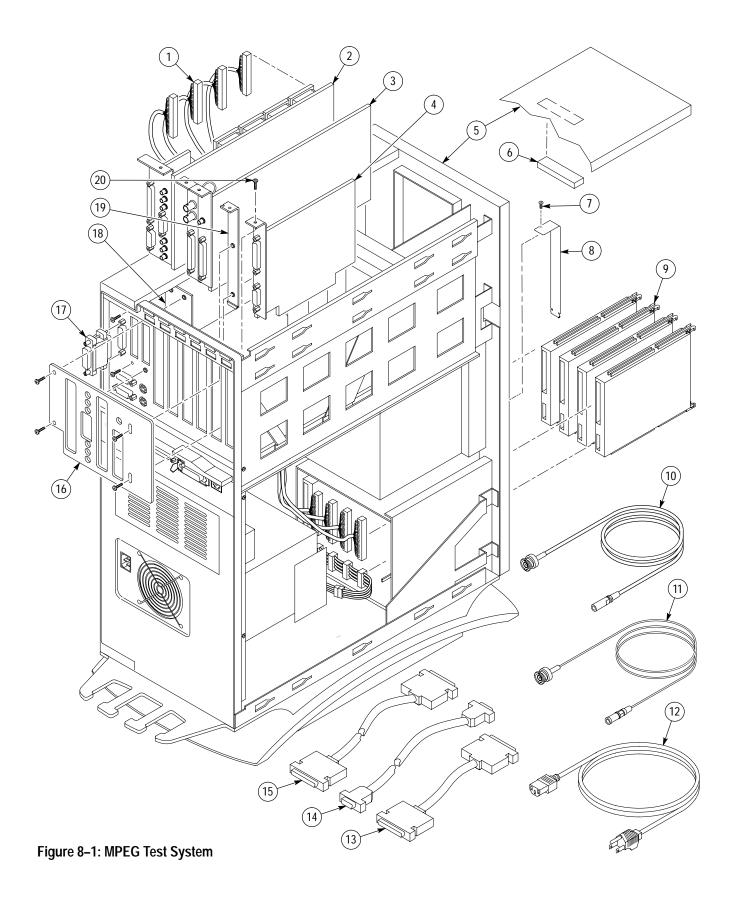

| Figure 8–1: MPEG Test System                                                                                    | 8–8  |

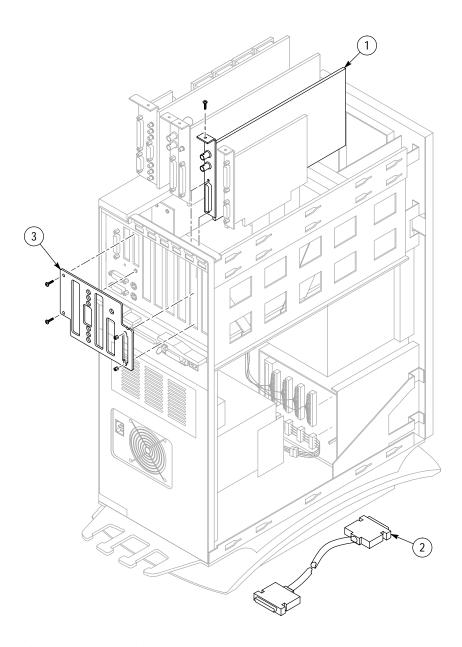

| Figure 8–2: Option SS                                                                                           | 8–9  |

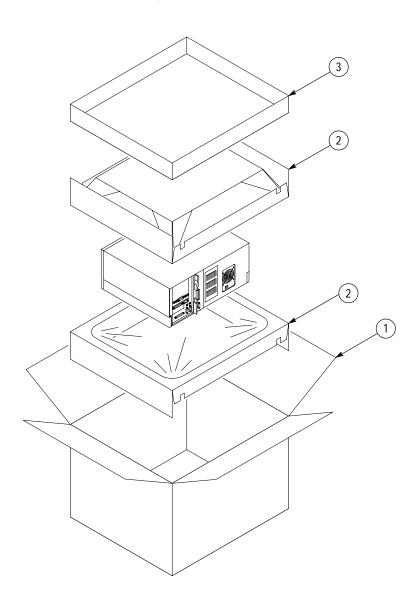

| Figure 8–3: Packing material                                                                                    | 8–10 |

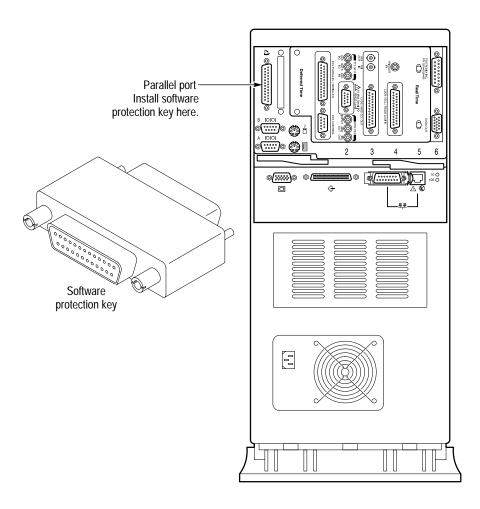

| Figure A-1: Rear Panel (MTS215 shown) showing parallel port and                                                 |      |

| software protection key                                                                                         | A-20 |

# **List of Tables**

| Table 1–1: G.703 — 8.448 MHz                            | 1–2  |

|---------------------------------------------------------|------|

| Table 1–2: G.703 — 34.368 MHz                           | 1–4  |

| Table 1–3: ECL parallel, serial, and control ports      | 1–6  |

| Table 1–4: ECL parallel data pinout                     | 1–7  |

| Table 1-5: ECL serial data pinout                       | 1–9  |

| Table 1–6: ECL control port pinout                      | 1–10 |

| Table 1–7: 50 Ohm TTL I/O                               | 1–11 |

| Table 1–8: TTL 50 Ohm Clock In port                     | 1–11 |

| Table 1–9: 10 Mbit serial port (RS-422 levels I/O Port) | 1–12 |

| Table 1–10: 10 Mbit serial port pinout                  | 1–12 |

| Table 1–11: PLL                                         | 1–13 |

| Table 1–12: Parallel input port                         | 1–13 |

| Table 1–13: Parallel output port                        | 1–13 |

| Table 1–14: LVDS/ECL/RS422 parallel data pinout         | 1–14 |

| Table 1–15: ASI input port                              | 1–15 |

| Table 1–16: ASI output port                             | 1–15 |

| Table 1–17: SSI input                                   | 1–16 |

| Table 1–18: SSI output                                  | 1–17 |

| Table 1–19: ECL Parallel I/O port                       | 1–17 |

| Table 1–20: SSI parallel I/O data pinout                | 1–18 |

| Table 1–21: Power requirements                          | 1–19 |

| Table 1–22: MPEG Test System mechanical characteristics | 1–19 |

| Table 1–23: Environmental characteristics               | 1–19 |

| Table 1–24: Safety certification compliance             | 1–20 |

| Table 1–25: Certifications and compliances              | 1–20 |

| Table 2–1: Estimated maximum cable lengths              | 2–5  |

| Table 4–1: Manuals containing the functional check      | 4–1  |

| Table 4–2: Required equipment                           | 4–2  |

| Table 4–3: The I/O port tests                           | 4–5  |

| Table 4–4: Internal clock accuracy limits               | 4_9  |

| Table 4–5: Required equipment list                      | 4–67 |

| Table 1 6. Dequired equipment list                      | 4 07 |

| Table 5–1: Required equipment list                        | 5–1  |

|-----------------------------------------------------------|------|

| Table 6–1: Static susceptibility                          | 6–1  |

| Table 6–2: Identifying defective data store disks         | 6-22 |

| Table 6–3: Correct RTA DIP switch configuration           | 6–23 |

| Table 6–4: Packaging Material                             | 6–24 |

| Table 7–1: Power cord options                             | 7–2  |

| Table A 1. Manuals for MTS200 Series version 2 v software | A 1/ |

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

#### **Injury Precautions**

**Use Proper Power Cord**. To avoid fire hazard, use only the power cord specified for this product.

**Avoid Electric Overload.** To avoid electric shock or fire hazard, do not apply a voltage to a terminal that is outside the range specified for that terminal.

**Avoid Overvoltage.** To avoid electric shock or fire hazard, do not apply potential to any terminal, including the common terminal, that varies from ground by more than the maximum rating for that terminal.

**Avoid Electric Shock**. To avoid injury or loss of life, do not connect or disconnect probes or test leads while they are connected to a voltage source.

**Ground the Product.** This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Do Not Operate Without Covers.** To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.

**Use Proper Fuse**. To avoid fire hazard, use only the fuse type and rating specified for this product.

**Do Not Operate in Wet/Damp Conditions.** To avoid electric shock, do not operate this product in wet or damp conditions.

**Do Not Operate in an Explosive Atmosphere**. To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.

### Product Damage Precautions

**Use Proper Power Source.** Do not operate this product from a power source that applies more than the voltage specified.

**Provide Proper Ventilation**. To prevent product overheating, provide proper ventilation.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

#### **Symbols and Terms**

**Terms in this Manual**. These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION**. Caution statements identify conditions or practices that could result in damage to this product or other property.

**Terms on the Product**. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

**Symbols on the Product**. The following symbols may appear on the product:

DANGER High Voltage

Protective Ground (Earth) Terminal

ATTENTION Refer to Manual

Double Insulated

# Certifications and Compliances

Refer to the specifications section for a listing of certifications and compliances that apply to this product.

# **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone.** Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

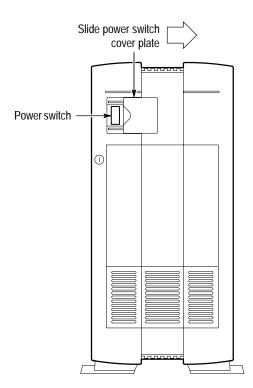

**Disconnect Power.** To avoid electric shock, disconnect the main power by means of the power cord or, if provided, the power switch.

**Use Care When Servicing With Power On.** Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

## **Preface**

This manual contains servicing information for the Tektronix MPEG Test System products, serial numbers B040000 and above, using the Compaq Proliant (2500 or 1600) platform. The information in this manual pertains to the Data Store, Synchronous Serial Interface, and Real-Time Analyzer hardware that enable the capture, generation, and analysis capabilities of the Tektronix MTS 205, MTS 210, and MTS 215 MPEG Test Systems.

User information in this manual applies to version 3.0 of the MPEG Test System hardware and software components and version 2.0 of the Real-Time Analyzer software. If your test system has earlier software, please contact your Tektronix representative for information about MPEG Test System upgrade options.

## **Related Documentation**

For complete information about the Tektronix MPEG Test System software applications and their use, refer to the user manual(s) that accompanied your system. If your system has been upgraded, refer to the documentation that accompanied the most recent upgrade.

For the latest information about Tektronix MPEG Test System features and bugs, refer to the *Read This First* document that accompanied your test system or most recent upgrade.

For information about the Windows NT Workstation operating system, refer to the Microsoft documentation that accompanied your test system.

For information about the Compaq Proliant server, refer to the Compaq documentation that accompanied your test system.

## **Manual Conventions**

The following terms and conventions are used throughout this manual:

- The term *test system* is used interchangeably with the more formal term Tektronix MPEG Test System.

- The term *server* refers to the Compaq Proliant computer that hosts the test system.

- Signal names that have overbars represent active low signals.

## **Contacting Tektronix**

Product For questions about using Tektronix measurement products, call

Support toll free in North America:

1-800-TEK-WIDE (1-800-835-9433 ext. 2400)

6:00 a.m. - 5:00 p.m. Pacific time

Or contact us by e-mail: tm\_app\_supp@tek.com

For product support outside of North America, contact your

local Tektronix distributor or sales office.

Service Tektronix offers extended warranty and calibration programs as

Support options on many products. Contact your local Tektronix

distributor or sales office.

For a listing of worldwide service centers, visit our web site.

For other In North America:

information 1-800-TEK-WIDE (1-800-835-9433)

An operator will direct your call.

To write us Tektronix, Inc.

P.O. Box 1000

Wilsonville, OR 97070-1000

**USA**

Website Tektronix.com

## Introduction

This short introduction emphasizes a few safety precautions that you need to keep in mind when servicing the MTS200 Series MPEG Test System, describes a service strategy for repairing the test system, and lists Tektronix service options available for this product.

## **Before You Begin**

To prevent injury to yourself or damage to the test system, fulfill the following requirements before you service your test system:

- Be sure you are a qualified service person.

- Read the Safety Summary found at the beginning of this manual.

- Read *Service Strategy*, below.

Be sure to heed all warnings, cautions, and notes in this manual when servicing your test system.

## **Service Strategy**

This manual contains the following service procedures:

- Performance verification procedures

- Adjustment procedures for the Data Store and synchronous serial interface boards

- Periodic maintenance

- Module removal and replacement

- Module-level fault diagnosis

Use the module-level fault diagnosis section (in the *Maintenance* section) to isolate problems to a specific module. Once you isolate a problem with a module, use the *Replaceable Parts List* in this manual to determine the correct module part number to order from Tektronix. Use the remove and replacement procedures to remove and replace defective modules. Use the performance verification and adjustment procedures to verify the accuracy of your test system after installing a new module (or for periodic maintenance).

## **Tektronix Service Offerings**

Tektronix provides service to cover repair under warranty. Other services are available that may provide a cost-effective alternative to servicing your instrument.

Whether providing warranty repair service or any of the other services listed below, Tektronix service technicians, trained on Tektronix products, are best equipped to service your MTS 200 Series MPEG Test System. Tektronix technicians are informed of the latest improvements to the product as well as the latest product options.

#### **Warranty Repair Service**

Tektronix warrants this product for one year from the date of purchase. Tektronix technicians provide warranty service at most Tektronix service locations worldwide. Your Tektronix product catalog lists all service locations; if necessary, contact your nearest Tektronix representative for more information or assistance.

#### Repair Service

Tektronix offers single per-incident and annual maintenance agreements that provide Depot Service repair of this test system.

Of these services, the annual maintenance agreement offers a particularly cost-effective approach to service for many MTS 200 Series MPEG Test System owners.

#### Self Service

Tektronix supports self service repair to the module level by offering a Module Exchange program. The Module Exchange service can reduce down time for repair by allowing you to exchange most modules for remanufactured ones. Tektronix ships you an updated and tested exchange module from the Beaverton, Oregon service center. Each module comes with a 90-day service warranty.

## For More Information

Please contact your local Tektronix service center or sales engineer for more information on any of the repair or adjustment services previously described.

# **Specifications**

# **Specifications**

The tables in this section list the electrical, physical, and environmental characteristics of the Tektronix MPEG Test System. Refer to the following definitions for an explanation of each specification table column heading.

#### Characteristics

Characteristics are properties of the product. Characteristics identified with a check mark  $(\slashed{\prime})$  are considered to be binding on the company (seller), and can be verified by performing the appropriate portions of the Performance Verification procedure or by a separate and available procedure.

#### **Descriptions**

Descriptions are statements that define the characteristic, often in limit form.

#### **Supplemental Information**

Supplemental information explains or adds to the information in the performance requirement column; it may include typical performance characteristics for the instrument. Statements in this column are not considered to be guaranteed performance and are not ordinarily supported by a Performance Verification procedure.

## **Performance Conditions**

The specifications are valid for test systems under the following conditions:

- The test system is operating within the environmental limits listed in Table 1–23 on page 1–19.

- The test system has been adjusted at  $25^{\circ}$  C  $\pm 5^{\circ}$  C.

- The test system has been operating a minimum of 20 minutes and has therefore reached normal operating temperature.

# **Electrical Characteristics, Data Store System**

The following tables pertain to the Tektronix MPEG Test System Data Store I/O ports.

Table 1-1: G.703 — 8.448 MHz

| Characteristic                | Description             | Supplemental information                                                          |

|-------------------------------|-------------------------|-----------------------------------------------------------------------------------|

| Standards Conformance         |                         | ITU-CCITT G.703, G.823                                                            |

| Line Encoding                 |                         | HDB3                                                                              |

| ✓ Serial Bit Rate             | 8.448 Mbytes/s ± 10 ppm |                                                                                   |

| Generation/Acquisition Test   | Error free              | Tested with a 10 Mbyte file (within the constraints of synchronization)           |

| Input                         |                         |                                                                                   |

| Voltage Levels                |                         | Standard level within 0 to 4 dB cable attenuation at 1/2 clock                    |

|                               |                         | Standard Levels:<br>Mark from 2.033 V to 2.607 V<br>Space from -0.237 to +0.237 V |

| Return Loss (75 $\Omega$ )    |                         | 12 dB, 211 kHz to 422 kHz                                                         |

|                               |                         | 18 dB, 422 kHz to 8.448 MHz                                                       |

|                               |                         | 14 dB, 8.448 to 12.672 MHz                                                        |

| Connector                     | SMB                     | Male (shared with the 34.36 Mbit input)                                           |

| Jitter Tolerance              |                         | 177 ns peak-to-peak 20 Hz to 400 Hz                                               |

|                               |                         | 23.6 ns peak-to-peak 3 kHz to 400 kHz                                             |

|                               |                         | Log prorated – 400 Hz to 3 kHz                                                    |

| Output                        |                         |                                                                                   |

| Pulse Width                   |                         | 59 ns, nominal                                                                    |

| ✓ Pulse "Mark" Amplitude      | 2.37 V ± 0.237 V        |                                                                                   |

| ✓ No-Pulse "Space" Voltage    | 0 ± 0.237 V             |                                                                                   |

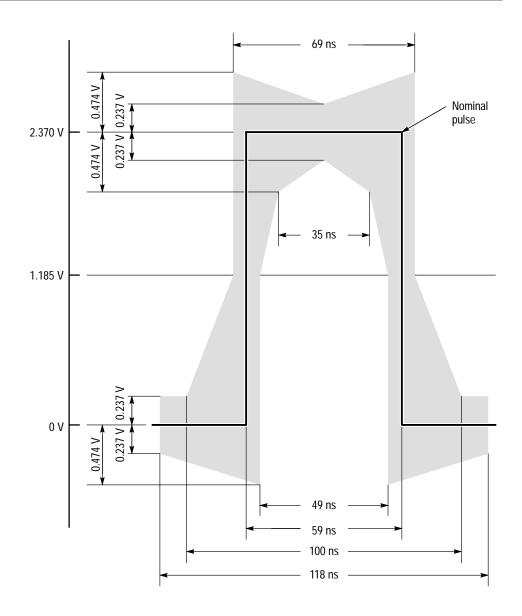

| Pulse Shape                   |                         | Conforms to 8.448 MHz Pulse Mask, G.703 Figure 16 (see Figure 1–1)                |

| Required Receiver Termination | Resistive, 75 Ω nominal |                                                                                   |

| Jitter                        |                         | 15 ns peak-to-peak with a 20 Hz lower cut-off and a 400 kHz upper cut-off filter  |

|                               |                         | 5 ns peak-to-peak with a 3 kHz lower cut-off and a 400 kHz upper cut-off filter   |

|                               |                         | Allows a cascade of ten different regenerators before system limit is reached     |

Table 1-1: G.703 — 8.448 MHz (cont.)

| Characteristic | Description | Supplemental information     |

|----------------|-------------|------------------------------|

| Connector      | SMB         | Male                         |

| Return Loss    |             | 12 dB – 211 kHz to 422 kHz   |

|                |             | 18 dB – 422 kHz to 8.448 MHz |

|                |             | 14 dB – 8.448 to 12.672 MHz  |

Figure 1–1: Pulse specification for a G.703 8.448 MHz pulse

Table 1-2: G.703 — 34.368 MHz

| Characteristic                | Description          | Supplemental information                                                            |

|-------------------------------|----------------------|-------------------------------------------------------------------------------------|

| Standards Conformance         |                      | ITU-CCITT G.703, G.823                                                              |

| Connector                     | SMB                  | Male                                                                                |

| Line Encoding                 |                      | HDB3                                                                                |

| ✓ Generation/Acquisition Test | Error free           | Tested with a 10 Mbyte file (within the constraints of synchronization)             |

| ✓ Serial Bit Rate             | 34.368 Mbps ± 20 ppm |                                                                                     |

| Input                         |                      |                                                                                     |

| Voltage Levels                |                      | Standard level within 0 to 4 dB cable attenuation at 1/2 clock                      |

|                               |                      | Standard level:<br>Mark from 0.9 V to 1.1 V<br>Space from -0.1 V to +0.1 V          |

| Return Loss (75 $\Omega$ )    |                      | 12 dB 860 kHz to 1.72 MHz                                                           |

|                               |                      | 18 dB 1.72 MHz to 34.368 MHz                                                        |

|                               |                      | 14 dB 34.368 to 51.55 MHz                                                           |

| Connector                     | SMB                  | Male (shared with the 8 Mbit input)                                                 |

| Jitter Tolerance              |                      | 43.7 ns peak-to-peak – 100 Hz to 1 kHz                                              |

|                               |                      | 4.37 ns peak-to-peak – 10 kHz to 800 kHz                                            |

|                               |                      | Log prorated – 1 kHz to 10 kHz                                                      |

| Output                        |                      |                                                                                     |

| Pulse Width                   |                      | 14.5 ns nominal                                                                     |

| ✓ Pulse Mark Amplitude        | 1.0 V ± 0.1 V        |                                                                                     |

| ✓ No-Pulse Space Voltage      | 0 ± 0.1 V            |                                                                                     |

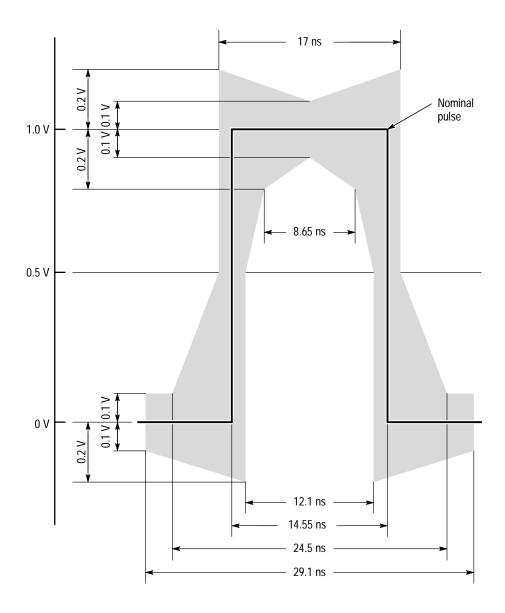

| Pulse Shape                   |                      | Conforms to 34.368 MHz Pulse Mask, Figure 17/G.703 (see Figure 1–2)                 |

| Required Receiver Termination |                      | 75 Ω nominal resistive                                                              |

| Jitter                        |                      | 10 ns peak-to-peak with a 100 Hz lower cut-off and a 800 kHz upper cut-off filter   |

|                               |                      | 2.45 ns peak-to-peak with a 10 kHz lower cut-off and a 800 kHz upper cut-off filter |

|                               |                      | Allows a cascade of ten different regenerators before system limit is reached       |

| Return Loss                   |                      | 12 dB – 860 kHz to 1.72 MHz                                                         |

|                               |                      | 18 dB – 1.72 MHz to 34.368 MHz                                                      |

|                               |                      | 14 dB – 34.368 MHz to 51.55 MHz                                                     |

Figure 1–2: Pulse specification for G.703 34.368 MHz

Table 1–3: ECL parallel, serial, and control ports

| Characteristic                           | Description    | Supplemental information                             |  |

|------------------------------------------|----------------|------------------------------------------------------|--|

| Connector                                |                |                                                      |  |

| Parallel Data                            | D25            | Female (pinout described in Table 1–4)               |  |

| Serial Data                              | D25            | Female (pinout described in Table 1–5)               |  |

| Flow Control                             | D9             | Female (pinout described in Table 1–6)               |  |

| Generation/Acquisition Test              | All error free | Tested with a 10 Mbyte file at maximum data rates    |  |

| Master/Slave<br>Slave/Master (w/control) |                | (within the constraints of synchronization)          |  |

| Digital Format                           |                | Binary, positive logic                               |  |

| Input                                    |                |                                                      |  |

| Maximum Data Rate                        |                | Serial: 55 Mbps                                      |  |

|                                          |                | Parallel: 60 Mbps (7.5 Mbytes/s)                     |  |

| Minimum Data Rate                        |                | Clock Rate: 1 MHz                                    |  |

|                                          |                | Serial: 1 Mbps<br>Parallel: 1 Mbps (125 Kbytes/s)    |  |

| Signal Level Amplitude                   |                | Differential ECL, Compliant with the ECL 100K levels |  |

| Time Reference                           |                | Rising edge of the clock                             |  |

| Output                                   |                |                                                      |  |

| Maximum Data Rate                        |                | Serial: 55 Mbps<br>Parallel: 60 Mbps (7.5 Mbytes/s)  |  |

| Minimum Data Rate                        |                | Clock rate: 1 MHz                                    |  |

|                                          |                | Serial: 1 Mbps<br>Parallel: 1 Mbps (125 Kbytes/s)    |  |

| Clock to Data Timing                     |                | Data changes within 5 ns of falling clock edge       |  |

| Signal Level Amplitude                   |                | Differential ECL,Compliant with the ECL 100K levels  |  |

| Required Receiver Termination            |                | 110 $\Omega$ , line-to-line                          |  |

Pin **ECL** parallel port Pin **Function Function** DCLK **DCLK** 1 14 2 15 Ground Ground 3 DATA 7 16 DATA 7 15 3 4 DATA 6 17 DATA 6 16 17 DATA 5 18 DATA 5 5 18 DATA 4 19 DATA 4 6 6 19 DATA 3 20 DATA 3 20 8 21 DATA 2 8 DATA 2 21 22 9 DATA 1 DATA 1 22 10 23 DATA 0 23 DATA 0 10 11 24 11 **DVALID** 24 **DVALID** 12 25 **PSYNC** 13 12 25 **PSYNC** 13 Shield

Table 1-4: ECL parallel data pinout

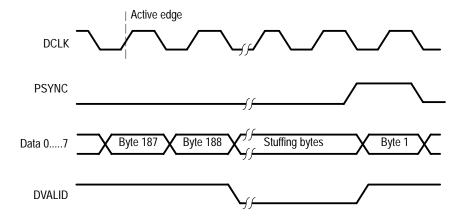

Figure 1-3: Parallel data timing

Figure 1-4: Parallel data timing, 204-byte packets

**ECL** serial port Pin **Function** DCLK 1 2 Ground 3 - 9 Not Managed 15 10 DATA 0 16 17 11 **DVALID** 5 PSYNC 12 6 19 13 Shield 7 8 DCLK 14 21 15 Ground 22 10 23 16 – 22 Not Managed 11 24 23 DATA 0 12 25 24 DVALID 13 **PSYNC** 25

Table 1–5: ECL serial data pinout

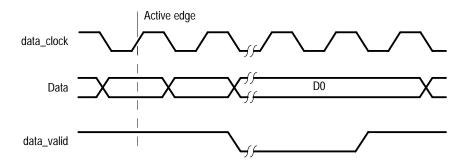

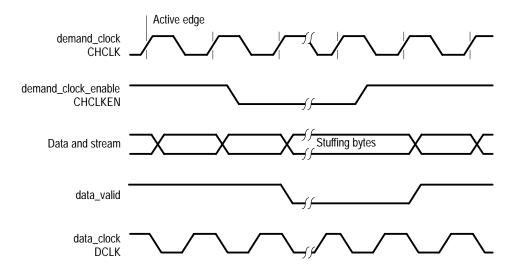

Figure 1–5: Timing diagram for the ECL serial port

Table 1-6: ECL control port pinout

| ECL control port               | Pin | Function                       |

|--------------------------------|-----|--------------------------------|

|                                | 1   | CHCLK (Channel Clock)          |

|                                | 2   | Ground                         |

| 1                              | 3   | CHSYNC (Channel Sync)          |

| 2 0 6<br>3 0 7<br>4 0 9<br>5 9 | 4   | CHCLKEN (Channel Clock Enable) |

|                                | 5   | Shield                         |

|                                | 6   | CHCLK (Channel Clock)          |

|                                | 7   | Ground                         |

|                                | 8   | CHSYNC (Channel Sync)          |

|                                | 9   | CHCLKEN (Channel Clock Enable) |

Figure 1–6: ECL Timing diagram with control port

Table 1-7: 50 Ohm TTL I/O

| Characteristic                                          | Description                  | Supplemental information                                                                       |  |

|---------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------|--|

| Connectors                                              | SMB                          | Male                                                                                           |  |

| Rise & Fall Times                                       |                              | Between 2 ns and 6.5 ns                                                                        |  |

| $ ightharpoonup$ Signal swing into 50 $\Omega$ (output) | Low < 0.3 V<br>High > 2.65 V |                                                                                                |  |

| Digital Format                                          |                              | Binary, positive logic                                                                         |  |

| Maximum Data Rate                                       |                              | 45 Mbps                                                                                        |  |

| Minimum Data Rate                                       |                              | 1 Mbps                                                                                         |  |

| ✓ Generation/Acquisition Test                           | Error free                   | Tested with a 10 MB file at maximum data rates (within the constraints of the stop/start bits) |  |

| Termination (input)                                     |                              | 50 Ω nominal resistive                                                                         |  |

| Timing Diagram                                          |                              | DATA signal is stable on the leading edge of the clock signal (see Figure 1–7)                 |  |

| Clock to Data Timing                                    |                              | Data changes within 5 ns of falling clock edge                                                 |  |

| Signal Level Amplitude (input)                          |                              | TTL Low < 0.8 V<br>High > 2.0 V                                                                |  |

Table 1-8: TTL 50 Ohm Clock In port

| Characteristic            | Description | Supplemental information              |

|---------------------------|-------------|---------------------------------------|

| Clock port voltage levels |             | TTL Low: < 0.8 V<br>TTL High: > 2.0 V |

| Termination               |             | 50 Ω, nominally resistive             |

| Range                     |             | 125 kHz to 45 MHz                     |

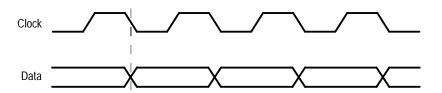

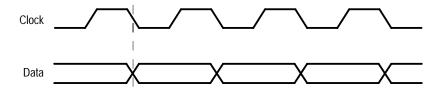

Figure 1–7: Timing for the TTL port and the separate clock input

Table 1-9: 10 Mbit serial port (RS-422 levels I/O Port)

| Characteristic                     | Description                | Supplemental information                                                                       |

|------------------------------------|----------------------------|------------------------------------------------------------------------------------------------|

| Connector                          | 9-pin sub-miniature D-type | Female (pinout described in Table 1–10)                                                        |

| 10 Mbit Serial Voltage Levels      |                            | Differential outputs measured single-ended                                                     |

| Output                             |                            | Low < 0.5 V<br>High > 2.5 V                                                                    |

| Input                              |                            | Low < -0.5 V differential<br>High > 0.5 V differential                                         |

| Common Mode Range                  |                            | ±5 Volts                                                                                       |

| 10 Mbit Serial Rise and Fall Times |                            | Between 2 ns and 12 ns                                                                         |

| Maximum Data Rate                  |                            | 10 Mbps                                                                                        |

| Minimum Data Rate                  |                            | 1 Mbps                                                                                         |

| Clock to Data Timing               |                            | Data changes within 10 ns of falling clock edge                                                |

| ✓ Generation/Acquisition Test      | Error free                 | Tested with a 10 MB file at maximum data rates (within the constraints of the stop/start bits) |

Table 1-10: 10 Mbit serial port pinout

| 10 Mbit serial port | Pin | Function      |

|---------------------|-----|---------------|

|                     | 1   | DATA IN       |

|                     | 2   | CLK IN        |

| 1                   | 3   | DATA OUT      |

| 2 1 6               | 4   | CLK OUT       |

| 3 7 8 8 5 9         | 5   | Ground        |

|                     | 6   | DATA IN       |

|                     | 7   | <u>CLK IN</u> |

|                     | 8   | DATA OUT      |

|                     | 9   | CLK OUT       |

Figure 1–8: Timing diagram for the 10 Mbit Serial port

Table 1-11: PLL

| Characteristic     | Description                              | Supplemental information         |

|--------------------|------------------------------------------|----------------------------------|

| Range              |                                          | 125 kHz to 60 MHz                |

| Resolution         |                                          | 1 Hz                             |

| ✓ Jitter           | 0.2 UI peak-to-peak over a 1000 UI delay |                                  |

| Settling Time      |                                          | 3 seconds after frequency change |

| Frequency Accuracy |                                          | 10 ppm ± resolution              |

# **Electrical Characteristics, Real-Time Analyzer**

Table 1–12: Parallel input port

| Characteristic                    | Description                                               | Supplemental information                |

|-----------------------------------|-----------------------------------------------------------|-----------------------------------------|

| Connector                         | D25                                                       | Female (pinout described in Table 1–14) |

| ✓ Input Data Rate                 | 60 Mbps maximum, 1 Mbps minimum                           |                                         |

| Signal Amplitude, typical         | 2.0 V <sub>pp</sub> maximum, 100 mV <sub>pp</sub> minimum |                                         |

| Signal Common Mode Range, typical | –1.8 V to +2.5 V                                          |                                         |

| Termination, nominal              | 100 ohms resistive                                        | Line-to-line                            |

| Timing Reference                  | Rising edge of clock                                      |                                         |

| Clock-to-data Timing              | Data must be stable ±5 ns of rising clock edge            |                                         |

Table 1-13: Parallel output port

| Characteristic      | Description                                                | Supplemental information                                                                          |

|---------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Connector           | D25                                                        | Female (pinout described in Table 1–14)                                                           |

| Signal Amplitude    | LVDS or modified ECL levels, software selectable           | Modified Differential ECL is less than the typical 100K ECL level of ≈ 700 mVp-p                  |

|                     | 454 mV <sub>pp</sub> maximum, 247 mV <sub>pp</sub> minimum | 908 mV <sub>pp</sub> max, 494 mV <sub>pp</sub> min, differential 100 ohm line-to-line termination |

| ✓ Modified ECL      | 454 mV <sub>pp</sub> maximum, 247 mV <sub>pp</sub> minimum | 908 mV <sub>pp</sub> max, 494 mV <sub>pp</sub> min, differential 100 ohm line-to-line termination |

| Common Mode Voltage |                                                            |                                                                                                   |

| LVDS Output         | + 0.70 V minimum, + 1.40 V maximum                         |                                                                                                   |

| Modified ECL Output | - 1.80 V maximum, - 1.50 V minimum                         |                                                                                                   |

LVDS/ECL/RS422 Pin Pin **Function Function** parallel port **DCLK** DCLK 1 14 2 Ground 15 Ground 3 DATA 7 16 DATA 7 15 3 DATA 6 17 DATA 6 16 17 5 DATA 5 18 DATA 5 5 18 6 DATA 4 19 DATA 4 6 7 DATA 3 7 DATA 3 20 20 8 DATA 2 8 DATA 2 21 9 9 DATA 1 22 DATA 1 10 23 DATA 0 23 DATA 0 10 11 24 24 DVALID 11 **DVALID** 12 13 12 **PSYNC** 25 **PSYNC** 13 Shield

Table 1-14: LVDS/ECL/RS422 parallel data pinout

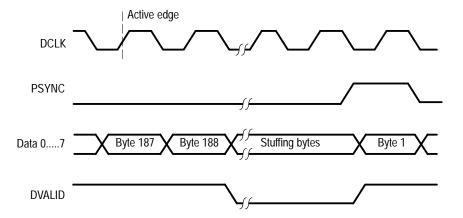

Figure 1-9: Parallel data timing, 188-byte packets

# Table 1-15: ASI input port

| Characteristic            | Description                                                | Supplemental information Female |  |

|---------------------------|------------------------------------------------------------|---------------------------------|--|

| Connector                 | BNC                                                        |                                 |  |

| Input Bit Rate            |                                                            | 270 Mbps ± 100 ppm              |  |

| Signal Amplitude, typical | 800 mV <sub>pp</sub> maximum, 200 mV <sub>pp</sub> minimum |                                 |  |

| Termination, nominal      | 75 ohms                                                    |                                 |  |

| Return Loss, typical      | –17 dB minimum                                             | 27 MHz to 270 MHz               |  |

| Data Formats              | Accepts both Burst and Packet modes                        |                                 |  |

# Table 1–16: ASI output port

| Characteristic               | Description                                                | Supplemental information |

|------------------------------|------------------------------------------------------------|--------------------------|

| Connector                    | BNC                                                        | Female                   |

| Output Bit Rate              |                                                            | 270 Mbps ± 100 ppm       |

| ✓ Signal Amplitude           | 880 mV <sub>pp</sub> maximum, 500 mV <sub>pp</sub> minimum | Into a 75 ohm load       |

| Rise and Fall Times, typical | 1.2 ns maximum                                             | 20% to 80%               |

# **Electrical Characteristics, Synchronous Serial Interface**

Tables 1–17 through 1–19 list the electrical characteristics of the optional Synchronous Serial Interface I/O ports.

Table 1-17: SSI input

| Characteristic       | Description                                                                 | Supplemental information                                                                                                                                                                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector            | BNC                                                                         | Male                                                                                                                                                                                                                                                                                                 |

| Bit rate             | 10 Mbps to 50 Mbps                                                          |                                                                                                                                                                                                                                                                                                      |

| Data format          |                                                                             | SMPTE 310M and DVB SSI compliant                                                                                                                                                                                                                                                                     |

| Signal amplitude     | Minimum: 250 mV <sub>p-p</sub><br>Maximum: 1100 mV <sub>p-p</sub>           |                                                                                                                                                                                                                                                                                                      |

| Signal DC offset     | ±0.5 VDC, maximum                                                           |                                                                                                                                                                                                                                                                                                      |

| Termination, nominal | 75 Ω                                                                        |                                                                                                                                                                                                                                                                                                      |

| Return loss, typical | 100 kHz to 77.6 MHz: -30 db, typical<br>100 kHz to 105 MHz: -15 db, minimum |                                                                                                                                                                                                                                                                                                      |

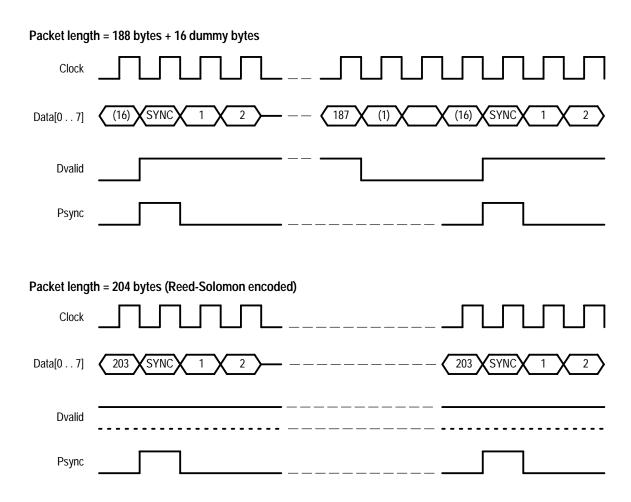

| Synchronization      |                                                                             | Occurs under the following conditions:                                                                                                                                                                                                                                                               |

|                      |                                                                             | The sync byte is 47 hex and the packet length is 188 bytes.                                                                                                                                                                                                                                          |

|                      |                                                                             | 2.) The sync byte is 47 hex and the packet length is 204 bytes; the condition when the 16 Reed Solomon (RS) bytes are dummies. The DVALID line in the SPI output will be low for the 16 RS bytes                                                                                                     |

|                      |                                                                             | 3.) The packet length is 204 bytes and the following sequence occurs: for 7 packets the sync byte is 47 hex and for 1 packet the sync byte is B8 hex. This condition sometimes occurs when the 16 RS bytes are valid. In such a case, the DVALID line in the SPI output is high for the 16 RS bytes. |

| Packet length        | 188 or 204 bytes                                                            |                                                                                                                                                                                                                                                                                                      |

Table 1-18: SSI output

| Characteristic Description      |                                                                                                                                                  | Supplemental information                                                                                                                                                                                                            |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector                       | BNC                                                                                                                                              | Male                                                                                                                                                                                                                                |

| Data format                     |                                                                                                                                                  | SMPTE 310M and DVB SSI compliant                                                                                                                                                                                                    |

| ✓Output Bit rate                | SMPTE 310M (two settings):<br>19,392,658.5 ±54 bits/s for 8 VSB<br>38,785,316.9 ±108 bits/s for 16 VSB<br>DVB, adjustable:<br>10 Mbps to 50 Mbps | The SSI output bit rate is directly dependant on the parallel input bit rate being input. To achieve a more accurate SSI output bit rate, drive the Data Store board external clock input with a precision clock during generation. |

| Transport clock drift rate      | 19,392,685.5 Hz: ±.54 Hz/s (±0.028 ppm/s)<br>38,758,316.9 Hz: ±1.10 Hz/s                                                                         | Measured below 1 Hz                                                                                                                                                                                                                 |

| Interface clock jitter          | Peak to peak: 2 ns                                                                                                                               | Measured at 19,392,658 and 38,758,317 Hz                                                                                                                                                                                            |

| Signal                          |                                                                                                                                                  |                                                                                                                                                                                                                                     |

| Amplitude                       | Minimum: Maximum:                                                                                                                                | Set by convertor board jumper                                                                                                                                                                                                       |

| SMPTE 310M jumper               | 720 mV <sub>p-p</sub> 880 mV <sub>p-p</sub>                                                                                                      |                                                                                                                                                                                                                                     |

| DVB jumper                      | 900 mV <sub>p-p</sub> 1100 mV <sub>p-p</sub>                                                                                                     |                                                                                                                                                                                                                                     |

| DC offset, maximum              | ±0.5 VDC                                                                                                                                         |                                                                                                                                                                                                                                     |

| Rise and fall time <sup>1</sup> | Minimum: 0.4 ns<br>Maximum: 5.0 ns                                                                                                               | Measured between 20% and 80%                                                                                                                                                                                                        |

| Overshoot                       | 10% of signal amplitude maximum                                                                                                                  |                                                                                                                                                                                                                                     |

| Output impedance, nominal       | 75 Ω                                                                                                                                             |                                                                                                                                                                                                                                     |

| Return loss, typical            | Minimum: -30 db 100 kHz to 77.6 MHz<br>-15 db 77.6 MHz to 105 MHz                                                                                |                                                                                                                                                                                                                                     |

<sup>1</sup> Rise and fall times shall not differ by more than 1.6 ns.

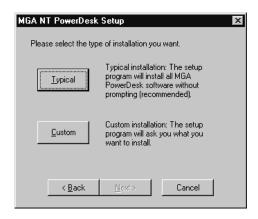

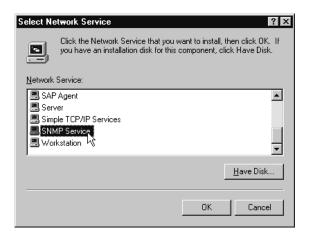

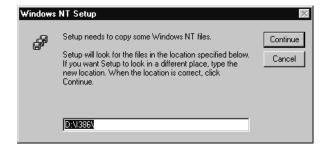

Table 1-19: ECL Parallel I/O port