## **Technical Reference**

# **Tektronix**

Tektronix Logic Analyzer Family Performance Verification and Adjustment Procedures Version 4.0 Software

071-0862-00

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

www.tektronix.com

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., 14200 SW Karl Braun Drive, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

|                  | General Safety Summary                                                                                                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Service Safety Summary                                                                                                                                                                                                                            |

|                  | Preventing Electrostatic Discharge                                                                                                                                                                                                                |

|                  | Preface  Naming Conventions  Service Offerings  Contacting Tektronix                                                                                                                                                                              |

| Introduction     |                                                                                                                                                                                                                                                   |

|                  | Introduction Functional Verification Procedures Certification Test Procedures Performance Verification Procedures Adjustment Procedures Test Equipment Software Installation and Removal Instructions Using the Software Calibration Data Reports |

| TLA600 Series Lo | gic Analyzer                                                                                                                                                                                                                                      |

|                  | TLA600 Series Logic Analyzer Functional Verification  Tests Performed  Test Procedure  Logic Analyzer Probe Functional Verification Procedure  TLA600 Series Certification                                                                        |

|                  | Calibration Data Report                                                                                                                                                                                                                           |

|                  | TLA600 Series Logic Analyzer Performance Verification Prerequisites Tests Performed Test Equipment Test Procedures Using the Software Troubleshooting Performance Verification Tests Completing the Performance Verification                      |

|                  | TLA600 Series Logic Analyzer Adjustment Prerequisites Using the Software Test Equipment Adjustment Instructions Tests Performed Adjustment Procedures Self Calibration                                                                            |

# **Portable Mainframe**

|                     | Portable Mainframe Functional Verification                                    |

|---------------------|-------------------------------------------------------------------------------|

|                     | Tests Performed                                                               |

|                     | Test Procedure                                                                |

|                     | Portable Mainframe Certification                                              |

|                     | Calibration Data Report                                                       |

|                     | Portable Mainframe Performance Verification  Tests Performed  Test Procedures |

|                     | Portable Mainframe Adjustment                                                 |

| Benchtop Chassis ar | nd Expansion Mainframe                                                        |

| •                   | Benchtop Chassis and Expansion Mainframe Functional                           |

|                     | Verification                                                                  |

|                     | Benchtop Chassis                                                              |

|                     | Expansion Chassis                                                             |

|                     | Benchtop Chassis and Expansion Mainframe Certification                        |

|                     | Benchtop Chassis and Expansion Mainframe Performance                          |

|                     | Verification                                                                  |

|                     | Test Procedure                                                                |

|                     | Benchtop Chassis and Expansion Mainframe Adjustment                           |

| Benchtop Controller |                                                                               |

|                     | Benchtop Controller Functional Verification                                   |

|                     | Benchtop Controller Certification                                             |

|                     | Calibration Data Report                                                       |

|                     | Benchtop Controller Performance Verification                                  |

|                     | Tests Performed                                                               |

|                     | Test Procedures                                                               |

|                     | Benchtop Controller Adjustment                                                |

| Logic Analyzer Modu | ıle                                                                           |

|                     | Logic Analyzer Module Functional Verification                                 |

|                     | Test Equipment                                                                |

|                     | Setup                                                                         |

|                     | Module Self Tests and Power-On Diagnostics                                    |

|                     | Merged LA Module Functional Verification Procedure                            |

|                     | Logic Analyzer Probe Functional Verification Procedure                        |

|                     | Logic Analyzer Module Certification                                           |

|                     | Logic Analyzer Module Performance Verification                                |

|                     | Prerequisites                                                                 |

|                       | Merged Modules                                                        |

|-----------------------|-----------------------------------------------------------------------|

|                       | Tests Performed                                                       |

|                       | Test Equipment                                                        |

|                       | Using the Software                                                    |

|                       | Troubleshooting                                                       |

|                       | Completing the Performance Verification                               |

|                       | Logic Analyzer Module Adjustment Procedure                            |

|                       | Prerequisites                                                         |

|                       | Merged Modules                                                        |

|                       | Using the Software                                                    |

|                       | Test Equipment                                                        |

|                       | Adjustment Instructions                                               |

|                       | Tests Performed                                                       |

|                       | Adjustment Procedures                                                 |

|                       | Self Calibration                                                      |

|                       | Completing the Adjustment Steps                                       |

| Logic Anlayzer Adjust | ment/Verification Fixture                                             |

|                       | Adjustment/Verification Fixture Functional Verification               |

|                       | Test Procedure                                                        |

|                       | Adjustment/Verification Fixture Certification                         |

|                       | Calibration Data Report                                               |

|                       | Adjustment/Verification Fixture Performance Verification              |

|                       | Prerequisites                                                         |

|                       | Test Equipment                                                        |

|                       | Tests Performed                                                       |

|                       | Test Procedures                                                       |

|                       | Adjustment/Verification Fixture Adjustment                            |

|                       | Adjustment Procedure                                                  |

|                       | Adjustment/Verification Fixture Adjustment                            |

| Oscilloscope Module   |                                                                       |

|                       | DSO Module Functional Verification                                    |

|                       | Test Equipment                                                        |

|                       | Setup                                                                 |

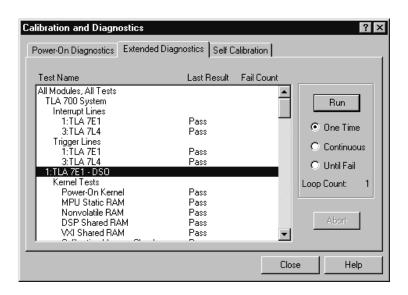

|                       | Module Self Tests and Power-On Diagnostics                            |

|                       | Extended Diagnostics                                                  |

|                       | Self Cal                                                              |

|                       | Probe Calibration                                                     |

|                       | DSO Module Certification                                              |

|                       | <b>DSO Module Performance Verification</b>                            |

|                       | Prerequisites                                                         |

|                       | Using the Software                                                    |

|                       | Test Equipment                                                        |

|                       | Performance Verification Instructions  Performance Verification Tests |

|                       | Completing the Performance Verification                               |

|                  | DSO Module Adjustment Prerequisites Using the Software Test Equipment Adjustment Instructions Adjustment Procedures Completing the Adjustment Steps                                                                                                         | 8-25<br>8-25<br>8-26<br>8-27<br>8-28<br>8-29<br>8-38 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Pattern Generato | r Module                                                                                                                                                                                                                                                    |                                                      |

|                  | Pattern Generator Module Functional Verification  Test Equipment Setup Module Self Tests and Power-On Diagnostics Extended Diagnostics Using the Software Setup Files Troubleshooting Functional Verification Tests  Pattern Generator Module Certification | <b>9–1</b> 9–2 9–4 9–5 9–6 9–7 <b>9–29</b>           |

|                  | Pattern Generator Module Performance Verification Prerequisites Tests Performed Test Equipment Performance Verification Tests Pattern Generator Module Adjustment Procedure                                                                                 | 9-31<br>9-31<br>9-31<br>9-31<br>9-32<br>9-37         |

| Appendices       |                                                                                                                                                                                                                                                             |                                                      |

|                  | Appendix A: Specifications                                                                                                                                                                                                                                  | <b>A-1 B-1</b> B-2                                   |

# **List of Figures**

| Figure 1–1: Calibration/certification procedure flow chart                   | 1-4  |

|------------------------------------------------------------------------------|------|

| Figure 2–1: Probe functional verification test setup                         | 2–4  |

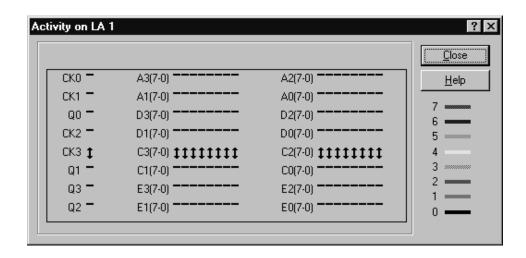

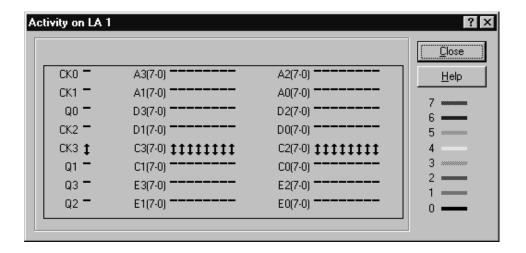

| Figure 2–2: Activity Monitor                                                 | 2-5  |

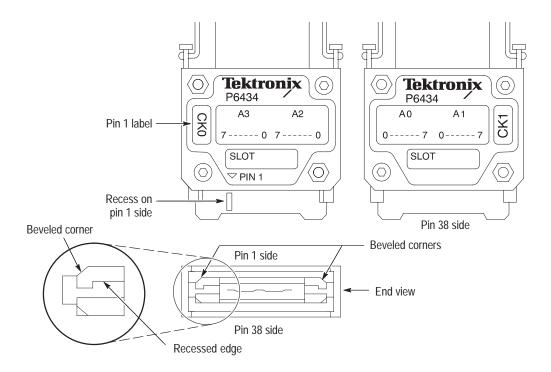

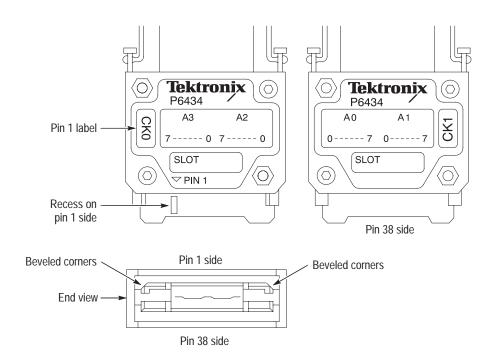

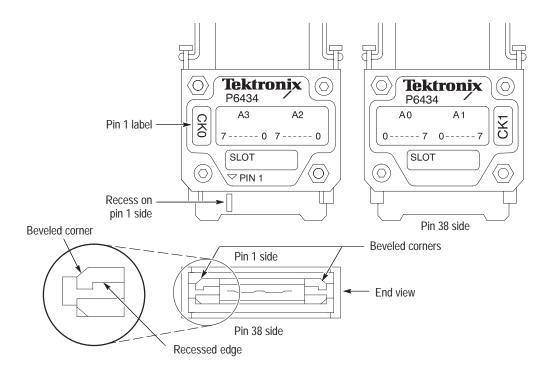

| Figure 2–3: P6434 probe detail                                               | 2–15 |

| Figure 2–4: Adjustment/verification fixture connections and jumper           |      |

| locations                                                                    | 2–17 |

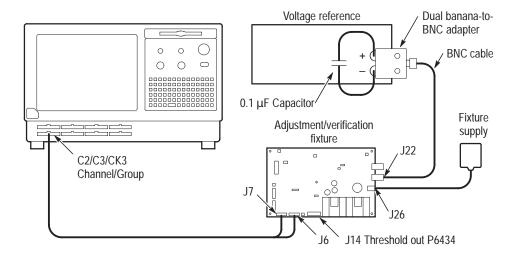

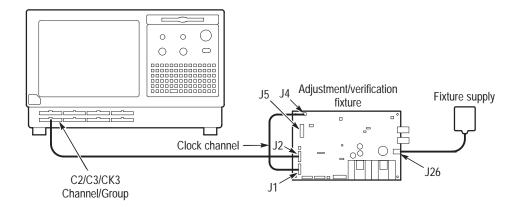

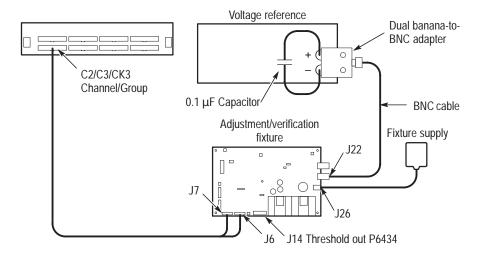

| Figure 2–5: FPV_DC_Threshold test setup                                      | 2–18 |

| Figure 2–6: Initial FPV_Setup_0F test setup                                  | 2–19 |

| Figure 2–7: Initial FPV_Hold_0F test setup                                   | 2-20 |

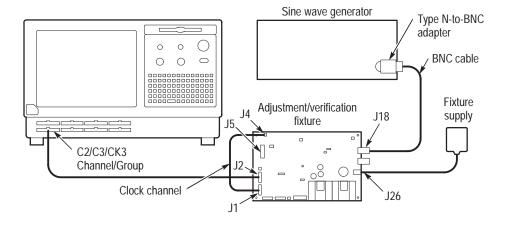

| Figure 2–8: FPV_Maxsync test setup                                           | 2-21 |

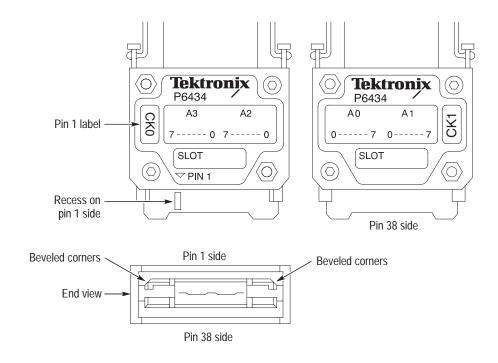

| Figure 2–9: P6434 probe detail                                               | 2-25 |

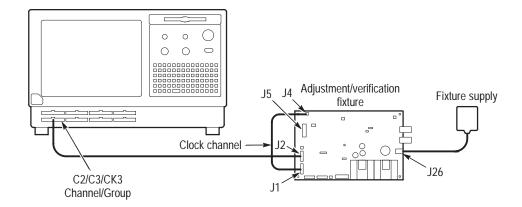

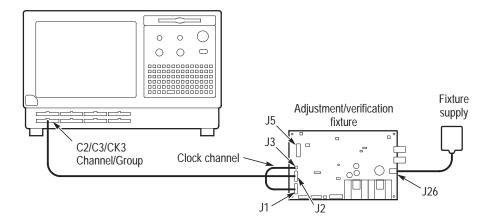

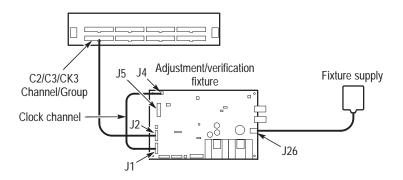

| Figure 2–10: Initial deskew test setup                                       | 2–28 |

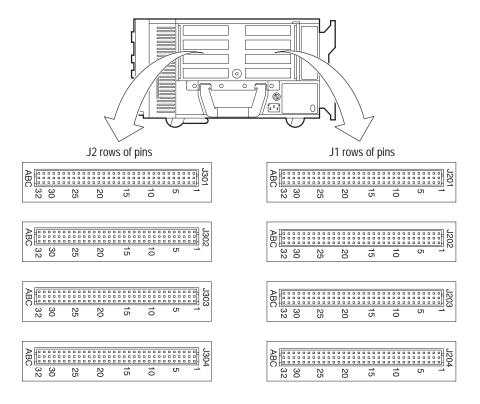

| Figure 3–1: Location of J1 and J2 pins in the portable mainframe             | 3–11 |

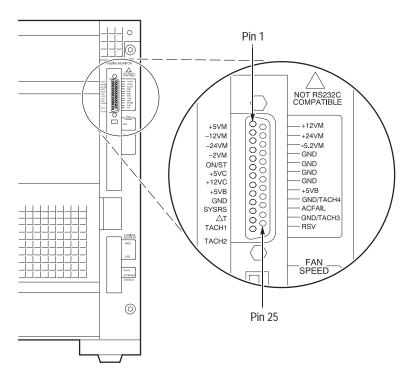

| Figure 4–1: Benchtop and Expansion Chassis 25-pin rear panel connector       | 4–6  |

| Figure 6–1: Probe functional verification test setup                         | 6-5  |

| Figure 6–2: Activity Monitor                                                 | 6-6  |

| Figure 6–3: P6434 probe detail                                               | 6-13 |

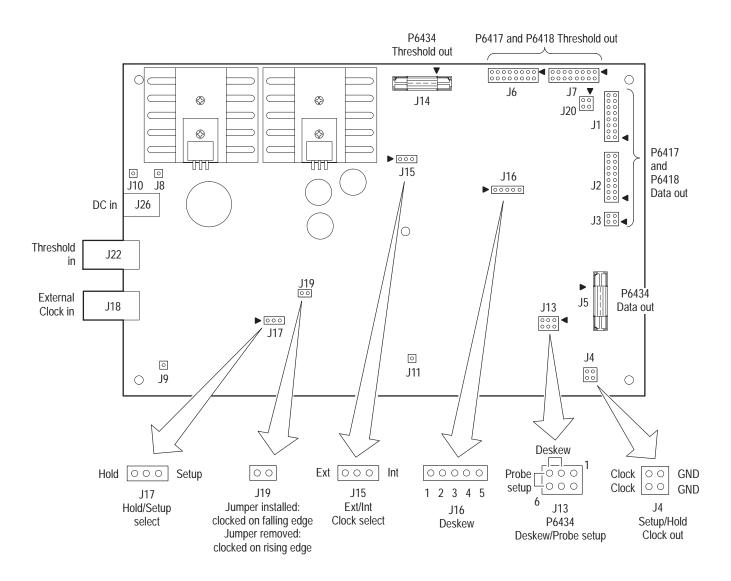

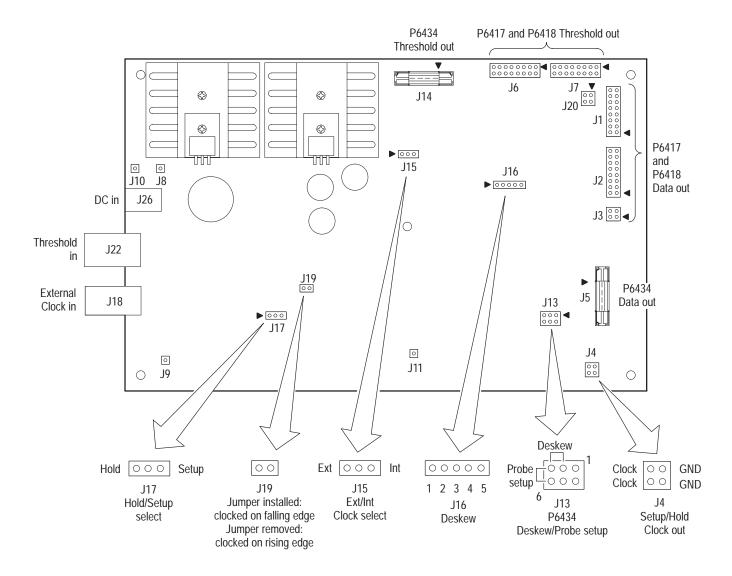

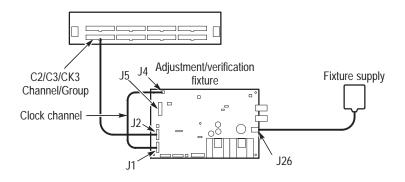

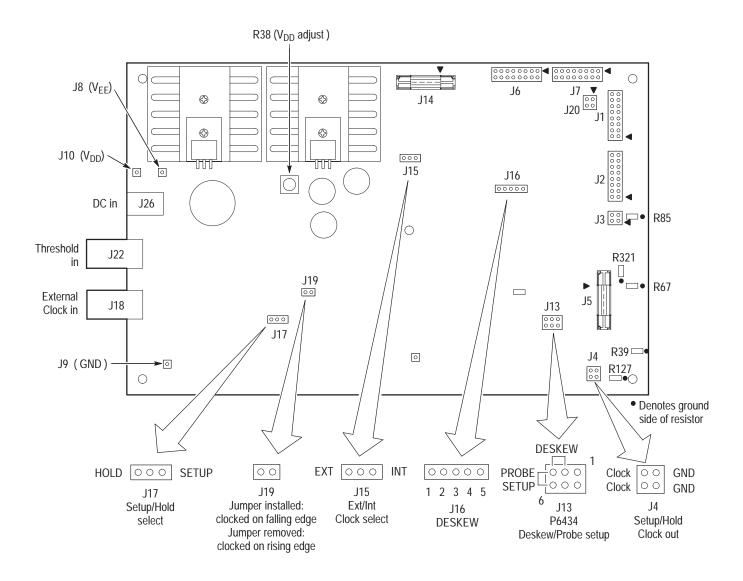

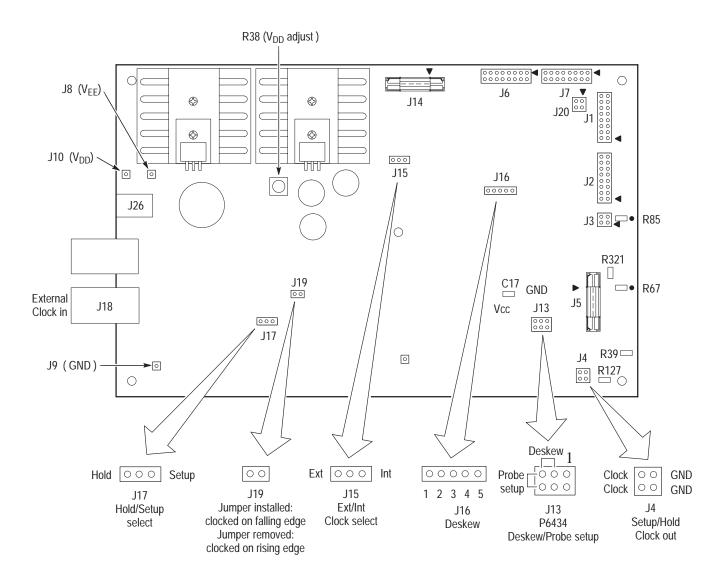

| Figure 6–4: Adjustment/verification fixture connections and jumper locations | 6–14 |

|                                                                              |      |

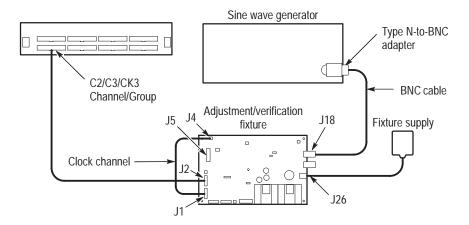

| Figure 6-5: FPV_DC_Threshold test setup                                      | 6–15 |

| Figure 6–6: Initial FPV_Setup_0F test setup                                  | 6–16 |

| Figure 6–7: Initial FPV_Hold_0F test setup                                   | 6–17 |

| Figure 6–8: FPV_Maxsync test setup                                           | 6–18 |

| Figure 6–9: P6434 probe detail                                               | 6–24 |

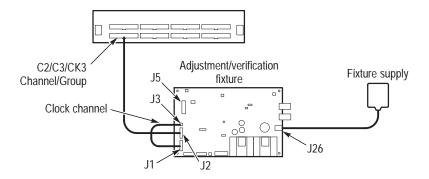

| Figure 6–10: Initial deskew test setup                                       | 6–28 |

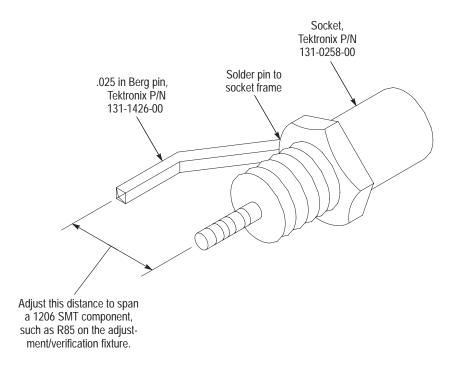

| Figure 7–1: Probe tip adapter detail                                         | 7–10 |

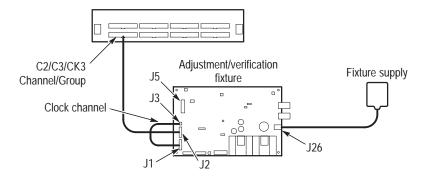

| Figure 7–2: Adjustment/verification fixture detail                           | 7–12 |

| Figure 7–3: Adjustment/verification fixture circuit board layout             | 7–23 |

| Figure 8–1: Calibration and Diagnostics property sheet                                                                         | 8–2  |

|--------------------------------------------------------------------------------------------------------------------------------|------|

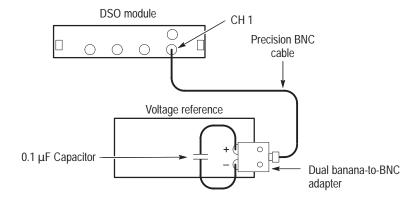

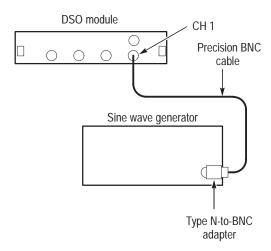

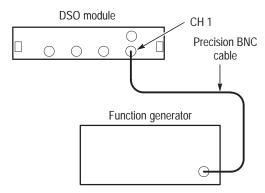

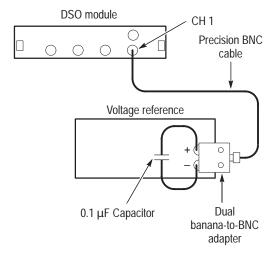

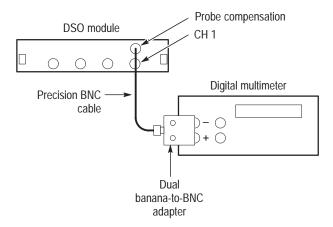

| Figure 8–2: Initial setup for the DC gain accuracy test                                                                        | 8–12 |

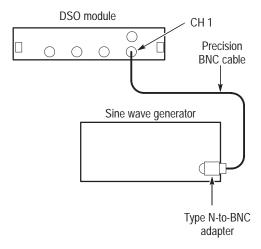

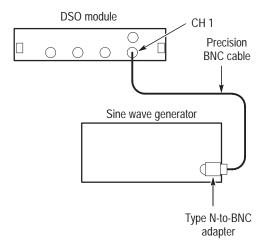

| Figure 8–3: Initial setup for the analog bandwidth test                                                                        | 8–14 |

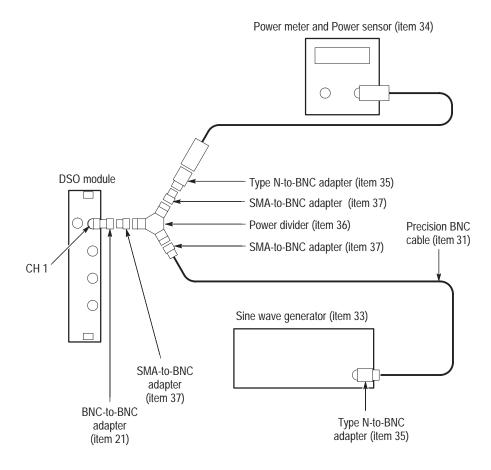

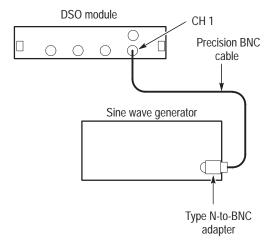

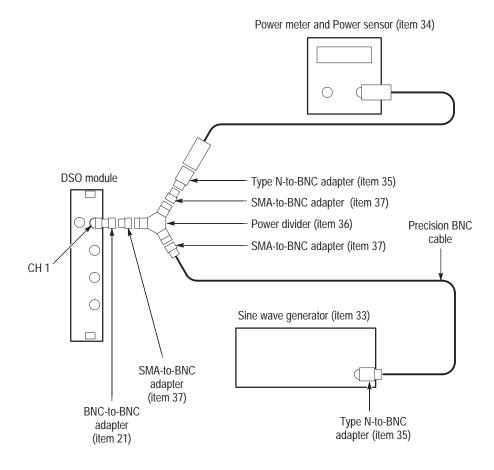

| Figure 8–4: Using a power meter to monitor the amplitude of the                                                                |      |

| sine wave generator during the analog bandwidth test                                                                           | 8–15 |

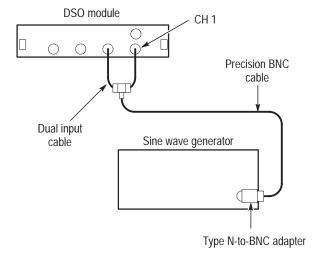

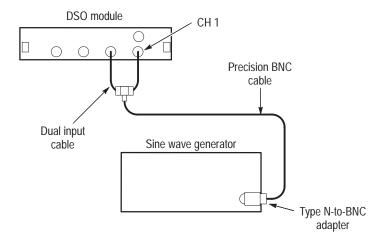

| Figure 8–5: Initial setup for the delay between channels test                                                                  | 8–17 |

| Figure 8–6: Initial setup for the timebase accuracy test                                                                       | 8–18 |

| Figure 8–7: Initial setup for the main trigger accuracy test                                                                   | 8–20 |

| Figure 8–8: Initial setup for the main trigger sensitivity test                                                                | 8–21 |

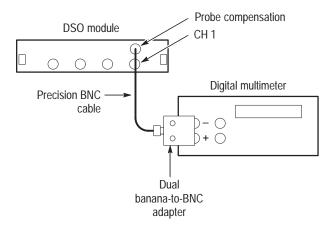

| Figure 8–9: Initial setup for the probe compensation test                                                                      | 8–22 |

| Figure 8–10: Initial setup for the base calibration adjustment                                                                 | 8–30 |

| Figure 8–11: Initial setup for the frequency response adjustment                                                               | 8–32 |

| Figure 8–12: Using a power meter to monitor the amplitude of the sine wave generator during the frequency response adjustment. | 8–33 |

| Figure 8–13: Initial setup for the channel-to-channel skew                                                                     |      |

| adjustment                                                                                                                     | 8–36 |

| Figure 8–14: Initial setup for the probe compensation test                                                                     | 8–37 |

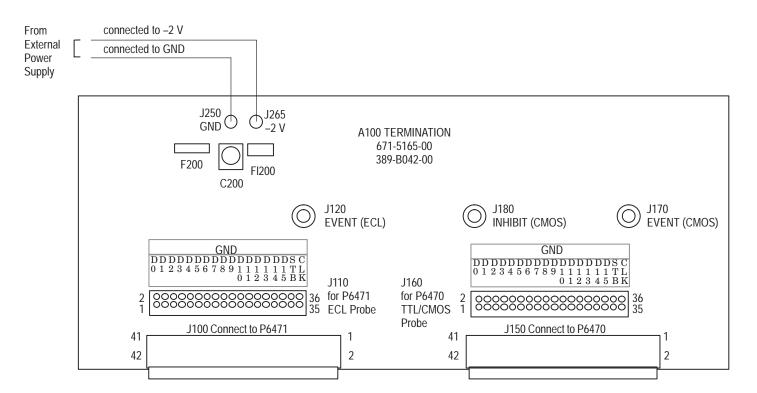

| Figure 9–1: Termination Board                                                                                                  | 9–2  |

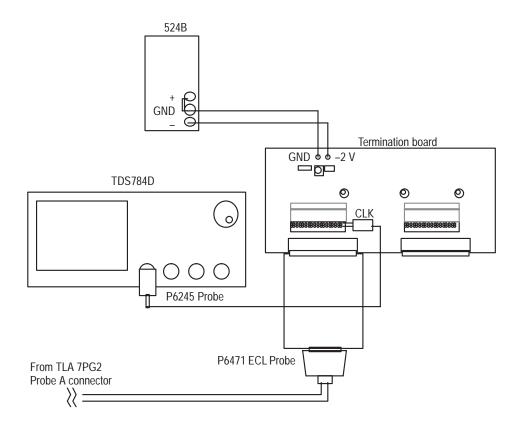

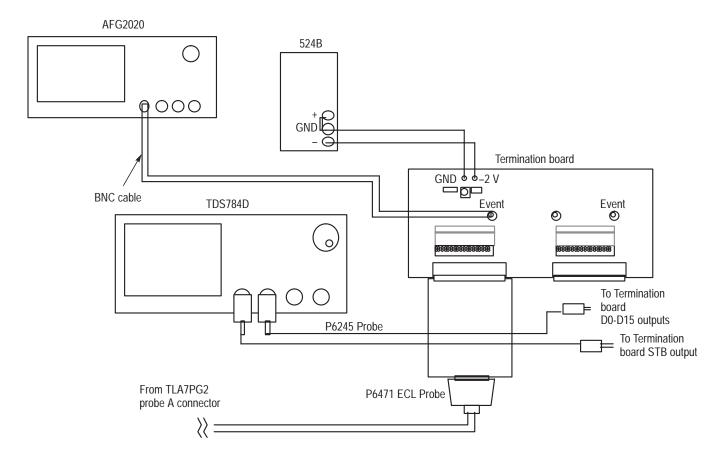

| Figure 9–2: Internal Clock Frequency connections                                                                               | 9–8  |

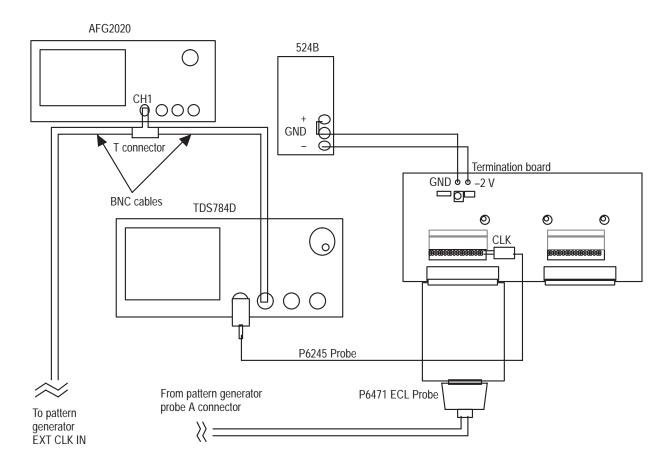

| Figure 9–3: External Clock Input connections                                                                                   | 9–11 |

| Figure 9–4: Sequence and Data Output connections                                                                               | 9–14 |

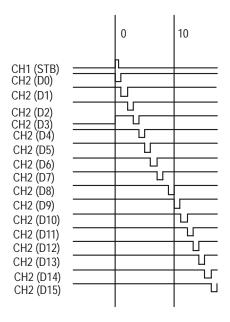

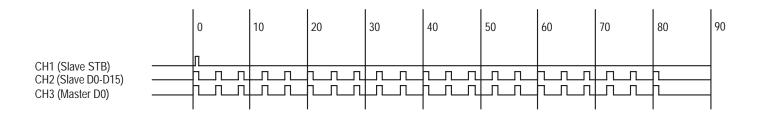

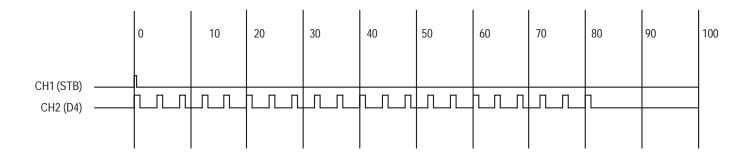

| Figure 9–5: Timing Chart                                                                                                       | 9–16 |

| Figure 9–6: Timing Chart                                                                                                       | 9–17 |

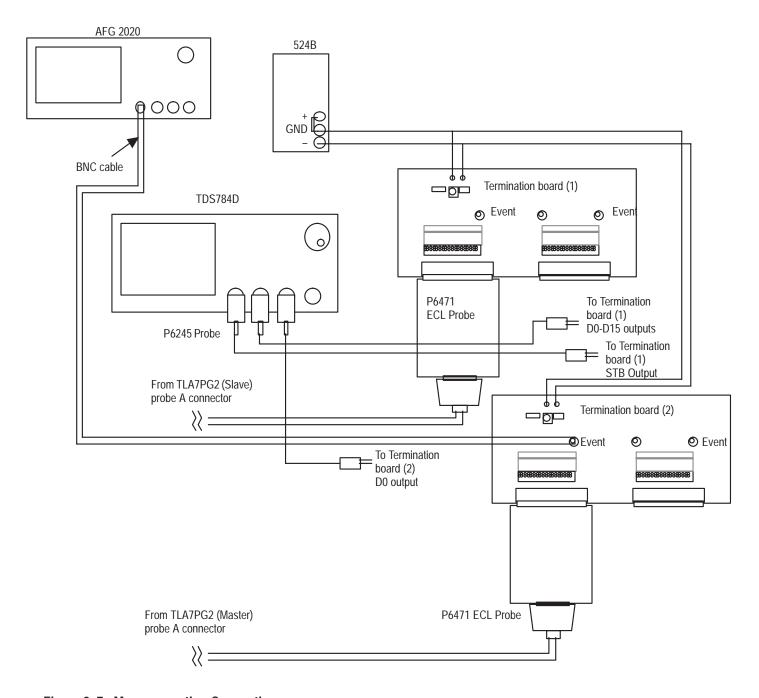

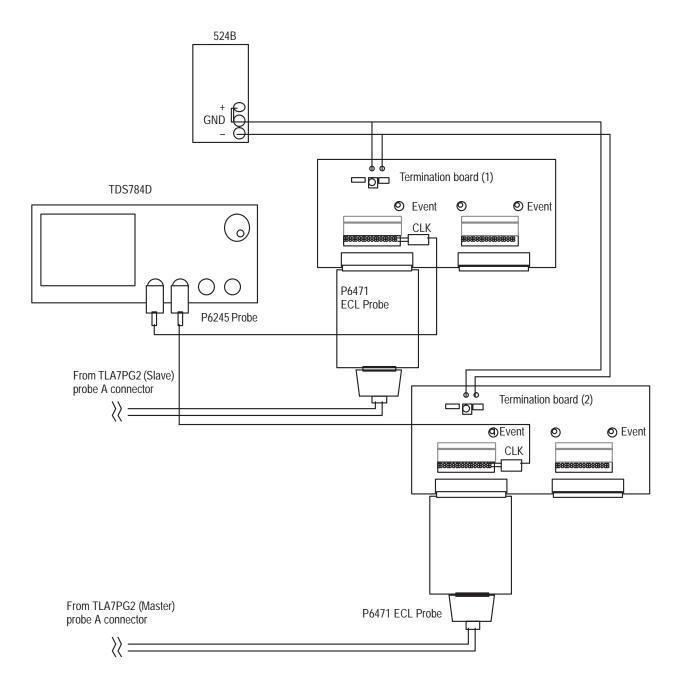

| Figure 9–7: Merge operation Connections                                                                                        | 9–18 |

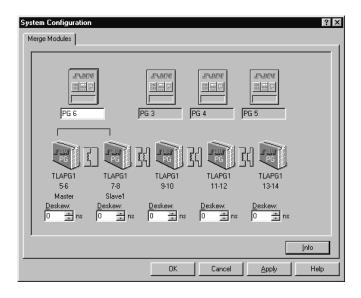

| Figure 9–8: Merged and unmerged modules in the Merge Modules                                                                   |      |

| window                                                                                                                         | 9–20 |

| Figure 9–9: Timing Chart                                                                                                       | 9–21 |

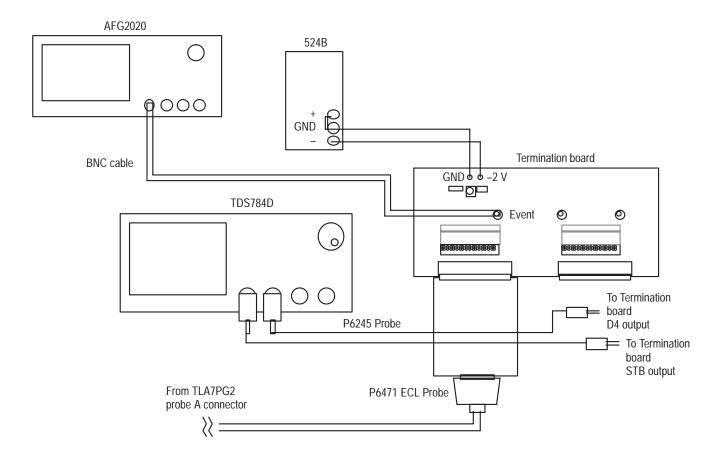

| Figure 9–10: Deskew function connections                                                                                       | 9–22 |

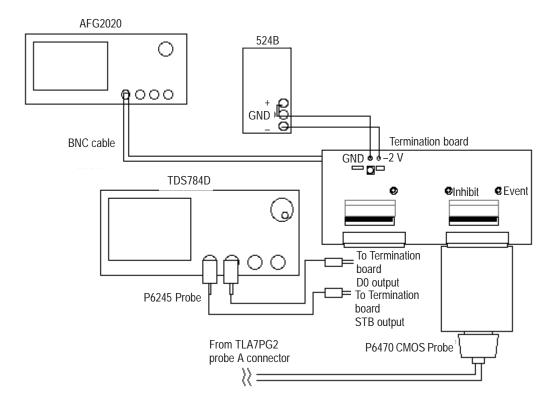

| Figure 9–11: Inhibit function connections                                                                                      | 9–25 |

| Figure 9–12: Maximum Operating Frequency Connections                                                                           | 9–33 |

| Figure 9–13: Timing chart for the maximum operating frequency                                                                  |      |

| check                                                                                                                          | 9–34 |

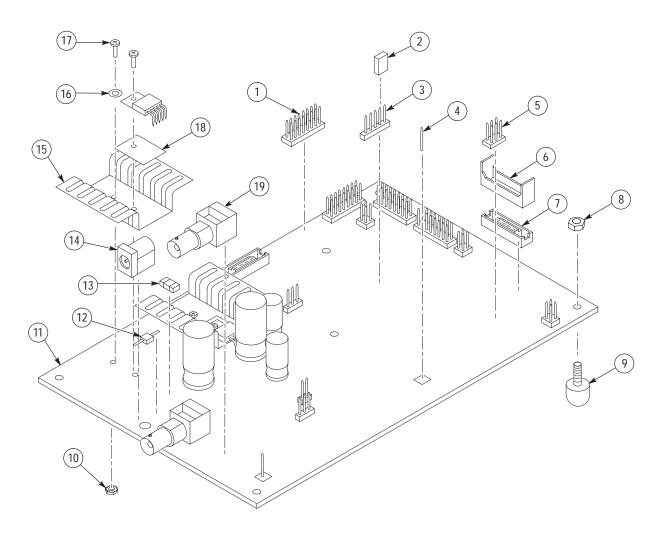

| Figure B–1: Adjustment/verification fixture exploded view                                                                      | B-5  |

# **List of Tables**

| Table 1–1: Levels of testing and adjustment                          | 1–2  |

|----------------------------------------------------------------------|------|

| Table 1–2: Typical order of procedures                               | 1–2  |

| Table 1–3: Test equipment                                            | 1–5  |

| Table 2–1: TLA600 Functional verification procedures                 | 2–1  |

| Table 2–2: TLA600 PV/Adjust software performance verification tests  | 2–12 |

| Table 2-3: TLA600 characteristics indirectly checked by the PV/Adjus | t    |

| software performance verification tests                              | 2–12 |

| Table 3–1: Functional verification procedures                        | 3–1  |

| Table 3–2: Performance verification procedures                       | 3–9  |

| Table 3–3: Power supply voltages and backplane connector pins        | 3–11 |

| Table 4–1: Power supply voltages at the 25-pin connector             | 4–6  |

| Table 5–1: Functional verification procedures                        | 5–1  |

| Table 5–2: Performance verification procedures                       | 5–7  |

| Table 6–1: Logic Analyzer Module functional verification             |      |

| procedures                                                           | 6–1  |

| Table 6–2: LA Module performance verification tests                  | 6–10 |

| Table 6–3: LA Module characteristics indirectly checked by the       | C 11 |

| performance verification tests                                       | 6–11 |

| Table 7–1: Adjustment/verification fixture performance               | 7–10 |

| verification tests                                                   |      |

| Table 7–2: Adjustment/verification fixture jumper settings           | 7–12 |

| Table 8–1: DSO PV/Adjust software performance verification tests     | 8–8  |

| Table 8–2: DSO module fault isolation                                | 8–10 |

| Table 8–3: DSO Adjustments and dependencies                          | 8–27 |

| Table 8–4: Fault isolation                                           | 8–29 |

| Table 9–1: Pattern generator module functional verification          |      |

| procedures                                                           | 9–1  |

| Table 9–2: Front panel indicators                                    | 9–4  |

| Table 9–3: Extended Diagnostic test Items and faulty component       | 9–5  |

Table A-1: Adjustment/verification fixture specifications  $\dots A-1$

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

## To Avoid Fire or Personal Injury

**Use Proper Power Cord.** Use only the power cord specified for this product and certified for the country of use.

**Connect and Disconnect Properly.** Do not connect or disconnect probes or test leads while they are connected to a voltage source.

**Ground the Product.** This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

The common terminal is at ground potential. Do not connect the common terminal to elevated voltages.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

**Do Not Operate Without Covers.** Do not operate this product with covers or panels removed.

**Use Proper Fuse.** Use only the fuse type and rating specified for this product.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

**Keep Product Surfaces Clean and Dry.**

**Provide Proper Ventilation**. Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

## **Symbols and Terms**

**Terms in this Manual**. These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION**. Caution statements identify conditions or practices that could result in damage to this product or other property.

**Terms on the Product**. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

**Symbols on the Product**. The following symbols may appear on the product:

WARNING High Voltage

Protective Ground (Earth) Terminal

CAUTION Refer to Manual

Double Insulated

# **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this Service Safety Summary and the General Safety Summary before performing any service

procedures.

**Do Not Service Alone** Do not perform internal service or adjustments of this product unless another

person capable of rendering first aid and resuscitation is present.

**Disconnect Power** To avoid electric shock, disconnect the main power by means of the power cord

or, if provided, the power switch.

**Use Care When Servicing** Dangerous voltages or currents may exist in this product. Disconnect power, With Power On

remove battery (if applicable), and disconnect test leads before removing

protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

# **Preventing Electrostatic Discharge**

**CAUTION.** Static discharge can damage internal semiconductor components. Follow the guidelines listed below to avoid product damage.

When performing service that requires internal access to an instrument, adhere to the following precautions to avoid damaging internal modules or their components:

- Avoid handling modules or components in areas that have floors or work surfaces capable of generating a static charge.

- Spray carpeted work areas with a solution of equal parts of water and fabric softener.

- Wear clothing made from materials that do not accumulate static charges.

Wool (and some artificial fibers) build up static charges readily; cotton conducts electricity and resists static accumulation.

- Minimize the handling of static-sensitive devices.

- Transport and store static-sensitive devices in their protected containers or on a metal rail. Label any package that contains static-sensitive parts.

- Service instruments and modules at grounded static-free work stations.

- Do not allow any device capable of generating a static charge on work station surfaces.

- Wear a grounding wrist strap while working with static-sensitive devices.

- Handle circuit boards by their edges, if possible.

- Do not slide static-sensitive components over any surface.

- Do not use high-velocity compressed air to clean or dry components or modules.

# **Preface**

This manual contains performance verification and adjustment information for the Tektronix Logic Analyzer Family hardware components. Each section covers an individual hardware component such as a mainframe, module, or adjustment fixture and includes the following information:

- An introduction that describes the procedures

- Equipment lists required to perform the procedures

- Functional verification procedures to quickly determine that the component operates properly (as for a brief incoming inspection)

- Certification test procedures and Calibration Data Reports

- Performance verification procedures to ensure the component operates properly and meets warranted specifications

- Adjustment procedures used to adjust the component to meet its warranted specifications

This manual also includes an introduction with important overview information, and an appendix with a parts list and an exploded view of the Logic Analyzer Adjustment and Verification fixture.

# **Naming Conventions**

This manual uses the following abbreviated names for the full product name throughout the text:

| Full product name                                               | Abbreviated name    |

|-----------------------------------------------------------------|---------------------|

| TLA600 Series Logic Analyzer                                    | TLA600              |

| TLA714 Portable Mainframe                                       | portable mainframe  |

| TLA720 Benchtop Chassis                                         | benchtop chassis    |

| TLA720 Benchtop Controller                                      | benchtop controller |

| TLA7XM Expansion Mainframe                                      | expansion mainframe |

| TLA7Lx, TLA7Mx, TLA7Nx, TLA7Px, or TLA7Qx Logic Analyzer Module | LA module or LA     |

| TLA7Dx and TLA7Ex Digital Storage Scope                         | DSO module          |

| TLA7PG2 Pattern Generator Module                                | pat gen module      |

| Device Under Test / System Under Test                           | DUT / SUT           |

Throughout this manual, the term "module" refers to a LA module, a DSO module, an expansion module, or a benchtop controller module.

## **Service Offerings**

Tektronix provides service to cover repair under warranty as well as other services that are designed to meet your specific service needs.

Whether providing warranty repair service or any of the other services listed below, Tektronix service technicians are well equipped to service the Tektronix Logic Analyzer Family products. Tektronix technicians train on Tektronix products; they have access to the latest information on improvements to the products as well as the latest new product upgrades. Services are provided at Tektronix Service Centers and on-site at your facility, depending on your location.

#### Warranty Repair Service

Tektronix technicians provide warranty service at most Tektronix service locations worldwide. The Tektronix product catalog lists all service locations worldwide or you can visit us on our *Customer Services World Center* web site at Tektronix.com/Measurement/Service. See our latest service offerings and contact us by email.

#### Calibration and Repair Service

In addition to warranty repair, Tektronix Service offers calibration and other services which provide cost-effective solutions to your service needs and quality-standards compliance requirements. Our instruments are supported worldwide by the leading-edge design, manufacturing, and service resources of Tektronix to provide the best possible service.

The following services can be tailored to fit your requirements for calibration and/or repair of the Tektronix Logic Analyzer Family products.

**Service Options.** Tektronix Service Options can be selected at the time you purchase your instrument. You select these options to provide the services that best meet your service needs. These service options are listed on the *Tektronix Service Options* page at the beginning of this manual.

**Service Agreements.** If service options are not added to the instrument purchase, then service agreements are available on an annual basis to provide calibration services or post-warranty repair coverage for the Tektronix Logic Analyzer Family products. Service agreements may be customized to meet special turn-around time and/or on-site requirements.

**Service on Demand.** Tektronix also offers calibration and repair services on a "per-incident" basis that is available with standard prices for many products.

**Self Service.** Tektronix supports repair to the replaceable-part level by providing for circuit board exchange.

Use this service to reduce down-time for repair by exchanging circuit boards for remanufactured ones. Tektronix ships updated and tested exchange boards. Each board comes with a 90-day service warranty.

**For More Information.** Contact your local Tektronix service center or sales engineer for more information on any of the Calibration and Repair Services just described.

# **Contacting Tektronix**

Phone 1-800-833-9200\*

Address Tektronix, Inc.

Department or name (if known) 14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1\*

Service support 1-800-833-9200, select option 2\*

1-800-833-9200, select option 3\*

1-503-627-2400

6:00 a.m. - 5:00 p.m. Pacific time

<sup>\*</sup> This phone number is toll free in North America. After office hours, please leave a voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

# Introduction

# Introduction

This manual contains instructions for testing the performance and adjustment of the following instruments:

- TLA600 Series Logic Analyzers

- TLA714 Portable Mainframe

- TLA720 Benchtop Chassis

- TLA720 Benchtop Controller

- TLA7Lx, TLA7Mx, TLA7Nx, TLA7Px, and TLA7Qx Logic Analyzer Modules

- Logic analyzer probes (tested with the associated logic analyzer)

- Logic Analyzer Module adjustment/verification fixture

- TLA7Dx and TLA7Ex Digitizing Oscilloscope Module

- TLA7PG2 Pattern Generator Modules

- Pattern generator probes (tested with the associated pattern generator module)

Four levels of testing are provided:

- Functional verification procedures

- Performance verification procedures

- Certification test procedures and Calibration Data Reports

- Adjustment procedures

Not all of the components of the Tektronix Logic Analyzer Family require all four levels of testing. Table 1–1 on page 1–2 lists the components of the logic analyzer family and the levels of testing described in this manual.

Certain instruments, such as the Termination Board (used with pattern generator modules), do not require any testing or certification.

Table 1–2 lists the typical order of procedures needed for verifying the performance and adjustment of the instruments. These procedures assume that you are familiar with operating the instruments.

Table 1–1: Levels of testing and adjustment

| Component/product                                          | Functional verification | Certification            | Performance verification | Adjustment               |

|------------------------------------------------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| TLA600 Series Logic<br>Analyzers                           | Yes                     | Yes                      | Yes                      | Yes, software controlled |

| TLA714 Portable<br>Mainframe                               | Yes                     | Yes                      | Yes                      | No                       |

| TLA720 Benchtop<br>Chassis                                 | Yes                     | No                       | Yes                      | No                       |

| TLA720 Benchtop<br>Controller                              | Yes                     | Yes                      | Yes                      | No                       |

| Logic analyzer modules (all versions)                      | Yes                     | Yes, software controlled | Yes, software controlled | Yes, software controlled |

| Logic Analyzer Adjust-<br>ment and Verification<br>fixture | Yes                     | Yes                      | Yes                      | Yes                      |

| TLA7Dx/TLA7Ex<br>Digitizing Oscilloscope<br>Module         | Yes                     | Yes, software controlled | Yes, software controlled | Yes, software controlled |

| TLA7PG2 Pattern<br>Generator modules                       | Yes                     | No                       | Yes                      | No                       |

Table 1-2: Typical order of procedures

| Instrument type                                          | Annual performance verification, calibration, re-certification <sup>1</sup>                                                                                                           | Adjustment, performance verification, calibration, re-certification <sup>1</sup> following board repair                                                                               |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mainframes and benchtop controller                       | Run performance verification procedure                                                                                                                                                | Run performance verification procedure                                                                                                                                                |

| TLA600 Logic<br>Analyzers and all<br>LA modules          | Run performance verification procedure     If module fails performance verification procedure, then run the adjustment procedure     Rerun performance verification if step 2 is done | Run adjustment procedure     Run performance verification procedure                                                                                                                   |

| Logic Analyzer<br>Adjustment and<br>Verification fixture | Run performance verification procedure <sup>2</sup>                                                                                                                                   | Run performance verification procedure                                                                                                                                                |

| Pattern Generator<br>Modules                             | Run the functional verification and the performance verification procedures                                                                                                           | Run the functional verification and the performance verification procedures                                                                                                           |

| DSO modules                                              | Run performance verification procedure     If module fails performance verification procedure, then run the adjustment procedure     Rerun performance verification if step 2 is done | Run performance verification procedure     If module fails performance verification procedure, then run the adjustment procedure     Rerun performance verification if step 2 is done |

<sup>1</sup> Refer to the appropriate certification sections in this document for all certification procedures

<sup>&</sup>lt;sup>2</sup> The Logic Analyzer Adjustment and Verification fixture requires calibration every two years

## **Functional Verification Procedures**

Functional verification procedures verify the basic functionality of the instrument inputs, outputs, and basic instrument actions. These procedures include power-on and extended diagnostics, self calibration, as well as semi-automated or manual check procedures. These procedures can be used for incoming inspection purposes.

## **Certification Test Procedures**

Certification procedures are used to certify the accuracy of an instrument and provide a traceability path to national standards. Certification data is recorded on Calibration Data Reports provided with this manual. Calibration Data Reports are produced for the TLA600 Logic Analyzers, LA modules, and DSO modules as an output from the PV/Adjust software.

### **Performance Verification Procedures**

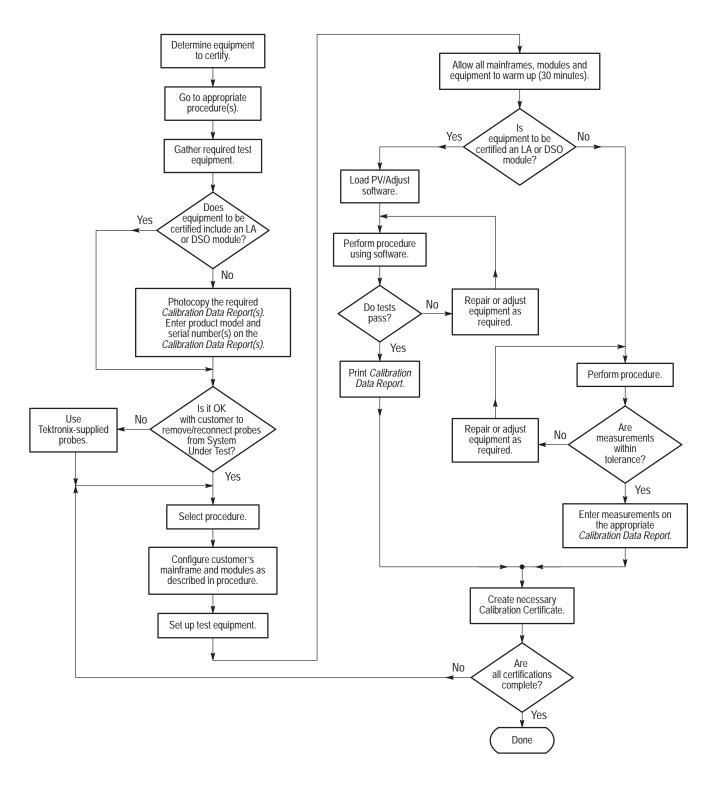

Performance verification procedures confirm that a product meets or exceeds the performance requirements for the published specifications documented in the *Tektronix Logic Analyzer Family User Manual*. Refer to Figure 1–1 on page 1–4 for a graphic overview of the procedures.

## **Adjustment Procedures**

Adjustment procedures check for and, if necessary, correct any adjustment errors discovered when performing functional or performance verification procedures. The adjustment procedures documented in this manual are controlled by software, except for the procedures for the adjustment/verification fixture.

Some procedures require user intervention to move probes or change test equipment settings. The adjustment software is part of the self-calibration routines in the logic analyzer application software and the PV/Adjust software provided with the product CD-ROM.

Figure 1-1: Calibration/certification procedure flow chart

# **Test Equipment**

The procedures in this manual use external, traceable signal sources to directly test characteristics that are designated as checked ( $\checkmark$ ) in the *Specifications* section of the *Tektronix Logic Analyzer Family User Manual*. Table 1–3 shows the required equipment list. Always warm up the equipment for 30 minutes before beginning the procedures.

Table 1–3: Test equipment

| Item number and description                                                                                       | Minimum requirements                                                 | Example                                                                                                                     | Where used                                                                         |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 1. Mainframe                                                                                                      | TLA700 Series Mainframe                                              | Benchtop Chassis or<br>Portable Mainframe                                                                                   | All procedures, except<br>TLA600 procedures                                        |

| 2. Controller                                                                                                     | TLA700 Series Controller                                             | Benchtop Controller used with the Benchtop Chassis or the embedded controller in the Portable Mainframe                     | All procedures, except<br>TLA600 procedures                                        |

| 3. TLA700 Series Logic Analyzer<br>Performance Verification &<br>Adjustment Software                              | Included with the Tektronix Logic<br>Analyzer Family CD-ROM          |                                                                                                                             | All procedures for the<br>TLA600 Logic Analyzers,<br>LA modules and<br>DSO modules |

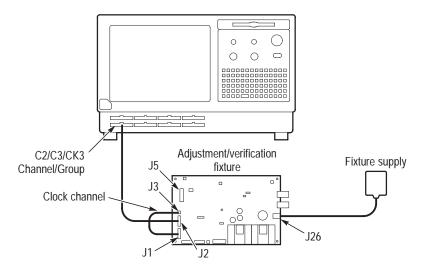

| 4. Adjustment/verification fixture, with one of the following Power Supplies: USA/CAN Europe Japan United Kingdom | 12 V, 1.5 A<br>12 V, 1.5 A<br>12 V, 1.5 A<br>12 V, 1.5 A             | Tektronix part number<br>671-3599-XX<br>Tektronix part numbers:<br>119-4855-XX<br>119-4856-XX<br>119-4859-XX<br>119-4857-XX | Most procedures for the LA module                                                  |

| 5. DSO probe calibration fixture                                                                                  | One required                                                         | Tektronix part number 671-3930-XX                                                                                           | DSO functional verification procedure                                              |

| 6. Oscilloscope                                                                                                   | 1 GHz bandwidth Delay time accuracy ±25 ppm over any ≥ 1 ms interval | Tektronix TDS 784D                                                                                                          | Adjustment/verification fixture procedures and pattern generator procedures        |

| 7. DSO probes                                                                                                     | Three required, with < one-inch ground leads                         | Tektronix P6243 or P6245 probe, with std. accessories                                                                       | Most procedures for the DSO and Pattern Generator modules                          |

| 8. Logic analyzer probes                                                                                          | Two required                                                         | Tektronix P6417 or P6418<br>Logic Analyzer probes                                                                           | Most procedures for TLA600 and the LA module                                       |

| High density logic analyzer probe (optional)                                                                      | One required                                                         | Tektronix P6434 Logic<br>Analyzer probe                                                                                     | Most procedures for TLA600 and the LA module                                       |

| 10. Pattern Generator module                                                                                      | One required                                                         | TLA7PG2                                                                                                                     | Merge and Deskew pattern generator procedures                                      |

| 11. Pattern Generator probe cable                                                                                 | Eight required                                                       | Tektronix part number 012-A212-00                                                                                           | Pattern generator procedures                                                       |

Table 1–3: Test equipment (Cont.)

| Item number and description                | Minimum requirements                                                           | Example                                     | Where used                                                  |

|--------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|

| 12. TTL/CMOS Pattern Generator probes      | Four required                                                                  | Tektronix P6470 Pattern<br>Generator probes | Most pattern generator procedures                           |

| 13. ECL Pattern Generator probes           | Four required                                                                  | Tektronix P6471 Pattern<br>Generator probes | Most pattern generator procedures                           |

| 14. Termination board                      | Two required                                                                   | Tektronix part number 067-A016-00           | Most pattern generator procedures                           |

| 15. Frequency counter                      | Frequency accuracy: <0.0025%<br>Frequency range: 1 kHz to 100 MHz              | Hewlett Packard 5314A                       | Portable Mainframe and<br>Benchtop Controller<br>procedures |

| 16. Function generator                     | Amplitude: 4V Offset: 2 V (50 $\Omega$ termination) Frequency: 1 MHz or higher | Tektronix AFG2020                           | Pattern generator procedures                                |

| 17. Power supply                           | Voltage: –2 V<br>Current: 1 A                                                  | METRONIX 524B                               | Pattern generator procedures                                |

| 18. BNC Cable                              | Impedance: 50 Ω,<br>Length: 24 in (two required)                               | Tektronix part number<br>012-1342-XX        | Pattern generator procedures                                |

| 19. T-Connector                            | One required                                                                   | Tektronix part number<br>103-0030-XX        | Pattern generator procedures                                |

| 20. SMB-to-BNC cable                       | One required                                                                   | Tektronix P6041                             | PV procedures for the<br>Benchtop Controller                |

| 21. Adapter, male BNC-to-male BNC          | One required                                                                   | Tektronix part number<br>103-0029-XX        | DSO procedures                                              |

| 22. Miniature probe-to-square pin adapters | Two required                                                                   | Tektronix part number<br>103-0177-XX        | Portable Mainframe (power supply check)                     |

| 23. 0.025-inch square pin                  | 3/4-inch length, (two required)                                                | Tektronix part number 131-1426-XX           | Portable Mainframe (power supply check)                     |

| 24. Digital multimeter with test leads     | DCV accuracy: 0.1% from –10 V to +100 V                                        | Tektronix DMM 900 Series                    | All procedures except<br>Benchtop Controller                |

| 25. Connector, dual-banana                 | Female BNC-to-dual banana                                                      | Tektronix part number<br>103-0090-XX        | PV procedures for the LA and DSO module                     |

| 26. Voltage reference                      | Accuracy: ≤0.01%                                                               | Data Precision 8200                         | PV procedures for the LA and DSO module                     |

| 27. Capacitor <sup>1</sup>                 | 0.1 μF, 200 V                                                                  | Tektronix part number 283-0189-XX           | PV procedures for the LA and DSO module                     |

| 28. Cable, dual-input                      | Female BNC-to-dual male BNC                                                    | Tektronix part number<br>067-0525-XX        | PV procedures for the DSO module                            |

| 29. Adapter, N-to-BNC                      | Male type N-to-female BNC                                                      | Tektronix part number<br>103-0045-XX        | PV procedures for the DSO module                            |

| 30. Adapter, SMA-to-BNC                    | Female type SMA-to-female BNC                                                  | Tektronix part number 015-1018-XX           | DSO procedures                                              |

Table 1-3: Test equipment (Cont.)

| Item number and description                                               | Minimum requirements                                                                                                                   | Example                                          | Where used                                      |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|

| 31. Cable, precision 50 $\Omega$ coaxial                                  | 50 Ω, 36 in, male-to-male BNC connectors                                                                                               | Tektronix part number 012-0482-XX                | All procedures except<br>Benchtop Chassis       |

| 32. Generator, function                                                   | Frequency range: 1 Hz to 20 MHz<br>Frequency accuracy: 0.1%<br>Amplitude range: 10 mV to 20 V <sub>p-p</sub>                           | Hewlett Packard 3325B                            | PV procedures for the DSO module                |

| 33. Generator, sine wave                                                  | Frequency range: 100 kHz to<br>1005 MHz<br>Frequency accuracy: <6 ppm<br>Amplitude: 2 mV to 1.5 V <sub>RMS</sub><br>Accuracy: <0.35 dB | Gigatronics 6061                                 | PV procedures for the DSO and LA module         |

| 34. Power meter with sensor                                               | Bandwidth: >1.2 GHz Accuracy: 0.2 dB Sensitivity: 500 pW to 20 mW                                                                      | Rohde & Schwarz NRVS<br>with model NRV-Z4 Sensor | DSO adjustment procedure #4                     |

| 35. Adapter, N-to-BNC (used only with power meter)                        | Female type N-to-male BNC                                                                                                              | Tektronix part number<br>103-0058-XX             | DSO adjustment procedure #4                     |

| 36. $50 \Omega$ power divider (used only with power meter)                | Provide load isolation between equipment Maximum VSWR: 1.50                                                                            | Tektronix part number 015-0565-XX                | DSO adjustment procedure #4                     |

| 37. SMA-to-BNC adapters (used only with power meter)                      | For use with the 50 $\Omega$ power divider (three required)                                                                            | Tektronix part number 015-1018-XX                | DSO adjustment procedure #4                     |

| 38. Printer with cable (optional, used to print Calibration Data Reports) | PC-compatible, continuous feed, prints ASCII text, connects to EPP connector                                                           | Any general purpose printer                      | Printing test results for the LA and DSO module |

The capacitor is installed across the Data Precision 8200 output terminals to reduce noise. If your voltage reference produces <4 mVp-p of noise, external noise reduction is not necessary.</p>

## Software Installation and Removal Instructions

These procedures describe loading and unloading the PV/Adjust software. It is recommended you have ≥10 MB of free space on the hard drive before installing the software. The Performance Verification software is located on Disc 1 of the Tektronix Logic Analyzer Family Application Software CD.

**NOTE**. This installation program uses parameters you supply to create a custom start-up file in your hard disk directory.

The batch file enables the software to configure your instrument properly before it runs the program.

- **1.** Power on the instrument.

- **2.** Exit the Application.

#### Verify PV/Adjust Software Version

If your logic analyzer already has PV/Adjust software loaded on it, you must verify that the version is the same as the version printed on Disc 1 of the Tektronix Logic Analyzer Family Application Software CD.

If the version of the PV/Adjust software loaded on your logic analyzer is an earlier version, you must delete the earlier version before you can load the newer version.

#### **Verify Directories**

If your logic analyzer already has a directory named Tekcats or Temptek on the hard drive, the software installation cannot be completed. Follow these instructions to verify the directory is not present:

- **1.** Select Start  $\rightarrow$  Programs  $\rightarrow$  Windows Explorer.

- 2. From the Exploring window select Tools  $\rightarrow$  Find  $\rightarrow$  Files or Folders.

- 3. Select the Name & Location tab, and search for the following directories:

- Tekcats

- Temptek

- **4.** If either directory is found follow the instructions under *Removing the Software* beginning on page 1–9 to remove the software and the directories.

# Install the PV/Adjust Software

Follow these instructions to install the PV/Adjust software and the pattern generator setup files.

- 1. Close all open windows on the desktop.

- **2.** Insert Disc 1 of the Tektronix Logic Analyzer Family Application Software CD in the CD-ROM drive.

- 3. Click the My Computer Icon and double-click the CD-ROM drive.

- **4.** Double-click the TLA Performance Verification folder.

- **5.** Double-click on the Logic Analyzer PV folder and then double-click the Disk1 folder.

- **6.** Double-click the Setup.exe icon to begin the installation program.

- 7. Follow the on-screen instructions to install the software on the hard disk.

- **8.** After the installation is complete, go back to the TLA Performance Verification folder on the CD.

- **9.** Double-click on the Pattern Generator PV folder and then double-click the Disk1 folder.

- **10.** Double-click the Setup.exe icon to begin the installation program.

- 11. Follow the on-screen instructions to install the pattern generator setup files on the hard disk.

This completes the software installation procedure.

#### Removing the Software

Use the following procedure to remove the PV/Adjust software from the instrument. These steps are necessary when you want to upgrade the PV software.

- **1.** Select Start  $\rightarrow$  Programs  $\rightarrow$  Windows Explorer.

- 2. Using Windows Explorer, click the C:\ Tekcats folder.

- **3.** Go to the File menu and select Delete to delete the folder.

- **4.** Repeat steps 1 through 3 to delete the Temptek folder if it exists.

- **5.** Select Start  $\rightarrow$  Settings  $\rightarrow$  Taskbar & Start Menu.

- **6.** Click the Advanced tab.

- Open the following directory path under Documents and Settings:

All Users → Start Menu → Programs

- **8.** Locate and delete the TLA Performance Verification item.

## **Using the Software**

The PV/Adjust software is required to complete the performance verification, adjustment and calibration/certification procedures for the TLA600 Logic Analyzers, the LA modules, and for the DSO modules. A separate series of program files are required for the pattern generator modules. Software is not required to perform any checks on the mainframes or any other subcomponents.

# Pattern Generator Setup Files

The PV/Adjust software used to verify the pattern generator modules consists of setup files rather than executable software. To use the pattern generator setup files complete the following steps:

- 1. Verify that your module configuration matches the setup as called for in the writtern procedure (for some of the setups you will need to merge or unmerge modules).

- **2.** Select Load Module from the File menu; the Load Module dialog box appears.

- **3.** Click the Browse button and navigate to the C:\Program Files\Tektronix Pattern Generator\PV folder.

- **4.** Double-click on the file name; the Load Module dialog box reappears with the file name and module name under the Module list.

- **5.** Click OK to load the module setup. A dialog box may appear reminding you that the current module settings and data will be lost.

- **6.** Click Yes to confirm your choice.

- 7. Follow the remaining written procedures.

## LA and DSO Performance Verification and Adjustment Software

The logic analyzer and DSO software consists of executable software files. Use the software in conjunction with this manual to set up and perform the adjustment procedures or the performance verification procedures. Use this manual in the following manner:

- To provide an overview of each test

- To identify the prerequisites for each test

- To identify the required test equipment

- To connect the external test equipment for each test

# Running the LA and DSO Software

Use the following steps to start and run the logic analyzer and DSO software:

- 1. Allow the instruments to warm up for at least 30 minutes before beginning the procedure.

- **2.** Quit all applications including the TLA application.

- 3. Select Start  $\rightarrow$  Programs  $\rightarrow$  TLA Performance Verification.

- **4.** To run the PV/Adjust software, select one of the following:

- For the TLA7Dx and TLA7Ex DSO modules, select DSO PV.

- For the TLA700 logic analyzer modules, select LA 7XX PV.

- For the TLA600 Logic Analyzer, select LA 6XX PV.

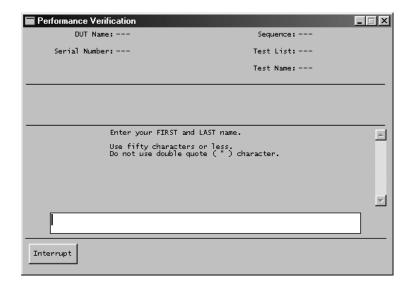

**5.** Follow the instructions on the screen to enter the name you want to appear in the User Name field as shown below. This name will appear on the Calibration Data Reports.

- **6.** Click Enter to continue.

- 7. The program lists several different modules, referred to as DUT (Device Under Test). Enter the number corresponding to the module type that you want to test; then click Enter to continue.

The screen will display an error message if the DUT chosen does not match the installed DUT.

- **8.** Enter the complete serial number of the DUT (for example, B010100). Click Enter to continue.

- **9.** Verify the serial number entry; then click Enter to continue.

If you select no, a prompt asks you to enter the serial number again.

- **10.** The program lists sequences for PV (performance verification) and ADJ (adjustments). Enter a number to select which sequence you want and click Enter to continue.

- 11. If an instrument is being tested, the program lists the different probe types available for testing. Enter the appropriate number corresponding to your probe and then click Enter to continue.

- **12.** Enter the operating temperature in degrees C (entries in the range of 20 to 30 degrees are valid). Click Enter to continue.

- **13.** Enter the operating humidity as a percentage (0% to 100% entries are valid). Click Enter to continue.

- **14.** Determine which sequence to run:

- RUN FULL SEQUENCE runs the entire sequence from beginning to end. This is the recommended selection.

- RUN PARTIAL SEQUENCE runs part of the full sequence. The sequence runs from the selected starting point to the end of the sequence.

- SELECT TEST(S) runs only the selected tests. To run a single test, enter the test number. To run multiple tests, enter a comma-separated list of numbers or a hyphen-separated list of numbers.

Enter the number next to your choice and click Enter to continue.

- **15.** Follow the on-screen instructions to connect and adjust test equipment. You can also refer to the connection diagrams provided in this manual for each test.

- **16.** When testing is completed, disconnect the test equipment.

## **Troubleshooting**

If the test you are attempting to run fails, do the following:

- Check the settings and connections of the test equipment used in the procedure.

- If you are using the adjustment/verification fixture, verify that the LED is lighted and that the jumper positions and external connections are correct.

- Rerun mainframe or module diagnostics and module self-cal, then rerun the test(s) which failed.

If the test(s) still do not pass, the mainframe or module might need further troubleshooting.

#### Using the Interrupt Button

While the program is running, you can interrupt the program to rerun a test, start over, or to exit the program by clicking the Interrupt button (shown below).

The program will then provide a list of choices. Enter the number next to the choice that you want and click Enter.

**NOTE**. If you interrupt a test before it has completed, you must restart the test to obtain valid test data.

Some tests such as Internal Cal do not allow interrupts. If you stop these tests using more aggressive methods, you may have to reboot the instrument.

#### **Obtaining Test Results**

The results of all tests can be stored in a file on the hard disk. You can view the test results, print the test results to a printer, or save the test results in another file on the hard disk.

After running the performance verification procedures, you should create a calibration data report for certification purposes. Refer to *Calibration Data Reports* for details on using the resultant test data with the Calibration Data Report.

## **Calibration Data Reports**

The Calibration Data Reports in this manual are intended to be copied and used for calibration/certification procedures. Some of the certification procedures require you to record data from manual measurements on the Calibration Data Reports directly. The TLA600 Logic Analyzer, the LA module, and the DSO module procedures require that you obtain the test results from the file created by the PV/Adjust software.

After completing the performance verification procedures or the certification procedures, you can fill out a Calibration Data Report to keep on file with your instrument. Calibration Data Reports are provided at the end of the certification procedures in each chapter of this manual, except for the TLA600 Logic Analyzer, the LA module, and DSO module. Calibration Data Reports for these instruments are generated by the PV/Adjust software. The Calibration Data Reports list those product attributes and specifications upon which product accuracy depends.

# Retrieving Test Data from the PV/Adjust Software

The program stores the test results in a file containing the module name and serial number (for example, TLA7E2.B020123). The file is located under the following path: C:\Tekcats\Rpt.

**NOTE**. If you want to save the content of the Report file, you must rename or copy the Report file using the Windows file utilities such as Explorer.

The Report file will be overwritten the next time you run the PV/Adjust software and print or view a new set of test data.

After completing a full or partial test sequence (or just before you exit the program) you can generate the test data and write it to a file. You have the option of printing the file, viewing the file on screen, or transferring the file to another directory or host computer.

You can print the test data directly from the program. Ensure that a printer is connected to your logic analyzer and follow the on-screen instructions to print the test results.

If a printer is not available, you can view the test results directly from the screen, or you can copy the test results to a different file or folder/host computer for future use.

## Field Adjust/PV Software Housekeeping

The PV/Adjust software creates data log files (.dlf files) that store program data. The .dlf files are used by the PV/Adjust software to generate the view data and print out options. Each .dlf file is identified by the product serial number; for example, B010100.dlf. The files are stored in the Tekcats folder under each TLA7xx folder. To conserve disk space, you must occasionally delete the .dlf files.

# **TLA600 Series Logic Analyzer**

### **TLA600 Series Logic Analyzer Functional Verification**

This section contains instructions for performing the functional verification procedure. This procedure provides an easy way to check the basic functionality of the TLA600 Series Logic Analyzer.

### **Tests Performed**

Table 2–1 lists the functional verification procedures that are available for the TLA600 Logic Analyzer and probes.

Table 2–1: TLA600 Functional verification procedures

| Instrument                                   | Procedure             | Adjustment/verification fixture required |

|----------------------------------------------|-----------------------|------------------------------------------|

| Logic Analyzer                               | Power-up diagnostics  | No                                       |

| Logic Analyzer                               | Extended diagnostics  | No                                       |

| Logic Analyzer                               | Mainframe diagnostics | No                                       |

| Logic Analyzer                               | QA+Win32 diagnostics  | No                                       |

| P6417, P6418, or P6434 logic analyzer probes | Signal Input check    | Yes                                      |

**NOTE**. Running the extended diagnostics will invalidate any acquired data. If you want to save any of the acquired data, do so before running the extended diagnostics.

If any check within this section fails, refer to the *TLA600 Series Logic Analyzer Service Manual* for corrective action.

The functional verification procedure consists of the following parts:

- Module self tests and power-on diagnostics

- Probe verification

This procedure provides a functional check only. If more detailed testing is required, perform the *Performance Verification Procedure* after completing this procedure.

### **Test Procedure**

You will need a TLA600 Series Logic Analyzer to complete this test procedure.

| Equipment required | Cable, 50 $\Omega$ coaxial (item 31) |

|--------------------|--------------------------------------|

| Prerequisites      | Warm-up time: 30 minutes             |

Perform the following tests to complete the functional verification procedure.

#### **Extended Diagnostics**

Do the following steps to run the extended diagnostics:

**NOTE**. Perform the following steps to complete the functional verification procedures. Before beginning this procedure, be sure that no active signals are applied to the logic analyzer. Certain diagnostic tests will fail if signals are applied to the probe during the test.

- 1. Power on the instrument and wait for the system application to start.

- 2. Go to the System menu and select Calibration and Diagnostics.

- **3.** Verify that all power-on diagnostics pass.

- 4. Click the Extended Diagnostics tab.

- **5.** Select All Modules, All Tests (top line) and click the Run button on the property sheet.

The diagnostics software performs each one of the tests listed in the menu under the module selection. All tests that displayed an Unknown status will change to a Pass or Fail status depending on the outcome of the tests.

**6.** Scroll through the test results for the instrument and verify that all tests pass.

**NOTE**. If Extended Diagnostics fail, run Self Cal for the logic analyzer and then rerun Extended Diagnostics.

#### **Mainframe Diagnostics**

The TLA Mainframe Diagnostics check the functionality of the instrument. To run these diagnostics, do the following steps:

- 1. Turn off all other applications.

- 2. Click the Windows Start button.

- **3.** Select Programs from the Start menu.

- **4.** Select Tektronix Logic Analyzer from the Programs menu.

- **5.** Select Tektronix TLA Mainframe Diagnostics from the Tektronix Logic Analyzer menu.

- **6.** Run the mainframe diagnostics. Connect the BNC cable when requested.

When the TLA Mainframe Diagnostics are run, a Mainframe Diagnostics Warning dialog box appears. Clicking OK will initiate a SYSRESET, which will invalidate any acquired data.

#### QA+Win32

QA+Win32 is a comprehensive software application used to check and verify the operation of the PC hardware in the instrument. To run QA+Win32, you must have either a working keyboard or a working mouse or other pointing device and have Windows running.