# **Technical Reference**

# **Tektronix**

DTG5078 & DTG5274

Data Timing Generators

Performance Verification & Specifications

071-1280-02

This document supports firmware version 1.0.14 and above.

Copyright © Tektronix Japan, Ltd. All rights reserved.

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix Japan, Ltd. 5-9-31 Kitashinagawa, Shinagawa-ku, Tokyo 141-0001 Japan

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077-0001

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

|                       | List of Figures                 | ii                                |

|-----------------------|---------------------------------|-----------------------------------|

|                       | List of Tables                  | iii                               |

|                       | General Safety Summary          | v                                 |

|                       | Preface                         | <b>vi</b> i<br>vii<br>vii<br>viii |

| Performance Veri      | -                               |                                   |

|                       | Conventions in this manual      | 1-1                               |

|                       | Self Tests                      | 1-3                               |

|                       | Performance Tests               | 1-10                              |

|                       | Mainframe                       | 1-15                              |

|                       | Output Module                   | 1-62                              |

| <b>Specifications</b> |                                 |                                   |

|                       | Product and Feature Description | 2-1                               |

|                       | Electrical Specification        | 2-3                               |

|                       | Miscellaneous                   | 2-32                              |

# **List of Figures**

| Figure 1-1: Diagnostics dialog                      | 1-4  |

|-----------------------------------------------------|------|

| Figure 1-2: Level Calibration dialog                | 1-6  |

| Figure 1-3: Skew Calibration dialog                 | 1-8  |

| Figure 1-4: Skew Calibration results screen         | 1-9  |

| Figure 1-5: Open Setup dialog                       | 1-13 |

| Figure 1-6: Sync output tests                       | 1-16 |

| Figure 1-7: Internal Clock Frequency tests          | 1-18 |

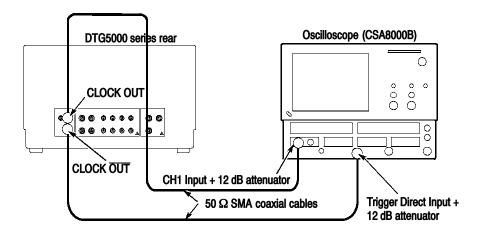

| Figure 1-8: External Clock Output tests             | 1-20 |

| Figure 1-9: External Clock Input tests              | 1-23 |

| Figure 1-10: 10 MHz Reference Input tests           | 1-25 |

| Figure 1-11: 10 MHz Reference Output tests          | 1-27 |

| Figure 1-12: Phase Lock Input tests                 | 1-28 |

| Figure 1-13: Internal Trigger tests                 | 1-30 |

| Figure 1-14: Event Input and Sequence tests         | 1-34 |

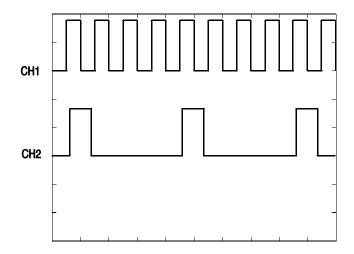

| Figure 1-15: Data pattern example                   | 1-36 |

| Figure 1-16: Jitter Generation tests                | 1-38 |

| Figure 1-17: Jitter Generation example (all)        | 1-39 |

| Figure 1-18: Jitter Generation example (partial)    | 1-41 |

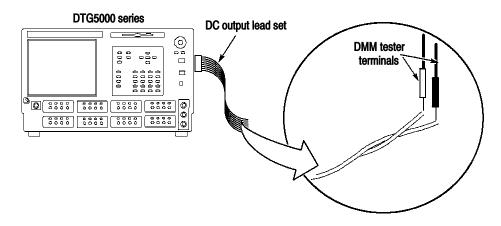

| Figure 1-19: DC Output tests                        | 1-42 |

| Figure 1-20: Delay timing tests                     | 1-44 |

| Figure 1-21: Clock out random jitter tests          | 1-48 |

| Figure 1-22: Clock out random jitter sample         | 1-49 |

| Figure 1-23: Random jitter tests                    | 1-50 |

| Figure 1-24: Random jitter waveform sample          | 1-52 |

| Figure 1-25: Total jitter waveform sample           | 1-54 |

| Figure 1-26: PG Mode tests                          | 1-55 |

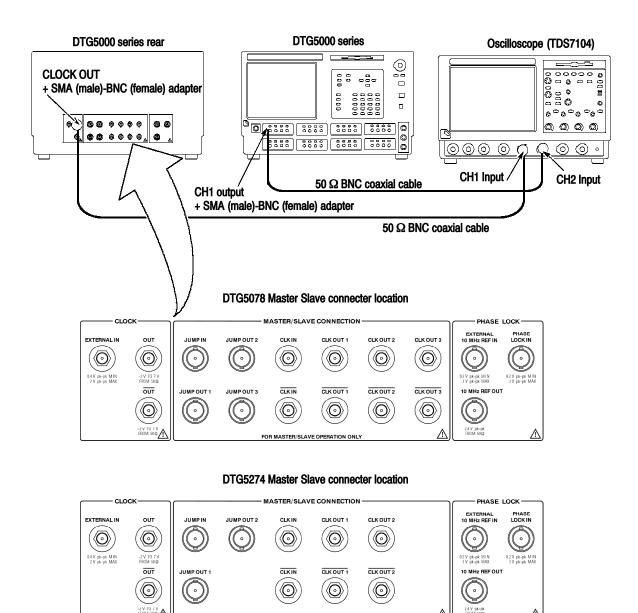

| Figure 1-27: Master-Slave operation tests           | 1-58 |

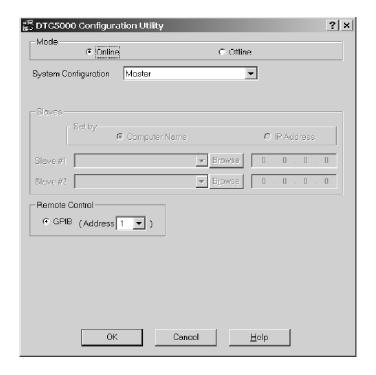

| Figure 1-28: DTG5000 Configuration Utility dialog   | 1-59 |

| Figure 1-29: Master-Slave operation waveform sample | 1-60 |

| Figure 1-30: Data output DC level tests             | 1-63 |

| Figure 1-31: Data format tests                      | 1-67 |

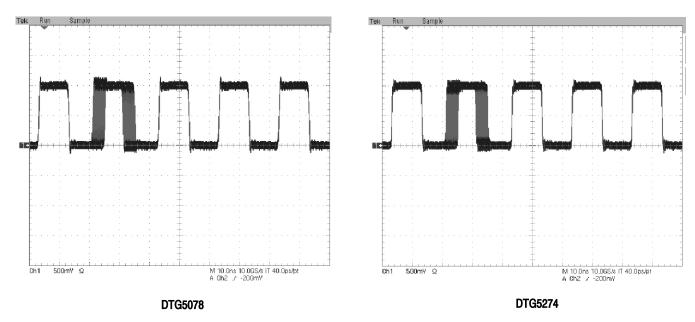

| Figure 1-32: Pulse pattern example                  | 1-68 |

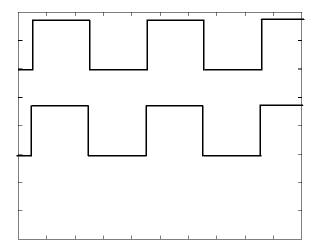

| Figure 1-33: RZ waveform example                    | 1-69 |

| Figure 1-34: R1 waveform example                    | 1-69 |

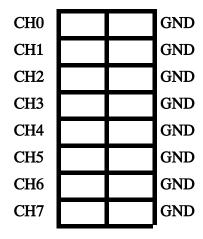

| Figure 2-1: DC Output channel assignment                        | 2-5  |

|-----------------------------------------------------------------|------|

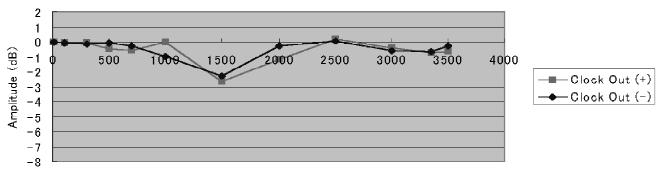

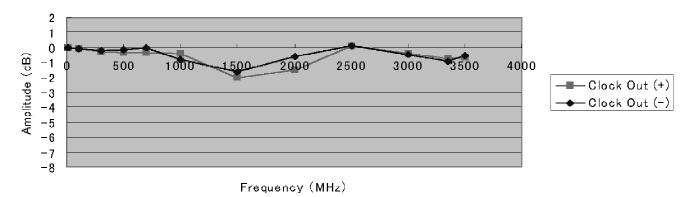

| Figure 2-2: Frequency response of clock output                  | 2-7  |

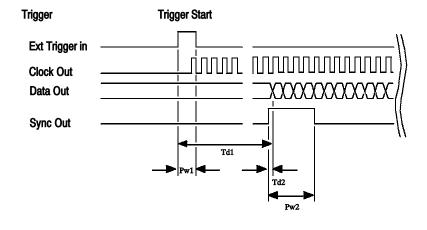

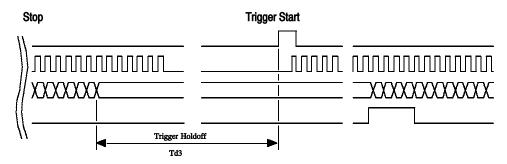

| Figure 2-3: Signal timing                                       | 2-12 |

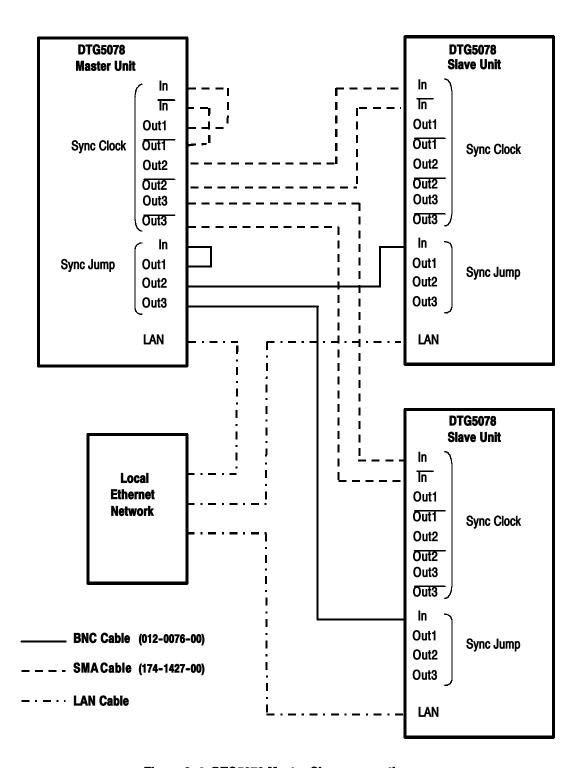

| Figure 2-4: DTG5078 Master-Slave connection                     | 2-13 |

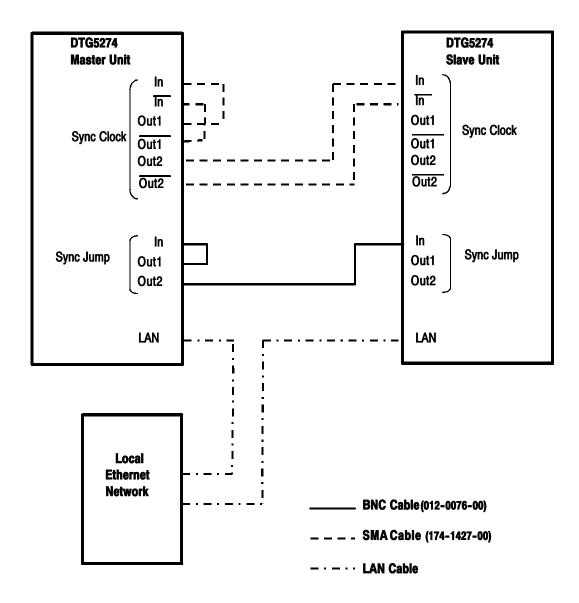

| Figure 2-5: DTG5274 Master-Slave connection                     | 2-14 |

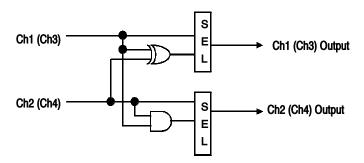

| Figure 2-6: Channel addition function                           | 2-21 |

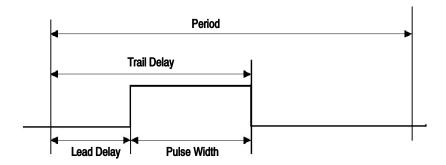

| Figure 2-7: The definitions of Lead/Trail Delay and Pulse Width | 2-22 |

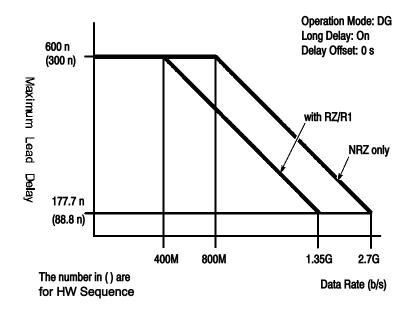

| Figure 2-8: Maximum Lead Delay                                  | 2-22 |

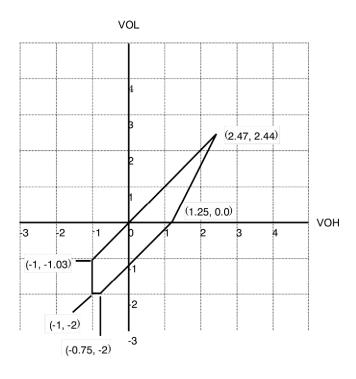

| Figure 2-9: Output voltage window and clock out (DTGM30)        | 2-30 |

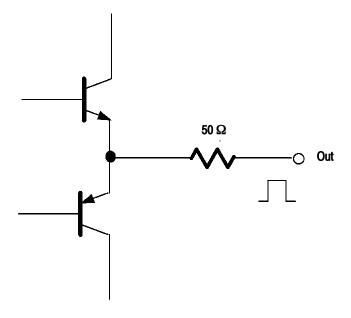

| Figure 2-10: Equivalent circuit of DTGM10 and DTGM20 outputs    | 2-31 |

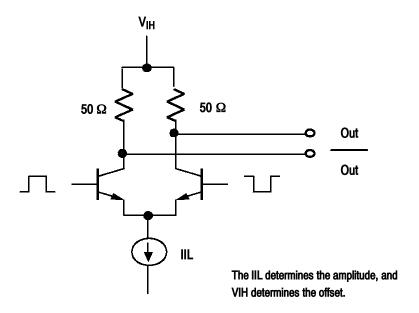

| Figure 2-11: Equivalent circuit of DTGM30 output                | 2-31 |

# **List of Tables**

| Table 1-1: Performance test items                | 1-10 |

|--------------------------------------------------|------|

| Table 1-2: Test equipment                        | 1-11 |

| Table 1-3: Performance check files               | 1-14 |

| Table 1-4: DTGM10 High Level Voltage Accuracy    | 1-64 |

| Table 1-5: DTGM10 Low Level Voltage Accuracy     | 1-64 |

| Table 1-6: DTGM20 High Level Voltage Accuracy    | 1-64 |

| Table 1-7: DTGM20 Low Level Voltage Accuracy     | 1-65 |

| Table 1-8: DTGM30 High Level Voltage Accuracy    | 1-66 |

| Table 1-9: DTGM30 Low Level Voltage Accuracy     | 1-66 |

| Table 2-1: DTG5000 Series Data Timing Generators | 2-1  |

| Table 2-2: Operation mode                        | 2-3  |

| Table 2-3: Sequencer                             | 2-3  |

| Table 2-4: Clock Generator                       | 2-4  |

| Table 2-5: Internal Trigger Generator            | 2-4  |

| Table 2-6: DC Output                             | 2-4  |

| Table 2-7: Clock Out                             | 2-5  |

| Table 2-8: External Clock In                     | 2-7  |

| Table 2-9: 10 MHz Reference In                   | 2-8  |

| Table 2-10: 10 MHz Reference Out                 | 2-8  |

| Table 2-11: Phase Lock In                        | 2-8  |

| Table 2-12: Skew Cal In                                | 2-9  |

|--------------------------------------------------------|------|

| Table 2-13: Trigger In                                 | 2-9  |

| Table 2-14: Sync Out                                   | 2-10 |

| Table 2-15: Sync Clock In                              | 2-10 |

| Table 2-16: Sync Clock Out 1, Out 2 and Out 3          | 2-10 |

| Table 2-17: Sync Jump In                               | 2-11 |

| Table 2-18: Sync Jump Out 1, Out 2 and Out 3           | 2-11 |

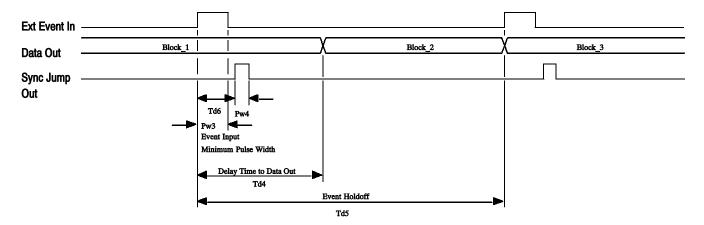

| Table 2-19: Event In                                   | 2-14 |

| Table 2-20: CPU module and peripheral devices          | 2-15 |

| Table 2-21: Display                                    | 2-16 |

| Table 2-22: DG Mode                                    | 2-16 |

| Table 2-23: Clock Range in NRZ                         | 2-20 |

| Table 2-24: Clock Range in RZ/R1                       | 2-21 |

| Table 2-25: Delay Offset                               | 2-21 |

| Table 2-26: Lead Delay                                 | 2-23 |

| Table 2-27: Trail Delay                                | 2-23 |

| Table 2-28: Jitter Amplitude                           | 2-24 |

| Table 2-29: PG Mode                                    | 2-25 |

| Table 2-30: DTGM10                                     | 2-27 |

| Table 2-31: DTGM20                                     | 2-28 |

| Table 2-32: DTGM30                                     | 2-29 |

| Table 2-33: Mechanical                                 | 2-32 |

| Table 2-34: Installation requirement                   | 2-33 |

| Table 2-35: Environmental                              | 2-33 |

| Table 2-36: Power Supply                               | 2-34 |

| Table 2-37: Certifications and compliances             | 2-35 |

| Table 2-38: Installation category and Pollution degree | 2-36 |

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

## To Avoid Fire or Personal Injury

**Use Proper Power Cord.** Use only the power cord specified for this product and certified for the country of use.

**Ground the Product.** This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

The common terminal is at ground potential. Do not connect the common terminal to elevated voltages.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

**Do Not Operate Without Covers.** Do not operate this product with covers or panels removed.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

Do Not Operate With Suspected Failures. If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

**Keep Product Surfaces Clean and Dry.**

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

### **Symbols and Terms**

Terms in this Manual. These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

WARNING High Voltage

Protective Ground (Earth) Terminal

CAUTION Refer to Manual

Double Insulated

# **Preface**

This manual provides information necessary for users or service technicians to verify the performance of the DTG5000 Series Data Timing Generator.

# **Manual Structure**

The DTG5000 Series Data Timing Generator Technical Reference contains the following sections:

The *Performance Verifications* section contains an introduction, a list of equipment required, and procedures that, when passed, ensure that the product meets its specifications.

The *Specifications* section contains a brief product description and characteristics tables. These tables cover the electrical, mechanical, environmental characteristics and certification.

# **Related Manuals and Online Documents**

This manual is part of a document set of standard-accessory manuals and online documentation; this manual mainly focuses on the performance verification and specifications information needed to verify the product performance. See the following list for other documents supporting the data timing generator operation and service. (Manual part numbers are listed in *Accessories & Options* section of User Manual.)

| Document name                        | Description                                                                                                                                                            |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTG5000 Series Online Help           | An online help system, integrated with the User Interface application that ships with this product. The help is preinstalled in the instrument.                        |

| DTG5000 Series User Manual, volume 1 | A quick reference to major features of the instrument and how they operate. It also provides several tutorials to familiarize the user with basic instrument features. |

| DTG5000 Series User Manual, volume 2 | A comprehensive usage information on how to operate the instrument including the descriptions of functions and menu operations.                                        |

| DTG5000 Series Programmer Manual     | Provides complete information on programming commands and remote control of the instrument.                                                                            |

| DTG5000 Series Service Manual        | Describes how to service the instrument to the module level. This optional manual must be ordered separately.                                                          |

# **Contacting Tektronix**

Phone 1-800-833-9200\*

Address Tektronix, Inc.

Department or name (if known) 14200 SW Karl Braun Drive

P.O. Box 500 Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1\*

Service support 1-800-833-9200, select option 2\*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3\* 6:00 a.m. - 5:00 p.m. Pacific time

<sup>\*</sup> This phone number is toll free in North America. After office hours, please leave a voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

# **Performance Verification**

Two types of Performance Verification procedures can be performed on this product: *Self Tests* and *Performance Tests*. You may not need to perform all of these procedures, depending on what you want to accomplish.

■ Verify that the DTG5000 Series Data Timing Generator is operating correctly by running the *Self Tests*, which begin on page 1-3.

Advantages: These procedures require minimal time to perform, and test the internal hardware of the DTG5000 Series Data Timing Generator.

■ If a more extensive confirmation of performance is desired, complete the self tests, and then do the *Performance Tests* beginning on page 1-10.

**Advantages:** These procedures add direct checking of warranted specifications. These procedures require suitable test equipment and more time to execute. (Refer to *Equipment Required* on page 1-11).

## Conventions in this manual

Throughout these procedures the following conventions apply:

■ Each test procedure uses the following general format:

Title of Test

**Equipment Required**

**Prerequisites**

Procedure

- Each procedure consists of as many steps, substeps, and subparts as required to do the test. Steps, substeps, and subparts are sequenced as follows:

- 1. First Step

- a. First Substep

- First Subpart

- Second Subpart

- **b.** Second Substep

- 2. Second Step

Where instructed to use a control in the display or a front-panel button or knob, the name of the control, button or knob appears in boldface type.

#### **Menu Selections**

Instructions for menu selection use the following format:

Menu button→Left or right Allow button (by using this button, you can move to desired menu category)→Upper or down Allow button (by using this button, you can move to desired menu item)→SELECT or Enter key (this completes the selection).

You can use a mouse as a pointer, use keyboard shortcuts for quick operation, or use front panel knob instead of sticking to above menu selection format.

#### **User Manual**

The DTG5078 & DTG5274 Data Timing Generators User Manual is strongly recommended to familiarize the first-time user with instrument controls and features.

#### **Install the Output Modules**

Any output modules ordered are shipped separately. For complete instructions on how to install the output modules, refer to the User Manual. (Output modules do not ship preinstalled.)

**CAUTION.** Do not install or remove any output modules while the instrument is powered on.

Always power the instrument down before attempting to remove or install any output module.

## **Self Tests**

There are two types of tests in this section that provide a quick way to confirm basic functionality and proper adjustment:

- Diagnostics

- Calibration (You must perform this calibration before the performance tests.)

These procedures use internal diagnostics to verify that the instrument passes the internal circuit tests, and calibration routines to check and adjust the instrument internal calibration constants.

**NOTE**. To perform the Self Tests, at least one output module (DTGM10, DTGM20, or DTGM30) must be installed in the DTG5000 series Data Timing Generator mainframe. You can select any slot when you perform the tests even though the descriptions below are assuming the Slot A is used.

## **Diagnostics**

This procedure uses internal routines to verify that the instrument is operating correctly. No test equipment or hookups are required.

The instrument automatically performs the internal diagnostics when powered on; you can also run the internal diagnostics using the menu selections described in this procedure. The difference between these two methods of initiating the diagnostics is that the menu method does a more detailed memory check than the power-on method.

Do the following steps to run the internal routines that confirm basic functionality and proper adjustment.

| Equipment required | None                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------|

| Prerequisites      | First, at least one output module must be installed properly in the mainframe.                |

|                    | Second, power on the instrument and allow a twenty-minute warmup before doing this procedure. |

#### 1. Set up the instrument:

Confirm that there is no output being performed by verifying that the RUN button indicator is not on. If the indicator is on, push the RUN button to turn it off.

- Verify that the output module LEDs are not on. If any output module LEDs are on, push the ALL OUTPUTS ON/OFF button to turn the LEDs off.

- 2. Internal diagnostics: Perform these substeps to verify internal diagnostics.

- a. Display the Diagnostics dialog:

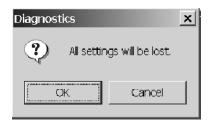

- From the application menu bar, select **System**, and then select **Diagnostics...**. The following dialog appears if you have changed the settings.

■ Select **OK** to display the Diagnostics dialog. See Figure 1-1.

Figure 1-1: Diagnostics dialog

- Verify that the Loop until Fail box is not checked. If it is checked, click the box to remove the check mark.

- Select Execute All Items to start the diagnostics.

- **b.** Wait: The internal diagnostics takes one to six minutes. When complete, the resulting status appears in the diagnostics control window.

- c. Verify that no failures are found and reported: All tests should pass. Confirm that the word **Pass** appears in all the **Status** fields. If any failures occur, record the failure information and contact your local Tektronix service personnel for more information.

- 3. Select Close to exit the diagnostics.

#### **Calibration**

Two types of calibrations are provided in the DTG5000 Series Data Timing Generator.

- The Level Calibration uses internal calibration routines that check electrical characteristics such as DC accuracy of data output, and then adjust the internal calibration constants as necessary.

- The Skew Calibration checks the delay time of data output, and then adjust the internal calibration constants as necessary. The calibration is performed by connecting each channel output to Skew Cal In.

**NOTE**. Level Calibration and Skew Calibration are not valid until the instrument reaches a valid temperature.

#### Level Calibration.

| Equipment required | None                                                                                                                                                                                                                                       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prerequisites      | Power on the instrument and allow a 20 minute warmup at an ambient temperature between +20° C and +30° C before doing this procedure.  The calibration routine must be performed whenever the ambient temperature changes by 5° C or more. |

#### 1. Set up the instrument:

- Confirm that there is no output being performed by verifying that the RUN button indicator is not on. If the indicator is on, push the RUN button to turn it off.

- Verify that the output module LEDs are not on. If any output module LEDs are on, push the ALL OUTPUTS ON/OFF button to turn the LEDs off.

#### 2. Perform the calibration suite:

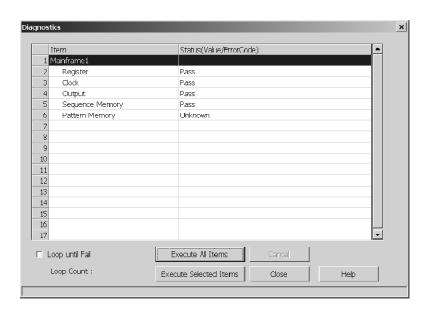

a. From the application menu bar, select **System**, and then select **Level** Calibration.... The Level Calibration dialog appears. See Figure 1-2.

Figure 1-2: Level Calibration dialog

- b. Select Execute.

- c. All the Status fields must be **Pass**. If any failures occur, record the failure information and contact your local Tektronix service personnel for more information.

- 3. Select Close to exit the calibration.

#### **Skew Calibration.**

| Equipment required | One 50 $\Omega$ SMA coaxial cable, Tektronix part number 174-1427-00 Refer to test equipment list on page 1-12.                                                                                                                            |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Prerequisites      | Power on the instrument and allow a 20 minute warmup at an ambient temperature between +20° C and +30° C before doing this procedure.  The calibration routine must be performed whenever the ambient temperature changes by 5° C or more. |  |

|                    |                                                                                                                                                                                                                                            |  |

#### 1. Set up the instrument:

- Confirm that there is no output being performed by verifying that the RUN button indicator is not on. If the indicator is on, push the RUN button to turn it off.

- Verify that the output module LEDs are not on. If any output module LEDs are on, push the ALL OUTPUTS ON/OFF button to turn the LEDs off.

#### 2. Perform the calibration suite:

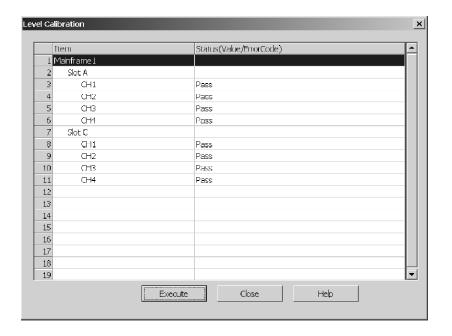

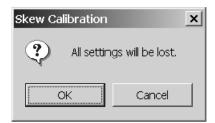

**a.** From the application menu bar, select **System**, and then select **Skew Calibration**. The following dialog appears if you have changed the settings. Click **OK**.

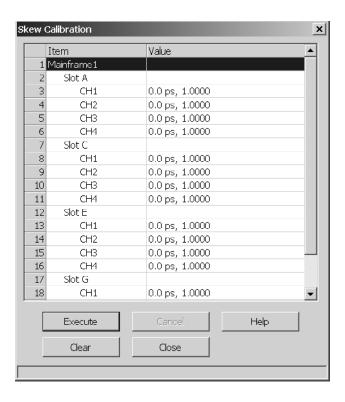

**b.** The Skew Calibration dialog appears. See Figure 1-3.

Figure 1-3: Skew Calibration dialog

- c. Attach an SMA coaxial cable to the SKEW CAL IN at the front panel of the data timing generator mainframe.

- **d.** Select **Execute** to display the dialog box shown below.

- e. Connect the opposite end of the SMA coaxial cable to the CH1 connector of output module and select **OK** to start the calibration. Wait until the calibration completes.

- **f.** Follow the on-screen instruction to continue the calibration:

- Disconnect the cable from the channel and reconnect it to next channel.

Repeat the same calibration procedure for all channels.

**NOTE**. When you connect the output module and Skew Cal In, use the identical cable. If you use different cables, the calibration result may be affected.

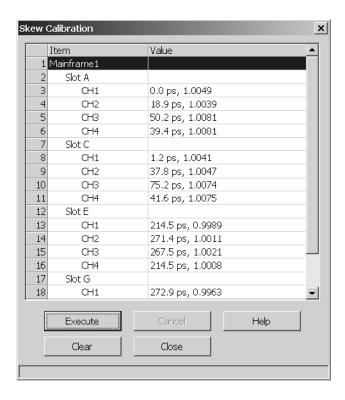

**g.** When complete, the resulting status appears on the screen. See Figure 1-4.

Figure 1-4: Skew Calibration results screen

- h. Verify that no failures are found and reported on the screen.

- i. If any failures occur, record the failure information and contact your local Tektronix service personnel for more information.

- 3. Select Close to exit the calibration.

**NOTE**. The calibration data in the memory may be lost if the instrument is powered off while the calibration is executed.

# **Performance Tests**

The *Performance Tests* include functional test items, such as the interface functional test, in this manual.

- The Functional Tests verify the functions, that is, they verify that the DTG5000 Series Data Timing Generator features operate. They do not verify that they operate within limits.

- The Performance Tests verify that the DTG5000 Series Data Timing Generator performs as warranted. The Performance Tests check all the characteristics that are designated as checked in Specifications. (The characteristics that are checked appear with a in Specifications.)

**Table 1-1: Performance test items**

| itles                                                     | Test items                                                                                 | Reference page |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------|

| TG5000 series mainframe <sup>1</sup>                      |                                                                                            |                |

| Sync output                                               | Output level                                                                               | Page 1-15      |

| Internal clock frequency                                  | Internal clock output frequency accuracy                                                   | Page 1-18      |

| External clock output                                     | External clock output amplitude, rise time/ fall time, and aberration                      | Page 1-20      |

| External clock input                                      | External clock input function and external clock input frequency accuracy                  | Page 1-22      |

| 10 MHz reference input                                    | 10 MHz reference input function                                                            | Page 1-25      |

| 10 MHz reference output                                   | 10 MHz reference output frequency and output level                                         | Page 1-26      |

| Phase lock input                                          | Phase lock input function                                                                  | Page 1-28      |

| Internal automatic trigger Internal auto trigger function |                                                                                            | Page 1-30      |

| Trigger input                                             | Trigger input function                                                                     |                |

| Event input and sequence function                         | Event input function, jump out function for master-slave operation, and sequence operation | Page 1-33      |

| All jitter generation                                     | Jitter profile and jitter volume                                                           | Page 1-38      |

| Partial jitter generation                                 | Jitter profile and jitter volume                                                           | Page 1-40      |

| DC output                                                 | DC output accuracy                                                                         | Page 1-42      |

| Skew and delay timing                                     | Skew time between channels (after skew calibration)                                        | Page 1-44      |

| Clock out random jitter                                   | Clock out random jitter                                                                    | Page 1-47      |

| Random jitter                                             | Random jitter                                                                              | Page 1-50      |

| Total jitter                                              | Total jitter                                                                               | Page 1-53      |

| PG Mode                                                   | Frequency, Duty, and Mode                                                                  | Page 1-54      |

| Master-Slave operation                                    | Master-Slave operation                                                                     | Page 1-57      |

Table 1-1: Performance test items (cont.)

| Titles               | Test items            | Reference page |

|----------------------|-----------------------|----------------|

| Output module        |                       |                |

| Data output DC level | Output level accuracy | Page 1-62      |

| Data format          | NRZ, RZ, and NRI      | Page 1-67      |

At least one output module, which operates correctly, must be installed into the DTG5000 series mainframe slot when you execute the performance tests.

### **Prerequisites**

The tests in this section comprise an extensive, valid confirmation of performance and functionality when the following requirements are met:

- The cabinet must be installed on the instrument.

- Allow 20 minutes warm up period.

- You must have performed and passed the procedures under *Self Tests*, found on page 1-3.

- The data timing generator must have been last adjusted at an ambient temperature between +20° C and +30° C, and must have been operating for a warm-up period of at least 20 minutes.

- The *Performance Tests* must be executed at an ambient temperature between +10° C and +40° C.

#### **Equipment Required**

Table 1-2 lists the required equipment used to complete the performance tests.

Table 1-2: Test equipment

| Item number and description |                       | Minimum requirements Recommended equipment or equivalent                        |                                           | uipment Purpose                                                                  |

|-----------------------------|-----------------------|---------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------|

| 1.                          | Frequency Counter     | 50 kHz to 5 GHz,<br>Accuracy: < 0.2 ppm                                         | Agilent 53181A op.050/010                 | Checks clock frequency.                                                          |

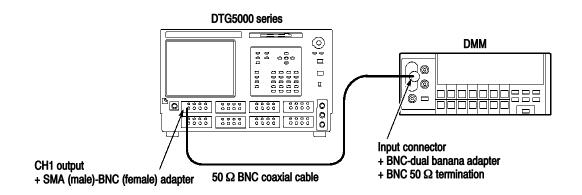

| 2.                          | Digital Multi Meter   | DC volts range: - 10 V to +10 V,<br>Accuracy: ±1%                               | Fluke 8842A                               | Measures voltage. Used in multiple procedures.                                   |

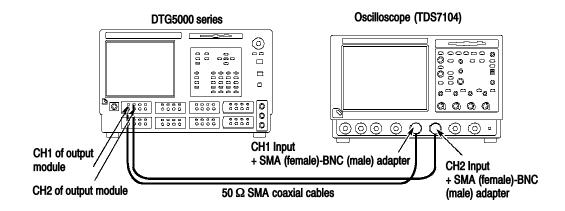

| 3.                          | Oscilloscope          | Bandwidth: > 1 GHz, Number of channel: > 4, 1 M $\Omega$ and 50 $\Omega$ inputs | Tektronix TDS7104                         | Checks output signals. Used in multiple procedures.                              |

| 4.                          | Sampling Oscilloscope | Bandwidth: $>$ 20 GHz,<br>Rise time: $<$ 17.5 ps, 50 $\Omega$ input             | Tektronix CSA8000B,<br>80E03 <sup>2</sup> | Checks output signals. Used in multiple procedures.                              |

| 5.                          | Function Generator    | Output voltage: -5 V to +5 V,<br>Frequency accuracy: < 0.01%                    | Tektronix AFG320                          | Generates external input signals. Used in multiple input signal test procedures. |

Table 1-2: Test equipment (cont.)

| Item number and description Minimum requirements |                                | Minimum requirements                       | Recommended equipment or equivalent  | Purpose                |

|--------------------------------------------------|--------------------------------|--------------------------------------------|--------------------------------------|------------------------|

| 6.                                               | SMA Coaxial Cable (3 required) | 50 $\Omega$ , male to male SMA connector   | Tektronix part number 174-1427-00    | Signal interconnection |

| 7.                                               | BNC Coaxial Cable (3 required) | 50 $\Omega$ , male to male BNC connector   | Tektronix part number 012-0076-00    | Signal interconnection |

| 8.                                               | Adapter<br>(2 required)        | SMA (male) to BNC (female), 50 $\Omega$    | Tektronix part number 015-0554-00    | Signal interconnection |

| 9.                                               | Adapter<br>(2 required)        | SMA (female) to BNC (male), 50 $\Omega$    | Tektronix part number 015-0572-00    | Signal interconnection |

| 10.                                              | Adapter                        | N (male) to SMA (male), 50 $\Omega$        | Tektronix part number 015-0369-00    | Signal interconnection |

| 11.                                              | Adapter                        | SMA (female) to SMA (female), 50 $\Omega$  | Tektronix part number 015-1012-00    | Signal interconnection |

| 12.                                              | Lead set for DC output         | 16-CON twisted pair, 60 cm (24in)          | Tektronix part number 012-A229-00    | Signal interconnection |

| 13.                                              | Dual-Banana Plug               | BNC (female) to dual banana                | Tektronix part number<br>103-0090-00 | Signal interconnection |

| 14.                                              | BNC-T Connector                | BNC (male) to BNC (female) to BNC (female) | Tektronix part number<br>103-0030-00 | Signal interconnection |

| 15.                                              | Feed-through Termina-<br>tion  | 50 Ω, 0.1%, BNC                            | Tektronix part number 011-0129-00    | Signal termination     |

| 16.                                              | SMA Termination                | 50 Ω, SMA                                  | Tektronix part number 015-0706-00    | Signal termination     |

| 17.                                              | Attenuator<br>(2 required)     | 12 dB, SMA                                 |                                      | Signal attenuation     |

For best repeatability and to prolong the life of both connectors, use a torque wrench (5/16 in) and tighten the connection to the range of 7-10 lb-in (79-112 N-cm) when you connect an SMA cable to a sampling module. For more information, refer to your sampling module user manual.

**CAUTION.** Sampling modules are inherently vulnerable to static damage. Always observe static-safe procedures and cautions as outlined in the sampling module user manual.

## **Loading Files**

The following steps explain how to load files from the DTG5000 Series Data Timing Generator.

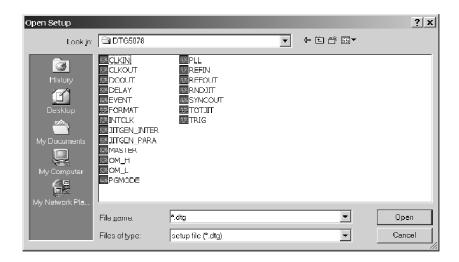

- 1. From the application menu bar, select File, and then select Open Setup. The Open Setup dialog appears. See Figure 1-5.

- 2. Specify C:\Program Files\Tektronix\DTG5000\PV\DTG5078 (or C:\Program Files\Tektronix\DTG5000\PV\DTG5274) to Look in field.

Figure 1-5: Open Setup dialog

- 3. Select the necessary file in the File name:, and then click Open.

- 4. The Open Setup Dialog automatically disappears, and then the selected waveform and sequence file are loaded.

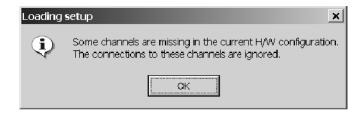

If your data timing generator mainframe is not equipped with maximum output module configuration, the following dialog box appears.

5. Click **OK** to complete the instrument setup.

### **Performance Check Files**

Table 1-3 lists the setup files on the internal hard disk drive that are used in these performance tests. A specified file must be loaded each time you execute Performance Test procedure. Test pattern data and setup information are included in the file.

Table 1-3: Performance check files

| No. | File name        | Clock frequency                                            | Test item                           |

|-----|------------------|------------------------------------------------------------|-------------------------------------|

| 1   | SYNCOUT.dtg      | Internal: 10 MHz                                           | Sync output                         |

| 2   | INTCLK.dtg       | Internal: 100 MHz                                          | Internal clock frequency            |

| 3   | CLKOUT.dtg       | Internal: 10 MHz                                           | External clock output               |

| 4   | CLKIN.dtg        | External clock: 10 MHz                                     | External clock input                |

| 5   | REFIN.dtg        | External reference: 100 MHz                                | 10 MHz reference                    |

| 6   | PLLdtg           | External PLL: 10 MHz                                       | Phase lock input                    |

| 7   | TRIG.dtg         | Internal: 2.7 GHz (DTG5274)<br>Internal: 750 MHz (DTG5078) | Trigger input                       |

| 8   | EVENT.dtg        | Internal: 2.7 GHz (DTG5274)<br>Internal: 750 MHz (DTG5078) | Event input and sequential function |

| 9   | JITGEN_INTER.dtg | Internal: 100 MHz                                          | Total jitter                        |

| 10  | JITGEN_PARA.dtg  | Internal: 100 MHz                                          | Partial jitter                      |

| 11  | DCOUT.dtg        |                                                            |                                     |

| 12  | REFOUT.dtg       | Internal: 100 MHz                                          | 10 MHz reference output             |

| 13  | DELAY.dtg        |                                                            |                                     |

| 14  | PGMODE.dtg       | Internal: 100 MHz                                          | PG mode                             |

| 15  | OM_H.dtg         |                                                            |                                     |

| 16  | OM_L.dtg         |                                                            |                                     |

| 17  | FORMAT.dtg       | Internal: 10 MHz                                           | Data format                         |

| 18  | MASTER.dtg       | Internal: 20 MHz                                           | Master-Slave operation              |

| 19  | RNDJIT.dtg       |                                                            | Random jitter                       |

| 20  | TOTJIT.dtg       |                                                            | Total jitter                        |

# **Mainframe**

The following procedures check those characteristics that relate to the mainframe that are checked under *Mainframe* in *Specifications*. Refer to page 2-3.

**NOTE**. To perform the Performance Tests, at least one output module must be installed in the DTG5000 Series Data Timing Generator mainframe. You can select any slot when you perform the tests even though the descriptions below are assuming the Slot A is used.

#### **Sync Output**

This test verifies that the DTG5000 series mainframe sync output is functional.

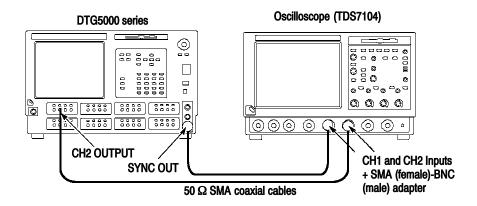

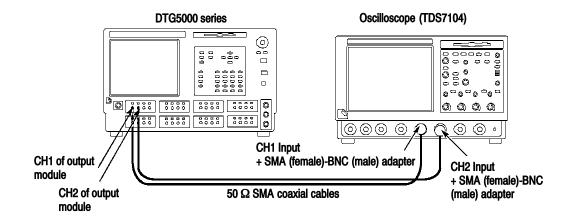

| Equipment     | One oscilloscope (TDS7104) (item 3)                                                       |

|---------------|-------------------------------------------------------------------------------------------|

| required      | Two 50 $\Omega$ SMA coaxial cables (item 6)                                               |

|               | Two SMA (female)-BNC (male) adapters (item 9)                                             |

| Prerequisites | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11. |

- 1. Install the test hookup and preset the instrument controls:

- **a.** Hook up the oscilloscope:

- Attach SMA (female)-BNC (male) adapters to the oscilloscope CH1 input and CH2 input connectors.

- Connect an SMA coaxial cable from the CH2 connector of output module, which is inserted in the slot A of DTG5000 series mainframe, to the SMA-BNC adapter (CH2 input of oscilloscope).

- Connect an SMA coaxial cable from the SYNC OUT at the front panel of the DTG5000 series mainframe to the SMA-BNC adapter (CH1 input of the oscilloscope). See Figure 1-6.

Figure 1-6: Sync output tests

**b.** Set the oscilloscope controls as follows:

| Vertical .                  |                     |

|-----------------------------|---------------------|

| CH1 and CH2 coupling        | DC                  |

| CH1 scale                   | 100 mV/div          |

| CH2 scale                   | 200 mV/div          |

| CH1 and CH2 input impedance | 50 Ω                |

| CH1 offset                  | -200 mV             |

| Horizontal                  |                     |

| Scale                       | 100 ns/div          |

| Acquisition                 |                     |

| Mode                        | Average             |

| Number of running averages  | 32                  |

| Trigger                     |                     |

| Source                      | CH2                 |

| Coupling                    | DC                  |

| Slope                       | <b>Positive</b>     |

| Level                       | 500 mV              |

| Mode                        | Auto                |

| Measurement                 | CH1 High<br>CH1 Low |

- 2. Set the data timing generator controls and load the setup file:

- **a.** Load the setup file (SYNCOUT.dtg). Refer to *Loading Files* on page 1-13.

- **b.** After the file is loaded, the **Frequency** of data timing generator is set to 10MHz.

- 3. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- **4.** Confirm the oscilloscope screen: Verify that the 400 ns width square waveform appears in the CH1 display.

- 5. Using the oscilloscope Measurement functions, verify that the High Level and Low Level values of Sync Out are within the following range.

■ High Level:  $0 \text{ V} \pm 50 \text{ mV}$

■ Low Level:  $-0.4 \text{ V} \pm 50 \text{ mV}$

## **Internal Clock Frequency**

This test verifies the frequency accuracy of internal clock.

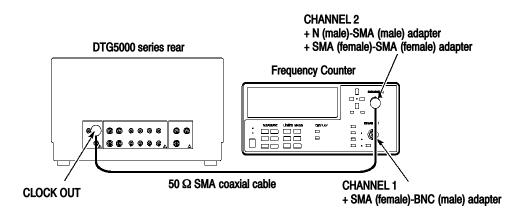

| Equipment required | One frequency counter (item 1) One 50 Ω SMA coaxial cable (item 6) One SMA (female) - BNC (male) adapter (item 9) One N (male) - SMA (male) adapter (item 10) |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | One SMA (female) - SMA (female) adapter (item 11)                                                                                                             |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11.                                                                     |

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the frequency counter:

- Attach an SMA (female)-BNC (male) adapter to the CHANNEL 1 input of frequency counter.

- Attach a N (male)-SMA (male) adapter to the CHANNEL 2 input of frequency counter, and then attach an SMA (female)-SMA (female) adapter to the N-SMA adapter.

- Connect an SMA coaxial cable from the CLOCK OUT at the rear panel of DTG5000 series mainframe through the SMA-SMA and N-SMA adapters to the frequency counter CHANNEL 2 input. See Figure 1-7.

Figure 1-7: Internal Clock Frequency tests

**b.** Power on the frequency counter, and verify that the frequency counter is set to frequency measurement mode (default setting).

- 2. Load the setup file (INTCLK.dtg). Refer to Loading Files on page 1-13.

- 3. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- 4. Set the frequency counter trigger to an appropriate value, and then verify that the frequency counter reading is between 99.9999 MHz and 100.0001 MHz.

- 5. From the application menu bar, select **Settings**, and then select **Timing**.

- **6.** Move cursor to **Clock Frequency** with the TAB key, and then set frequency counter as follows.

#### **DTG5078**

| Setup frequency | Range                          | Frequency counter input |

|-----------------|--------------------------------|-------------------------|

| 750.00000 MHz   | 745.99925 MHz to 750.00075 MHz | CHANNEL 2               |

| 500.00000 MHz   | 499.99950 MHz to 500.00050 MHz | CHANNEL 2               |

| 499.99999 MHz   | 499.99949 MHz to 500.00049 MHz | CHANNEL 2               |

| 50.000000 kHz   | 49.999950 kHz to 50.000050 kHz | CHANNEL 1               |

#### **DTG5274**

| Setup frequency | Range                            | Frequency counter input |

|-----------------|----------------------------------|-------------------------|

| 3.3500000 GHz   | 3.34999665 GHz to 3.35000335 GHz | CHANNEL 2               |

| 2.7000000 GHz   | 2.699973 GHz to 2.7000027 GHz    | CHANNEL 2               |

| 2.0000000 GHz   | 1.9999980 GHz to 2.0000020 GHz   | CHANNEL 2               |

| 1.9999999 GHz   | 1.9999979 GHz to 2.0000019 GHz   | CHANNEL 2               |

| 50.000000 kHz   | 49.999950 kHz to 50.000050 kHz   | CHANNEL 1               |

7. Verify that the frequency measurements are within the specified range.

**NOTE**. Disconnect the SMA coaxial cable from CHANNEL 2 input and then connect it to CHANNEL 1 input of frequency counter for 50kHz measurements.

#### **External Clock Output**

This test verifies the rise time/fall time and aberration of external clock output.

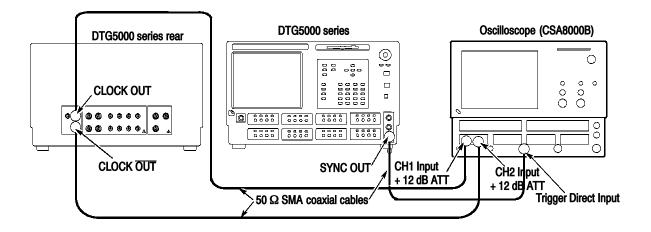

| Equipment required | One sampling oscilloscope with a 80E03 sampling module (item 4) Three 50 $\Omega$ SMA coaxial cables (item 6) |

|--------------------|---------------------------------------------------------------------------------------------------------------|

|                    | Two attenuators (item 17)                                                                                     |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11.                     |

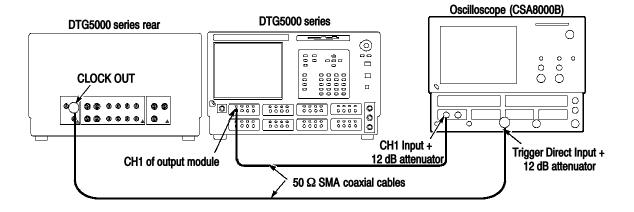

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the oscilloscope:

- Attach the attenuator to **CH1 input** and **CH2 input** of the 80E03 sampling module.

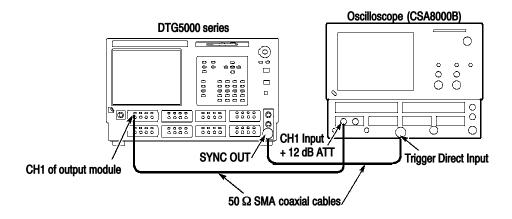

- Connect an SMA coaxial cable from the CLOCK OUT at the rear panel of DTG5000 series mainframe to the CH1 input of the 80E03 sampling module.

- Connect an SMA coaxial cable from the CLOCK OUT at the rear panel of DTG5000 series mainframe to the CH2 input of the 80E03 sampling module.

- Connect an SMA coaxial cable from the SYNC OUT at the front panel of DTG5000 series mainframe to the Trigger Direct Input of sampling oscilloscope. See Figure 1-8.

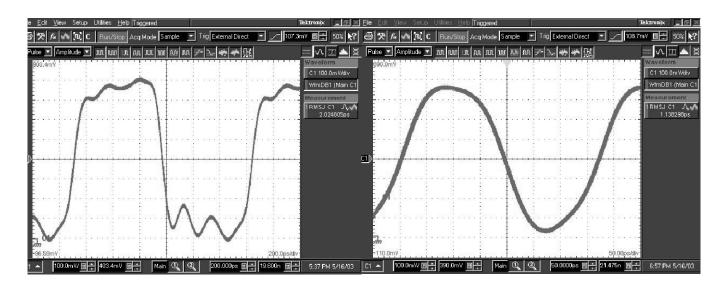

Figure 1-8: External Clock Output tests

**b.** Set the oscilloscope controls as follows:

Vertical

Select Setup -> Vertical -> External

Attenuation, then set 12 dB.

Horizontal

Scale . . . . . . . . . . 2 ns/div

Trigger

Source

External Direct

Slope

Positive

Level

-200 mV

Measurement . . . . . . . . . . . Common to CH1 and CH2

**Amplitude**

Positive Overshoot Negative Overshoot

Rise Time

High Ref = 80%, Low Ref = 20%

Fall Time

High Ref = 80%, Low Ref = 20%

- 2. Load the setup file (CLKOUT.dtg). Refer to Loading Files on page 1-13.

- 3. Push the RUN (front) button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF (front) button to activate the output.

- 4. From the application menu bar, select Settings, and then select Time Base.

- 5. Move cursor to **Amplitude** with the TAB key.

- **6.** Set the **Amplitude** values as shown in the following table.

| Setup value            | Typical value                                                       |                                         |  |

|------------------------|---------------------------------------------------------------------|-----------------------------------------|--|

| Amplitude              | Aberration (Positive Overshoot and Negative Overshoot) <sup>3</sup> | Rise Time and Fall Time <sup>3</sup>    |  |

| 1.000 V <sup>p-p</sup> | <10 %                                                               | < 80 ps (DTG5274)<br>< 100 ps (DTG5078) |  |

| 0.100 V <sub>p-p</sub> |                                                                     | < 70 ps (DTG5274)<br>< 85 ps (DTG5078)  |  |

These are typical values. Typical specifications are provided for user convenience, but are not guaranteed.

- 7. Perform the following measurements for the oscilloscope CH1 input:

- **a.** Verify the aberration: Confirm that the measurement results are approximately the same as stated in the list by observing the rising and falling edges of displayed waveform while adjusting the horizontal position.

- **b.** Verify the rise time: Measure the rise time while observing the rising edge. Confirm that the measurement results are approximately the same values as stated in the list.

- c. Verify the fall time: Measure the fall time while observing the falling edge. Confirm that the measurement results are approximately the same values as stated in the list.

- **d.** Verify the amplitude: Confirm on the oscilloscope screen that the amplitude values are approximately the same level as specified by step 6 above.

- 8. Repeat the same measurements as 7-a through 7-d for the CH2 input.

#### **External Clock Input**

This test verifies the external clock input function and frequency measurement accuracy of the DTG5000 series mainframe.

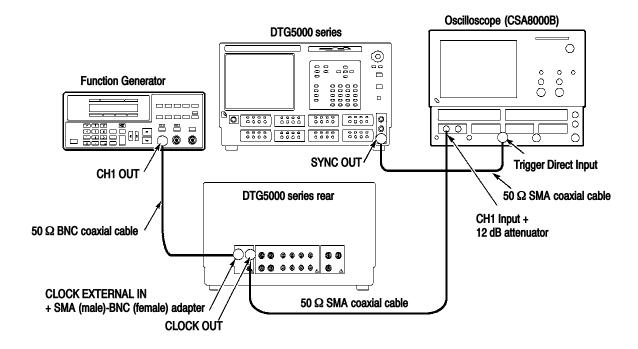

| Equipment required | One sampling oscilloscope with a 80E03 sampling module (item 4) One function generator (item 5) |  |

|--------------------|-------------------------------------------------------------------------------------------------|--|

|                    | Two 50 $\Omega$ SMA coaxial cables (item 6)                                                     |  |

|                    | One 50 $\Omega$ BNC coaxial cable (item 7)                                                      |  |

|                    | One SMA (male)-BNC (female) adapter (item 8)                                                    |  |

|                    | One attenuator (item 17)                                                                        |  |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11.       |  |

- 1. Install the test hookup and preset the instrument controls:

- **a.** Hook up the oscilloscope and function generator:

- Attach the attenuator to **CH1 input** of the 80E03 sampling module.

- Attach an SMA (male)-BNC (female) adapter to the CLOCK

EXTERNAL IN at the rear panel of DTG5000 series mainframe.

- Connect a BNC coaxial cable from the front panel CH1 Out of function generator to the SMA-BNC adapter (Clock External In).

- Connect an SMA coaxial cable from the CLOCK OUT at the rear panel of DTG5000 series mainframe to the CH1 input of the 80E03 sampling module.

- Connect an SMA coaxial cable from the SYNC OUT at the front panel of DTG5000 series mainframe to the Trigger Direct Input of sampling oscilloscope. See Figure 1-9.

Figure 1-9: External Clock Input tests

**b.** Set the oscilloscope controls as follows:

| Vertical   |                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|

| CH1 scale  | 200 mV/div (with 12 dB ATT)<br>Select <b>Setup</b> -> <b>Vertical</b> -> <b>External</b><br><b>Attenuation</b> , then set <b>12 dB</b> . |

| Horizontal |                                                                                                                                          |

| Scale      | 50 ns/div                                                                                                                                |

| Trigger    |                                                                                                                                          |

| Source     | External Direct                                                                                                                          |

| Slope      | Positive                                                                                                                                 |

| Level      | -0.2 V                                                                                                                                   |

c. Set the function generator controls:

$\begin{array}{cccc} \text{Output channel} & & \text{CH1} \\ \text{Function} & & \text{Square} \\ \text{Parameters} & & & \\ \text{Frequency} & & 10 \text{ MHz} \\ \text{Amplitude} & & 1.0 \text{ V into 50 } \Omega \\ \text{Offset} & & 0 \text{ mV} \\ \text{Output} & & \text{Off} \end{array}$

- 2. Load the setup file (CLKIN.dtg). Refer to Loading Files on page 1-13.

- 3. Turn the function generator Output on.

- 4. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- **5.** Verify the displayed waveform: A 10 MHz, approximately 1 Vp-p clock pattern is displayed on the oscilloscope screen.

- **6.** Verify the frequency: Push the **TIMING** button at the front panel of DTG5000 series mainframe and verify that 10.00 MHz (four digits) is displayed at the **Clock Frequency** field.

## 10 MHz Reference Input

This test verifies that the 10 MHz reference input of the DTG5000 series mainframe is functional.

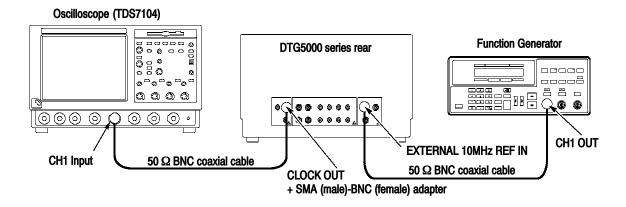

| Equipment required | One oscilloscope (TDS7104) (item 3) One function generator (item 5) Two BNC coaxial cables (item 7) |

|--------------------|-----------------------------------------------------------------------------------------------------|

|                    | One SMA (male)-BNC (female) adapter (item 8)                                                        |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11.           |

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the oscilloscope and function generator:

- Use an SMA (male)-BNC (female) adapter and a BNC coaxial cable to connect the CLOCK OUT at the rear panel of DTG5000 series mainframe and the CH1 input of oscilloscope.

- Connect a BNC coaxial cable from the CH1 Out at the front panel of function generator to the EXTERNAL 10MHz REF IN at the rear panel of DTG5000 series mainframe. See Figure 1-10.

Figure 1-10: 10 MHz Reference Input tests

| Vertical            CH1 scale            CH1 input impedance | -                          |  |

|--------------------------------------------------------------|----------------------------|--|

| Horizontal Scale                                             | 10 ns/div                  |  |

| Trigger SourceSlope                                          | CH1<br>Positive<br>+ 0.5 V |  |

c. Set the function generator controls:

$\begin{array}{ccccc} \text{Output channel} & & \text{CH1} \\ \text{Function} & & \text{Square} \\ \text{Parameters} & & & \\ \text{Frequency} & & 10 \text{ MHz} \\ \text{Amplitude} & & 1.0 \text{ V into } 50 \text{ }\Omega \\ \text{Offset} & & 0 \text{ mV} \\ \end{array}$

- 2. Load the setup file (REFIN.dtg). Refer to Loading Files on page 1-13.

- 3. Turn the function generator Output on.

- 4. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- 5. Verify the displayed waveform: A 100 MHz, approximately 1  $V_{p-p}$  clock pattern is displayed on the oscilloscope screen.

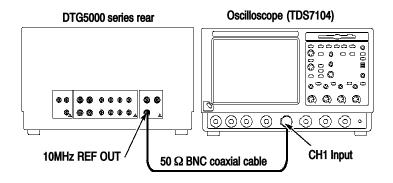

## 10 MHz Reference Output

This test verifies that the 10 MHz reference output of the DTG5000 series mainframe is functional.

| Equipment     | One oscilloscope (TDS7104) (item 3)                                                       |

|---------------|-------------------------------------------------------------------------------------------|

| required      | One BNC coaxial cable (item 7)                                                            |

| Prerequisites | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11. |

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the oscilloscope:

■ Connect a BNC coaxial cable from the **10MHz REF OUT** at the rear panel of DTG5000 series mainframe to the CH1 input of oscilloscope. See Figure 1-11.

Figure 1-11: 10 MHz Reference Output tests

| Vertical            | CH1        |

|---------------------|------------|

| CH1 scale           | 500 mV/div |

| CH1 input impedance | 50 Ω       |

| CH1 offset          | 0.6 V      |

| Horizontal          |            |

| Scale               | 50 ns/div  |

| Trigger             |            |

| Source              | CH1        |

| Slope               | Positive   |

| Level               | 0.5 V      |

- 2. Load the setup file (REFOUT.dtg). Refer to Loading Files on page 1-13.

- 3. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- **4.** Verify the displayed waveform: A 10 MHz, approximately 1.2 V<sub>p-p</sub> clock pattern is displayed on the oscilloscope screen.

- 5. Modify the oscilloscope setting and verify the displayed waveform:

- a. Change the CH1 impedance setting of oscilloscope to  $1 M\Omega$ .

- **b.** Verify that the amplitude of the clock pattern changes to approximately 2.4  $V_{\text{p-p}}$ .

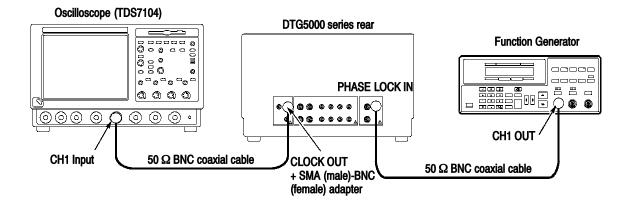

## **Phase Lock Input**

This test verifies that the phase lock input of the DTG5000 series mainframe is functional.

| Equipment required | One oscilloscope (TDS7104) (item 3) One function generator (item 5)                       |

|--------------------|-------------------------------------------------------------------------------------------|

|                    | Two BNC coaxial cables (item 7)                                                           |

|                    | One SMA (male)-BNC (female) adapter (item 8)                                              |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11. |

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the oscilloscope and function generator:

- Connect a BNC coaxial cable from the CH1 Out at the front panel of function generator to the PHASE LOCK IN at the rear panel of DTG5000 series mainframe.

- Use an SMA (male)-BNC (female) adapter and a BNC coaxial cable to connect the CLOCK OUT at the rear panel of DTG5000 series mainframe and the oscilloscope CH1 input. See Figure 1-12.

Figure 1-12: Phase Lock Input tests

| Vertical            | CH1        |

|---------------------|------------|

| CH1 scale           | 200 mV/div |

| CH1 input impedance | 50 Q       |

Horizontal

Scale ..... 50 ns/div

Trigger

Source

CH1

Slope

Positive

Level

+ 0.5 V

**c.** Set the function generator controls:

**Parameters**

- 2. Load the setup file (PLL.dtg). Refer to Loading Files on page 1-13.

- 3. Turn the function generator Output on.

- 4. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- 5. Verify the displayed waveform: A 10 MHz, 1 V<sup>p-p</sup> clock pattern is displayed on the oscilloscope screen.

- **6.** Observe the clock pattern change:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings**, and then select **Timing**.

- **b.** Move cursor to **Clock Frequency** with the TAB key.

- c. Change the Clock Frequency to 20MHz, 30MHz, and 40MHz in this sequence.

- d. Verify the displayed waveform on the oscilloscope screen: A 10 MHz, 1 V<sub>p-p</sub> clock pattern is changed to 20 MHz, 30 MHz, and 40 MHz in response to the clock frequency change.

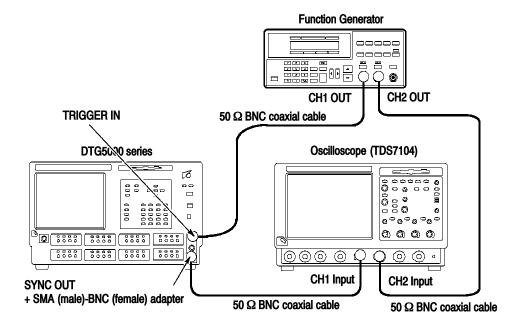

# Internal Auto Trigger and Trigger Input

This test verifies that the internal trigger is functional.

| Equipment required | One oscilloscope (TDS7104) (item 3)  One function generator (item 5)  Three RNC cooxiel coblec (item 7) |

|--------------------|---------------------------------------------------------------------------------------------------------|

|                    | Three BNC coaxial cables (item 7) One SMA (male)-BNC (female) adapter (item 8)                          |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11.               |

- 1. Install the test hookup and preset the instrument controls:

- a. Hook up the oscilloscope and function generator:

- Connect a BNC coaxial cable from the CH1 OUT at the front panel of function generator to the TRIGGER IN at the front panel of DTG5000 series mainframe.

- Connect a BNC coaxial cable from the CH2 OUT at the front panel of function generator to the CH2 input of oscilloscope

- Use an SMA (male)-BNC (female) adapter and a BNC coaxial cable to connect the SYNC OUT at the front panel of DTG5000 series mainframe and the CH1 input of oscilloscope. See Figure 1-13.

Figure 1-13: Internal Trigger tests

Vertical

Horizontal

Scale . . . . . . . . . . . . . . . . 200 ns/div

Acquisition

Mode ..... Peak Detect

Trigger

Source

CH2

Mode

Normal

Slope

Positive

Level

0.5 V

c. Set the function generator controls:

Output channel ..... CH1, CH2

Function . . . . . . . . . . . . Square (CH1, CH2)

**Parameters**

Frequency . . . . . . . . . . 1 MHz (CH1, CH2)

Amplitude . . . . . . . . . . . . . 1.0 V into 50  $\Omega$  (CH1, CH2)

Offset . . . . . . . . . . . . . 0.5 V (CH1, CH2)

BOTH CH . . . . . Press SHIFT key, then press CH.

- 2. Load the setup file (TRIG.dtg). Refer to Loading Files on page 1-13.

- 3. Turn the function generator CH1 and CH2 Outputs on.

- 4. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

- 5. Confirm the displayed waveforms: Verify that an approximately  $0.4~V_{p-p}$  amplitude pulse waveform is generated from CH 1 every  $1.00~\mu s$  synchronizing with CH2 signal rising edge on the oscilloscope screen.

- **6.** Observe the trigger level change effects:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- **b.** Move cursor to **Trigger Level** with the TAB key and set the trigger level to +1.1 V.

- Verify that the CH1 pulse signal disappears from the oscilloscope screen and that the data timing generator screen message changes to Waiting Trigger.

- 7. Change the trigger impedance and observe the waveform:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings**, and then select **Time Base**.

- **b.** Move cursor to **Trigger Impedance** with the TAB key and set the trigger impedance to  $1 \text{ k}\Omega$ .

- c. Verify that an approximately  $0.4~V_{p-p}$  amplitude pulse waveform is generated from CH 1 every  $1.00~\mu s$  synchronizing with CH2 signal rising edge on the oscilloscope screen.

- **8.** Observe the trigger level change effects:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- **b.** Move cursor to **Trigger Level** with the TAB key and set the trigger level to -0.4 V.

- Verify that the CH1 pulse signal disappears from the oscilloscope screen and that the data timing generator screen message changes to Waiting Trigger.

- **9.** Change the trigger level and trigger slope, and then observe the waveform:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- **b.** Move cursor to **Trigger Level** and **Trigger Slope** with TAB key. Set the trigger level to +1.0 V and trigger slope to **Negative**.

- c. Confirm the displayed waveform: Verify that an approximately  $0.4~V_{p-p}$  amplitude pulse waveform is generated from CH 1 every  $1.00~\mu s$  synchronizing with CH2 signal falling edge on the oscilloscope screen.

- 10. Turn the function generator CH1 and CH2 Outputs off.

- 11. Change the trigger source and trigger level, and then observe the waveform:

- a. Set the oscilloscope trigger source to CH1 and trigger level to 0.2 V.

- **b.** Confirm the displayed waveform: Each time you push the **MANUAL TRIGGER** button at the front panel of DTG5000 series mainframe, the oscilloscope screen is updated with a pulse waveform.

- 12. Push the RUN button of the data timing generator to turn the RUN LED off.

- 13. Change the trigger source and interval, and then observe the waveform:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- b. Move cursor to Trigger Source with the TAB key and set to Internal.

- c. Set the Interval to  $1.00 \mu s$ .

- **d.** Push the **RUN** button of the data timing generator to light the RUN LED.

- e. Verify that an approximately 0.4  $V_{p-p}$  amplitude pulse waveform is generated every 1.00  $\mu$ s on the oscilloscope screen.

- 14. Change the Interval setting and observe the waveform:

- a. Change the Interval from  $1.00 \mu s$  to 1.00 ms.

- b. Change the horizontal scale of the oscilloscope from 200 ns/div to 200 μs/div.

- c. Verify that an approximately  $0.4 V_{p-p}$  amplitude pulse waveform is generated every 1.00 ms on the oscilloscope screen.

# **Event Input and Sequence Function**

This test verifies that the event input and sequence of the DTG5000 series mainframe are functional.

| Equipment required | One oscilloscope (TDS7104) (item 3) One function generator (item 5)                       |

|--------------------|-------------------------------------------------------------------------------------------|

|                    | One 50 $\Omega$ SMA coaxial cable (item 6)                                                |

|                    | Three 50 $\Omega$ BNC coaxial cables (item 7)                                             |

|                    | One SMA (female)-BNC (male) adapter (item 9)                                              |

|                    | One BNC-T connector (item 14)                                                             |

| Prerequisites      | The DTG5000 Series Data Timing Generator must meet the prerequisites listed on page 1-11. |

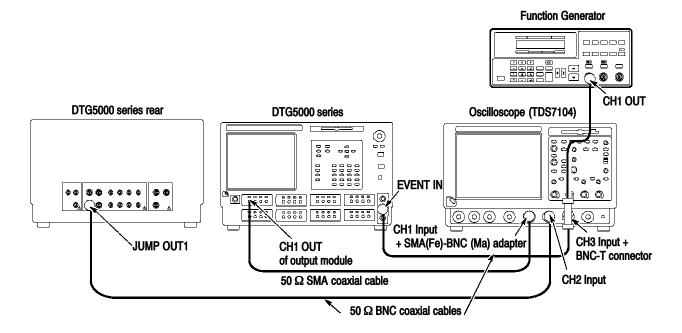

- 1. Install the test hookup and preset the instrument controls:

- **a.** Hook up the oscilloscope and function generator:

- Attach a BNC-T connector to the **CH3 input** of the oscilloscope.

- Connect a BNC coaxial cable from the CH1 Out of function generator to the CH3 input of the oscilloscope (through BNC-T connector).

- Connect a second BNC coaxial cable to the EVENT IN at the front panel of DTG5000 series mainframe, and then connect the opposite end of the cable to the CH3 input of the oscilloscope (through BNC-T connector).

- Connect a third BNC coaxial cable from the JUMP OUT1 at the rear panel of DTG5000 series mainframe to the CH2 input of oscilloscope.

- Attach an SMA (female)-BNC (male) adapter to the oscilloscope

CH1 input connector.

- Connect an SMA coaxial cable from the CH1 connector of the output module, which is inserted in the slot A of DTG5000 series mainframe, to the SMA-BNC adapter (CH1 input of oscilloscope). See Figure 1-14.

Figure 1-14: Event Input and Sequence tests

#### Vertical

Horizontal

Scale ...... 200 ns/div

Acquisition

Mode . . . . . Peak Detect

Sequence . . . . . . RUN/STOP button Only

Trigger

Source

CH3

Mode

Normal

Slope

Positive

Level

+ 0.5 V

Coupling

DC

Position

50%

c. Set the function generator controls:

Function . . . . . . . . . . . . . Square (CH1 and CH2)

**Parameters**

Frequency ...... 500 Hz (CH1 and CH2)

Amplitude . . . . . . . . . . . . 1.0 V into 50  $\Omega$  (CH1 and CH2)

Offset . . . . . . . . . . . . 0.5 V (CH1 and CH2)

- 2. Load the setup file (EVENT.dtg). Refer to Loading Files on page 1-13.

- 3. Turn the function generator Output on.

- 4. Push the RUN button of the data timing generator to light the RUN LED, and then push the ALL OUTPUTS ON/OFF button to activate the output.

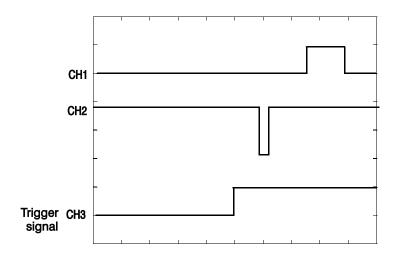

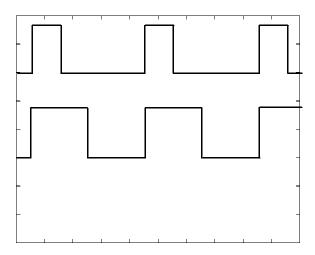

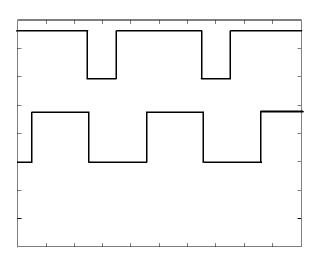

- 5. Verify that the oscilloscope displays data pattern such as shown in Figure 1-15.

**NOTE**. The CH1 and CH2 signals appear to have jitters. The DTG5274 has 120 clocks width jitter and the DTG5078 has 30 clocks width jitter compared to CH3 trigger signal.

Figure 1-15: Data pattern example

- **6.** Verify the waveform after **trigger source** and **trigger level** settings change:

- a. Set the trigger source to CH2 and the trigger level to + 1.4 V.

- **b.** Verify that an approximately  $3.3 \ V_{p-p}$  amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal rising edge on the oscilloscope screen.

- 7. Change the DTG5000 series mainframe settings and verify the waveform:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- b. Set the Event Input Polarity to Invert.

- c. Verify that an approximately 3.3 V<sub>p-p</sub> amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal falling edge on the oscilloscope screen.

- **8.** Change the DTG5000 series mainframe settings and verify that the oscilloscope untriggered:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- **b.** Set the **Event Input Threshold** to **+ 1.1** V.

- c. Confirm that the oscilloscope does not trigger.

- 9. Change the DTG5000 series mainframe settings and verify the waveform:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- b. Set the Event Input Impedance to 1 k $\Omega$ .

- c. Verify that an approximately  $3.3~V_{p-p}$  amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal falling edge on the oscilloscope screen.

- **10.** Change the DTG5000 series mainframe settings and verify that the oscilloscope untriggered:

- **a.** From the application menu bar of DTG5000 series mainframe, select **Settings** and then select **Time Base**.

- b. Set the Event Input Threshold to 0.4 V.

- **c.** Confirm that the oscilloscope does not trigger.

- 11. Change the DTG5000 series mainframe settings and verify the waveform:

- **a.** From the application menu bar of DTG5000 series mainfram, select **Settings** and then select **Time Base**.

- **b.** Set the **Event Input Threshold** to + 1.0 V.

- c. Verify that an approximately 3.3 V<sub>p-p</sub> amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal falling edge on the oscilloscope screen.

- 12. Connect the cable to Jump Out2 and verify the displayed waveform:

- a. Disconnect the BNC cable from the **JUMP OUT1** and then connect it to the **JUMP OUT2** at the rear panel of DTG5000 series mainframe.

- **b.** Verify that an approximately  $3.3~V_{p-p}$  amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal falling edge on the oscilloscope screen.

- 13. (DTG5078 only) Connect the cable to Jump Out3 and verify the displayed waveform:

- a. Disconnect the BNC cable from the JUMP OUT2 and then connect it to the JUMP OUT3 at the rear panel of DTG5000 series mainframe.

- **b.** Verify that an approximately  $3.3~V_{p-p}$  amplitude low pulse waveform is generated from CH 2 synchronizing with CH3 signal falling edge on the oscilloscope screen.

- 14. Turn the function generator Output off.

- 15. Each time you push the MANUAL EVENT button at the front panel of DTG5000 series mainframe, the oscilloscope screen is updated with data pattern same as step 12-b. Ignore the CH3 waveform.

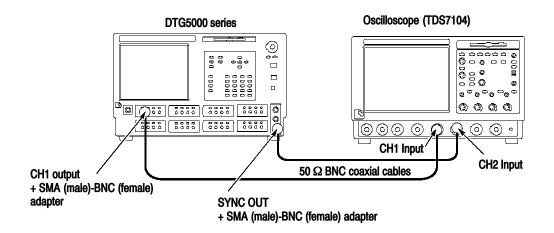

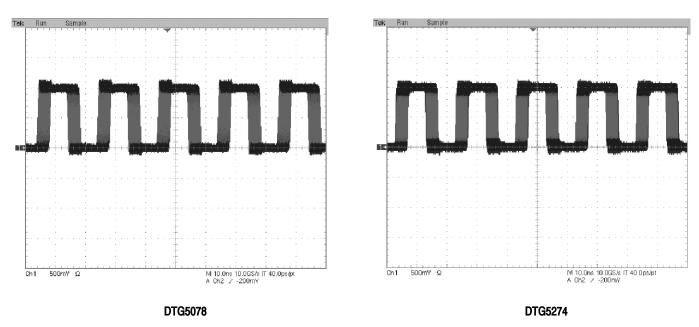

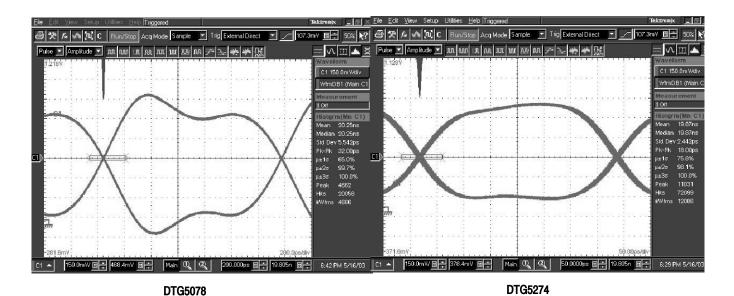

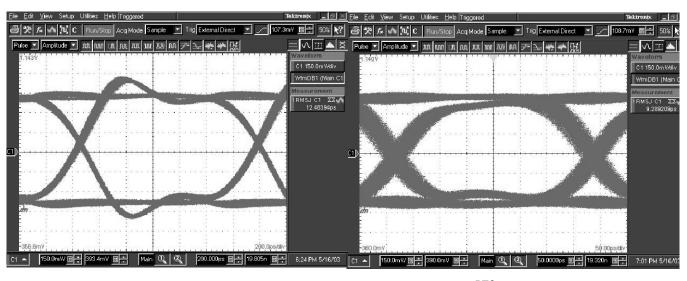

#### All Jitter Generation