# Reference

# **Tektronix**

PCI Express Methods of Implementation (MOI)

071-1772-00

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX, TEK and RT-Eye are registered trademarks of Tektronix, Inc.

# **Contacting Tektronix**

Tektronix, Inc. 14200 SW Karl Braun Drive or P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

# **Table of Contents**

| 1 | Intr | oduction to the RT-Eye PCI Express Compliance Module1            |

|---|------|------------------------------------------------------------------|

| 2 | PCI  | Express Compliance Specifications2                               |

|   | 2.1  | Differential Transmitter (TX) Output Specifications3             |

|   | 2.2  | Differential Transmitter (TX) Compliance Eye Diagrams4           |

|   | 2.3  | Differential Receiver (RX) Input Specifications5                 |

|   | 2.4  | Differential Receiver (RX) Compliance Eye Diagrams5              |

|   | 2.5  | Add-In Card Transmitter Path Compliance Specifications6          |

|   | 2.6  | Add-In Card Compliance Eye Diagrams7                             |

|   | 2.7  | System Board Transmitter Path Compliance Eye Diagrams7           |

|   | 2.8  | System Board Compliance Eye Diagrams8                            |

|   | 2.9  | PCI ExpressModule <sup>TM</sup> Compliance Specifications9       |

|   |      | 2.9.1 ExpressModule Add-In Card Transmitter Path Specifications9 |

|   |      | 2.9.2 ExpressModule System Board Transmitter Path                |

|   |      | 2.9.3 Express Module System Board Compliance Eye Diagrams10      |

|   | 2.10 | PCI Express External Cabling Specifications11                    |

|   |      | 2.10.1 External Cabling Transmitter Path Specifications11        |

|   |      | 2.10.2 Cable (Transmitter Side) Eye Diagrams11                   |

|   |      | 2.10.3 External Cabling Receiver Path Specifications12           |

|   |      | 2.10.4 Cable (Receive Side) Eye Diagrams12                       |

|   | 2.11 | Reference Clock Compliance Specifications13                      |

| 3 | Prep | paring to Take Measurements14                                    |

|   | 3.1  | Required Equipment14                                             |

|   | 3.2  | Probing Options for Transmitter Testing14                        |

|   |      | 3.2.1 SMA Input Connection                                       |

|   |      | 3.2.2 ECB pad connection16                                       |

|   | 3.3  | Initial Oscilloscope Setup17                                     |

|   | 3.4  | Running the RT-Eye Software17                                    |

|   | 3.5  | Configuring the Software to take measurements18                  |

|   |      | 3.5.1 Select Standard                                            |

|   |      | 3.5.2 Select Test Point                                          |

|   |      | 3.5.3 Select Probe Type                                          |

|   |     | 3.5.4 Select Measurements                                      | 19         |

|---|-----|----------------------------------------------------------------|------------|

|   |     | 3.5.5 Configure Source of Waveforms                            | 20         |

|   |     | 3.5.6 Configure Clock Recovery                                 | 21         |

|   |     | 3.5.7 Configure Plots                                          | 23         |

| 4 | PCI | Express Transmitter Compliance Testing                         | 24         |

|   | 4.1 | Probing the link for TX compliance                             | 24         |

|   | 4.2 | TX Compliance Test Load                                        | 24         |

|   | 4.3 | Running a Transmitter (TX) Compliance Test                     | 24         |

|   |     | 4.3.1 TX Unit Interval Measurement MOI                         | 26         |

|   |     | 4.3.2 TX Differential Pk-Pk Output Voltage MOI                 | 27         |

|   |     | 4.3.3 TX De-Emphasized Differential Output Voltage (Ratio) MOI | 29         |

|   |     | 4.3.4 Minimum TX Eye Width MOI                                 | 30         |

|   |     | 4.3.5 TX Median-to-Max Jitter MOI                              | 31         |

|   |     | 4.3.6 TX Output Rise/Fall Time MOI                             | 32         |

|   |     | 4.3.7 TX AC Common Mode Output Voltage MOI                     | 34         |

|   |     | 4.3.8 TX Delta DC Common Mode Voltage MOI                      | 35         |

|   |     | 4.3.9 TX Total Jitter@BER MOI                                  | 36         |

|   |     | 4.3.10 Spectrum Analysis Based Rj/Dj Separation on             |            |

|   |     | 4.3.11 Arbitrary Pattern Analysis Based Rj/Dj Separation       | 38         |

|   |     | 4.3.12 TX Deterministic MOI (Using Dual-Dirac Model)           | 39         |

|   |     | 4.3.13 Rj/Dj Separation Based on Dual Dirac Model              | 39         |

|   |     | 4.3.14 TX Waveform Eye Diagram Mask Test MOI                   | 40         |

| 5 | PCI | Express Receiver (RX) Compliance Testing                       | 41         |

|   | 5.1 | Probing the Link for RX Compliance                             | 41         |

|   | 5.2 | Running a Complete RX Compliance Test                          | 41         |

|   |     | 5.2.1 RX Unit Interval Measurement MOI                         | 42         |

|   |     | 5.2.2 RX Differential Pk-Pk Input Voltage MOI                  | 42         |

|   |     | 5.2.3 Minimum RX Eye Width MOI                                 | 43         |

|   |     | 5.2.4 RX Median-to-Max Jitter MOI                              | <b>4</b> 4 |

|   |     | 5.2.5 RX Total Jitter@BER MOI                                  | 45         |

|   |     | 5.2.6 RX Deterministic Jitter@BER using Dual-Dirac model       | 46         |

|   |     | 5 2 7 RY Wayafarm Fya Diagram Mask Tost MOI                    | 47         |

ii PCI Express

| 6  | PCI                           | Express Interconnect Test Point Testing                             | 48    |  |  |

|----|-------------------------------|---------------------------------------------------------------------|-------|--|--|

|    | 6.1                           | Unit Interval Measurement MOI                                       | 49    |  |  |

|    | 6.2                           | Transition and Non-Transition Bit Eye Height Measurement MOI        | 49    |  |  |

|    | 6.3                           | Eye Width Measurement MOI                                           | 50    |  |  |

|    | 6.4                           | Interconnect Median-to-Max Jitter and Total Jitter@BER MOI          | 52    |  |  |

| 7  | PCI                           | Express Reference Clock Compliance Measurements                     | 53    |  |  |

|    | 7.1                           | Probing the Link for Reference Clock Compliance                     | 53    |  |  |

|    | 7.2                           | Running a Complete Reference Clock Compliance Test                  | 53    |  |  |

|    |                               | 7.2.1 Reference Clock Frequency Measurement Test MOI                | 54    |  |  |

|    |                               | 7.2.2 Reference Clock Differential Voltage Hi and Lo Test MOI       | 55    |  |  |

|    |                               | 7.2.3 Reference Clock Differential rise and fall edge rates test MC | )I 56 |  |  |

|    |                               | 7.2.4 Reference clock Duty cycle test MOI                           | 57    |  |  |

|    |                               | 7.2.5 Reference Clock Jitter Test MOI                               | 58    |  |  |

| 8  | Usir                          | ng SigTest                                                          | 59    |  |  |

| 9  | Usir                          | ng Dynamic Test Points                                              | 62    |  |  |

|    | 9.1                           | Test Point File Syntax                                              | 63    |  |  |

|    | 9.2                           | Creating the new Test Point                                         | 65    |  |  |

|    | 9.3                           | Running a test with the new DTP                                     | 66    |  |  |

| 10 | Giv                           | ing a Device an ID                                                  | 67    |  |  |

| 11 | Cre                           | ating a Compliance Report                                           | 67    |  |  |

| 12 | Further Analysis Techniques67 |                                                                     |       |  |  |

| 13 |                               | uring Compliance over specified population                          |       |  |  |

PCI Express iii

iv PCI Express

# 1 Introduction to the RT-Eye PCI Express Compliance Module<sup>1</sup>

This document provides the procedures for making PCI Express compliance measurements with Tektronix TDS6000 Series and TDS7704B, real time oscilloscopes (6 GHz models and above) and probing solutions.

The PCI Express (PCI-E) Compliance Module Version 2.0 (Opt. PCE) is an optional software plug-in to the RT-Eye Serial Data Compliance and Analysis software (Opt. RTE). The PCI Express Compliance module provides transmitter path measurements (amplitude, timing, and jitter), waveform mask testing, and Reference Clock (RefClk) compliance measurements described in multiple variants of the PCI Express specifications. Specifications covered in this document and the PCE module includes a total of eighteen data and reference clock test points defined in the following specifications.

Additional test points can also be added by the user, or provided by Tektronix representatives, using *Dynamic Test Point (DTP)* definition, described in detail in Section 9.

Table 1 – Supported Specifications

| Test Methods | Spec<br>Revision | PCI Express Specification Title             | Test Points Defined                                                             |

|--------------|------------------|---------------------------------------------|---------------------------------------------------------------------------------|

| Rev1.0a      | Rev1.0a          | Base Specification                          | Transmitter and Receiver (Section 4.3)                                          |

|              | Rev 1.0          | Mobile Graphics Lower Power Addendum        | Transmitter (Section 2.2)                                                       |

|              | Rev1.0a          | CEM (Card Electro-Mechanical) Specification | System and Add-In Card (Section 4.7)                                            |

| Rev1.1       | Rev1.1           | Base Specification                          | Transmitter & Receiver (Section 4.3)                                            |

|              | Rev1.1           | CEM Specification                           | System and Add-In Card (Section 4.7) Reference Clock (Section 2.1)              |

|              | Rev1.0           | Express Module Specification                | Transmitter Path and System Board (Section 5.4)                                 |

|              | Rev0.4C          | External Cabling Specification              | Transmitter and Receiver Path (Section 3.3)                                     |

|              | TBD              | Future 2.5 Gb/s Variants                    | Dynamic Test Points as specifications are defined                               |

| Gen2         | Rev0.3           | Base Specification                          | Transmitter & Receiver (Section 4.4) Mobile Low Power Transmitter (Section 4.4) |

|              |                  |                                             | Reference Clock (Section 4.4)                                                   |

<sup>&</sup>lt;sup>1</sup> **Disclaimer:** The tests provided in the PCI Express compliance module (which are described in this document) do not guarantee PCI Express compliance. The test results should be considered "Pre-Compliance". Official PCI Express compliance and PCI-SIG Integrator List qualification is governed by the PCI-SIG (Special Interest Group) and can be achieved only through official PCI-SIG sanctioned testing.

| Test Methods | Spec<br>Revision | PCI Express Specification Title | Test Points Defined                               |

|--------------|------------------|---------------------------------|---------------------------------------------------|

|              | TBD              | Future 5 Gb/s Variants          | Dynamic Test Points as specifications are defined |

Refer to <a href="http://www.pcisig.com/specifications/pciexpress/">http://www.pcisig.com/specifications/pciexpress/</a> for the latest specifications.

The PCE module can also be used to automate setup procedures for SigTest by using its *SigTest Import feature* (Refer to Section 8).

In this document, for all references to the PCI Express Base Specification and Card Electrical Mechanical (CEM) specification, refer to all versions of the Spec. (Rev 1.0a, 1.1, and Gen2). Differences between the specifications are specifically called out when appropriate.

In the subsequent sections, step-by-step procedures are described to help you perform PCI Express measurements. Each measurement is described as a Method of Implementation (MOI). For further reference, consult the Compliance checklists offered to PCI-SIG members at <a href="https://www.pcisig.com">www.pcisig.com</a>.

# 2 PCI Express Compliance Specifications

As shown in Table 1, Electrical Specifications for PCI Express are provided in multiple documents. This section provides a summary of the measurement parameters measured in the RT-Eye PCE module and how they are related to the symbol and test limits in the specification.

# 2.1 Differential Transmitter (TX) Output Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base specifications.

Table 2- Supported base specification transmitter measurements

| Parameter                                                                    | Symbol(s)                              | Specification            |                          |                          |

|------------------------------------------------------------------------------|----------------------------------------|--------------------------|--------------------------|--------------------------|

|                                                                              |                                        | Gen1                     | Gen1                     | Gen2                     |

|                                                                              |                                        | Rev1.0a                  | Rev1.1                   | Rev0.3                   |

| Unit interval                                                                | UI                                     | 400 ps                   | 400 ps                   | 200 ps                   |

|                                                                              |                                        | +/- 300 ppm              | +/- 300 ppm              | +/- 300 ppm              |

| Differential p-p TX                                                          | $V_{\mathit{TX-DIFF}p-p}$              | 0.8 V (min)              | 0.8 V (min)              | 0.8 V (min)              |

| voltage swing                                                                | V <sub>TX-SWING</sub>                  | 1.2 V (max)              | 1.2 V (max)              | 1.2 V (max)              |

| Low power differential p-p TX voltage swing                                  | VTX-SWING-LOW                          | Not Specfied             | Not Specfied             | 0.4 V (min)              |

| p-p 17 voltage swing                                                         |                                        |                          |                          | 0.6 V (max)              |

| De-emphasized output                                                         | $V_{TX-DE-RATIO}$                      | -3.0 dB (min)            | -3.0 dB (min)            | -5.5 dB (min)            |

| voltage ratio                                                                | TA BE KITTO                            | -4.0 dB (max)            | -4.0 dB (max)            | -6.5 dB (max)            |

| Transmitter eye including all jitter                                         | $T_{TX-EYE}$                           | .70 UI (min)             | .75 UI (min)             | .75 UI (min)             |

| sources                                                                      | ttx-eye_tj                             |                          |                          |                          |

| Maximum time between the jitter median and maximum deviation from the median | T <sub>TX-EYEMEDIAN-10-MAXJITTER</sub> | .125 UI (max)            | .125 UI (max)            | Not Spec'd               |

| Deterministic jitter                                                         | $T_{TX	ext{-}DJ	ext{-}DD}$             |                          |                          | 0.15 UI (max)            |

| D+/D- TX output rise/fall Time                                               | $T_{TX-RISE}$ $T_{TX-FALL}$            | 0.125 UI (min)           | 0.125 UI (min)           | 0.15 UI (min)            |

| AC RMS common mode output voltage                                            | $V_{TX-CM-ACp}$                        | 20 mV (max)              | Not Specfied             | Not Specfied             |

| Absolute delta of DC common mode voltage between D+ and D-                   | $V_{TX-CM-DC-LINE-DELTA}$              | 0 V (min)<br>25 mV (max) | 0 V (min)<br>25 mV (max) | 0 V (min)<br>25 mV (max) |

# 2.2 Differential Transmitter (TX) Compliance Eye Diagrams

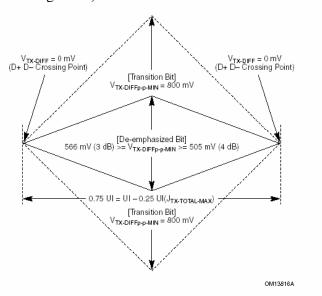

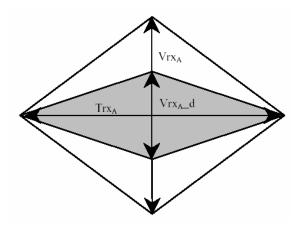

Figure 1a shows the eye mask definitions for the Rev1.1 Base specification. It provides an example of a transmitter mask for a signal with de-emphasis. Transition and non-transition bits must be separated to perform the mask testing. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications. Low power transmitter variants in both Gen1 and Gen2 do not use de-emphasis (This is shown in Figure 1b).

Figure 1a: Transmitter eye masks for transition and non-transition bits

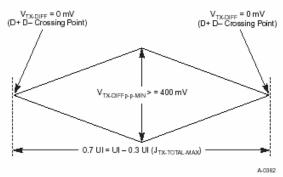

Figure 1b: Transmitter eye mask for low power variant where de-emphasis is not used

# 2.3 Differential Receiver (RX) Input Specifications

The following table shows the available measurements in the PCE Module and their test limits defined in each of the Base specifications.

Table 3 – Supported base specification receiver measurements

| Parameter                                                                     | Symbol                                            | Gen1         | Gen1         | Gen2             |

|-------------------------------------------------------------------------------|---------------------------------------------------|--------------|--------------|------------------|

|                                                                               |                                                   | Rev1.0a      | Rev1.1       | Rev0.3           |

| Unit interval                                                                 | UI                                                | 400 ps       | 400 ps       | 200 ps           |

|                                                                               |                                                   | +/- 300 ppm  | +/- 300 ppm  | +/- 300 ppm      |

| Minimum receiver eye height                                                   | $V_{RX\_EYE}$                                     | .175 V (min) | .175 V (min) | .120 V (min)     |

|                                                                               |                                                   | 1.2 V (max)  | 1.2 V (max)  | 1.2 V (max)      |

| Minimum receiver eye width                                                    | $T_{RX-EYE}$                                      | .40 UI (min) | .40 UI (min) | .40 UI (min)     |

| Receiver deterministic jitter –<br>Dj                                         | $T_{RX\_DJ\_DD}$                                  | Not Specfied | Not Specfied | .44 UI (max)     |

| Maximum time between the jitter median and maximum deviation from the median. | $T_{TX	ext{-}EYEMEDIAN	ext{-}to	ext{-}MAXJITTER}$ | .30 UI (max) | .30 UI (max) | Not<br>Specified |

# 2.4 Differential Receiver (RX) Compliance Eye Diagrams

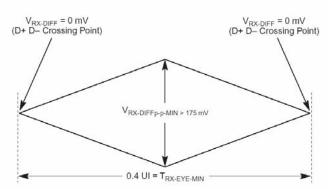

Figure 2 shows the receiver eye mask definitions for the Rev1.1 Base specification. The amplitude and jitter mask geometries are derived from the amplitude and jitter specifications.

Figure 2: Receiver input eye mask

# 2.5 Add-In Card Transmitter Path Compliance Specifications

Table 5 is derived from the Electrical Mechanical Specifications (CEM). See the CEM Specification for additional notes and test definitions.

Table 4 – Supported CEM add-in card measurements

| Parameter                                                                      | Symbol                    | Gen1         | Gen1          | Gen2        |

|--------------------------------------------------------------------------------|---------------------------|--------------|---------------|-------------|

|                                                                                |                           | Rev1.0a      | Rev1.1        | Rev0.3      |

| Unit interval                                                                  | UI                        | 400 ps       | 400 ps        | 200 ps      |

|                                                                                |                           | +/- 300 ppm  | +/- 300 ppm   | +/- 300 ppm |

| Eye height of transition                                                       | V <sub>TXA</sub>          | .514 V (min) | .514 V (min)  | TBD         |

| bits                                                                           |                           | 1.2 V (max)  | 1.2 V (max)   |             |

| Eye height of non-<br>transition bits                                          | $V_{TXA\_d}$              | .360 V (min) | .360 V (min)  | TBD         |

| Eye width across any                                                           | T <sub>TXA</sub>          | 237 ps (min) | Not           | TBD         |

| 250 Uls                                                                        | In Rev1.0a                |              | Specified     |             |

| Eye width with sample                                                          | T <sub>TXA</sub>          | Not Specfied | 287 ps (min)  | TBD         |

| size of 10 <sup>6</sup> UI                                                     | In Rev1.1                 |              |               |             |

| Jitter eye opening at BER 10-12                                                |                           | Not Specfied | 274 ps (min)  | TBD         |

| Maximum median-max<br>jitter outlier with sample<br>size of 10 <sup>6</sup> UI | JTXA-MEDIAN-to-MAX-JITTER | Not Specfied | 56.5 ps (max) | TBD         |

| Maximum median-max<br>jitter outlier with sample<br>size of 10 <sup>6</sup> UI |                           | Not Specfied | 63 ps (max)   | TBD         |

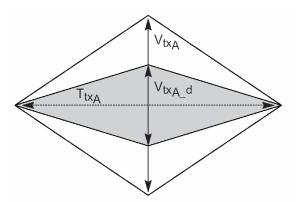

# 2.6 Add-In Card Compliance Eye Diagrams

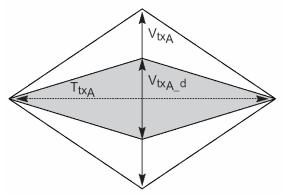

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 4.

Figure 3: Add-in card compliance eye masks

# 2.7 System Board Transmitter Path Compliance Eye Diagrams

Table 6 is derived from the Electrical Mechanical Specifications (CEM). See the CEM Specification for additional notes and test definitions.

Table 5 – Supported CEM System Board Measurements

| Parameter                                                    | Symbol                                    | Gen1         | Gen1          | Gen2        |

|--------------------------------------------------------------|-------------------------------------------|--------------|---------------|-------------|

|                                                              |                                           | Rev1.0a      | Rev1.1        | Rev0.3      |

| Unit interval                                                | UI                                        | 400 ps       | 400 ps        | 200 ps      |

|                                                              |                                           | +/- 300 ppm  | +/- 300 ppm   | +/- 300 ppm |

| Eye height of transition bits                                | V <sub>TXS</sub>                          | .274 V (min) | .274 V (min)  | TBD         |

|                                                              |                                           | 1.2 V (max)  | 1.2 V (max)   |             |

| Eye height of non-transition bits                            | $V_{TXS\_d}$                              | .253 V (min) | .253 V (min)  | TBD         |

| Eye width across any 250                                     | $T_{TXS}$                                 | 18 ps (min)  | Not Specfied  | TBD         |

| Uls                                                          | In Rev1.0a                                |              |               |             |

| Eye width with sample size of                                | $T_{TXS}$                                 | Not Specfied | 246 ps (min)  | TBD         |

| 10 <sup>6</sup> UI                                           | In Rev1.1                                 |              |               |             |

| Jitter eye opening at BER 10-                                |                                           | Not Specfied | 233 ps (min)  | TBD         |

| Maximum median-max jitter outlier with sample size of 106 UI | J <sub>TXA-MEDIAN-to-MAX-</sub><br>JITTER | Not Specfied | 77 ps (max)   | TBD         |

| Maximum median-max jitter outlier with sample size of 106 UI |                                           | Not Specfied | 83.5 ps (max) | TBD         |

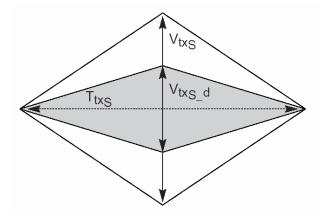

# 2.8 System Board Compliance Eye Diagrams

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 5.

Figure 4: System Board Compliance Eye Masks

# 2.9 PCI ExpressModule™ Compliance Specifications

The specifications in this section are taken from the PCI Express ExpressModule™ specification, which is a companion specification to the *PCI Express Base specification*. Its primary focus is the implementation of a modular I/O form factor that is focused on the needs of workstations and servers. Measurements in the PCE module support add-in card and system transmitter path measurements at the PCI Express connector.

## 2.9.1 ExpressModule Add-In Card Transmitter Path Specifications

Table 6 is derived from Section 5.4.1 of the ExpressModule Electro-Mechanical Specifications Rev. 1.0.

| Table 6    | Supported | Everecel | ALUBAN   | Λdd-In | Card | Measurements |  |

|------------|-----------|----------|----------|--------|------|--------------|--|

| i abie o – | Supported | Expressi | noaule i | Auu-m  | Caro | weasurements |  |

| Parameter                                                    | Symbol                      | Rev1.0        |

|--------------------------------------------------------------|-----------------------------|---------------|

| Unit interval                                                | UI                          | 400 ps        |

|                                                              |                             | +/- 300 ppm   |

| Eye height of transition Bits                                | $V_{TXA}$                   | .514 V (min)  |

|                                                              |                             | 1.2 V (max)   |

| Eye height of non-transition Bits                            | $V_{TXA\_d}$                | .360 V (min)  |

| Eye width with sample size of 106 UI                         | T <sub>TXA</sub>            | 287 ps (min)  |

|                                                              | In Rev1.1                   |               |

| Jitter eye opening at BER 10 <sup>-12</sup>                  |                             | 274 ps (min)  |

| Maximum median-max jitter outlier with sample size of 106 UI | J <sub>TXA-MEDIAN-to-</sub> | 56.5 ps (max) |

| Maximum median-max jitter outlier with sample size of 10° UI |                             | 63 ps (max)   |

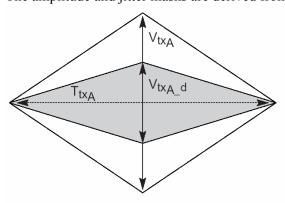

Figure 5: ExpressModule add-in card compliance eye masks

# 2.9.2 ExpressModule System Board Transmitter Path Compliance Eye Diagrams

Table 7 is derived from Section 5.4.3 of the ExpressModule Electro-Mechanical Specifications Rev. 1.0.

Table 7 – Supported ExpressModule system board measurements

| Parameter                                                    | Symbol                                    | Gen1          |

|--------------------------------------------------------------|-------------------------------------------|---------------|

|                                                              |                                           | Rev1.0        |

| Unit interval                                                | UI                                        | 400 ps        |

|                                                              |                                           | +/- 300 ppm   |

| Eye height of transition bits                                | $V_{TXS}$                                 | .274 V (min)  |

|                                                              |                                           | 1.2 V (max)   |

| Eye height of non-transition bits                            | $V_{TXS\_d}$                              | .253 V (min)  |

| Eye width with sample size of 10 <sup>6</sup> UI             | $T_{TXS}$                                 | 246 ps (min)  |

| Jitter eye opening at BER 10 <sup>-12</sup>                  |                                           | 233 ps (min)  |

| Maximum median-max jitter outlier with sample size of 106 UI | J <sub>TXA-MEDIAN-</sub><br>to-MAX-JITTER | 77 ps (max)   |

| Maximum median-max jitter outlier with sample size of 106 UI |                                           | 83.5 ps (max) |

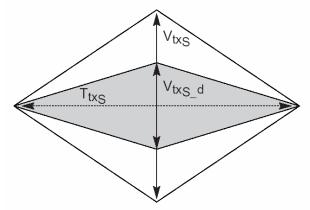

# 2.9.3 Express Module System Board Compliance Eye Diagrams

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 7.

Figure 6: ExpressModule system board compliance eye masks

# 2.10 PCI Express External Cabling Specifications

The specifications in this section are taken from the PCI Express External Cabling Specification. Its primary focus is the implementation of a cabled interconnect. Measurements in the PCE module support transmitter path and receiver path measurements. These measurements represent the test points at the transmitter end of the cable and the receiver end of the cable respectively.

## 2.10.1 External Cabling Transmitter Path Specifications

Table 8 is derived from Section 3.3.1 of the External Cabling Specification Rev. 0.4C.

Table 8 - Supported external cabling transmitter path measurements

| Parameter                            | Symbol           | Rev0.4C      |  |  |

|--------------------------------------|------------------|--------------|--|--|

| Unit interval                        | UI               | 400 ps       |  |  |

|                                      |                  | +/- 300 ppm  |  |  |

| Eye height of transition bits        | $V_{TXA}$        | .659 V (min) |  |  |

|                                      |                  | 1.2 V (max)  |  |  |

| Eye height of non-transition bits    | $V_{TXA\_d}$     | .456 V (min) |  |  |

| Eye width with sample size of 106 UI | T <sub>TXA</sub> | 309 ps (min) |  |  |

| Jitter eye opening at BER 10-12      |                  | 296 ps (min) |  |  |

## 2.10.2 Cable (Transmitter Side) Eye Diagrams

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 8.

Figure 7: Cable (transmitter side) compliance eye masks

# 2.10.3 External Cabling Receiver Path Specifications

Table 9 is derived from Section 3.3.2 of the External Cabling Specification Rev. 0.4C.

Table 9 - Supported CEM System Board Measurements

| Parameter                                        | Symbol       | Gen1         |  |  |  |

|--------------------------------------------------|--------------|--------------|--|--|--|

|                                                  |              | Rev1.0       |  |  |  |

| Unit interval                                    | UI           | 400 ps       |  |  |  |

|                                                  |              | +/- 300 ppm  |  |  |  |

| Eye height of transition bits                    | $V_{RXA}$    | .219 V (min) |  |  |  |

|                                                  |              | 1.2 V (max)  |  |  |  |

| Eye height of non-transition bits                | $V_{RXA\_d}$ | .200 V (min) |  |  |  |

| Eye width with sample size of 10 <sup>6</sup> UI | $T_{RXA}$    | 247 ps (min) |  |  |  |

| Jitter eye opening at BER 10 <sup>-12</sup>      |              | 234 ps (min) |  |  |  |

# 2.10.4 Cable (Receive Side) Eye Diagrams

The amplitude and jitter masks are derived from the amplitude and jitter specifications in Table 9.

Figure 8: Cable (receiver side) compliance eye masks

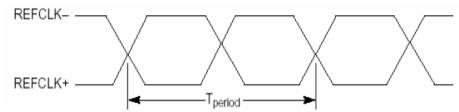

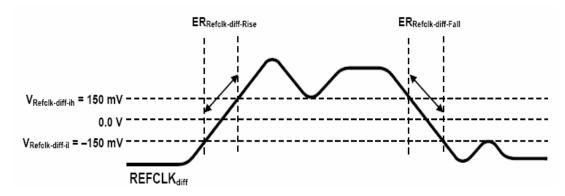

# 2.11 Reference Clock Compliance Specifications

Table 10 is derived from section 2.1 of the Gen1 Rev1.1 Electrical Mechanical Specifications (CEM) and Gen2 Base specifications.

Table 10 – Supported reference clock measurements

| Parameter                         | Symbol                  | Gen1            | Gen2            |  |  |

|-----------------------------------|-------------------------|-----------------|-----------------|--|--|

|                                   |                         | Rev1.1          | Rev0.3          |  |  |

| Rise edge rate                    | Rise Edge Rate          | 0.6 V/ns (min)  | 0.6 V/ns (min)  |  |  |

|                                   |                         | 4.0 V/ns (max)  | 4.0 V/ns (max)  |  |  |

| Fall edge rate                    | Fall Edge Rate          | 0.6 V/ns (min)  | 0.6 V/ns (min)  |  |  |

|                                   |                         | 4.0 V/ns (max)  | 4.0 V/ns (max)  |  |  |

| Differential input high voltage   | V <sub>IH</sub>         | 150 mV (max)    | 150 mV (max)    |  |  |

| Differential input low voltage    | V <sub>IL</sub>         | -150 mV (min)   | -150 mV (min)   |  |  |

| Absolute period (including jitter | T <sub>PERIOD_ABS</sub> | 9.847 ns (min)  | 9.997 ns (min)  |  |  |

| and spread spectrum)              |                         | 10.203 ns (max) | 10.053 ns (max) |  |  |

| Duty cycle                        | Duty Cycle              | 40% (min)       | 40% (min)       |  |  |

|                                   |                         | 60% (max)       | 60% (max)       |  |  |

| Maximum peak-peak filtered        | Jitter @ 10-12 BER      | 108 ps (max)    | Not             |  |  |

| phase jitter                      |                         |                 | Specified       |  |  |

| Maximum peak-peak filtered        | Jitter @ 10-6 BER       | 86 ps (max)     | Not             |  |  |

| phase jitter                      |                         |                 | Specified       |  |  |

| RMS jitter                        | T <sub>CLK_RJ</sub>     |                 | 3.1 ps (max)    |  |  |

# 3 Preparing to Take Measurements

# 3.1 Required Equipment

The following equipment is required to take the measurements:

- Oscilloscope Selection:

- o Gen1 (2.5 Gb/s) The PCI-SIG recommends a minimum of 6 GHz system BW for Gen1 Measurements. Tektronix models that meet this recommendation are: All the TDS6000B/C Series instruments and the TDS7704B.

- o Gen2 (5 Gb/s) It is recommended that >12 GHz system BW is used for Gen2. This ensures the 5<sup>th</sup> harmonic is represented in the measurements. Tektronix models that meet this recommendation are TDS6000C models.

- RT-Eye software (Opt. RTE) and PCI Express Compliance Module (PCE) installed.

- Probes probing configuration is MOI specific. Refer to each MOI for proper probe configuration.

- Test fixture breakout from transmitter to differential SMA connectors. A Compliance Base Board (CBB) used for add-in card compliance tests and a Compliance Load Board (CLB) used for system compliance tests are available through the PCI-SIG at the following URL: http://www.pcisig.com/specifications/ordering information/ordering information

- Test fixtures for notebook testing are available from the following URL: http://www.expresscard.org/web/site/testtools.jsp

# 3.2 Probing Options for Transmitter Testing

The first step is to probe the link. Use one of the following four methods to connect probes to the link.

Table 11 - Probing configurations for a PCI express link

|                          | Probing Configurations |              |                                          | Captured W | /aveforms            | Typical System Specifications |               |                          |               |                          |               |                          |               |                          |               |                          |

|--------------------------|------------------------|--------------|------------------------------------------|------------|----------------------|-------------------------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|

|                          |                        |              | Break<br>Serial<br>Link Channels<br>Used |            |                      | TDS6604/B                     |               | TDS7704B**               |               | TDS6804B                 |               | TDS6124C                 |               | TDS6154C                 |               |                          |

|                          |                        | Probe        |                                          | Channels   | Differential<br>Mode | Common<br>Mode                | Band<br>Width | Rise*<br>Time<br>(20-80) |

| SMA<br>Connection        | Α                      | 2 x TCA-SMA  | Υ                                        | 2          | Pseudo               | AC                            | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 12GHz         | 24ps                     | 15GHz         | 19ps                     |

|                          | В                      | 1 x P7380SMA | Υ                                        | 1          | True                 | No                            | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     |

| ECB<br>Pad<br>Connection |                        | 2 x P7260    | Y or N                                   | 2          | Pseudo               | AC/DC                         | 6GHz          | 53ps                     | 6GHz          | 56ps                     | 6GHz          | 56ps                     | 6GHz          | 56ps                     | 6GHz          | 56ps                     |

|                          | С                      | 2 x P7380    | Y or N                                   | 2          | Pseudo               | AC/DC                         | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     |

|                          |                        | 2 x P7313    | Y or N                                   | 2          | Pseudo               | AC/DC                         | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 12GHz         | 28ps                     | 12.5GHz       | 25ps                     |

|                          | D                      | 1 x P7380    | Y or N                                   | 1          | True                 | No                            | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     | 8GHz          | 35ps                     |

|                          | U                      | 1 x P7313    | Y or N                                   | 1          | True                 | No                            | 6GHz          | 53ps                     | 7GHz          | 43ps                     | 8GHz          | 35ps                     | 12GHz         | 28ps                     | 12.5GHz       | 25ps                     |

<sup>\*</sup> Typica

<sup>\*\* 10</sup>GS/s in Pseudo-differential

## 3.2.1 SMA Input Connection

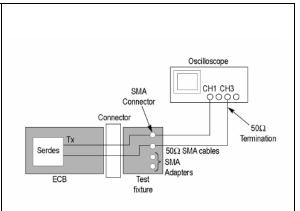

# 1. Two TCA-SMA inputs using SMA cables (Ch1) and (Ch3)

The differential signal is created by the RT-Eye software from the math waveform Ch1-Ch3. The Common mode AC measurement is also available in this configuration from the common mode waveform (Ch1+Ch3)/2. This probing technique requires breaking the link and terminating into a 50  $\Omega$ /side termination of the oscilloscope. While in this mode, the PCI Express SerDes will transmit the compliance test pattern. Ch-Ch de-skew is required using this technique because two channels are used. This configuration does not compensate for cable loss in the SMA cables. The measurement reference plane is at the input of the TCA-SMA connectors on the oscilloscope. Any cable loss should be measured and entered into the vertical attenuation menu for accurate measurements at the SMA cable attachment point.

#### **Probe Configuration A**

SMA Psuedo-differential

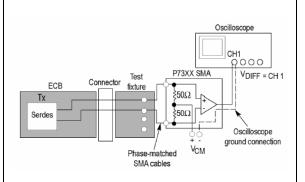

# 2. One P7380SMA differential active probe (Ch1)

The differential signal is measured across the termination resistors inside the P7380SMA probe. This probing technique requires breaking the link. While in this mode, the PCI Express SerDes will transmit the compliance test pattern. Matched cables are provided with the P7380 probe to avoid introducing de-skew into the system. Only one channel of the oscilloscope is used. The P7380SMA provides a calibrated system at the Test Fixture attachment point, eliminating the need to compensate for cable loss associated with the probe configuration A.

**Probe Configuration B**

SMA Input Differential Probe

## 3.2.2 ECB pad connection

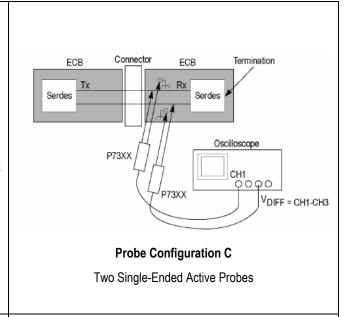

# 3. Two P7300 or P7260 active probes (Ch1) and (Ch3)

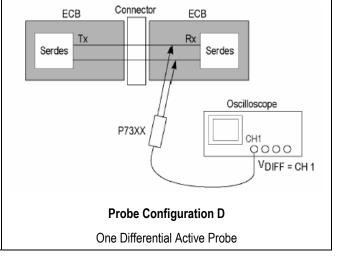

The differential signal is created by the RT-Eye software from the math waveform Ch1-Ch3. The Common mode AC measurement is also available in this configuration from the common mode waveform (Ch1+Ch3)/2. This probing technique can be used for either a live link that is transmitting data, or a link that has terminated into a "dummy load." In both cases, the single-ended signals should be probed as close as possible to the termination resistors on both sides with the shortest ground connection possible. Ch-Ch de-skew is required using this technique because two channels are used.

The differential signal is measured directly across the termination resistors. This probing technique can be used for either a live link that is transmitting data, or a link that is terminated into a "dummy load." In both cases, the signals should be probed as close as possible to the termination resistors. De-skew is not necessary because a single channel of the oscilloscope is used.

# 3.3 Initial Oscilloscope Setup

After connecting the DUT by following the proper probing configuration for the test, click **DEFAULT SETUP** and then **Autoset** to display the serial data bit stream.

# 3.4 Running the RT-Eye Software

1. On non-B or non-C model oscilloscopes (Example: TDS6604), Go to File > Run Application > RT-Eye Serial Compliance and Analysis. For B and C models (Example: TDS7704B, TDS6154C), go to App > RT-Eye Serial Compliance and Analysis.

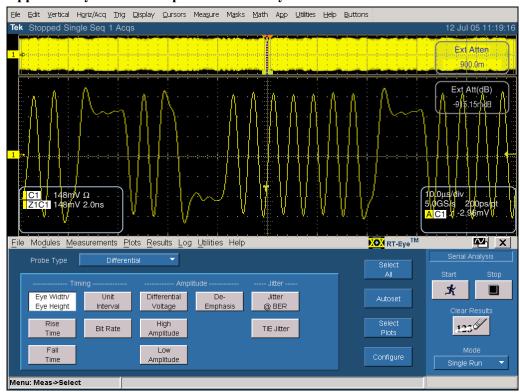

Figure 9: Default menu of the RT-Eye software

Figure 9 shows the oscilloscope display. The default mode of the software is the Serial Analysis module (Opt.RTE). This software is intended for generalized Serial Data analysis on 8B/10B encoded copper links.

2. Select the PCI Express Compliance Module from the **Modules** pull-down list.

Figure 10: Choosing PCI Express Compliance Module.

**Note:** If PCI Express does not appear in the list (as in Figure 10), the PCI Express Compliance Module (Opt. PCE) has not been installed.

The rest of this MOI document details the use of the PCI Express Compliance Module to perform electrical compliance measurements.

For additional information, refer to the online help for the RT-Eye software available through the Serial Analysis Module help menu.

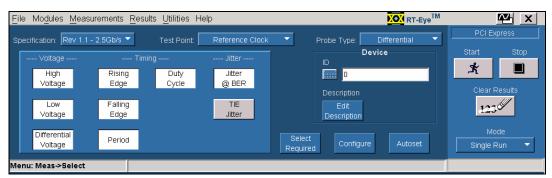

# 3.5 Configuring the Software to take measurements

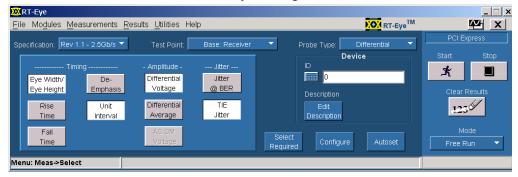

Before you take compliance measurements, configure the software as follows:

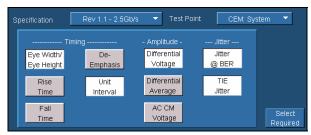

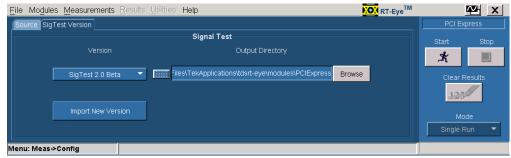

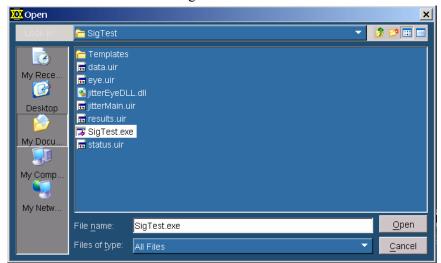

#### 3.5.1 Select Standard

Using the Specification pull-down menu, select the desired specification to be measured.

The selections are:

Rev1.0a - 2.5 Gb/s

Rev1.1 - 2.5 Gb/s

Gen2 - 5 Gb/s

Use SIG-TEST – refer to Section 8

#### 3.5.2 Select Test Point

Use the Test Point pull-down list to select the desired test point.

Selections in the Test Point menu are dependent on which specification is selected. The selections are as follows:

#### If Rev1.0a – 2.5 Gb/s is selected as Standard:

Receiver

Driver

CEM: Add-In

CEM: System

Mobile LP: Transmitter

User Defined – Using Dynamic Test Points – See Section 9 for definition

#### If Rev1.1 - 2.5 Gb/s is selected as Standard:

Base: Transmitter

Base: Receiver

CEM: Add-In

CEM: System

Cable: Transmitter

Cable: Receiver

ExpressModule: System TX ExpressModule: TX Path

User Defined – Using Dynamic Test Points – See Section 9 for definition

Reference Clock

#### If Gen2 – 5Gb/s is selected as Standard:

Base: Transmitter

Base: Receiver

User Defined – Using Dynamic Test Points – See Section 9 for definition

Reference Clock

## 3.5.3 Select Probe Type

Using the Probe Type pull-down menu, select the desired probing configuration.

The selections are:

Single-Ended – Select if Pseudo-differential (probing configurations A or C from Section 3.2) is being used

Differential – Select use if true differential (probing configurations B or D from Section 3.2) is being used.

#### 3.5.4 Select Measurements

In the **Measurement > Select** menu, select the desired measurements. Measurements can be selected either manually or as a group by using **Select Required**. If a measurement has a pass/fail limit associated with it in the test point file, it will be selected when **Select Required** is clicked. Measurements with pass/fail limits will show up in the **Results Summary** panel when the compliance test is run. Measurement results of selected measurements, which do not have limits associated with them can be viewed in the **Results Details** panel.

Figure 11: Measurement Select menu

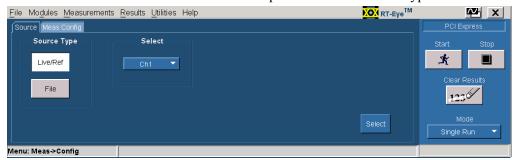

## 3.5.5 Configure Source of Waveforms

Use the **Measurements > Configure > Source** menu to select the source of the measured data.

Figure 12: Configure Source menu

Source selections are dependent on which probe type is selected. The selections are as follows:

## If **Differential** is selected as **Probe Type**:

Live/Ref source selection (uses single differential signal as data source)

- o Live channel selections-Ch1, Ch2, Ch3, Ch4

- o Reference waveform selections–Ref1, Ref2, Ref3, Ref4

File source selection

o File selection – Uses one saved .csv as file as differential data source

### If **Single-Ended** is selected as **Probe Type**:

Live/Ref source selection (uses two single-ended signals as data source)

- o Live channel selections—(Ch1-Ch3), (Ch1-Ch4), (Ch2-Ch3), (Ch2-Ch4)

- o Reference waveform selections –Refx-Refy, where x and y are integers 1-4

File source selection

o File selection–Uses two saved .csv files as single-ended data source

## 3.5.6 Configure Clock Recovery

Use the **Measurements> Configure> Meas Config** menu to select the type of clock recovery to be used.

Figure 13: Measurement Configuration menu

Selections in the General Config panel depend on the specification that has been chosen. The selections are defined as follows:

#### If Rev1.0a – 2.5 Gb/s is selected as Standard:

SSC (Scan Off) – 3500:250 clock recovery with no waveform scanning is used.

SSC (Scan On) – 3500:250 clock recovery with waveform scanning is used.

#### If Rev1.1 – 2.5 Gb/s is selected as Standard:

SSC (Scan Off) – 3500:250 clock recovery with no waveform scanning is used.

SSC (Scan On) – 3500:250 clock recovery with waveform scanning is used.

Clean Clock – A 1st Order PLL with a corner frequency of 1.5 MHz is used to recover the clock.

#### If Gen2 - 5 Gb/s is selected as Standard:

SSC (Scan Off) – 3500:250 clock recovery with no waveform scanning is used.

SSC (Scan On) – 3500:250 clock recovery with waveform scanning is used.

Clean Clock – A 1st Order PLL with a corner frequency of 3 MHz is used to recover the clock.

#### When to use SSC selection:

SSC is the only selection in Rev1.0a and is optional in the Rev1.1 and Gen2. It is to be used when a clean clock source is not available or if SSC is turned on in a system. The following describes how the clock is recovered using this technique:

The "SmartGating" feature of the RT-Eye application is used to set up a software clock recovery window and an analysis window. This feature is available (and configurable) outside the PCI Express Compliance Module in the Measurements> Configure> SmartGating menu of the Serial Analysis module.

The clock recovery window is 3500 consecutive UIs and the Mean of the UIs is used as the reference clock. The first 3500 UIs in the acquisition are used.

An analysis window is established to be 250 UIs centered in the 3500 UI clock recovery window. The placement of mask is based on the median of the 250 UI analysis windows.

Optionally, the "Scan On" check box can be selected. When checked, the clock recovery and analysis

waveform will scan the waveform by stepping the 3500:250 window across the waveform in 100 UI

steps. This technique is same as the PCI-SIG SigTest software, used to determine compliance over a

single shot waveform.

#### When to use the Clean Clock selection:

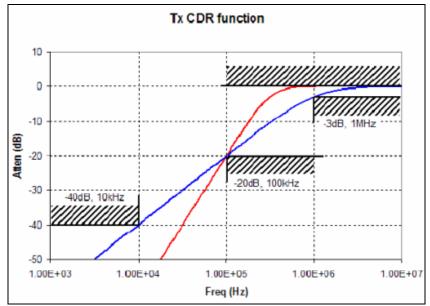

The clean clock selection is not available in Rev1.0a and is optional in the Rev1.1 and Gen2. It is to be used when a clean reference clock is available. As defined in the base specification, the clock recovery function to be used is a 1st order PLL with a corner frequency of 1.5 MHz (Rev1.1) and 1 MHz (Gen2). In the Gen2 specification, a mask function is provided. The PCI Express module implements a first order PLL with a 1 MHz cutoff frequency. The first order PLL can be changed to a second order PLL by using a dynamic test point file as described in section 9.

Figure 14: Clock recovery mask function in Gen2 base specification

# 3.5.7 Configure Plots

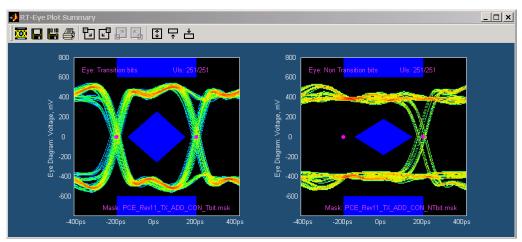

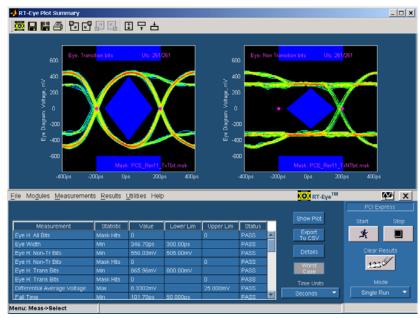

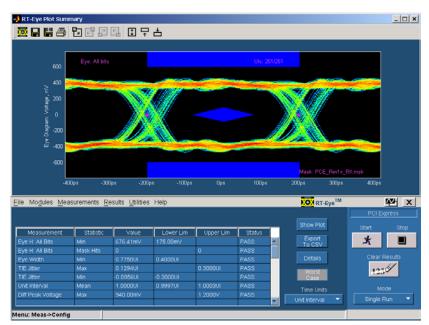

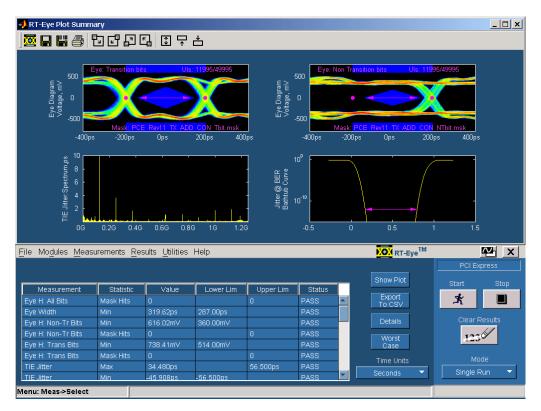

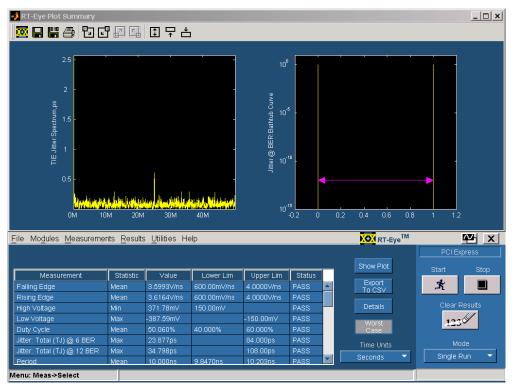

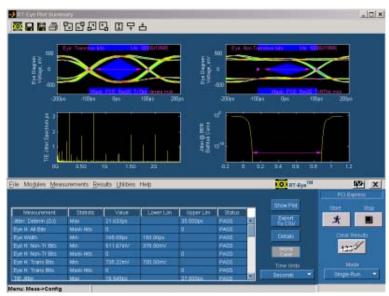

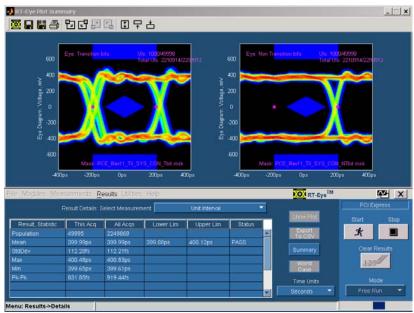

The plots in the PCI Express Module are configured automatically. If the **Jitter@BER** measurement is not selected, eye diagrams with masks will be displayed in the **Plot Summary** window (Figure 15a). The eye diagram can either be a double plot showing transition bit and non-transition bit or can be a single plot showing all bits depending on the test point selected.

Figure 15a: Plot Summary when Jitter@BER measurement is not selected

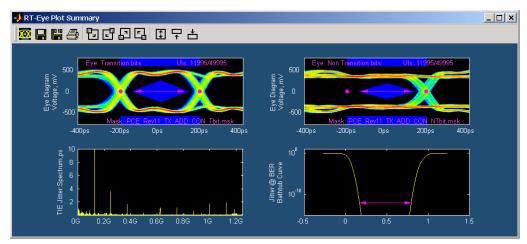

If the **Jitter@BER** measurement is selected, then a Jitter Spectrum and Bathtub Curve are added to the **Plot Summary** window.

Figure 15b: Plot Summary when the Jitter@BER measurement is selected

# 4 PCI Express Transmitter Compliance Testing

This section provides the Methods of Implementation (MOIs) for Transmitter tests using a Tektronix real-time oscilloscope, probes, and the RT-Eye compliance software.

# 4.1 Probing the link for TX compliance

Use probing configuration B from Section 3.2. Connect the positive leg of the differential signal to the '+' SMA connector and the negative leg of the differential signal to the '- 'SMA connector on the P7380SMA differential probing system.

Alternatively, use probe configuration A, to connect Ch1 and Ch3 to the inputs of an oscilloscope that has 20 GS/s sample rate available on two channels (TDS66004 or TDS6000B Series).

Since the link is broken and terminated into a 50  $\Omega$  load, the compliance pattern is defined in the base specification will be transmitted automatically.

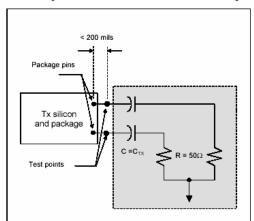

# 4.2 TX Compliance Test Load

The compliance test load for driver compliance is shown in the base specification.

Figure 16: Driver compliance test load

# 4.3 Running a Transmitter (TX) Compliance Test

The MOI for each of the transmitter measurements is documented in the following sections. All transmitter compliance measurements can be selected and run simultaneously with the same acquisition. See Section 3.5 for more info on configuring the module to make measurements.

To perform a compliance test of all transmitter measurements:

- 1. Select the desired **Specification** from the Specification pull-down list.

- 2. Select the desired **Test Point** from the Test Point pull-down list.

- 3. In the Measurement Select menu (Figure 17), choose Single-Ended (for probe configuration A defined in Section 3) or Differential (for probe configurations B defined in Section 3) as the probe type.

- 4. Click **Configure** to configure the source and clock recovery method to be used.

- 5. Click **Source** tab to configure the data source.

- 6. Click **General Config** tab to select the desired clock recovery method.

- 7. Return the Measurement Select menu by clicking **Select**.

Figure 17: Measurements Select menu setup

- 8. Click **Select Required** and/or select desired measurements manually.

- 9. Click **Autoset** in the RT-Eye Measurement Select menu. This will automatically set up the oscilloscope vertical, horizontal, and measurement reference levels for the compliance test.

- 10. Click Start.

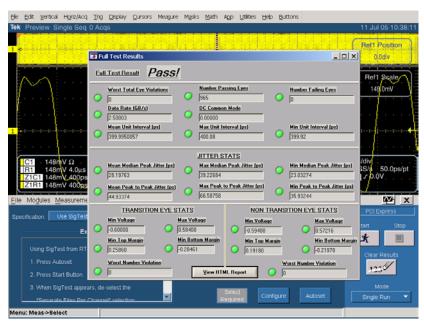

Figure 18 shows the result of a Transmitter Compliance test on a signal that passes the driver tests at all three TX compliance test points.

Figure 18: Result of a successful transmitter compliance test

#### 4.3.1 TX Unit Interval Measurement MOI

## **Test Definition Notes from the Specification:**

- UI (Unit Interval) is specified to be +/- 300 ppm

- UI does not account for SSC dictated variations

**Definition:** UI is defined in the base specification.

#### **Limits:**

Refer to Table 2 for specified limits on UI measurement.

#### **Test Procedure:**

Ensure that UI is selected in the **Measurements> Select** menu.

### **Measurement Algorithm:**

This measurement is made over the Analysis Window of 250 consecutive bits defined in Section 3.4 (Base specification).

The Unit Interval measurement calculates the cycle duration of the recovered clock.

$$UI(n) = t_{R-CLK}(n+1) - t_{R-CLK}(n)$$

$$UI_{AVG} = Mean(UI(n))$$

Where:

$t_{R-CLK}$  is a recovered clock edge

*n* is the index to UI in the waveform

## 4.3.2 TX Differential Pk-Pk Output Voltage MOI

#### **Definition:**

$V_{\it TX-DIFFp-p}$  (Differential Output Pk-Pk Voltage) is defined in the base specification. This measurement is solved by two measurements. One is Differential Peak Voltage measurement and the other is Eye Height: Transition Bits measurement. If you select Differential Voltage and Eye Width/Eye Height, you will get five measurements: Eye Height, Eye Height: Transition Bits, Eye Height: Non-Trans Bits, Eye Width and Differential Peak Voltage.

### **Test Definition Notes from the Specification:**

-

$$V_{{\it TX-DIFF}p-p} = 2* |V_{{\it TX-D+}} - V_{{\it TX-D-}}|$$

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification and measured over specified number of UIs. Also refer to the transmitter compliance eye diagram shown in the base specification.

#### **Limits:**

Refer to Table 2 for specified limits on the  $V_{\it TX-DIFFp-p}$  measurement.

#### **Test Procedure:**

Ensure that **Differential Voltage** and **Eye Width/Eye Height** are selected in the **Measurements> Select** menu.

#### **Measurement Algorithm:**

**Differential Peak Voltage Measurement:** The Differential Peak Voltage measurement returns two times the larger of the Min or Max statistic of the differential voltage waveform.

$$V_{DIFF-PK} = 2 * Max(Max(v_{DIFF}(i)); Min(v_{DIFF}(i)))$$

Where:

i is the index of all waveform values

$v_{DIFF}$  is the differential voltage signal

**Eye Height Measurement:** The measured minimum vertical eye opening at the UI center as shown in the plot of the eye diagram. There are three types of eye height values:

### **Eye Height:**

$$V_{\rm EYE-HEIGHT} = V_{\rm EYE-HI-MIN} - V_{\rm EYE-LO-MAX}$$

#### Where:

$V_{EYE-HI-MIN}$  is the minimum of the high voltage at mid UI

$V_{\it EYE-LO-MAX}$  is the maximum of the low voltage at mid UI

#### **Eye Height – Transition:**

$$V_{\textit{EYE-HEIGHT-TRAN}} = V_{\textit{EYE-HI-TRAN-MIN}} - V_{\textit{EYE-LO-TRAN-MAX}}$$

### Where:

$V_{\it EYE-HI-TRAN-MIN}$  is the minimum of the high transition bit eye voltage at mid UI

$V_{EYE-LO-TRAN-MAX}$  is the maximum of the low transition bit eye voltage at mid UI

## **Eye Height – Non-Transition:**

$$V_{\textit{eye-height-ntran}} = V_{\textit{eye-hi-ntran-min}} - V_{\textit{eye-lo-ntran-max}}$$

#### Where:

$V_{\it EYE-HI-NTRAN-MIN}$  is the minimum of the high non-transition bit eye voltage at mid UI

$V_{\it EYE-LO-NTRAN-MAX}$  is the maximum of the low non-transition bit eye voltage at mid UI

## 4.3.3 TX De-Emphasized Differential Output Voltage (Ratio) MOI

#### **Definition:**

$V_{TX-DE-RATIO}$  (De-Emphasized Differential Output Voltage (Ratio)) is defined in the base specification.

# **Test Definition Notes from the Specification:**

- This is the ratio of the  $V_{\mathit{TX-DIFF}p-p}$  of the second and following bits after a transition divided by the  $V_{\mathit{TX-DIFF}p-p}$  of the first bit after a transition.

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification over the specified number of UIs. Also refer to the transmitter compliance eye diagram shown the base specification.

#### **Limits:**

Refer to Table 2 for specified limits on the  $V_{{\it TX-DE-RATIO}}$  measurement.

#### **Test Procedure:**

Ensure that **De-Emphasis** is selected in the **Measurements** > **Select** menu.

### **Measurement Algorithm:**

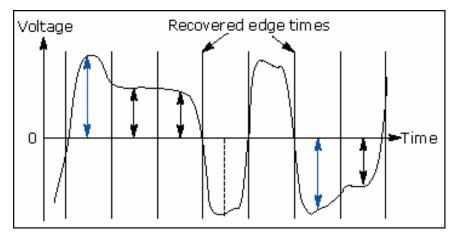

The de-emphasis measurement calculates the ratio of any non-transition eye voltage (2<sup>nd</sup>, 3<sup>rd</sup>, etc. eye voltage succeeding an edge) to its nearest preceding transition eye voltage (1<sup>st</sup> eye voltage succeeding an edge). In Figure 19, it is the ratio of the black voltages over the blue voltages. The results are given in dB.

Figure 19: De-emphasis measurement

$$DEEM(m) = dB \left( \frac{v_{EYE-HI-NTRAN}(m)}{v_{EYE-HI-TRAN}(n)} \right)$$

or

$$DEEM(m) = dB \left( \frac{v_{EYE-LO-NTRAN}(m)}{v_{EYE-LO-TRAN}(n)} \right)$$

Where:

$v_{EYE-HI-TRAN}$  is the high voltage at mid UI following a positive transition

$v_{EYE-LO-TRAN}$  is the low voltage at mid UI following a negative transition

$v_{EYE-HI-NTRAN}$  is the high voltage at mid UI following a positive transition bit

$v_{EYE-LO-NTRAN}$  is the low voltage at mid UI following a negative transition bit

*m* is the index for all non-transition UIs

n is the index for the nearest transition UI preceding the UI specified by m

# 4.3.4 Minimum TX Eye Width MOI

#### **Definition:**

$T_{TX-EYE}$  (Minimum TX Eye Width) is defined in the base specification. Note that the definition of the Eye width changes from Rev1.x to the Gen2. See Section 4.3.9 for the Gen2 definition. For Gen1, the Eye width is a histogram-based measurement that is defined as follows.

#### **Test Definition Notes from the Specification:**

- The maximum Transmitter jitter can be derived as  $T_{TXMAX-JITTER} = 1 T_{TX-EYE}$

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification and measured over the specified number of UIs. Also refer to the transmitter compliance eye diagram shown in the base specification.

**Note:** The median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

#### **Limits:**

Refer to Table 2 for specified limits on the  $T_{TX-EYE}$  measurement.

#### **Test Procedure:**

Ensure that **De-Emphasis** is selected in the **Measurements> Select** menu.

### **Measurement Algorithm:**

The *measured* minimum horizontal eye opening at the zero reference level as shown in the eye diagram.

$$T_{EYE-WIDTH} = UI_{AVG} - TIE_{Pk-Pk}$$

Where:

$UI_{AVG}$  is the average UI

$TIE_{Pk-Pk}$  is the Peak-Peak TIE

### 4.3.5 TX Median-to-Max Jitter MOI

### **Definition:**

$T_{TX-EYEMEDIAN-to-MAXJITTER}$  (maximum time between the jitter median and maximum deviation from the median.) is defined in Rev1.0a of the base specification.

### Limits:

Refer to Table 2 for  $T_{TX-EYEMEDIAN-to-MAXJITTER}$  measurement.

### **Test Procedure:**

Ensure that **TIE** is selected in the **Measurements> Select** menu.

### **Measurement Algorithm:**

The measured time difference between a data edge and a recovered clock edge.

$$tie(n) = t_{R-DAT}(n) - t_{DAT}(n)$$

Where:

$t_{DAT}$  is the original data edge

$t_{R-DAT}$  is the recovered data edge (for example, the recovered clock edge corresponding to the UI boundary of  $t_{DAT}$ )

n is the index of all edges in the waveform

### 4.3.6 TX Output Rise/Fall Time MOI

### **Definition:**

$T_{TX-RISE}$ ,  $T_{TX-RISE}$  (D+/D- TX Output Rise/Fall Time) is defined in the base specification.

### **Test Definition Notes from the Specification:**

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification and measured over the specified number of TX UIs.

- Measured between 20-80% at transmitter package pins into a test load for both  $V_{TX-D+}$  and  $V_{TX-D-}$

#### **Limits:**

Refer to Table 2 for specified limits on  $T_{TX-RISE}$ ,  $T_{TX-FALL}$  measurements.

#### **Test Procedure:**

Ensure that **Rise Time** and **Fall Time** are selected in the **Measurements> Select** menu.

**Note:** Rise/Fall time D+ and D- measurements show up when the probe type is single-ended. Rise Time measurements show up when differential probe type is used. Error in Rise/Fall time measurements includes bandwidth limitations of the system in some cases.

### **Measurement Algorithm:**

Rise/Fall time is limited to only rising or falling edges of consecutive transitions for transmitter measurements. Rise/Fall Time is taken independently on each single-ended waveform sources when you use two single-ended probes as the signal source. Differential signal Rise/Fall Time show up when you select Differential probe type.

**Rise Time:** The Rise Time measurement is the time difference between when the  $V_{REF-HI}$  reference level is crossed and the  $V_{REF-LO}$  reference level is crossed on the rising edge of the waveform.

$$t_{RISE}(n) = t_{HI+}(i) - t_{LO+}(j)$$

Where:

$t_{RISE}$  is a Rise Time measurement

$t_{HI+}$  is a set of  $t_{HI}$  for rising edges only

$t_{LO+}$  is a set of  $t_{LO}$  for rising edges only

i and j are indexes for nearest adjacent pairs of  $t_{LO_+}$  and  $t_{HI_+}$ .

*n* is a the index of rising edges in the waveform

Rise Time for  $v_{D+}(t)$  is as follows:

$$t_{D+RISE}(n) = t_{D+HI+}(i) - t_{D+LO+}(j)$$

and for  $v_{D-}(t)$

$$t_{D-FALL}(n) = t_{D-LO-}(i) - t_{D-HI-}(j)$$

**Fall Time:** The Fall Time measurement is the time difference between when the  $V_{REF-HI}$  reference level is crossed and the  $V_{REF-LO}$  reference level is crossed on the falling edge of the waveform.

$$t_{FALL}(n) = t_{LO-}(i) - t_{HI-}(j)$$

Where:

$t_{FALL}$  is a Fall Time measurement

$t_{HI}$  is set of  $t_{HI}$  for falling edge only

$t_{LO}$  is set of  $t_{LO}$  for falling edge only

*i* and *j* are indexes for nearest adjacent pairs of  $t_{LO-}$  and  $t_{HI-}$ .

n is the index to falling edges in the waveform

Fall Time for  $v_{D+}(t)$  is as follows:

$$t_{D+FALL}(n) = t_{D+LO-}(i) - t_{D+HI-}(j)$$

and for  $v_{D}(t)$

$$t_{D-FALL}(n) = t_{D-LO-}(i) - t_{D-HI-}(j)$$

### 4.3.7 TX AC Common Mode Output Voltage MOI

### **Definition:**

$V_{TX-CM-ACp}$  (RMS AC Pk Common Mode Output Voltage) is defined in Rev1.0a Base Specification. The nomenclature ACp is retained to be consistent with the specification. However, the measurement is defined and reported by the PCI Express module as an RMS value, not a Pk value.

### **Test Definition Notes from the Specification:**

$$V_{\mathit{TX-CM-ACp}} = RMS(|\frac{V_{\mathit{TX-D+}} + V_{\mathit{TX-D-}}}{2}| - V_{\mathit{TX-CM-DC}})V_{\mathit{TX-CM-DC}} = DC_{(avg)}of |\frac{V_{\mathit{TX-D+}} + V_{\mathit{TX-D-}}}{2}|$$

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification and measured over the specified number of TX UIs.

#### Limits:

Refer to Table 2 for specified limits on  $V_{\mathit{TX-CM-ACp}}$  measurement.

### **Test Procedure:**

Ensure that AC CM Voltage is selected in the Measurements> Select menu.

**Note:** This measurement is available only when the probe type is single-ended.

### **Measurement Algorithm:**

**AC CM RMS Voltage:** The AC Common Mode RMS Voltage measurement calculates the RMS statistic of the common mode voltage waveform with the DC value removed.

$$v_{AC-RMS-CM}(i) = RMS(v_{AC-M}(i))$$

Where:

*i* is the index of all waveform values

$v_{AC-RMS-CM}$  is the RMS of the AC common mode voltage signal

$v_{AC-M}$  is the AC common mode voltage signal

### 4.3.8 TX Delta DC Common Mode Voltage MOI

### **Definition:**

$V_{\it TX-CM-DC-LINE-DELTA}$  (Absolute Delta of DC Common Mode Voltage between D+ and D-) is defined in the base specification.

### **Test Definition Notes from the Specification:**

$$|V_{TX-CM-DC-D+} - V_{TX-CM-DC-D-}| \le 25mV$$

$V_{TXCM-DC-D+} = DC_{(avg)}of |V_{TX-D+}|$

$V_{TX-CM-DC-D-} = DC_{(avg)}of |V_{TX-D-}|$

- Specified at the measurement point into a timing and voltage compliance test load as shown in the base specification and measured over the specified number of UIs.

### **Limits:**

Refer to Table 2 for specified limits on  $V_{\mathit{TX-CM-DC-LINE-DELTA}}$  measurement.

### **Test Procedure:**

Ensure that **Differential Average** is selected in the **Measurements> Select** menu.

### **Measurement Algorithm:**

The **Differential Average** measurement returns the mean of the differential voltage waveform.

$$V_{DIFF-AVG} = Mean(v_{DIFF}(i))$$

Where:

i is the index of all waveform values

*v<sub>DIFF</sub>* is the differential voltage signal

### 4.3.9 TX Total Jitter@BER MOI

#### **Definition:**

The jitter eye opening  $T_{TX-EYE}$  is re-defined Gen2 specification to statistical relevance to  $10^{-12}$  BER. A detailed definition can be found in section 4.4.8 of the Gen2 base specification.

### Test Definition Notes from the Gen2 (Rev0.3) Specification:

- Does not include SSC or Refclk. Jitter Includes Rj at 10<sup>-12</sup>.

- Transmitter jitter is measured by driving the transmitter under test with a low jitter "ideal" clock and connecting the DUT to a reference load.

- Transmitter jitter must be post-processed with a filtering function that represents the worst case CDR tracking BW.

### **Limits:**

Refer to Table 2 for specified limits on the  $T_{TX-EYE}$  measurement.

#### **Test Procedure:**

Ensure that **Jitter@BER** is selected in the **Measurements> Select** menu.

### **Measurement Algorithm:**

Total jitter in the PCI Express Compliance Module uses the Arbitrary Pattern Jitter Algorithm in RT-Eye to establish  $T_{TX-EYE}$ . To understand the complete algorithm, one must understand RT-Eye's spectrum approach to jitter measurements.

### 4.3.10 Spectrum Analysis Based Rj/Dj Separation on Repeating Pattern

Dj components can be identified in a jitter spectrum under a set of conditions. PJ will appear as spectral impulses regardless of conditions. DDJ and DCD will appear as spectral impulses provided that the data signal is a repeating pattern. The frequencies of DDJ and DCD spectral impulses are at harmonics of the (Bit Rate / Pattern length). The remaining spectral energy is attributed to Rj. Dj components are spectrally separated from Rj.

The Dj measurement is the peak-to-peak value of the inverse Fourier transform of the deterministic jitter spectral components, Tj is the total jitter which is composed of Dj and Rj. The Tj measurement calculates the peak-to-peak value of the total jitter. Rj is assumed to be near-Gaussian. The Rj measurement is the calculated RMS value of random jitter.

A Jitter PDF is formed by convolving a Gaussian distribution of Rj and Histograms of Dj. A Bathtub curve is calculated from the left and right side CDFs of the Jitter PDF. The Bathtub curve will yield TJ and Eye Opening ( $T_{EYE-OPEN}$ ).

The application calculates the measurements using the following equations:

$$Dj = Max(Dj^{Time}) - Min(Dj^{Time})$$

$$Rj = RMS(tie - Dj^{Time})$$

$TJ_{PDF} = normalizedHistogram(Dj) * GaussianPDF(Rj)$

$$TJ = TJ_{Max} - TJ_{MIN}$$

$$T_{EYE-OPEN} = UI - TJ$$

Where:

Dj is the deterministic jitter

Rj is the random jitter

TJ is the total jitter

$TJ_{PDF}$  is the PDF of the total jitter

$TJ_{MIN}$  is the minimum value at the bathtub curve at a given BER

$TJ_{\mathit{Max}}$  is the maximum value at the bathtub curve at a given BER

$Dj^{Time}$  is the is the time domain record of the Dj component of jitter obtained by performing an inverse FFT of the Dj components of the TIE spectrum.

tie is the time domain record of measured TIE jitter.

Additionally, Dj is further decomposed as follows:

$$PJ = Max(PJ^{Time}) - Min(PJ^{Time})$$

$$DCD = \left| Mean(DCDDDJ_{Rise}^{Time}) - Mean(DCDDDJ_{Fall}^{Time}) \right|$$

$$DDJ = Max(DCDDDJ^{Time}) - Min(DCDDDJ^{Time}) - DCD$$

Where:

PJ is the periodic jitter

DCD is the duty cycle jitter

DDJ is the data dependent (or ISI) jitter

$PJ^{Time}$  is the time domain record of the PJ component of jitter obtained by performing an inverse FFT of the PJ components of the TIE spectrum.

$DCDDDJ^{Time}$  is the time domain record of the DCD + DDJ component of jitter obtained by performing an inverse FFT of the DCD + DDJ components of the TIE spectrum.

$DCDDDJ_{Rise}^{Time}$  is  $DCDDDJ^{Time}$  on rising edges only.

$DCDDDJ_{Fall}^{Time}$  is  $DCDDDJ^{Time}$  on falling edges only.

### 4.3.11 Arbitrary Pattern Analysis Based Rj/Dj Separation

When data pattern is non-repeating, PJ still has a spectrum of impulses, while DCD+DDJ no longer has a spectrum of impulses. Therefore, Dj no longer has a spectrum of impulses.

The DCD+DDJ value is obtained through the arbitrary data pattern analysis method that is based on the assumption that any given bit is affected by a finite number of preceding bits. By averaging all events where the current bit is preceded by a particular bit sequence, for example the current bit is preceded by the bit sequence 1001101, the DCD+DDJ with such a pattern is obtained since PJ and RJ are not correlated to a particular data sequence and thus are averaged out.

If each bit is assumed to be affected by N preceding bits, there are a total of 2<sup>N</sup> possible data sequences. The sequence length N is set to 5 in the PCI Express module (user configurable in the Serial Analysis module) because PCI Express is 8b/10b encoded. To get statistically sound average values, a population limit of 50 is set in the PCI Express module (user configurable in the Serial Analysis module) that prevents using an average value without enough population. Only DCD+DDJ values obtained from data sequences with a population above the limit are used to calculate DCD+DDJ values.

After each edge is associated with a DCD+DDJ value, with known total jitter, the PJ+Rj value for each bit is then obtained by subtracting DCD+DDJ from TJ.

Separation of DDJ and DCD from DCD+DDJ is the same as that in the spectrum based Rj/Dj separation method.

PJ and Rj are then separated from PJ+Rj and use the spectrum analysis method. PJ has a spectrum of impulses, and Rj has a flat spectrum. All the edges whose DCD+DDJ can not be determined because of their associated data sequences have low populations and are treated as if there are no edges when performing PJ and Rj separation.

The histogram of Dj is a convolution of the histogram of DCD+DDJ and the histogram of PJ.

All other aspects of the arbitrary pattern analysis based Rj/Dj separation are the same as those of the spectrum analysis based Rj/Dj separation.

### 4.3.12 TX Deterministic MOI (Using Dual-Dirac Model)

### **Definition:**

Deterministic jitter  $t_{TX-DJ-DD}$  using the Dual-Dirac model is defined in Section 4.4.8 of the Gen2 Base Specification.

### **Test Definition Notes from the Gen2 (Rev0.3) Specification:**

- De-emphasis effects must be filtered out as a post processing operation. This parameter is measured by accumulating a record length of  $10^6$  samples while the DUT outputs a compliance pattern.

#### Limits:

Refer to Table 2 for specified limits on Common the  $t_{TX-DJ-DD}$  measurement.

### **Test Procedure:**

Ensure that **Jitter@BER** is selected in the **Measurements**> **Select** menu.

### 4.3.13 Ri/Di Separation Based on Dual Dirac Model

Dual Dirac model based Rj/Dj separation method fits the Bathtub curve to a theoretical model of Rj and Dj where Rj is assumed to have a Gaussian distribution, Dj is assumed to have a distribution of two Dirac impulses with the same height. Curve fitting at different BER levels in Bathtub curve yields the standard deviation value of Rj and peak-to-peak value of Dj. The Bathtub curve is obtained from the spectrum analysis based or the arbitrary pattern analysis based Rj/Dj separation methods. Rj and Dj based on the Dual-Dirac model can be denoted as  $RJ_{\it g}$  and  $DJ_{\it dd}$ .

After  $RJ_g$  and  $DJ_{dd}$  are obtained, Tj can be calculated using

$$TJ(BER) = 2Q(BER) \times RJ_g + DJ_{dd}$$

where Q is the function of BER that has a value of about 7 when  $BER = 10^{-12}$ . Eye opening is computed in the same way as it is computed in the spectrum analysis based Rj/Dj separation.

Dual Dirac model based Rj/Dj separation method is used in PCI-Express module and FB-DIMM module.

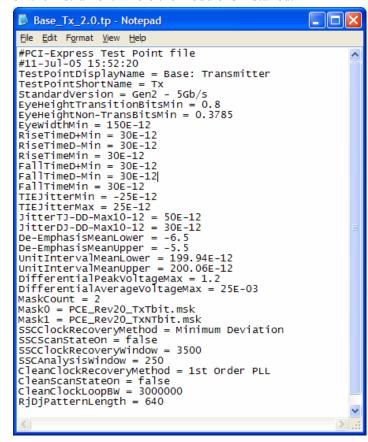

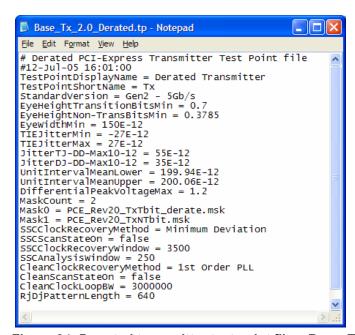

Usually, actual Dj does not have a pure Dual-Dirac distribution. So the value of  $RJ_g$  is often greater than the value of Rj obtained from the spectrum analysis based or the arbitrary pattern analysis based Rj/Dj separation. The value of  $DJ_{dd}$  is often less than that of its corresponding one.