SDLA Serial Data Link Analysis Printable Online Help

SDLA Serial Data Link Analysis Printable Online Help Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are protected by national copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Compiled Online Help Part number: 076-0173-02.

Online help version: 3.0

· · · · · ·

July 29, 2011

#### **Contacting Tektronix**

Tektronix, Inc. 14150 SW Karl Braun Drive P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- **I** In North America, call 1-800-833-9200.

- **Worldwide**, visit www.tektronix.com to find contacts in your area.

# **Table of Contents**

| Welcome                                                           |    |  |

|-------------------------------------------------------------------|----|--|

| Product Overview                                                  | 1  |  |

| Software Updates from the Tektronix Web Site                      | 2  |  |

| Conventions                                                       | 2  |  |

| Getting Started                                                   |    |  |

| Requirements and Installation.                                    | 3  |  |

| Signal Path Window Overview                                       | 3  |  |

| Configuring Blocks                                                | 6  |  |

| Choosing the Tx or Rx Configuration                               | 9  |  |

| Display Frequency and Time Domain Plots                           | 10 |  |

| Application File Types and Locations                              | 15 |  |

| Operating Basics                                                  |    |  |

| Fixture and Channel Blocks                                        | 17 |  |

| Emphasis Block                                                    | 20 |  |

| Equalizer Block (available with Option SLA)                       |    |  |

| Equalizer Block Overview                                          | 21 |  |

| Running the Equalizer                                             |    |  |

| Adjusting the FFE/DFE Equalizer to Improve Signal Recovery        |    |  |

| Adjusting the CTLE Equalizer to Improve Signal Recovery           | 27 |  |

| Renormalization of S-Parameters to Different Reference Impedances | 30 |  |

| Filter Files and Options                                          | 33 |  |

| Running a Test                                                    | 35 |  |

| GPIB Remote Control                                               |    |  |

| Using GPIB Remote Control                                         | 37 |  |

| GPIB Commands                                                     | 38 |  |

| APPLICATION:ACTIVATE "Serial Data Link Analysis"                  | 38 |  |

| VARIABLE:VALUE? "sdla"                                            | 39 |  |

| VARIABLE: VALUE "sdla", "p:analyze"                               | 39 |  |

| VARIABLE: VALUE "sdla", "p:apply"                                 | 40 |  |

| VARIABLE: VALUE "sdla", "p:bitrate: < value>"                     | 40 |  |

| VARIABLE:VALUE "sdla", "p:exit"                                   | 40 |  |

| VARIABLE: VALUE "sdla", "p:recall: < path and file name > "       | 41 |  |

| VARIABLE: VALUE "sdla", "p:source: <source/> "                    | 41 |  |

| VARIABLE:VALUE "sdla", "p:tx"   "p:rx"                            | 42 |  |

# Index

Welcome Product Overview

### **Product Overview**

The SDLA application helps you test your serial data link design against industry electrical standards, such as PCIE, SAS and USB3. Any of four circuit blocks, Fixture, Emphasis, Channel, and Equalizer, may be included in the simulation processing.

Excellent flat magnitude response, linear phase response, and low jitter noise floor make the MSO/DPO/DSA70000 Series oscilloscopes the ideal tool for engineers designing serial data links.

The SDLA application offers the following capabilities:

- Enables design and test of serial standards using a set of four configurable blocks that simulate common system components. The SDLA application works with PCIE Gen3 8GT/s, SATA/SAS Gen3.0 6 Gb/s, QPI, and Display Port standards.

- Supports de-embeding a Fixture and de-embedding or embedding a Channel.

- Supports both channel and fixture S-parameters files: .s1p (S21), .s2p, or .s4p (single-ended or differential).

- Creates custom bandwidth limit filters or auto-sets an effective bandwidth limit.

- Generates plots of test point filter characteristics and block filter characteristics.

- Simulates a reference receiver with the Equalizer block to test the quality of the signal entering the receiver.

- Time shifts output waveforms to allow visual comparison of signal features before and after filtering and equalization.

- Sets the DPOJET application to analyze link quality with eye diagrams and jitter measurements.

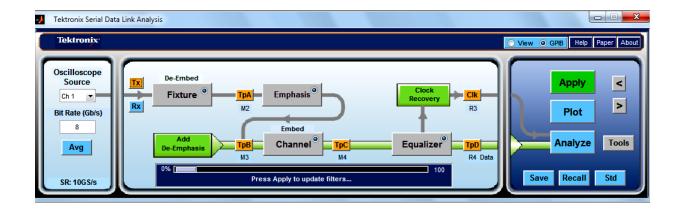

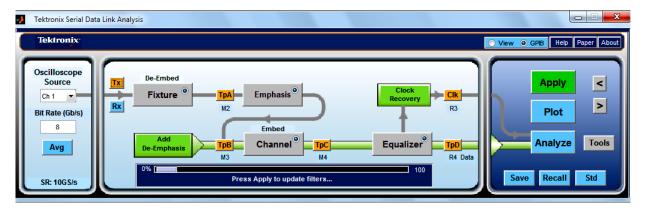

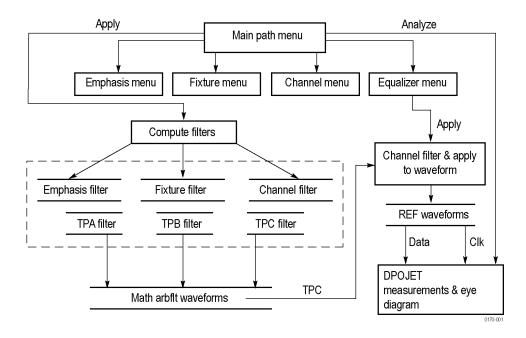

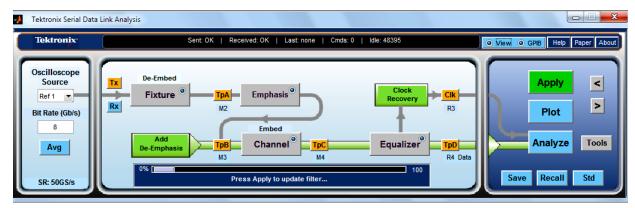

The following figure shows the main SDLA application window.

The Fixture and three Circuit blocks embed or de-embed their settings on the source signal. Click on a block to configure that block's settings. The test points (TpA, TpB, and TpC) show the effects of the block filters on the source signal. Select each test point to enable its output.

The processing and analysis operate on actively acquired waveforms or stored waveforms. The oscilloscope software must be running to use the SDLA application.

Click here for more information on the Signal Path Setup window (see page 3).

### **Software Updates from the Tektronix Web Site**

Periodic software upgrades may be available from the Tektronix Web site.

To check for upgrades:

- 1. Go to the Tektronix Web site Software Downloads page (www.tektronix.com/software).

- 2. Enter the product name in the **Search by keyword** field to find the available software upgrades.

- **3.** Click the appropriate software title and read the application information to be sure that it is compatible with your instrument model.

- **4.** Click the Download File link.

### **Conventions**

The online help uses the following conventions:

- DUT refers to the Device Under Test.

- When a step requires a sequence of selections, the > delimiter indicates the path from menus to sub-menus and to menu options.

- The directory path to support files is shortened to SDLA\directory\_name. The full product path is C:\TekApplications\SDLA on Windows XP instruments, and C:\Users\Public\TekApplications\SDLA on Windows 7 instruments.

### Requirements and Installation

The SDLA application is installed on newer Tektronix DPO/DSA/MSO70000 Series oscilloscopes before they leave the factory. The installation provides ten free uses of the full featured SDLA application.

#### **Requirements for Proper Operation**

The SDLA application requires a DPO/DSA/MSO70000 Series Oscilloscope with a single shot bandwidth ≥4.0 GHz.

#### **Software Compatibility**

Refer to the product Release Notes or the Optional Applications Software Installation manual for the compatible versions of oscilloscope software.

#### **Option Key Requirement**

You must have a valid option key for the application. Without the key, there are ten free trials. Consult with your Tektronix Applications Engineer or Account Manager for details.

#### Reinstalling the SDLA Software

To install the latest version of SDLA software, go to the topic <u>Software Updates From the Tektronix</u> Web Site.

### Signal Path Window Overview

The Signal Path Window is the top level control panel for the SDLA application. This is where you enable and configure the circuit blocks to model your system components. The following figure shows the initial SDLA application display with the SDLA application in the bottom half and the oscilloscope display in the top half. This configuration quickly displays the results of signal processing.

The four circuit blocks are:

- Fixture de-embed your source fixture from a transmitter (Tx) or Channel (Rx) connection.

- Channel simulates a transmission line or device, embedding or de-embedding.

- Emphasis adds or removes preemphasis or de-emphasis added by a transmitter.

- Equalizer (optional) simulates a reference receiver with configurable data and clock recovery capabilities.

The Signal Path window offers many other controls, such as choices of the Rx or Tx mode and GPIB communications. The figure shows the Channel and Equalizer enabled. The Test points, such as TpA, show the signal after application of the enabled processing blocks. The processing blocks are discussed in overview form in this section and in more detail in the Operating Basics section starting with Fixture and Channel Blocks (see page 17).

For information on using the GPIB function, refer to Using GPIB Remote Control (see page 37).

#### Moving Between the SDLA Software and TekScope Oscilloscope Application

The quickest way to move between software applications is to hold down the keyboard Alt key and tap the Tab key to pick an application.

An alternative is to use the main SDLA window buttons on the right side that switch between the SDLA, TEKScope and DPOJET applications.

- Click the < button to bring the oscilloscope waveform display to the foreground.

- Click the > button to bring the oscilloscope waveform display into view with SDLA application still in the foreground. This option is handy when also using the DPOJET application.

Of course you can use the Windows minimize button in the oscilloscope display to bring all SDLA windows to the foreground.

#### **Choosing a Source Waveform**

The SDLA application operates only on waveforms displayed on the oscilloscope. Select from actively acquired channel signals, Math waveforms and reference waveforms. For a live acquired waveform, you select its channel number. To operate on a saved waveform, recall it to the oscilloscope display. Then, in the SDLA application select its reference waveform name, such as Ref1 from the Oscilloscope Source drop-down list.

**NOTE.** Math waveforms generated by the SDLA application are not allowed as sources.

#### **Using the Average Function**

Clicking the Average button turns on the oscilloscope averaging mode with the number of averages you set in the SDLA application. An actively acquired source (CH1) is averaged as are the waveforms resulting from the processing blocks. These calculated or Math averaged waveforms are shown on the oscilloscope display. Averaging reduces noise on the signal when you are reviewing or measuring characteristics. High-frequency noise may appear when running a de-embed processing block. Averaging allows you to better see and measure the resultant waveforms.

#### Saving and Recalling Setups

The Save button lets you save all the current SDLA application settings to a file with a .sdl file extension. The Recall button lets you recall saved setup files to return the software to a previous configuration. Your setups are saved to the directory SDLA\Save recall. Only the SDLA setup is saved and recalled, not the entire oscilloscope setup.

Getting Started Configuring Blocks

**NOTE.** You must provide an appropriate source file for the recalled setup.

#### **Loading Standards**

Click the Standards button to load a predefined setup provided by Tektronix to test an existing serial data standard. Standards files are located at SDLA/standards.

### **Configuring Blocks**

Click a processing block in the Signal Path menu, shown in the figure, to access the configuration controls for that block. Instead of configuring each block separately, click the Standards button and load a standards setup file for popular serial standards. All circuit blocks are configured as defined by the standard. You can change any parameters after loading the setup file.

The circuit blocks use either Tektronix supplied S-parameter files or an S-parameter or FIR filter file supplied by you. Once you have selected appropriate filters for all enabled process blocks, click Apply and the software generates FIR filters for all enabled blocks. View the response of the filters by clicking the Plot button. This is a good way to verify that you have loaded the right filters and set appropriate cutoff frequencies with the Bandwidth Limit function.

For more on filter files, see Filter Files and Options (see page 33).

#### **Enabling Processing Blocks**

To enable or disable a processing block, click the option button in a processing block. In the figure, the Emphasis, Channel, and Equalizer processing blocks are enabled; the Fixture processing block is disabled. Process blocks may also be enabled within their configuration windows.

#### **Selecting Test Points to Enable Output Waveforms**

To generate and plot the waveforms resulting from each processing block, click the desired test point Tp[ABC] blocks. Once selected, they change color to orange. When you click the Apply button, the

Getting Started Configuring Blocks

software creates calculated waveforms for all selected Test points. The live calculated waveforms are labeled and appear on the oscilloscope display. Use Alt-Tab keyboard keys to switch to the oscilloscope display. Click the Plot button to show the calculated filter responses.

The test points and their oscilloscope screen waveform labels are:

- TpA M2

- TpB M3

- TpC M4

The test point FIR filters are saved to files in the directory SDLA\output filters.

For more on the filters, see Filter Files and Options (see page 33).

#### **Apply Button**

Clicking the Apply button initiates the following processes:

- 1. The software calculates the enabled blocks and test point filters. The status at the bottom of the Signal Path Setup window shows the progress.

- 2. The Equalizer operates on the TpC waveform to recover the data signal and clock.

#### **Analyze Button**

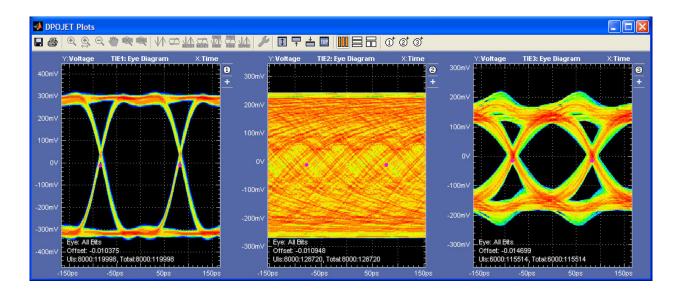

The Analyze button enables a smooth transition to waveform analysis with the DPOJET application. The SDLA application is put into a sleep state and then the DPOJET application is started with the test point signals, and the recovered data and clock signals selected for analysis. You must first select the Apply button and wait for filter processing to complete before selecting the Analyze button. The DPOJET application must be installed for this transfer to work. The SDLA software configures the DPOJET application to analyze the link quality with eye diagrams and jitter measurements.

The normal method for switching between the SDLA and the DPOJET applications is to use Alt Tab keyboard combination or the navigation buttons (< and >) on the main SDLA window. Use the TekScope application minimize button to minimize the SDLA application to view the DPOJET and SDLA applications.

The following figure shows the DPOJET application as it is configured when you click the Analyze button. The left plot shows the source waveform you selected. The eye is open with little degradation. The middle plot shows the TpC signal, which shows the effects of the source going through the Channel block. The right plot shows the TpD signal out of the Equalizer block. Note how the Equalizer was able to recover the data and open the eye.

Getting Started Configuring Blocks

# **Choosing the Tx or Rx Configuration**

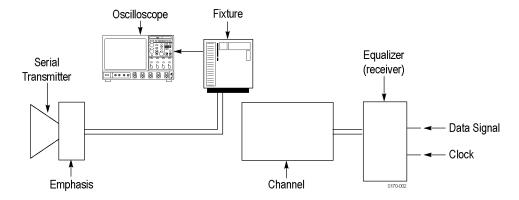

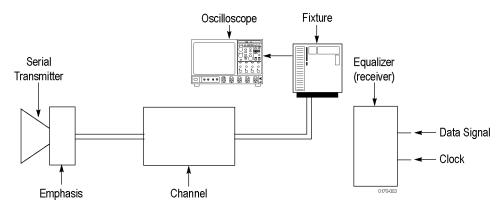

The Tx button configures the software to match your system as shown in the following figure. The oscilloscope is connected to the Fixture as shown. The Fixture, when enabled, provides access to the transmitter signal. By de-embedding the Fixture, you effectively move the oscilloscope connection right to the output of the Transmitter. The figure shows the Emphasis block as attached to the serial transmitter. By configuring the Emphasis block to remove emphasis added in the transmitter and de-embedding the Fixture, you can get an approximation of the live transmitter signal at test point TpB. TpA gives the transmitter signal with just the Fixture de-embedded.

The Rx button configures the software to match your system as shown in the following figure. The oscilloscope is connected to the Fixture as shown. The Fixture, when enabled, provides access to the receiver side of the transmission Channel. By de-embedding the Fixture, you effectively move the oscilloscope connection right to output of the Channel. This setup allows you to de-embed the transmission channel and see the quality of the transmitter signal at TpB.

# **Display Frequency and Time Domain Plots**

Click the **Plot** button to turn on three graphic window plots. The plots show the results of running the enabled processing blocks and the enabled test points, Tp[ABC]. Use the plots to verify filter configuration of each block as you configure the SDLA software. The navigation features at the top, such as the zoom (+) tool, help you see details of the filter response.

**NOTE.** Click the Plot button again to turn off the plots.

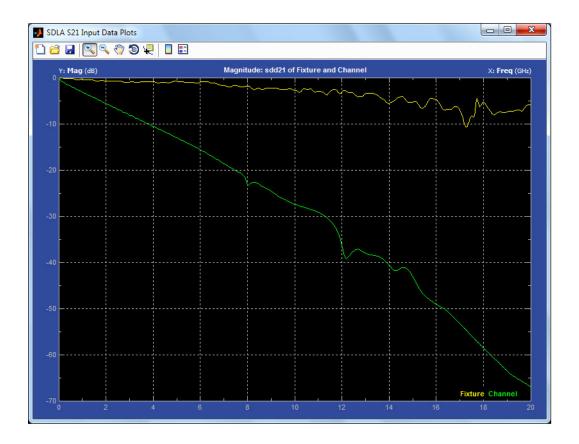

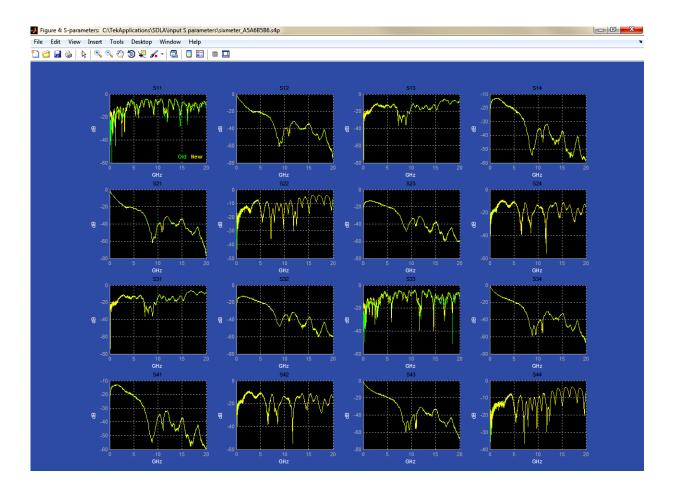

The following figure shows the magnitude versus frequency response of the Fixture and the Channel filter setup. If you use a FIR filter or other type of S-parameter file, the plot shows the frequency response of that filter data.

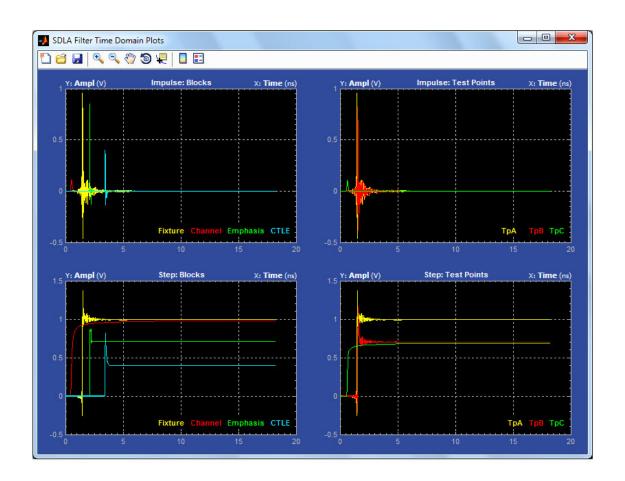

#### **Amplitude Versus Time Plots**

The following figure shows the Amplitude versus time plots for the six potential filter outputs from SDLA software. Three circuit block filters are on the left and the three test point filters are on the right. The top shows the standard impulse responses for the filters and on the bottom are the step responses for the enabled filters. The navigation features at the top, such as the zoom (+) tool, help you see details of the filter response. The plots are color coded as follows:

Yellow: Fixture, TpA

Red: Channel, TpB

Green: Emphasis, TpC

Blue: Equalizer, CTLE

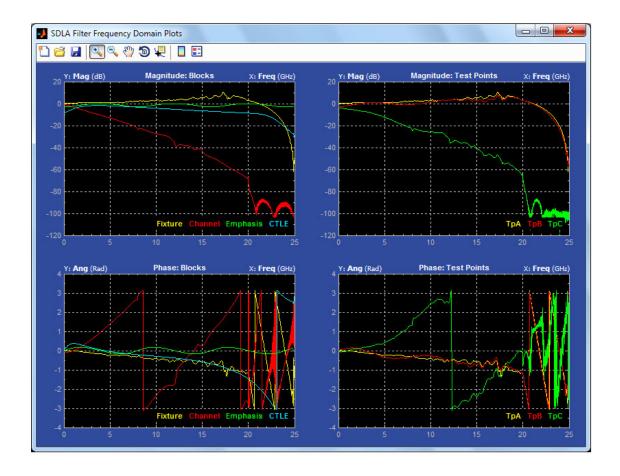

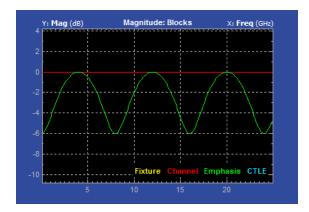

#### **Magnitude and Phase Versus Frequency Plots**

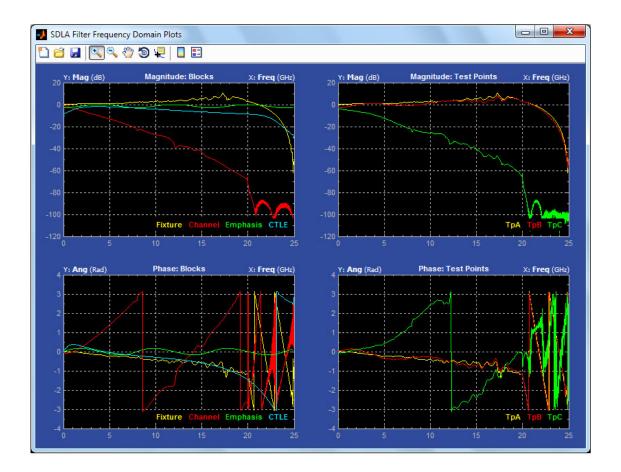

The following figure shows magnitude and phase plots versus frequency for the six potential filter outputs from SDLA software. Three block filters are on the left and the three test point filters are on the right. The top shows magnitude (dB) for the filters and on the bottom are the phase plots for the enabled filters. The navigation features at the top, such as the zoom (+) tool, help you examine details of the filter response. They are color coded as follows:

Yellow: fixture, TpA

Red: channel, TpB

Green: emphasis, TpC

Blue: Equalizer, CTLE

#### **Plot Window Tools and Navigation**

The plot windows have a tool bar that lets you zoom (+), pan and set measurement cursors on the filter response plots. The following figure shows the available tools.

The plot window title bar identifies each plot. As in the following example figure, the plots are color coded.

- Yellow traces are either the Fixture filter or the test point filter TpA

- Red traces are the Channel filter or the test point filter TpB

- Green traces are the Emphasis filter or the test point filter TpC

- Blue traces are the CTLE filter.

### **Application File Types and Locations**

The software uses the following file types and locations. The support files are arranged in folders with descriptive names at C:\TekApplications\SDLA on Window XP systems, and at C:\Users\Public\TekApplications\SDLA on Windows 7 systems.

- Example waveforms Example waveform files to help you learn the application.

- Input filters FIR filter files

- Input S-parameters Touchstone 1.0 version

- Output filters where the software stores generated Fixture, Emphasis, Channel and CTLE FIR filters. The filenames are overwritten each time you click the Apply button. You can rename the filter files to save a set of FIR filters for later use.

- Save recall temporary location where software stores the SDLA setup configuration files.

- Standards setup files for industry standards to set the Equalizer, Channel and Emphasis blocks as defined by the standard.

Your custom S-parameter files and filter files can reside at any path accessible to the instrument. For more information on the filters, see Filter Files and Options (see page 33).

### **Fixture and Channel Blocks**

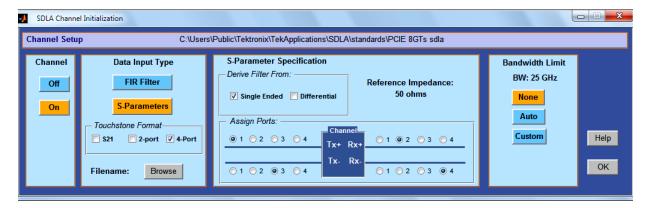

The circuit blocks allow you to remove (de-embed) the effects of the Fixture and to embed or de-embed the effects of the Channel. Select the Fixture or Channel block from the main signal path window to access the configuration dialog box. The following figure shows the Channel block.

#### **Data Input Type**

You can use either an S-parameter filter or a FIR Filter to represent your transmission channel. The FIR Filter selection allows you to choose your custom FIR filter file to simulate the block. The S-Parameters selection lets you choose from Tektronix supplied example S-parameter files in the Touchstone format covering a variety of Channel and Fixture types. You may also load your custom S-parameter files. Click the Browse button to choose the appropriate standards file to simulate your channel or fixture.

You can choose standard 2-port or 4-port Touchstone formats. You can also choose the S21 option, which is a nonstandard Touchstone format file where S21 data is stored in a 1-port file format. The S21 file option must have a .s1p file name extension.

#### 2-Port S-Parameter Format

When you select 2-Port, you can select either an S21 or an S12 format filter. The SDLA system assumes that the block ports are terminated with the reference impedance used to measure the S-parameters. Typically, the port impedance is 50 ohms.

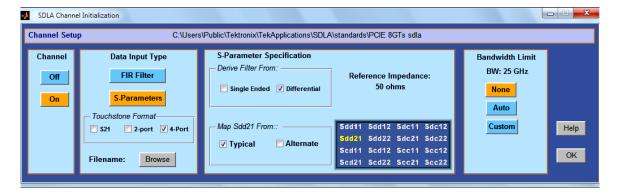

#### 4-Port S-Parameter Format

The 4-port selection allows the Touchstone file to contain data in single-ended standard format or in a mixed-mode differential format

**Differential S-Parameter.** When you select Differential, the software expects the Touchstone file to contain mixed mode, differential data rather than single-ended data.

**Single-Ended S-Parameter.** In this mode, you must use the Assign Ports feature to identify the input and output block ports used when measuring the S-parameters. The Channel and Fixture blocks should match the port assignments used when creating the S-parameter files.

The software performs the following operations to compute the FIR filter when using 4-port, single-ended S-parameter data.

- 1. Converts the S-parameter data from single-ended to mixed mode differential.

- 2. Identifies the Sdd21 element from result of step 1.

- **3.** As needed, extrapolates the Sdd21 data back to DC.

- **4.** If necessary, extends the stop frequency out to the Nyquist point of the waveform sample rate.

- 5. Converts the Sdd21 complex frequency domain data into a FIR filter.

**4-Port Differential.** When the 4-port Touchstone file contains mixed mode S-parameters then only the two columns containing the real and imaginary parts of Sdd21 are used to compute the FIR filter. In the Channel or Fixture block, you must select either the Typical or Alternate choices for the parameter Map to select the location of the Sdd21 characteristic. No other mappings are supported. The figure shows the Typical differential map.

#### **Creating Custom S-Parameter Files**

You can measure and create S-parameter files of your actual transmission channel and fixture by using a Tektronix sampling oscilloscope running IConnect software, or by using other circuit modeling and measurement systems. For more information on using filters, see Filter Files and Options (see page 33).

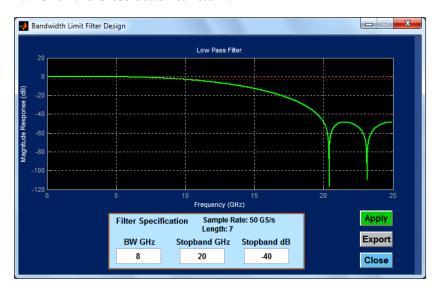

#### **Bandwidth Limit**

With the Bandwidth Limit function, you can apply an upper bandwidth limit to the block filter results. The created filter has a configurable bandwidth, stop-band frequency, and stop-band attenuation.

You have the following options:

**Auto.** The software determines the point at which the S21 or Sdd21 filter is -14 dB down from the DC value and sets the that frequency as the upper bandwidth limit. The stop-band frequency is set to 1.25 times the bandwidth limit. The stop-band attenuation is set to -80 dB.

**Custom.** Specifies the desired bandwidth filter. The Custom option is most useful when the Auto bandwidth filter is not appropriate for your input data.

Follow these steps to create a custom filter:

- 1. Click the Custom button and then the Filter button.

- 2. Set values in the BW GHz, Stopband GHz and Stopband dB fields.

- **3.** Click Apply to generate the bandwidth filter. The filter response is plotted for review. Click the Export button to save the FIR filter.

- **4.** Click the Close button to return.

**None.** The software does not use a bandwidth filter. The overall bandwidth for analysis is the Nyquist point for the sample rate of the source waveform.

#### Notes on Use of Bandwidth Limit

The None option may be the best choice when you are embedding the Channel.

When de-embedding a Fixture or Channel, a bandwidth limit filter is usually necessary to obtain a usable result. In such cases, a bandwidth limit filter can reduce noise by filtering out the high frequency components. By adjusting the values of BW GHz, Stopband GHz and Stopband dB, you can get better

Operating Basics Emphasis Block

control of the pass band, transition band and stop band responses, which affect noise attenuation, rise time, preshoot and overshoot.

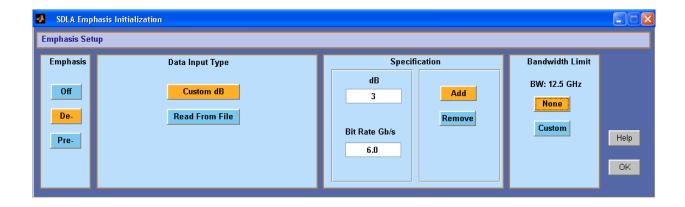

### **Emphasis Block**

The Emphasis block removes or adds the emphasis or de-emphasis added in most transmitters. You can use the typical 3 dB setting or enter a custom dB setting. Also, you can load a FIR filter that better represents your transmitter emphasis. When connected in Tx mode, select the test point TpB (Math3 waveform) to see the results of the filter on the source signal. When in the Rx mode, select the test point TpC (Math4 waveform) to see the results of the filter on the source signal. The Emphasis FIR filter is applied at the oscilloscope sample rate.

There are four types of filter response available:

- Add de-emphasis attenuates the low frequency components to compensate for high-frequency loss through the Channel.

- Remove de-emphasis removes the effect of de-emphasis added by another circuit block or device.

- Add pre-emphasis amplifies the high frequency components to compensate for high-frequency loss through the Channel.

- Remove pre-emphasis removes the effect of pre-emphasis added in a serial transmitter circuit.

Each option offers the ability to either remove the effects of a component or to simulate one.

**NOTE.** The filter setup need not be an emphasis type. It may be of any type required to better simulate your system.

#### **Bandwidth Limiting**

To limit the bandwidth resulting from the Emphasis filter, you can set the upper bandwidth by creating a Filter. Select the Custom button and then the Filter button. In the dialog box, enter the desired limit

value, such as 6.25 GHz, and apply it. Return to the Emphasis dialog box to complete the configuration. Click OK to return to the main signal path window.

#### Read Filter from a File

The Emphasis block may be set up from a FIR filter file. Click the Read From File button and browse to the location of your filter file.

#### Affect of the Signal Bit Rate on Filter Response

The bit rate is the bit rate of the source signal. The bit rate determines the region of increase or decrease in the frequency response of the Emphasis filter. For example, adding de-emphasis to a signal can result in the frequency response seen in the figure. The magnitude frequency response is periodic with a period determined by the bit rate. The peak to peak value of the filter magnitude response is set by the dB value you chose.

For more on filter file formats, see Filter Files and Options (see page 33).

### **Equalizer Block Overview**

The Equalizer block restores the integrity of the data stream and recovers the embedded clock. It can serve as a "reference receiver" in that it performs at the minimal acceptable level, as defined by a standard, for a serial data receiver. The SDLA Equalizer consists of a trio of digital equalizers working together:

- An adaptive feed forward equalizer (FFE)

- A decision feedback equalizer (DFE)

- A continuous time linear equalizer (CTLE)

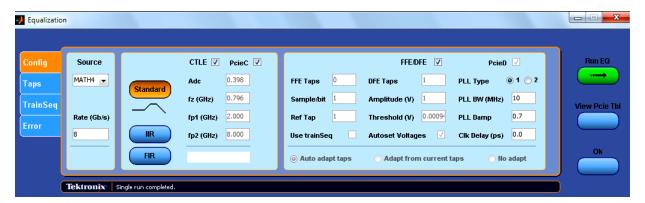

As shown in the following illustration, the CTLE may be enabled separately from the FFE/DFE equalizers. When both sets of equalizers are enabled, the CTLE filtering occurs first, followed by the FFE/DFE filtering. These equalizers can work together to recover the data stream by correcting for effects of channel impairment and noise.

Operating Basics Running the Equalizer

The following figure shows the Equalizer window with CTLE and FFE/DFE equalizers enabled. The Source is set to the Math4 waveform, which is the output of the Channel block, TpC.

The bit rate you enter must be accurate to recover the data and clock signals. The software performs clock recovery by emulating a phase locked loop (PLL) circuit. Use the data rate defined for the serial standard you are testing. If you are testing a new serial line, you may need to measure the bit rate near the Transmitter.

The Equalizer runs on an oscilloscope source waveform, it defaults to TpC. The Equalizer outputs static Data and Clock waveforms into Ref4 and Ref3 waveform records, respectively. To update these waveforms, select the Run EQ button in the Equalizer block or select the Apply button in the main Signal Path window

### **Running the Equalizer**

The following steps describe how to make a first run of the Equalizer to determine whether further adjustments are necessary.

- 1. In the Config tab, enter the FFE and DFE taps and configure the PLL fields for a Receiver as defined in the standard you are testing. Alternatively, you can load a standards setup file using the Standards button on the main Signal Path menu. The standards setup file sets all Equalizer parameters as defined in the standard.

- **2.** Select the input if not the TpC output, the calculated waveform, or Math4. Set the bit Rate, if not already set by a Standards file.

- 3. Click the Run EQ button.

- **4.** To view the output waveforms, go to the oscilloscope display. The Ref4 waveform is the Data signal and is labeled TpD R4. The Ref3 waveform is the Clock signal and is labeled Clk R3.

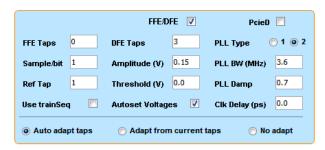

### Adjusting the FFE/DFE Equalizer to Improve Signal Recovery

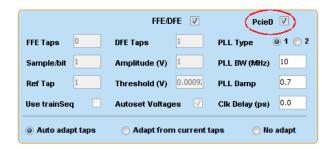

You may need to adjust the Equalizer settings to recover the data and clock signals. Many of the techniques used to optimize a hardware receiver are available in the Equalizer. The adjustments described here apply only when the FFE/DFE Equalizer is enabled as shown in the following illustration.

Most of the following parameters are defined in a serial data standard.

**FFE Taps.** The Feed Forward Equalizer tap number is normally set to a number defined by the serial data standard. A value of FFE Taps=0 means the FFE has one tap with tap coefficients fixed to 1, which signifies the FFE is off. The default value is 0.

**Sample/bit.** Sample per bit specifies the number of FFE taps per bit. If set to >1, it implies an FFE with fractional spaces. The default value is 1.

**Ref Tap.** The Reference Tap for the FFE indicates the number of precursor taps. It must be set to one (1) more than a multiple of the number of FFE taps per bit. The default value is 1.

**DFE Taps.** The Decision Feedback Equalizer tap number is normally set to a number defined by the serial data standard. For example, the setting for SAS is 3, and the setting for PCIE 8GT/s is 1.

**Amplitude**. The Amplitude is the target output amplitude for the Equalizer. When you select Autoset Voltages, the adaptation routine adjusts this value automatically to optimize the recovery of the data signal. The default value is 0.15 V.

**Threshold**. The Threshold is the middle voltage level of the signal, which may be the transition between logic levels. For biased signals, enter the mid-level value. For differential signals, the value should be close to 0 V. The default value is 0 V. Lacking clear knowledge of the correct voltage, use the Autoset Voltages function to determine the optimal value.

**PLL Type.** The software supports Type I and Type II PLL clock recovery. Each serial standard specifies the type of PLL to use for clock recovery.

**PLL BW.** The loop bandwidth of the PLL is defined as the -3 dB frequency of the error transform function of the PLL. The value should be specified in the serial standard.

**PLL Damp.** This is the damping ratio of the Type II PLL. The value should be specified in the serial standard.

**Clk Delay (ps).** The clock delay is a specific delay added to the recovered clock after the PLL result. The value adjusts the clock offset to optimize the equalization result and achieve the best data recovery.

**Use TrainSeq.** Enables the Equalizer to optimize its adaptation routine over a specific pattern the length of which is defined on the TrainSeq tab.

**Autoset Voltages.** When enabled, the Equalizer adaptation routine adjusts the Amplitude and Threshold values to optimize recovery of the data and clock.

**Auto adapt Taps.** The adaptation routine starts by identifying initial Tap settings and then adjusts them to optimize recovery of the data and clock.

Adapt from Current taps. The adaptation routine uses initial Taps settings, then adjusts them to optimize recovery of the data and clock. The initial Taps settings might be those for a serial standard or those saved from an earlier test.

**No Adapt.** The Equalizer uses the current Taps either from your inputs or from a previous adaptive session. Use the entered values without changes. This option is useful when you want to load a known Taps file in the Taps tab to resume a test started earlier.

**PcieD.** PcieD is the special DFE defined in the PCIE 8GT/s specification. The PCIE 8GT/s specification defines a one-tap DFE with no FFE. The DFE tap value is limited to a value between -30 mV and 30 mV.

When PcieD is checked, the following field values are grayed out and their values set by internal algorithms:

- FFE Taps =  $\mathbf{0}$

- $\blacksquare$  Sample/bit = 1

- Ref Tap = 1

- Use trainSeq = unchecked

- DFE Taps =  $\mathbf{1}$

- $\blacksquare$  Amplitude (V) = 1

- Autoset Voltages = **checked**

These fields are enabled again when PcieD is unchecked.

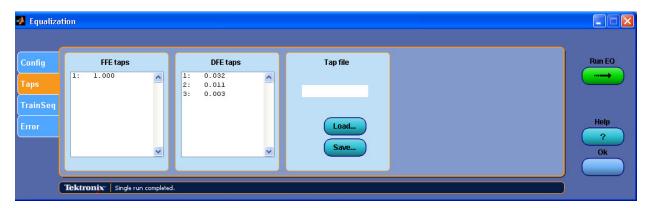

#### **Taps Tab Settings**

In the following figure, the FFE taps have a value of one and the DFE field shows three taps with different values. This state results from settings on the Config tab where FFE is set to 0 and DFE set to three. If this was the result of running Auto adapt Taps, you could save the results in a tap file for use in a later Equalizer run.

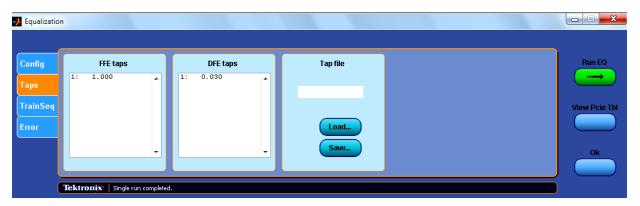

When PcieD is checked, and Auto adapt taps or Adapt from current taps is selected, the DFE adaptation algorithms attempt to maximize the eye area. The resulting DFE tap value is shown in the Taps tab.

**View Pcie Tbl.** The View Pcie Tbl button is enabled when PcieD is selected and Auto adapt taps or Adapt from current taps is selected. After adaptation is finished, click **View Pcie Tbl** to open the adaptation results file *pcieAdaptationEQ.txt*. This results file has better numerical resolution for DFE Tap(mv) than what is shown in the Taps tab.

```

pcieAdaptationEQ - Notepad

File Edit Format View Help

# PCIE equalizer adaptation results

# Time: 18-Jul-2011 14:04:11

# CTLE(dB), CTLE(lin) DFE Tap(mV), Eye Area(UI*mV), Eye Height(mV), Eye Width(UI)

-6 0.500 30.00 44.51 84.53 0.53

```

#### **Troubleshooting Data and Clock Recovery**

If clock recovery fails, your bit rate might not be what you expect. One solution is to measure the bit rate as near to the transmitter as possible. You can use the DPOJET application running on the oscilloscope to accurately measure the bit rate.

If you have entered the defined standard values for the FFE Taps, DFE Taps and PLL and not been successful recovering the data and clock, your next step is to use the adaptation settings. Without changing your initial settings, select Autoset Voltages and Adapt from current taps on the Config tab. Click the Run EQ button and check the resultant waveforms. If they are better or acceptable, note the Taps values and voltages set by the adaptation routines.

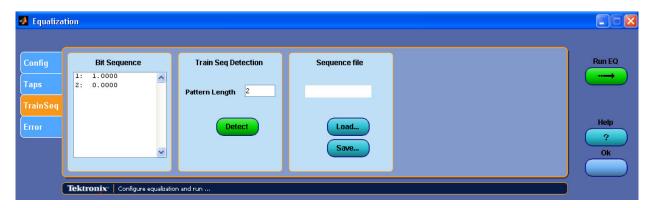

Another technique is to use the TrainSeq functions to help the Equalizer identify the correct bit sequence before again running your test signal through the Equalizer. The figure shows the TrainSeq tab of the Equalizer.

- 1. On the Equalizer Config tab, set the Equalizer source to a signal with the same data pattern as the signal you plan to test, but with a clean, open eye pattern. This signal could be one acquired close to the transmitter, or a slower speed version of the original signal or the original signal compensated using transmitter emphasis to improve the eye opening.

- 2. Click the Use TrainSeq box on the Config tab.

- 3. Select the TrainSeq tab and set the correct **Pattern Length** according to the standard.

- **4.** Click the **Detect** button. You should see a Bit Sequence displayed in the left field, which should be the same bit sequence as in your original signal.

- 5. With the correct bit sequence in place, select the Config tab and select the original test source.

- **6.** Select (enable) the **Use TrainSeq** box if not already enabled. Enter the correct bit rate if you changed it in a preceding step.

- 7. Click the **Run EQ** button.

- **8.** Check the results on the oscilloscope display. You should see a recovered data signal, though it may not meet the standard specifications. You may need to address other design issues to correct any problems with the recovered data.

Another area for investigation is whether your Channel and Fixture filters are correct. Review the plots for those filters to determine if high-frequency noise or other aberrations are corrupting the signal. Use the Bandwidth Limit filters to reduce such noise.

# Adjusting the CTLE Equalizer to Improve Signal Recovery

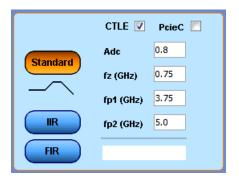

You may need to adjust the CTLE Equalizer settings to recover the data and clock signals. The adjustments described here only apply when the CTLE Equalizer is enabled as shown in the following image.

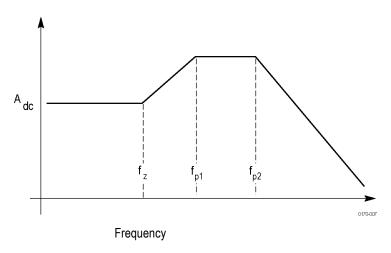

The function of most of the key parameters described here are shown in the following illustration. Refer to it as you review the parameter descriptions in the list that follows.

Most of the following parameters are defined in serial data standards.

A<sub>dc</sub>. This is the DC gain of the CTLE transfer function. It is a positive number. The default value is 0.8.

**F**<sub>z</sub>. This is the zero frequency of the CTLE transfer function. The value must be within the range of 1 MHz to 20 GHz. The default value is 750 MHz.

$F_{p1}$ . This is the frequency of the first pole of the CTLE transfer function. The value must be within the range of 1 MHz to 20 GHz. The default value is 3.75 GHz.

$\mathbf{F}_{p2}$ . This is the frequency of the second pole of the second order CTLE transfer function. The value must be within the range of 1 MHz to 20 GHz. The default value is 3.75 GHz.

**IIR.** This button loads a custom IIR filter file that sets the CTLE parameters. The IIR filter file is an ASCII text file with file extension .tsf. The file uses a polynomial transfer function to define the IIR filter. There is no limit on the order of polynomials. The file uses # to indicate a comment line; **Numerator** as the key word for the numerator polynomial, and **Denominator** as the key word for the denominator polynomial. For example, if an IIR is a first order filter having the pole at 4 GHz, then the denominator should be written as 1, 2\*pi\*4\*1e6.

The following is an example IIR filter file definition:

```

# IIR CTLE Filter

# defined by a polynomial transfer function

#

b1s^{(n-1)}+b2s^{(n-2)}+...+bn

a1s^{(m-1)}+a2s^{(m-2)}+...+am

# using the following format

#

#[Numerator]

#b1, b2, ..., bn

#[Denominator]

#a1, a2, ..., am

# Note that unit is radian/second, not Hz

[Numerator]

5.026548245743669e+010, 3.158273408348595e+020

[Denominator]

1, 6.283185307179587e+010, 6.316546816697189e+020

```

#### **NOTE.** The frequency unit is radians/second, not Hz.

The instrument creates an FIR filter file (based on the IIR filter definition) after clicking the **Apply** button in the SDLA main menu or the **Run EQ** button in the equalizer menu. The FIR filter is called *sdlaCtle.flt* and is located at C:\TekApplications\SDLA\output filters.

**FIR.** This button opens a file browser to load a custom FIR filter to set the CTLE parameters.

**Standard**. The Standard button uses either the default values for the CTLE parameters or the values you manually enter into the CTLE parameter fields.

**PcieC.** When PcieC is checked, SDLA runs an optimization process to find the best CTLE setting to maximize the eye area (per the PCIE 8GT/s specification). The PCIE 8GT/s specification defines 7 CTLE presets. The DC gains are -6, -7, -8, -9, -10, -11, and -12 in dB. When PcieC is checked, the UI changes as shown in the following image:

#### Settings:

- Standard button is selected.

- Adc, fz (GHz), fp1 (GHz), fp2 (GHz) are grayed out, as they are set by the SDLA optimization routine.

- fp1 = 2 GHz, fp2 = 8 GHz, and fz = fp1\*Adc. The value of Adc and fz are updated after running the CTLE optmization.

- PcieD is selected. See <u>PcieD</u> (see page 24).

- Auto adapt taps is selected.

The following is the sequence of SDLA operations:

- 1. SDLA generates an optimal setting after clicking the Apply button in the main menu or the Run EQ button in the equalizer menu is clicked.

- 2. SDLA updates the setting of Adc, fz (GHz), fp1 (GHz), fp2 (GHz).

- **3.** SDLA creates the file pcieAdaptationEQ.txt at C:\TekApplications\SDLA\taps.

- **4.** When DFE is off, the DFE Tap value should be 0. When DFE is on, the DFE Tap value should be between -30 mV and 30 mV.

**View Pcie Tbl.** Click **View Pcie Tbl** to view the contents of the optimization results file pcieAdaptationEQ.txt. All 7 presettings are listed. The best CTLE setting is labeled with \*\*\*, where the best setting has the maximum Eye Area value.

```

pcieAdaptationEQ - Notepad

File Edit Format View Help

PCIE equalizer adaptation results

Time: 18-Jul-2011 14:07:40

CTLE(dB), CTLE(lin), DFE Tap(mV),

Eye Height(mV), Eye Width(UI)

84.13

91.01

0.57

Eye Area(UI*mV),

0.501

0.447

44.21

29.96

51.84

0.398

0.60

25.50

22.05

-9

0.355

43.33

81.33

0.53

0.316

```

**NOTE.** PcieC must be unchecked to use the Standard, IIR, or FIR buttons.

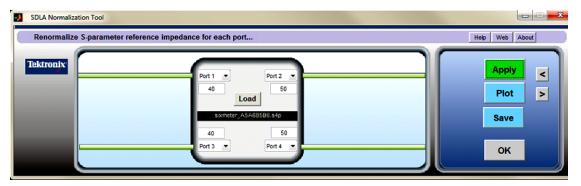

### Renormalization of S-Parameters to Different Reference Impedances

SDLA makes the assumption that the reference impedance of each port is attached to the port for analysis. This is true regardless of what the reference impedance is. Typically it is  $50~\Omega$  for single-ended measurements. SDLA reads the S-parameter file reference impedance value and displays the value in the block menu.

However, the actual reference impedance value on all ports is not used in the computation of the filter. That means that each port has a value equal to its reference impedance connection value. This value is contained in the # options line of the Touchstone version 1 file. It will read out in the Channel or Block menu after the Apply menu button is pressed.

You should check this reference impedance. If the reference impedance is different from what is actually connected to the DUT, then you should renormalize the S-parameters to the correct reference impedance for each port before reading them into SDLA fixture or channel blocks. This is done by using the renormalization tool, accessed from the main SDLA menu.

For example, if the user has a 40  $\Omega$  transmitter connected to a fixture, which in turn is connected to a 50  $\Omega$  oscilloscope channel, then renormalization may be needed. You can renormalize the 4-port S-parameter set for the fixture so that the input ports are 40  $\Omega$  and the output ports are 50  $\Omega$ .

If multiple S-parameter blocks are cascaded together to create one block for analysis, then the reference impedance of S-parameters sets must be equal at the port connections specified in the cascade chain.

Reference impedance may be different at different points in the cascade of blocks but they must be the same at the connection points between blocks. This makes the renormalization tool useful for establishing the correct reference impedance at each port in this situation.

#### **Using the Renormalization Tool**

- 1. Select Tools > Renormalization.

- 2. Click **Load** and browse to select the 4-port S-parameter file that is to be renormalized.

- 3. Select the port numbers to correspond to how the data is labeled. Selecting port numbers has no effect on how the renormalization calculations will occur but it does affect how the plots are labeled.

- **4.** Edit/enter the correct reference impedance for each port.

- 5. Click Apply.

- **6.** Click **Plot** to see the renormalization results.

#### **Controls**

Load. Opens a browser to select the 4-port S-parameter file that is to be renormalized.

**Port.** Selects the port number (1 through 4). Below the port number is the reference impedance field for that port.

**Apply.** Performs a renormalization on the current file.

**Plot.** Shows the original S-parameter data in green traces and the new renormalized plots in yellow. Use the zoom tool on the plot tool bar to zoom in on the detail of each individual plot. A cursor tool allows the read out of trace data to be performed and there is also a trace marking tool.

**NOTE.** The Plot tool provides useful information even if an S-parameter set does not need to be renormalized. You can load the S-parameter set and leave all the port impedances the same and click Apply. Then click the Plot button to view and verify the S-parameter data. These plots can also help to identify which ports are which to correctly set up the port number menu in the fixture or channel block of the main SDLA menu.

**Save.** Saves the new renormalized S-parameter data may be saved to a file in Touchstone 1 format by pressing the Save menu button. However, Touchstone 1 format does not allow for specifying different impedance for different ports in the options line. When the file is saved the options line will show a value of 1 as a reference impedance. This is a flag that indicates that this file was renormalized.

To keep track of the impedance status in the file, SDLA writes a comment line in the file containing the Touchstone 2 command:

#### ! [ reference ] <r1> <r2> <r3> <r4>

You can load the renormalized file into a SDLA fixture block or channel block. A correct filter is then derived from the S-parameter data.

Click Apply to view the fixture reference impedance of each individual port or channel in the block menu panel.

The renormalized file can be read back into the tool and restored back to the original reference impedance values if required.

# **Filter Files and Options**

All of the SDLA Software processing blocks operate from the same type of filter files. The circuit blocks use either Tektronix supplied S-parameter files or an S-parameter or FFE filter file supplied by you. For information on the location of filter and other support files, go to Application File Types and Locations (see page 15).

#### **Filter File Formats**

FIR block filters are saved as ASCII files in the arbfilt format needed by the oscilloscope math functions.

The first entry in the FIR filter files is the sample rate and the remaining entries are filter coefficients. The arbfilt format also may simply be a column or row of filter coefficients without a defined sample rate. The software stores the created FIR filter files in the SDLA\output filters directory.

#### **Filter Interactions**

The block filters, test point filters and BW Limit filters are created to support all interactions within the SDLA software model. The filter processing diagram shows the processing order of the various defined filters. The Analyze function runs the TpC waveform through the Equalizer and passes its output data and clock signals on to the DPOJET application where you can validate that the eye is opened enough on the data signal to satisfy the serial standard. DPOJET offers an extensive set of measurements to help analyze your signal.

Test point filters for TpA, TpB, and TpC are created by convolving them with combinations of the circuit block filters as shown in the table.

**Table 1: Convolving Test Point filters**

| Rx/Tx selected | Test point | Circuit block (when enabled) |

|----------------|------------|------------------------------|

| Тх             | ТрА        | Fixture de-embedded          |

|                | ТрВ        | Fixture de-embedded          |

|                |            | Emphasis                     |

|                | TpC        | Fixture de-embedded          |

|                |            | Emphasis                     |

|                |            | Channel embedded             |

| Rx             | ТрА        | Fixture de-embedded          |

|                | ТрВ        | Fixture de-embedded          |

|                |            | Emphasis                     |

|                |            | Channel de-embedded          |

|                | TpC        | Fixture de-embedded          |

|                |            | Emphasis                     |

### **Extrapolation of Filter Data**

When S-parameter files do not begin at 0 Hz (DC) or do not extend to the Nyquist of the source waveform as required by the filters, the SDLA Software extrapolates the existing data to fill the bandwidth gaps.

**DC to Starting Frequency.** The software uses the first two magnitude data points in the characteristic response to compute the slope to 0 Hz. It unwraps the phase and linearly extrapolates phase response to generate data points along the defined slope. This data is prepended to the original S-parameter data.

Operating Basics Running a Test

**Extending Upper Bandwidth.** When necessary, the software may extend the stop frequency out to the Nyquist point of the source waveform sample rate. This is done by point replication of the complex data point in the magnitude and phase response data beginning at the stop frequency.

# **Running a Test**

This section describes the recommended order from configuring blocks, running a simulation to jitter and eye analysis on the SDLA test points using the DPOJET application.

- 1. Connect the fixture and oscilloscope to the DUT either at the transmitter (Tx) end or at the receiver (Rx) end of the transmission Channel. Select the appropriate connection from either Rx or Tx.

- 2. Connect the source signal to an oscilloscope input channel. Adjust the oscilloscope trigger, vertical and horizontal settings to capture signals with good fidelity. Using the oscilloscope Autoset function can simplify this adjustment.

- 3. If you plan a serial standard compliance test, click the Standards button and browse to the appropriate setup file. The Standards file sets all SDLA Software parameters at once. If your source is not CH1, select the correct source in the main Signal Path window. After loading a Standards setup file, click the Apply button and monitor the status bar for completion of the filter creation, and then go to step 10.

- **4.** When not using a Standards or other setup file, enable the processing blocks you need and the test points (Tp[ABC]) you want generated. Tune the bandwidth limit filter if needed.

- **5.** When using a Fixture block, locate and load the S-parameter or FIR filter file to de-embed its affects on the signal. If you have a custom S-parameter or FIR filter file, load it. Tune the bandwidth limit filter if needed.

- **6.** When using a Channel block, locate and load an appropriate S-parameter or FIR filter file. Tune the bandwidth limit filter if needed.

- 7. When using the Emphasis block, enter an appropriate dB value for your transmitter circuit and an accurate bit rate. Instead, you could locate and load a FIR filter file to condition the signal. Tune the bandwidth limit filter if needed.

- **8.** When using the Equalizer block, configure the FFE/DFE and the clock recovery parameters.

- **9.** Click the Apply button to generate the FIR filters for each block and selected test points. Wait until the status bar at the bottom shows processing is complete.

- 10. Click the Plots button to inspect the block and test point time and frequency domain responses to be sure they have the response you expected. Click the Plots button again to remove the plots. You can quickly revise any block configuration and click the Apply button again to regenerate the filters. You can check equalizer optimization results in the Equalizer menu.

- 11. Verify that DPOJET is installed and that it runs correctly. You can leave DPOJET running. It is a better approach to start DPOJET before using the Analyze function in SDLA.

Operating Basics Running a Test

12. Click the Analyze button and switch to the DPOJET application (use the Alt Tab keys) to analyze the results of the simulation. DPOJET is set to analyze the test point waveforms with jitter and eye analysis. Revise the SDLA software setup and repeat steps 7–10 as needed to complete your testing.

13. Switch to the oscilloscope display (use the Alt Tab keys) and observe the enabled test point waveforms.

This completes the procedure for running the SDLA Software. Each block has many configuration parameters not covered in this procedure. The Equalizer has features to significantly improve recovery of the data and clock signals. Explore the details of each processing block to get the most out of the SDLA Software.

# **Using GPIB Remote Control**

You can use remote GPIB commands for basic remote control of the SDLA application. When on, the GPIB function provides the following remote commands:

- Start starts the SDLA application.

- Exit closes the SDLA application.

- Recall loads a provided industry standard file or a custom set-up file you created.

- Apply computes the enabled filters.

- Analyze starts and configures the DPOJET application to analyze and display eye diagrams for the enabled SDLA test-point signals.

- Source specifies the source waveform processed by the SDLA application.

- Bit rate specifies the bit rate of the source waveform.

- Tx/Rx specifies either a transmitter connection or channel connection for the test fixture.

Analysis results are available by querying the DPOJET application using its GPIB command set or from the oscilloscope front panel. Use the GPIB command interface for the DPOJET application to retrieve measurement results. Refer to the DPOJET online Help or the PDF document derived from it for GPIB control information.

The GPIB commands listed here are separate from, and handled differently than, the DPO70000 Series Oscilloscope GPIB commands. The GPIB selection in the upper right corner of the Signal Path Window enables the GPIB functionality and provides a monitor for GPIB communications with the application.

#### **GPIB Control Menu**

You enable the GPIB function for the SDLA application by clicking the selector at the upper right in the main SDLA application window. Click the View selector to monitor SDLA command traffic. In the following illustration, GPIB is enabled and View is selected to show command traffic to and from the SDLA application. Other GPIB command traffic is not shown. Use the TekVisa OpenChoice Call Monitor to see all GPIB traffic.

The GPIB status includes the following values:

Sent – shows the status sent after executing the last command. May be OK or ERROR.

- Received shows the last value read from the SDLA handshaking variable. It is either OK, meaning no command is available, or it shows the received command now being processed.

- Last shows the last instruction executed.

- Cmds contains the count of the commands received since you enabled the GPIB function.

- Idle contains the count of the number of polls of the handshaking variable by the SDLA application since completing the last command. GPIB communications is enabled by default.

Using the SDLA application GPIB interface consumes additional compute resources.

#### **Handshaking Protocol**

The SDLA application handles GPIB communications through its own protocol handshaking.

The requirements for SDLA GPIB communications with a controller are as follows:

- 1. Once the SDLA application has started, it writes an "OK" status to the SDLA handshake variable. This tells the controller application that it may now write a valid SDLA command into the "sdla' variable.

- 2. The GPIB controller polls the handshake variable (variable:value? "sdla") until it detects the OK status.

- **3.** The GPIB controller writes a command string into the SDLA handshake variable. For example, sending the command 'variable: value "sdla", "p:apply" writes the string "p:apply" into the variable "sdla".

- **4.** The SDLA GPIB function polls the handshake variable, reads the command string and interprets it as a command. If the command is bad, it writes an ERROR handshake value to the variable.

- **5.** A good command is parsed and executed. On successful execution, it writes an OK to the handshake variable. When the GPIB controller reads the OK status, it may send a new command string.

### **GPIB Commands**

This section lists the commands available for remote control of the SDLA application.

### **APPLICATION:ACTIVATE "Serial Data Link Analysis"**

This command instructs the oscilloscope to start the SDLA application. It is a set-only parameter.

#### **Syntax**

APPLICATION: ACTIVATE "Serial Data Link Analysis"

#### **Arguments**

"Serial Data Link Analysis" which must be just as defined in the syntax and enclosed in double quotes (" ").

#### **Returns**

NONE

#### VARIABLE: VALUE? "sdla"

Reads the value of the SDLA handshake variable. The returned status must be "OK" before you can send any other commands.

#### **Syntax**

VARIABLE: VALUE? "sdla"

#### **Arguments**

None

**NOTE.** The string sdla must be in lowercase characters.

#### **Returns**

OK: The SDLA application is running and ready for a command.

ERROR: The SDLA application was not able to parse or run the previous command.

## VARIABLE: VALUE "sdla", "p:analyze"

Starts the DPOJET application and configures it to display the eye diagrams for the SDLA application waveform(s) resulting from the Apply operation.

#### **Syntax**

VARIABLE: VALUE "sdla", "p:analyze"

#### **Arguments**

"p:analyze" starts the DPOJET application to display the SDLA application waveforms.

**NOTE.** The strings, sdla and p:analyze argument text must be in lowercase characters.

### VARIABLE: VALUE "sdla", "p:apply"

Computes the enabled filter blocks and test points and performs equalization if enabled. The result is the same as selecting the front panel Apply button. The Apply computation may take over 60 seconds, depending on input data and sample rate. Make sure that your polling time-out is sufficiently long.

#### **Syntax**

VARIABLE: VALUE "sdla", "p:apply"

#### **Arguments**

"p:apply" starts computation of the enabled filters and equalization.

**NOTE.** The strings, sdla and p:apply, must be lowercase characters.

# VARIABLE:VALUE "sdla", "p:bitrate:<value>"

Sets the bit rate for the source waveform. Determine the native bit rate of the source waveform and use that value.

#### **Syntax**

VARIABLE: VALUE "sdla", "p:bitrate: <value>"

#### **Arguments**

"p:bitrate:<value>" specifies the bit rate of input source waveform. The <value> must be an integer in either engineering notation (6.25e6) or as a regular number (6250000).

**NOTE.** The strings, sdla and p:bitrate, must be in lowercase characters. The <source> string may be all uppercase or all lowercase.

#### **Example**

variable:value "sdla", "p:bitrate:6e9" sets the source bit rate to 6 Gb/s.

### VARIABLE: VALUE "sdla", "p:exit"

Closes the SDLA application. The current state of the application is not saved.

#### **Syntax**

```

VARIABLE: VALUE "sdla", "p:exit"

```

#### **Arguments**

"p:exit" forces the application to close.

**NOTE.** The strings, sdla and p:exit, must be in lowercase characters.

### VARIABLE:VALUE "sdla", "p:recall:<path and file name >"

Loads a setup file from "path and file name". The setup file may be one of the included Standards setup files or a setup file you created with the SDLA application interface. The setup file includes configuration of Rx/Tx, the enabled filter blocks and test points, and any custom FIR filters you specified in your custom setup.

#### **Syntax**

VARIABLE: VALUE "sdla", "p:recall: <path and file name >"

#### **Arguments**

"p:recall:<path and file name >" where <path and file name > specify the path on a mapped drive and a setup file with the .sdl suffix. The path and file name must not contain space characters, but they may contain upper and lower case characters.

**NOTE.** The strings, sdla and p:recall, must be in lowercase characters.

#### **Example**

variable:value "sdla", "p:recall:C:\TekApplications\MyDirectory\mysetup.sdl" recalls the SDLA application setup file named mysetup.sdl.

### VARIABLE: VALUE "sdla", "p:source: <source>"

Sets the input source waveform for the SDLA application to operate on.

#### **Syntax**

VARIABLE: VALUE "sdla", "p:source: <source>"

#### **Arguments**

"p:source<source>" specifies the input source waveform as any one of ch1 | ch2 | ch3 | ch4 | math1 | ref1 | ref2.

**NOTE.** The strings, sdla and p:source, must be in lowercase characters. The <source> string may be all uppercase or all lowercase.

### **Example**

variable:value "sdla", "p:source:ch1" sets the source waveform to be the oscilloscope CH1 input.

### VARIABLE:VALUE "sdla", "p:tx" | "p:rx"

Sets the SDLA application to connect the oscilloscope and test Fixture either directly to the transmitter (tx) or directly to the receiver end of the Channel (rx) for the test. The results are the same as selecting the front panel Tx selector or the front panel Rx selector.

#### **Syntax**

```

VARIABLE: VALUE "sdla", "p:tx"

VARIABLE: VALUE "sdla", "p:rx"

```

#### **Arguments**

"p:tx" sets the SDLA application to the transmitter configuration for testing.

"p:rx" sets the SDLA application to the receiver configuration for testing.

**NOTE.** The strings, sdla, p:tx and p:rx, must be in lowercase characters.

# Index

#### Symbols and Numbers Conventions, 2 Filter Convolving, 34 Convolving Test Point Filters, 34 Filter Data, 34 2-Port S-Parameter, 17 Filter File Formats, 33 CTLE FIR button, 29 4-Port Differential, 18 CTLE parameters, 27 Filter Files, 33 4-Port S-Parameter, 17 Filter Input Type, 17 CTLE selector, 22 CTLE Standard button, 29 Filter Interactions, 33 Α Custom bandwidth limit, 19 Filter Response, 21 Adapt from Current taps, 24 custom filter (IIR), 28 Filter Types, 17 Adc CTLE parameter, 27 filter verification, 10 Adjusting the CTLE Equalizer, 27 FIR Filter Format, 33 Adjusting the Equalizer, 23 FIR filter saving, 15 Data Input Type, 17 Amplitude, 23 FIR Filter selection, 17 Data signal R4, 22 Analyze button, 7 Fixture and Channel Blocks, 17 DC to Starting Frequency, 34 analyze link quality, 7 Fixture Block, 17 de-emphasis, 20 application Fixture FIR filter, 15 decision feedback equalizer, 21 switch, 7 Fp1 CTLE parameter, 28 denominator (IIR filter), 28 application requirements, 3 Fp2 CTLE parameter, 28 DFE Taps, 23 Apply button, 7 free ten uses, 3 Differential S-Parameter, 17 Auto adapt Taps, 24 Frequency Domain Plots, 10 directory path, 2 Auto bandwidth limit, 19 Fz CTLE parameter, 28 Display Plots, 10 Autoset Voltages, 24 DPOJET application, 7 G DPOJET use, 7 B Getting Started, 3 Bandwidth Limit, 18 GPIB Commands, 37 E Bandwidth Limit usage, 19 APPLICATION: ACTIVATE Emphasis Block, 20 bandwidth requirement, 3 "Serial Data Link enable GPIB, 37 bit rate, 22 Analysis", 38 Enable Output Waveforms, 6 Bit Rate and Filter Response, 21 VARIABLE: VALUE "sdla", Enabling Processing Blocks, 6 "p:analyze", 39 Equalizer adjustment, 23 C VARIABLE: VALUE "sdla", Equalizer Block, 21 "p:apply", 40 Channel Block, 17 Equalizer configuration, 22 VARIABLE: VALUE "sdla". Channel FIR filter, 15 Example waveforms "p:bitrate:<value>", 40 circuit block filters, 6 location, 15 VARIABLE: VALUE "sdla", circuit blocks, 4 Extending Filter Data, 34 "p:exit", 40 Clk Delay, 24 Extending Upper Bandwidth, 35 VARIABLE: VALUE "sdla", clock recovery, 22 Extrapolation of Filter Data, 34 "p:recall:<path/file name Clock Recovery >", 41 troubleshooting, 26 F VARIABLE: VALUE "sdla", Clock signal Clk R3, 22 "p:rx, 42 feed forward equalizer, 21 Configuring Blocks, 6 VARIABLE: VALUE "sdla", FFE Taps, 23

FFE/DFE selector, 22

File Types and Locations, 15

configuring the Equalizer, 22

continuous time linear

equalizer, 21

"p:source:<source>", 41

| VARIABLE: VALUE "sdla",        | phase locked loop, 22                   | Signal Path Window, 3           |

|--------------------------------|-----------------------------------------|---------------------------------|

| "p:tx, 42                      | PLL BW, 23                              | signal recovery, 27             |

| VARIABLE: VALUE?               | PLL Damp, 23                            | Single-Ended S-Parameter, 18    |

| "sdla", 39                     | PLL Type, 23                            | sleep state, 7                  |

| GPIB Control Menu, 37          | Plot Window Tools, 14                   | Software Compatibility, 3       |

| GPIB enable, 37                | plots                                   | Software reinstallation, 3      |

| GPIB handshaking protocol, 38  | Amplitude Versus Time, 12               | Software Updates, 2             |

| GPIB View selector, 37         | color code, 12                          | standards                       |

|                                | filter configuration                    | location, 15                    |

| Н                              | verification, 10                        | Standards, 6                    |

| Handshaking Protocol, 38       | test point, 10                          | Standards button, 6             |

| ,                              | Plots, 10                               | switch to DPOJET application,   |

| I                              | Magnitude and Phase, 13                 | switch to TekScope display, 5   |

| HD cl 20                       | polynomial transfer function (IIR       | _                               |

| IIR custom filter, 28          | filter), 28                             | T                               |

| improving signal recovery, 27  | pre-emphasis, 20                        | Taps Tab Settings, 25           |

| Input filters                  | Processing Blocks                       | Taps Tab Settings (PcieD), 25   |

| location, 15                   | enable, 6                               | Test Point Filters, 34          |

| Installation, 3                | Product Overview, 1                     | test point FIR filters          |

| installation path, 2           |                                         | saving, 7                       |

|                                | R                                       | test point plots, 10            |

| L                              | R3 labeled Clock waveform, 22           | Test Points, 6                  |

| Loading Standards, 6           | R4 labeled Data waveform, 22            | Text Conventions, 2             |

|                                | Recall button, 5                        | Threshold, 23                   |

| M                              | recalling setups, 5                     | Time Domain Plots, 10           |

|                                | recovering the data clock, 23           | TpA, 7                          |

| Math4 waveform, 22             | Ref Tap, 23                             | TpB, 7                          |

| moving between applications, 5 | reference receiver, 21                  | TpC, 7                          |

|                                | Reinstall the SDLA Software, 3          | TrainSeq, 24                    |

| N                              | remote Commands, 37                     | TrainSeq tab, 26                |

| Notes on Bandwidth Limit, 19   | Requirements, 3                         | Troubleshooting Clock           |

| numerator (IIR filter), 28     | Running a Test, 35                      | Recovery, 26                    |

| , ,,,                          | Running the Equalizer, 22               | Tx Configuration, 9             |

| 0                              | Rx Configuration, 9                     |                                 |

|                                |                                         | U                               |

| Operating Basics, 17           | S                                       | Updates                         |

| Option Key Requirement, 3      | Sample/bit, 23                          | Software, 2                     |

| oscilloscope display, 3        | Save button, 5                          | Use TrainSeq, 24                |

| Output filters                 | Save recall                             | ose manised, 21                 |

| location, 15                   | location, 15                            | V                               |

| saving, 15                     | saving settings, 5                      | •                               |

| Output Waveforms               | saving setups, 5                        | verify filter configuration, 10 |

| enable, 6                      | Sdd21, 18                               | View Pcie Tbl (PcieC), 30       |

| Overview, 1                    | sdl file extension, 5                   | View Pcie Tbl (PcieD), 25       |

| B                              | SDLA application window, 3              | View selector, 37               |

| P                              | Setups, 5                               |                                 |

| PcieD, 24                      | Signal Bit Rate, 21                     |                                 |

|                                | - · · · · · · · · · · · · · · · · · · · |                                 |

7

Web Site software update, 2