AWG7000C Series

Arbitrary Waveform Generators

Specifications and Performance Verification

Technical Reference

AWG7000C Series

Arbitrary Waveform Generators

Specifications and Performance Verification

Technical Reference

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries before performing service.

www.tektronix.com

077-0456-02

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are protected by national copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

TekLink is a trademark of Tektronix, Inc.

#### **Contacting Tektronix**

Tektronix, Inc. 14150 SW Karl Braun Drive P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- = In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

#### Warranty

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product. Parts, modules and replacement products used by Tektronix for warranty work may be new or reconditioned to like new performance. All replaced parts, modules and products become the property of Tektronix.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THE PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

[W2 - 15AUG04]

# **Table of Contents**

| General Safety Summary                 | 1V  |

|----------------------------------------|-----|

| Service Safety Summary                 | vi  |

| Preface                                | vii |

| Related Documents                      | vii |

| Specifications                         | 1   |

| Performance Conditions                 | 1   |

| Electrical Specifications.             | 2   |

| Mechanical (Physical) Characteristics. | 15  |

| Environmental Characteristics          | 16  |

| Performance Verification Procedures    | 17  |

| Brief Procedures                       | 18  |

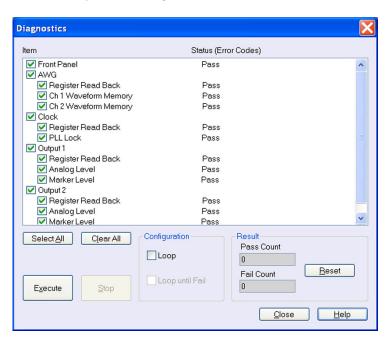

| Diagnostics                            | 18  |

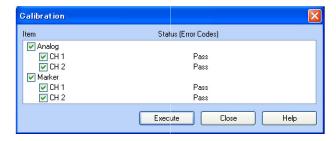

| Calibration                            | 19  |

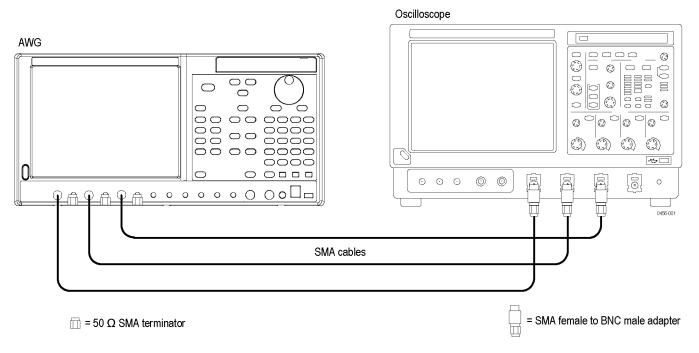

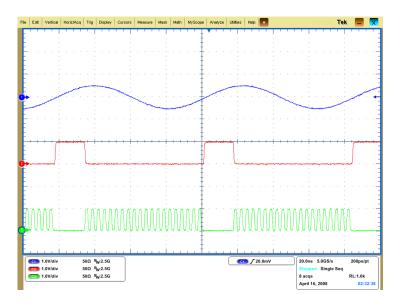

| Functional Test                        | 20  |

| Performance Tests                      | 23  |

| Prerequisites                          | 23  |

| Required Equipment                     | 23  |

| Test Record                            | 25  |

| 10 MHz Reference Frequency Accuracy    | 33  |

| Analog Offset Accuracy                 | 34  |

| Analog Amplitude Accuracy              | 36  |

| Analog Harmonic Distortion             | 39  |

| Analog Non-Harmonic Spurious Signal.   | 41  |

| Analog Phase Noise                     | 43  |

| Marker High and Low Level Accuracy     |     |

| Marker Output Delay Accuracy           | 48  |

| DC Output Voltage Accuracy             | 50  |

# **List of Figures**

| Figure 1: Diagnostics dialog box                                                     | 18 |

|--------------------------------------------------------------------------------------|----|

| Figure 2: Calibration dialog box                                                     | 19 |

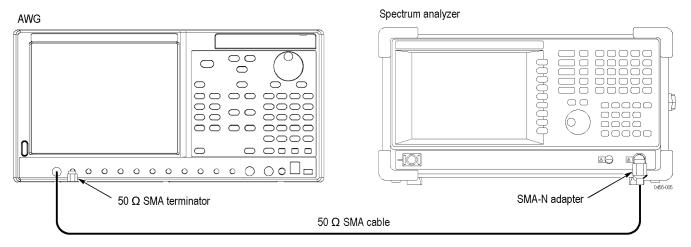

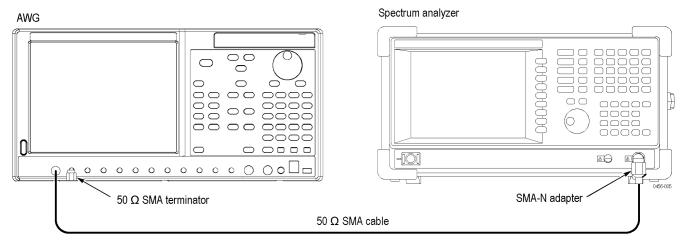

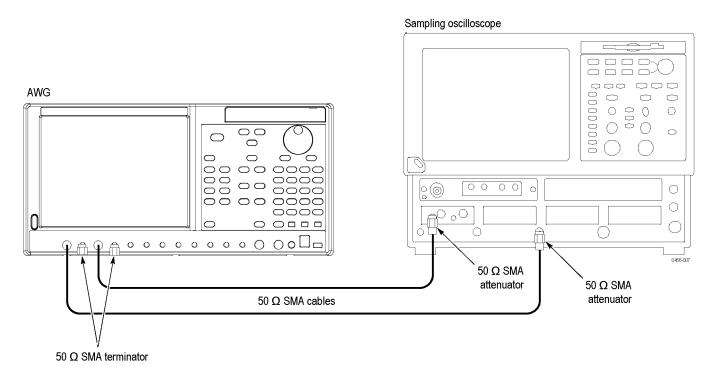

| Figure 3: Equipment connections for checking the analog and marker outputs           | 21 |

| Figure 4: Output waveform from the Analog, Mkr 1, and Mkr 2 connectors               | 22 |

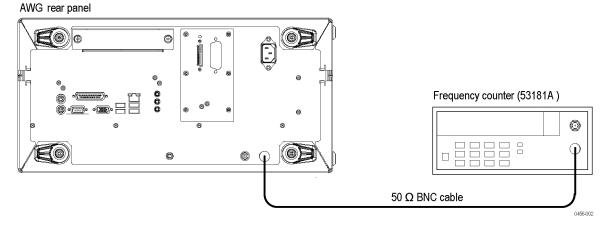

| Figure 5: Equipment connection for verifying the 10 MHz reference frequency accuracy | 33 |

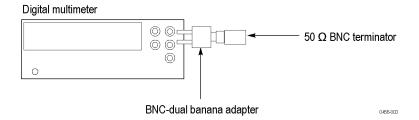

| Figure 6: Equipment connection for measuring the termination resistance              | 34 |

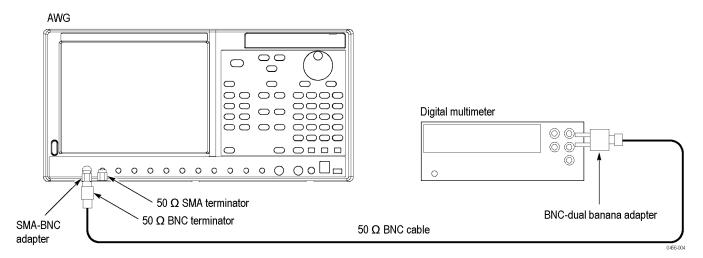

| Figure 7: Equipment connection for verifying the analog offset accuracy              | 35 |

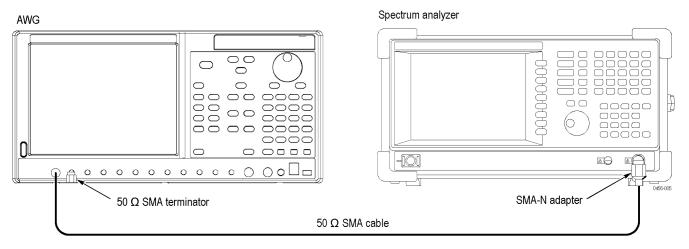

| Figure 8: Equipment connections for verifying the analog harmonic distortion         | 39 |

| Figure 9: Equipment connections for verifying the non-harmonic spurious signal       | 41 |

| Figure 10: Equipment connections for verifying the analog phase noise                | 43 |

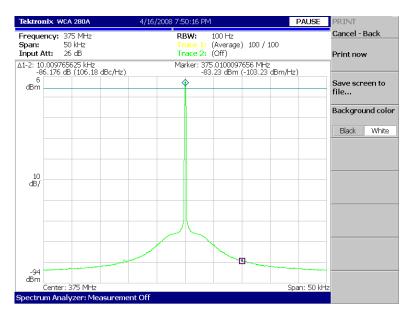

| Figure 11: Example of the analog phase noise measurement.                            | 45 |

| Figure 12: Equipment connection for verifying the marker high and low level accuracy | 46 |

| Figure 13: Equipment connections for verifying the marker output delay accuracy      | 49 |

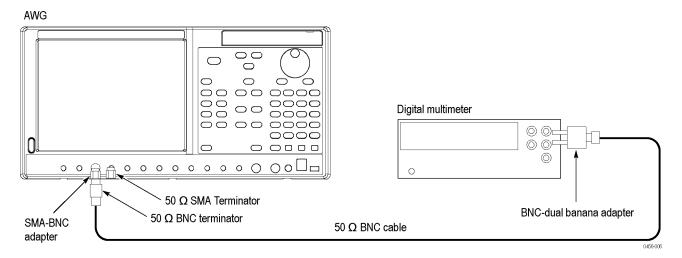

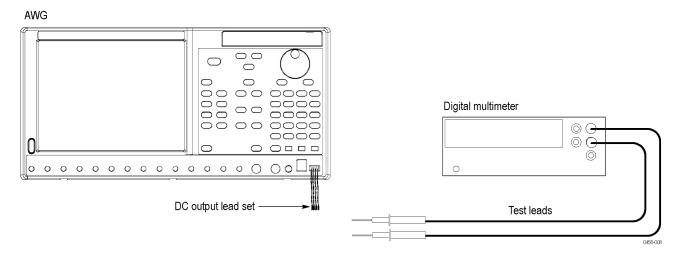

| Figure 14: Equipment connection for verifying the DC output voltage accuracy         | 51 |

## **List of Tables**

| Table 1: Run mode                                    | 2  |

|------------------------------------------------------|----|

| Table 2: Arbitrary waveform                          | 2  |

| Table 3: Clock generator                             | 3  |

| Table 4: Trigger generator                           | 4  |

| Table 5: Inter-channel skew control                  | 4  |

| Table 6: Interleave adjustment (Option 06).          | 4  |

| Table 7: Waveform rotation control for analog output | 5  |

| Table 8: Analog output (Standard)                    | 5  |

| Table 9: Analog output (Option 02 and 06)            | 7  |

| Table 10: Interleave analog output (Option 06)       | 8  |

| Table 11: Marker output                              | 9  |

| Table 12: Trigger and gate input                     | 10 |

| Table 13: Event input                                | 11 |

| Table 14: Reference clock input                      | 12 |

| Table 15: Oscillator (External clock) input.         | 12 |

| Table 16: DC output                                  | 12 |

| Table 17: Dynamic Jump In connector                  | 13 |

| Table 18: 10 MHz clock output                        | 14 |

| Table 19: TekLink port                               | 14 |

| Table 20: CPU module and peripheral devices.         | 14 |

| Table 21: Display                                    | 14 |

| Table 22: Power supply                               | 15 |

| Table 23: Mechanical characteristics.                | 15 |

| Table 24: Environmental characteristics              | 16 |

| Table 25: Required equipment                         | 23 |

| Table 26: Test waveforms                             | 24 |

| Table 27: Analog offset accuracy                     | 35 |

| Table 28: Analog amplitude accuracy                  | 37 |

| Table 29: Analog harmonic distortion.                | 40 |

| Table 30: Analog non-harmonic spurious signal        | 42 |

| Table 31: Analog phase noise                         | 44 |

| Table 32: Marker High and Low level accuracy         | 46 |

| Table 33: DC output voltage accuracy                 | 51 |

## **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.

To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

# To Avoid Fire or Personal Injury

**Use proper power cord.** Use only the power cord specified for this product and certified for the country of use.

**Ground the product.** This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe all terminal ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

**Power disconnect.** The power cord disconnects the product from the power source. Do not block the power cord; it must remain accessible to the user at all times.

**Do not operate without covers.** Do not operate this product with covers or panels removed.

**Do not operate with suspected failures.** If you suspect that there is damage to this product, have it inspected by qualified service personnel.

**Avoid exposed circuitry.** Do not touch exposed connections and components when power is present.

Do not operate in wet/damp conditions.

Do not operate in an explosive atmosphere.

Keep product surfaces clean and dry.

**Provide proper ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

#### **Terms in This Manual**

These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

#### Symbols and Terms on the **Product**

These terms may appear on the product:

- DANGER indicates an injury hazard immediately accessible as you read the marking.

- WARNING indicates an injury hazard not immediately accessible as you read the marking.

- CAUTION indicates a hazard to property including the product.

The following symbol(s) may appear on the product:

Refer to Manual

High Voltage

Protective Ground (Earth) Terminal

Earth Terminal

Chassis Ground

Standby

## **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone.** Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power.** To avoid electric shock, switch off the instrument power, then disconnect the power cord from the mains power.

**Use Care When Servicing With Power On.** Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

## **Preface**

This manual contains specifications and performance verification procedures for the AWG7000C Series Arbitrary Waveform Generators.

#### **Related Documents**

The following user documents are also available for this product:

- AWG5000 and AWG7000 Series Arbitrary Waveform Generators Quick Start User Manual. This document describes the functions and use of the instrument.

- AWG7000 Series Arbitrary Waveform Generators Service Manual. This is a PDF only manual that provides module-level service information. It can be downloaded from the Tektronix Web site.

## **Specifications**

This section contains the specifications for the instruments.

All specifications are guaranteed unless noted as (Typical). Typical specifications are provided for your convenience but are not guaranteed. Specifications that are marked with the  $\nu$  symbol are checked in this manual.

#### **Performance Conditions**

To meet specifications, the following conditions must be met:

- The instrument must have been calibrated/adjusted at an ambient temperature between +20 °C and +30 °C.

- The instrument must be operating within the environmental limits. (See Table 24 on page 16.)

- The instrument must be powered from a source that meets the specifications. (See Table 22 on page 15.)

- The instrument must have been operating continuously for at least 20 minutes within the specified operating temperature range.

## **Electrical Specifications**

Table 1: Run mode

| Characteristics   | Description                                                                                                                                                                                                           |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Continuous mode   | An arbitrary waveform is output continuously.                                                                                                                                                                         |  |

| Triggered mode    | An arbitrary waveform is output only once when a trigger signal is applied. After the waveform is output, the instrument waits for the next trigger signal.                                                           |  |

| Gated mode        | An arbitrary waveform is output only when a gate signal is asserted. The waveform output is repeated while the gate signal stays asserted. When the gate signal is deasserted, the waveform output stops immediately. |  |

| Sequence mode     |                                                                                                                                                                                                                       |  |

| Without Option 08 | Sequence switching with wait trigger                                                                                                                                                                                  |  |

| Option 08         | Fast sequence switching                                                                                                                                                                                               |  |

#### Table 2: Arbitrary waveform

| Description                                                                                      |  |

|--------------------------------------------------------------------------------------------------|--|

|                                                                                                  |  |

| 1 to 32,400,000 points (Interleave is off)                                                       |  |

| 2 to 64,800,000 points (Option 06, Interleave is on)                                             |  |

| 1 to 64,800,000 points (Interleave is off)                                                       |  |

| 2 to 129,600,000 points (Interleave is on)                                                       |  |

| 960 points minimum (Interleave is off)                                                           |  |

| 1920 points minimum (Option 06, Interleave is on)                                                |  |

| 1 point                                                                                          |  |

| 4 points (AWG7082C, AWG7122C)                                                                    |  |

| 8 points (AWG7082C, AWG7122C Option 06, Interleave on)                                           |  |

| 10 bits or 8 bits selectable (when the 10 bits DAC mode is selected, marker output is disabled.) |  |

| Up to 32,000 waveforms (predefined waveforms are not included)                                   |  |

| 1 to 16,000 steps                                                                                |  |

|                                                                                                  |  |

| Repeat count, Wait-for-Trigger (On only), Go-to-N, and Jump are available                        |  |

| Repeat count, Wait-for-Trigger (On or Off), Go-to-N, and Jump are available                      |  |

| 1 to 65,536 or infinite (all channels operate the same sequence)                                 |  |

| Synchronous or Asynchronous selectable                                                           |  |

|                                                                                                  |  |

Table 2: Arbitrary waveform (cont.)

| Description       |

|-------------------|

|                   |

| 8 ns (AWG7082C)   |

| 106 μs (AWG7122C) |

| 8 ns (AWG7082C)   |

| 106 μs (AWG7122C) |

| 160 μs (AWG7082C) |

| 106 μs (AWG7122C) |

| 312 ps (AWG7082C) |

| 208 ps (AWG7122C) |

| 312 ps (AWG7082C) |

| 208 ps (AWG7122C) |

| 156 ps (AWG7082C) |

| 104 ps (AWG7122C) |

|                   |

#### **Table 3: Clock generator**

| Characteristics                             | Description                            |

|---------------------------------------------|----------------------------------------|

| Sampling rate control                       |                                        |

| Range                                       |                                        |

| AWG7122C                                    | 10 MS/s to 12 GS/s (Interleave is off) |

| AWG7122C with<br>Option 06 <sup>1</sup>     | 12 GS/s to 24 GS/s (Interleave is on)  |

| AWG7082C                                    | 10 MS/s to 8 GS/s (Interleave is off)  |

| AWG7082C with<br>Option 06 <sup>1</sup>     | 8 GS/s to 16 GS/s (Interleave is on)   |

| Resolution                                  | 8 digits                               |

| ✓ Internal clock frequency                  | Within ± (1 ppm + aging)               |

| Internal clock frequency accuracy (Typical) | Aging: within ± 1 ppm/year             |

| ✓ Reference oscillator accuracy             | Within ± (1 ppm + aging)               |

| Reference oscillator aging (Typical)        | Aging: within ± 1 ppm/year             |

<sup>1</sup> Interleaving is applied to analog output. When interleaving is on, marker data with even numbers will be output.

**Table 4: Trigger generator**

| Characteristics           | Description                      |  |

|---------------------------|----------------------------------|--|

| Trigger rate <sup>1</sup> |                                  |  |

| Range                     | 1.0 µs to 10.0 s                 |  |

| Resolution                | 0.1 µs minimum                   |  |

| Accuracy                  | Same as the reference oscillator |  |

<sup>1</sup> Trigger is ignored when all the following conditions are met:

• Instrument type: AWG7122C with Option 06, without Option 08

Run mode: SequenceInterleave: On

Table 5: Inter-channel skew control

| Characteristics           | Description                               |

|---------------------------|-------------------------------------------|

| Skew control              |                                           |

| Range                     | –100 ps to +100 ps                        |

| Resolution                | 1 ps                                      |

| Skew accuracy (Typical) 1 | ± (10% of effective skew setting +10 ps)  |

|                           | Direct output mode on standard instrument |

<sup>1</sup> Effective skew setting is the absolute value of the difference between the skew setting on channels.

Table 6: Interleave adjustment (Option 06)

| Characteristics      | Description                                      |

|----------------------|--------------------------------------------------|

| Phase adjustment     |                                                  |

| Range                | –180 ° to +180 °                                 |

| Resolution           | 0.1 °                                            |

| Amplitude adjustment | At amplitude setting 0.75 V <sub>p-p</sub>       |

| Range <sup>1</sup>   | –0.25 V <sub>p-p</sub> to +0.25 V <sub>p-p</sub> |

| Resolution           | 0.001 V                                          |

<sup>1</sup> Range depends on the amplitude settings.

(Amplitude setting + Adjustment) and (Amplitude setting - Adjustment) should be within the following range:

- 0.5  $V_{\mbox{\tiny p-p}}$  to 1.0  $V_{\mbox{\tiny p-p}}$  with zeroing off

- 0.25  $V_{\text{p-p}}$  to 0.5  $V_{\text{p-p}}$  with zeroing on

Table 7: Waveform rotation control for analog output

| Characteristics | Description                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------|

| Phase control   |                                                                                                                  |

| Range           | CVR Gain stability is ±0.1% if measured within 25° of the temperature at factory calibration                     |

| Resolution      | CVR Gain linearity is $\pm 0.2\%$ . Perform an automatic sweep and take voltage measurements at every DAC value. |

| Time control    |                                                                                                                  |

| Range           | -1/2 period to +1/2 period of waveform                                                                           |

| Resolution      | 0.1 ps                                                                                                           |

| Point control   |                                                                                                                  |

| Range           | -50% to +50% of waveform                                                                                         |

| Resolution      | 0.001 points                                                                                                     |

Table 8: Analog output (Standard)

| Characteristics          | Description                                                          |

|--------------------------|----------------------------------------------------------------------|

| Connector type           | SMA on front panel                                                   |

| Type of output           | (+) and (-) complementary output                                     |

| Output impedance         | 50 Ω                                                                 |

| Amplitude controls       |                                                                      |

| Range                    |                                                                      |

| Normal mode              | 50 mV to 2.0 $V_{p-p}$                                               |

| Direct D/A mode          | 50 mV to 1.0 $V_{p-p}$                                               |

| Resolution               | 1 mV                                                                 |

| Offset controls          |                                                                      |

| Range                    |                                                                      |

| Normal mode              | –0.5 V to +0.5 V                                                     |

| Direct D/A mode          | N/A                                                                  |

| Resolution               | 1 mV                                                                 |

| Amplitude accuracy       | DC accuracy: within ± (3% of amplitude + 2 mV) at offset = 0V        |

| ✓ Offset accuracy        | DC accuracy: within ± (2% of amplitude + 10 mV) at minimum amplitude |

| Bandwidth (Typical)      |                                                                      |

| Normal mode              | 750 MHz, at -3 dB                                                    |

| Direct D/A mode          | 3.5 GHz, at -3 dB                                                    |

| Rise/fall time (Typical) |                                                                      |

| Normal mode              | 350 ps (20% to 80%), when amplitude = 2.0 $V_{p-p}$ , offset = 0 $V$ |

| Direct D/A mode          | 75 ps (20% to 80%), when amplitude = 1.0 V <sub>p-p</sub>            |

| Overshoot (Typical)      | < 10%, when amplitude = 1.0 V <sub>p-p</sub>                         |

Table 8: Analog output (Standard) (cont.)

| Characteristics                                     | Description                                                                                                                                                      |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low pass filter                                     |                                                                                                                                                                  |

| Normal mode                                         | 50 MHz, 200 MHz, Through (Bessel type)                                                                                                                           |

| Direct D/A mode                                     | N/A                                                                                                                                                              |

| Delay from marker (Typical)                         | 10.15 ns ±0.15 ns: low pass = 50 MHz                                                                                                                             |

|                                                     | $4.05 \text{ ns } \pm 0.05 \text{ ns: low pass} = 200 \text{ MHz}$                                                                                               |

|                                                     | 2.26 ns ±0.04 ns: low pass = Through                                                                                                                             |

|                                                     | 0.585 ns ±0.045 ns: Direct output mode                                                                                                                           |

|                                                     | (when amplitude = 1.0 $V_{p-p}$ , offset = 0 V)                                                                                                                  |

| Skew between (+) and (–) outputs ( <i>Typical</i> ) | < 20 ps (direct D/A mode)                                                                                                                                        |

| ON/OFF control                                      | Output relay is available for each channel. The control is common to the complementary output.                                                                   |

| ✓ Harmonic distortion                               | Amplitude = 1.0 $V_{p-p}$ , offset = 0 V, DAC resolution = 10 bits, measured with 32-point sine waveform, defined up to 5 <sup>th</sup> harmonic                 |

| AWG7122C Normal mode                                | < –35 dBc, when clock = 12 GS/s, signal = 375 MHz                                                                                                                |

| AWG7122C Direct D/A mode                            | < –42 dBc, when clock = 12 GS/s, signal = 375 MHz                                                                                                                |

| AWG7082C Normal mode                                | < -37 dBc, when clock = 8 GS/s, signal = 250 MHz                                                                                                                 |

| AWG7082C Direct D/A mode                            | < -43 dBc, when clock = 8 GS/s, signal = 250 MHz                                                                                                                 |

| Non-harmonic spurious                               | Amplitude = 1.0 $V_{p-p}$ , offset = 0 V, DAC resolution = 10 bits, measured with 32-point sine waveform, measurement range is DC to sampling_frequency $\div$ 2 |

| AWG7122C                                            | < –50 dBc, DC to 6 GHz, when clock = 12 GS/s, signal = 375 MHz                                                                                                   |

| AWG7082C                                            | < -50 dBc, DC to 4 GHz, when clock = 8 GS/s, signal = 250 MHz                                                                                                    |

| SFDR (Typical)                                      | Normal output mode, amplitude = 1.0 $V_{p-p}$ , offset = 0 V, DAC resolution = 10 bits, measurement range is DC to sampling_frequency $\div$ 2                   |

| AWG7122C                                            | 43 dBc, when clock = 12 GS/s, signal = 375 MHz                                                                                                                   |

| AWG7122C, AWG7082C                                  | 45 dBc, when clock = 8 GS/s, signal = 250 MHz                                                                                                                    |

| Phase noise                                         | Normal output mode, amplitude = $1.0 \text{ V}_{p-p}$ , offset = $0 \text{ V}$ , DAC resolution = $10 \text{ bits}$ , measured with 32-point sine waveform       |

| AWG7122C                                            | < -90 dBc/Hz at 10 kHz offset, when clock = 12 GS/s, signal = 375 MHz                                                                                            |

| AWG7082C                                            | < -90 dBc/Hz at 10 kHz offset, when clock = 8 GS/s, signal = 250 MHz                                                                                             |

| Random jitter on clock pattern ( <i>Typical</i> )   | Using 0101 clock pattern, amplitude = 1.0 $V_{p-p}$ , offset = 0 $V$                                                                                             |

| Normal mode                                         | 1.6 ps <sub>RMS</sub>                                                                                                                                            |

| Direct D/A mode                                     | 0.45 ps <sub>rms</sub>                                                                                                                                           |

| Total jitter on random pattern ( <i>Typical</i> )   | Using PN15 pattern, amplitude = 1.0 V <sub>p-p</sub> , offset = 0 V, measured at bit error rate = 1e <sup>-12</sup>                                              |

| Normal mode                                         | 50 ps <sub>p-p</sub> at 500 MS/s                                                                                                                                 |

| Direct D/A mode                                     | 30 ps p-p from 1 GS/s to 6 GS/s                                                                                                                                  |

| Amplitude flatness (Typical)                        | ±2 db from 50 MHz to 3.5 GHz                                                                                                                                     |

|                                                     | Measured with Direct Output at 50 MHz increments, mathematically corrected for sin(x)/x roll-off                                                                 |

Table 9: Analog output (Option 02 and 06)

| Characteristics                                     | Description                                                                                                                                                   |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector type                                      | SMA on front panel                                                                                                                                            |

| Type of output                                      | (+) and (–) complementary outputs                                                                                                                             |

| Output impedance                                    | 50 Ω                                                                                                                                                          |

| Amplitude controls                                  |                                                                                                                                                               |

| Range                                               | 0.5 V to 1.0 V <sub>p-p</sub>                                                                                                                                 |

| Resolution                                          | 1 mV                                                                                                                                                          |

| ✓ Amplitude accuracy                                | DC accuracy: Within ± (2% of amplitude + 2 mV) at offset = 0V                                                                                                 |

| ✓ DC offset                                         | Within ± 10 mV                                                                                                                                                |

| Bandwidth ( <i>Typical</i> )                        | 7.5 GHz at –3 dB                                                                                                                                              |

| Rise/fall time (Typical)                            | 35 ps (20% to 80%), when amplitude = 1.0 $V_{p-p}$                                                                                                            |

| Overshoot (Typical)                                 | < 3%, when amplitude = 1.0 V <sub>p-p</sub>                                                                                                                   |

| Delay from marker (Typical)                         | Option 02:                                                                                                                                                    |

|                                                     | $0.185 \text{ ns } \pm 0.05 \text{ ns}$ , when amplitude = $1.0 \text{ V}_{p-p}$                                                                              |

|                                                     | Option 06                                                                                                                                                     |

|                                                     | 1.025 ns $\pm 0.05$ ns, when amplitude = 1.0 $V_{p-p}$                                                                                                        |

| Skew between (+) and (–) outputs ( <i>Typical</i> ) | < 12 ps                                                                                                                                                       |

| ON/OFF control                                      | Output relay is available for each channel. The control is common to the complementary output.                                                                |

| Harmonic distortion                                 | Amplitude = $1.0 \text{ V}_{\text{p-p}}$ , DAC resolution = 10 bit, measured with 32-point sine waveform, defined up to 5th harmonic                          |

| AWG7122C                                            | < -42 dBc, when clock = 12 GS/s, signal = 375 MHz                                                                                                             |

| AWG7082C                                            | < -44 dBc, when clock = 8 GS/s, signal = 250 MHz                                                                                                              |

| ✓ Non-harmonic spurious                             | Amplitude = $1.0 \text{ V}_{\text{p-p}}$ , resolution = 10 bits, measured with 32-point sine waveform, measurement range is DC to sampling frequency $\div$ 2 |

| AWG7122C                                            | < -50 dBc, DC to 6 GHz, when clock = 12 GS/s, signa I =375 MHz                                                                                                |

| AWG7082C                                            | < -50 dBc, DC to 4 GHz, when clock = 8 GS/s, signal = 250 MHz                                                                                                 |

| SFDR (Typical)                                      | Amplitude = 1.0 V <sub>p-p</sub> , DAC resolution = 10 bits, measurement range is DC to sampling frequency ÷ 2 including harmonics                            |

| AWG7122C                                            | 44 dBc, when clock = 12 GS/s, signal = 375 MHz                                                                                                                |

| AWG7082C                                            | 46 dBc, when clock = 8 GS/s, signal = 250 MHz                                                                                                                 |

| ✓ Phase noise                                       | Amplitude = 1.0 V <sub>p-p</sub> , DAC resolution = 10 bit, measured with 32 point sine waveform                                                              |

| AWG7122C                                            | < -90 dBc/Hz at 10 kHz offset, when clock = 12 GS/s, signal = 375 MHz                                                                                         |

| AWG7082C                                            | < -90 dBc/Hz at 10 kHz offset, when clock = 8 GS/s, signal = 250 MHz                                                                                          |

| Random jitter on clock pattern ( <i>Typical</i> )   | $0.4 \text{ ps}_{\text{RMS}}$ , using $0101$ clock pattern, amplitude = $1.0 \text{ V}_{\text{p-p}}$ , measured for five minutes                              |

| Total jitter on random pattern ( <i>Typical</i> )   | 20 ps <sub>p-p</sub> from 2 GS/s to 12 GS/s, PN15 pattern, amplitude = 1.0 $V_{p-p}$ , measured at bit error rate = $1e^{-12}$ for five minutes               |

| Amplitude flatness (Typical)                        | ±2 dB from 50 MHz to 4.8 GHz                                                                                                                                  |

|                                                     | Measured at 50 MHz increments, mathematically corrected for sin(x)/x roll-off                                                                                 |

Table 10: Interleave analog output (Option 06)

| Characteristics                            | Description                                                                                                                                             |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector type                             | SMA on front panel                                                                                                                                      |

| Type of output                             | (+) and (–) complementary output                                                                                                                        |

| Output impedance                           | 50 Ω                                                                                                                                                    |

| Zeroing control                            | Zeroing On and Off is selectable.                                                                                                                       |

| Amplitude controls                         |                                                                                                                                                         |

| Range                                      | 0.25 V to 0.5 V <sub>p-p</sub> , Zeroing = On                                                                                                           |

|                                            | 0.5 V to 1.0 $V_{p-p}$ , Zeroing = Off                                                                                                                  |

| Resolution                                 | 1 mV                                                                                                                                                    |

| Amplitude accuracy (Typical)               | DC accuracy at offset = 0 V                                                                                                                             |

|                                            | Within ± (40% of amplitude + 2 mV), Zeroing = On                                                                                                        |

|                                            | Within ± (8% of amplitude + 2 mV), Zeroing = Off                                                                                                        |

| ✓ DC offset                                | Within ± 10 mV                                                                                                                                          |

| Bandwidth (Typical)                        | 7.5 GHz at $-3$ dB, when amplitude = 0.5 $V_{p-p}$ , zeroing = On                                                                                       |

| Rise/fall time (Typical)                   | 35 ps (20% to 80%), when amplitude = $0.5 V_{p-p}$ , zeroing = On                                                                                       |

| Delay from marker (Typical)                | 0.86 ns ±0.05 ns when amplitude = 0.5 V <sub>p-p</sub> , zeroing = On                                                                                   |

| Skew between (+) and (-) outputs (Typical) | < 12 ps                                                                                                                                                 |

| ON/OFF control                             | Output relay is available for each channel. The control is common to the complementary output.                                                          |

| Harmonic distortion ( <i>Typical</i> )     | Measured with 32-point sine waveform, defined up to 5 <sup>th</sup> harmonics                                                                           |

| AWG7122C                                   |                                                                                                                                                         |

| Zeroing = On                               | < –38 dBc, when amplitude = 0.5 V <sub>p-p</sub> , clock = 24 GS/s, signal = 750 MHz                                                                    |

| Zeroing = Off                              | < –40 dBc, when amplitude = 1.0 V <sub>p-p</sub> , clock = 24 GS/s, signal = 750 MHz                                                                    |

| AWG7082C                                   |                                                                                                                                                         |

| Zeroing = On                               | < -38 dBc, when amplitude = 0.5 V <sub>p-p</sub> , clock = 16 GS/s, signal = 500 MHz                                                                    |

| Zeroing = Off                              | < -40 dBc, when amplitude = 1.0 V <sub>p-p</sub> , clock = 16 GS/s, signal = 500 MHz                                                                    |

| Non-harmonic spurious ( <i>Typical</i> )   | Amplitude = 1.0 V $_{\text{p-p}}$ , DAC resolution = 10 bit, measured with 32-point sine waveform, measurement range: DC to sampling frequency $\div$ 4 |

| AWG7122C                                   |                                                                                                                                                         |

| Zeroing = On                               | < -45 dBc, DC to 6 GHz, when amplitude = 0.5 V <sub>p-p</sub> , clock = 24 GS/s, signal = 750 MHz                                                       |

| Zeroing = Off                              | < -45 dBc, DC to 6 GHz, when amplitude = 1.0 V <sub>p-p</sub> , clock = 24 GS/s, signal = 750 MHz                                                       |

| AWG7082C                                   |                                                                                                                                                         |

| Zeroing = On                               | < -45 dBc, DC to 4 GHz, when amplitude = 0.5 V <sub>p-p</sub> , clock = 16 GS/s, signal = 500 MHz                                                       |

| Zeroing = Off                              | < -45 dBc, DC to 4 GHz, when amplitude = 1.0 $V_{p-p}$ , clock = 16 GS/s, signal = 500 MHz                                                              |

Table 10: Interleave analog output (Option 06) (cont.)

| Characteristics              | Description                                                                                               |

|------------------------------|-----------------------------------------------------------------------------------------------------------|

| SFDR (Typical)               | Amplitude = 1.0 $V_{p-p}$ , DAC resolution = 10 bit, measurement range: DC to sampling frequency $\div$ 2 |

| AWG7122C                     |                                                                                                           |

| Zeroing = On                 | 30 dBc, when amplitude = $0.5 V_{p-p}$ , clock = 24 GS/s, signal = 3 GHz                                  |

| Zeroing = Off                | 40 dBc, when amplitude = 1.0 $V_{p-p}$ , clock = 24 GS/s, signal = 3 GHz                                  |

| AWG7082C                     |                                                                                                           |

| Zeroing = On                 | 30 dBc, when amplitude = $0.5 V_{p-p}$ , clock = $16 GS/s$ , signal = $2 GHz$                             |

| Zeroing = Off                | 40 dBc, when amplitude = 1.0 $V_{p-p}$ , clock = 16 GS/s, signal = 2 GHz                                  |

| ✓ Phase noise                | DAC resolution = 10 bit, measured with 32-point sine waveform                                             |

| AWG7122C                     |                                                                                                           |

| Zeroing = On                 | < -85 dBc/Hz at 10 kHz offset, when amplitude = 0.5 V <sub>p-p</sub> , clock = 24 GS/s, signal = 750 MHz  |

| Zeroing = Off                | < -85 dBc/Hz at 10 kHz offset, when amplitude = 1.0 $V_{p-p}$ , clock = 24 GS/s, signal = 750 MHz         |

| AWG7082C                     |                                                                                                           |

| Zeroing = On                 | < -85 dBc/Hz at 10 kHz offset, when amplitude = 0.5 V <sub>p-p</sub> , clock = 16 GS/s, signal = 500 MHz  |

| Zeroing = Off                | < -85 dBc/Hz at 10 kHz offset, when amplitude = 1.0 V <sub>p-p</sub> , clock = 16 GS/s, signal = 500 MHz  |

| Amplitude flatness (Typical) | ±3 dB from 50 MHz to 9.6 GHz                                                                              |

|                              | Measured with Zeroing ON, at 50 MHz increments, mathematically corrected for sin(x)/x roll-off            |

Table 11: Marker output

| Characteristics           | Description                                                                                                |

|---------------------------|------------------------------------------------------------------------------------------------------------|

| Connector type            | SMA on front panel                                                                                         |

| Number of outputs         | Marker 1 and Marker 2 are available for each channel.                                                      |

| Type of output            | (+) and (-) complementary output                                                                           |

| Output impedance          | 50 Ω                                                                                                       |

| Level controls            | Output voltage into RLOAD( $\Omega$ ) to GND is approximately (2 × RLOAD ÷ (50 + RLOAD)) × voltage setting |

| Voltage window            | –1.4 V to +1.4 V into 50 Ω                                                                                 |

| Amplitude                 | 0.5 $V_{p-p}$ to 1.4 $V_{p-p}$ into 50 Ω                                                                   |

| Resolution                | 0.01 V                                                                                                     |

| External termination      | When an external termination is used the termination voltage should be within –2.8 V to +2.8 V             |

| ✓ Level accuracy          | DC accuracy: $\pm$ (10% of  setting  + 75 mV) into 50 $\Omega$                                             |

| Output current            | ± 28 mA max                                                                                                |

| Variable delay control    | Available for Marker 1 and Marker 2                                                                        |

| Range                     | 0 to 300 ps                                                                                                |

| Resolution                | 1 ps                                                                                                       |

| ✓ Variable delay accuracy | ± (5% of setting + 50 ps)                                                                                  |

| Rise/fall time (Typical)  | 45 ps (20% to 80% of swing), when Hi = 1.0 V, Low = 0 V                                                    |

Table 11: Marker output (cont.)

| Characteristics                                       | Description                                                                                                                                                             |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Random jitter on clock pattern ( <i>Typical</i> )     | 1 ps <sub>RMS</sub> (using 0101 clock pattern), when Hi = 1.0 V, Low = 0 V                                                                                              |

| Total jitter on random pattern ( <i>Typical</i> )     | 30 ps $_{p-p}$ (using PN15 pattern, when Hi = 1.0 V, Low = 0 V, measured at bit error rate = $1e^{-12}$ )                                                               |

| Skew between (+) and (–) outputs ( <i>Typical</i> )   | < 13 ps                                                                                                                                                                 |

| Skew between Marker 1 and Marker 2 ( <i>Typical</i> ) | < 30 ps                                                                                                                                                                 |

| Aberrations (Typical)                                 |                                                                                                                                                                         |

| High speed                                            | < ±20% <sub>p-p</sub> for the first 1 ns following the step transition with 100% reference at 4 ns, for an ambient temperature range of 20 °C to 30 °C (68 °F to 86 °F) |

| Long term                                             | $<\pm5\%_{p-p}$ after 1 ns to 4 ns following the step transition with 100% reference at 4 ns, for an ambient temperature range of 20 °C to 30 °C (68 °F to 86 °F)       |

#### Table 12: Trigger and gate input

| Characteristics                          | Description                     |

|------------------------------------------|---------------------------------|

| Connector                                | BNC on front panel              |

| Input impedance                          | 1 kΩ or 50 Ω selectable         |

| Polarity                                 | Positive or negative selectable |

| Input voltage range                      |                                 |

| When 1 kΩ selected                       | –10 V to 10 V                   |

| When 50 Ω selected                       | < 5 V <sub>RMS</sub>            |

| Threshold control                        |                                 |

| Level                                    | –5.0 V to 5.0 V                 |

| Resolution                               | 0.1 V                           |

| Accuracy (Typical)                       | ± (5% of  setting  + 0.1 V)     |

| Input voltage swing (Typical)            | 0.5 V <sub>p-p</sub> minimum    |

| Minimum pulse width                      |                                 |

| Triggered mode                           | 20 ns                           |

| Gated mode                               | 1024 × sampling period + 210 ns |

| Trigger delay to analog output (Typical) | 128 × sampling period + 250 ns  |

| Trigger hold off (Typical)               | 832 × sampling period – 100 ns  |

| Gate delay to analog output (Typical)    | 640 × sampling period + 260 ns  |

Table 12: Trigger and gate input (cont.)

| Characteristics                                                     | Description                                                                                                                               |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger jitter (Typical)                                            | 0.7 ns at 12 GS/s                                                                                                                         |

|                                                                     | 0.8 ns at 9 GS/s                                                                                                                          |

|                                                                     | 1.0 ns at 6 GS/s                                                                                                                          |

| Synchronized between external clock and trigger timing              | 12 GS/s, x 1 clock divider, synchronous trigger mode with specific timing: 50 ps <sub>p-p</sub> , 10 ps <sub>RMS</sub>                    |

| Synchronized between external 10 MHz reference and trigger timing   | 12 GS/s setting, synchronous trigger mode with specific timing: 120 ps <sub>p-p</sub> , 30 ps <sub>RMS</sub>                              |

| Synchronized between external variable reference and trigger timing | $2^N$ (N: integer) Clock setting of reference, synchronous trigger mode with specific timing: 50 ps <sub>p-p</sub> , 10 ps <sub>RMS</sub> |

| Trigger timing                                                      | Selectable synchronous mode or asynchronous mode, settable only through the program interface.                                            |

#### Table 13: Event input

| Characteristics                  | Description                     |

|----------------------------------|---------------------------------|

| Connector type                   | BNC on front panel              |

| Input impedance                  | 1 kΩ or 50 $\Omega$ selectable  |

| Polarity                         | Positive or negative selectable |

| Input voltage range              |                                 |

| When 1 kΩ selected               | –10 V to 10 V                   |

| When 50 Ω selected               | < 5 V <sub>RMS</sub>            |

| Threshold control                |                                 |

| Level                            | –5.0 V to 5.0 V                 |

| Resolution                       | 0.1 V                           |

| Accuracy (Typical)               | ± (5% of  setting  + 0.1 V)     |

| Input voltage swing (Typical)    | 0.5 V <sub>p-p</sub> minimum    |

| Minimum pulse width              | 20 ns                           |

| Delay to analog output (Typical) | When asynchronous jump          |

|                                  | 1024 × sampling period + 280 ns |

| Hold off time (Typical)          | When hardware sequencer is used |

|                                  | 900 × sampling period + 150 ns  |

Table 14: Reference clock input

| Characteristics                     | Description                                                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Connector type                      | BNC on rear panel                                                                                                 |

| Input impedance                     | 50 Ω (AC coupled)                                                                                                 |

| Input voltage swing                 | $0.2 V_{p-p}$ to $3 V_{p-p}$                                                                                      |

| Fixed mode input frequency          | 10 MHz, 20 MHz, and 100 MHz within ± 0.1%                                                                         |

| Variable mode input frequency range | 10 MHz to 800 MHz Acceptable frequency drift while the instrument is operating: ± 0.1% Frequency should be stable |

| Variable mode multiplier rate       | The rate value is limited by sampling rate range.                                                                 |

| AWG7122C without interleave         | 1 to 2400                                                                                                         |

| AWG7122C with interleave            | 2 to 4800                                                                                                         |

| AWG7082C without interleave         | 1 to 1600                                                                                                         |

| AWG7082C with interleave            | 2 to 3200                                                                                                         |

#### Table 15: Oscillator (External clock) input

| Characteristics   | Description                                        |

|-------------------|----------------------------------------------------|

| Connector type    | SMA on rear panel                                  |

| Input impedance   | 50 Ω (AC coupled)                                  |

| Frequency range   | 6.0 GHz to 12.0 GHz                                |

|                   | Frequency should be stable.                        |

|                   | Acceptable frequency drift while running is ±0.1%. |

| Input power range | +7 dBm to +10 dBm                                  |

| Divider           | 1/1, 1/2, 1/4, 1/8, ,1/256                         |

#### Table 16: DC output

| Characteristics            | Description                                             |

|----------------------------|---------------------------------------------------------|

| Connector type             | 2 x 4 pin header, 2.54 mm pitch (female) on front panel |

| Number of outputs          | 4                                                       |

| Output voltage control     |                                                         |

| Range                      | –3.0 V to +5.0 V                                        |

| Resolution                 | 10 mV                                                   |

| Control                    | Independent for each output                             |

| ✓ Output voltage accuracy  | ± (3% of  setting  + 120 mV) into High-Z load           |

| Output current             | ±100 mA maximum                                         |

| Output impedance (Typical) | 1 Ω                                                     |

Table 17: Dynamic Jump In connector

| Connector type  15-pin D-sub female connector on rear panel Input signal & pin assignment  8 15 9  Pin Signal and direction 1 GND 2 Jump bit 0, input 3 Jump bit 1, input 4 Jump bit 2, input 5 Jump bit 3, input 6 GND 7 Strobe, input 8 GND 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND 10 Jump bit 7, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND Input levels TTL = 5 V compliant inputs 3.33 V LV CMOS level Input impedance Pull up to 3.3 V by 1 kΩ resistor Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.        | Characteristics               | Description                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------|

| Input signal & pin assignment    Pin   Signal and direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Function                      | Allows fast switching during table jump and subsequence |

| Pin Signal and direction  1 GND  2 Jump bit 0, input  3 Jump bit 1, input  4 Jump bit 2, input  5 Jump bit 3, input  6 GND  7 Strobe, input  8 GND  9 GND  10 Jump bit 4, input  11 Jump bit 5, input  12 Jump bit 6, input  13 Jump bit 6, input  14 GND  15 GND  15 GND  10 Finput  11 Jump bit 5, input  12 Jump bit 7, input  13 Jump bit 7, input  14 GND  15 GND  10 Finput  15 GND  10 Finput  10 Finput  11 Jump bit 8, input  12 Jump bit 9, input  13 Jump bit 17, input  14 GND  15 GND  16 GND  17 Le 5 V compliant inputs  3.33 V LV CMOS level  Input impedance  Pull upt of dynamic jump  256 Maximum sequence indices  The flag that decides whether or not the event input pattern is valid can be set to each of the patterns. | Connector type                | 15-pin D-sub female connector on rear panel             |

| 1 GND 2 Jump bit 0, input 3 Jump bit 1, input 4 Jump bit 2, input 5 Jump bit 3, input 6 GND 7 Strobe, input 8 GND 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 6, input 14 GND 15 GND 16 GND 17 GND 19 GND 10 Jump bit 6, input 11 Jump bit 7, input 12 Jump bit 8, input 13 Jump bit 7, input 14 GND 15 GND 15 GND 16 GND 17 L = 5 V compliant inputs 3.33 V LV CMOS level 18 Input impedance 18 Pull up to 3.3 V by 1 kΩ resistor 19 Valid to a be set to each of the patterns.                                                                                                                                                                                                                            | Input signal & pin assignment | © (0000000) ©<br>15 9                                   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin                           | Signal and direction                                    |

| 3 Jump bit 1, input 4 Jump bit 2, input 5 Jump bit 3, input 6 GND 7 Strobe, input 8 GND 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND 10 TTL = 5 V compliant inputs 3.33 V LV CMOS level Input impedance Pull up to 3.3 V by 1 kΩ resistor Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                                                               | 1                             | GND                                                     |

| 4 Jump bit 2, input 5 Jump bit 3, input 6 GND 7 Strobe, input 8 GND 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND Input levels TTL = 5 V compliant inputs 3.33 V LV CMOS level Input impedance Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                                                                                                           | 2                             | Jump bit 0, input                                       |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                             | Jump bit 1, input                                       |

| 6 GND 7 Strobe, input 8 GND 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND Input levels TTL = 5 V compliant inputs 3.33 V LV CMOS level Input impedance Pull up to 3.3 V by 1 kΩ resistor  Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                                                                                                                | 4                             | Jump bit 2, input                                       |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                             | Jump bit 3, input                                       |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                             | GND                                                     |

| 9 GND 10 Jump bit 4, input 11 Jump bit 5, input 12 Jump bit 6, input 13 Jump bit 7, input 14 GND 15 GND Input levels TTL = 5 V compliant inputs 3.33 V LV CMOS level Input impedance Pull up to 3.3 V by 1 kΩ resistor  Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                                                                                                                                            | 7                             | Strobe, input                                           |

| 10       Jump bit 4, input         11       Jump bit 5, input         12       Jump bit 6, input         13       Jump bit 7, input         14       GND         15       GND         Input levels       TTL = 5 V compliant inputs         3.33 V LV CMOS level         Input impedance       Pull up to 3.3 V by 1 kΩ resistor         Number of dynamic jump destinations       256 Maximum sequence indices         The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                | 8                             | GND                                                     |

| 11       Jump bit 5, input         12       Jump bit 6, input         13       Jump bit 7, input         14       GND         15       GND         Input levels       TTL = 5 V compliant inputs         3.33 V LV CMOS level         Input impedance       Pull up to 3.3 V by 1 kΩ resistor         Number of dynamic jump destinations       256 Maximum sequence indices         The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                   | 9                             | GND                                                     |

| 12 Jump bit 6, input  13 Jump bit 7, input  14 GND  15 GND  Input levels TTL = 5 V compliant inputs 3.33 V LV CMOS level  Input impedance Pull up to 3.3 V by 1 kΩ resistor  Number of dynamic jump destinations The flag that decides whether or not the event input pattern is valid can be set to each of the patterns.                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                            | Jump bit 4, input                                       |