# TLA6000 Series Logic Analyzer Product Specifications & Performance Verification

**Technical Reference**

#### **Revision A**

This document applies to TLA System Software Version 5.7 and above

#### Warning

These servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries before performing service.

www.tektronix.com

077-0484-00

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are protected by national copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

MagniVu and iView are registered trademarks of Tektronix, Inc.

#### **Contacting Tektronix**

Tektronix, Inc. 14150 SW Karl Braun Drive P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- = In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

# **Table of Contents**

| General safety summary              | iii |

|-------------------------------------|-----|

| Service safety summary              | v   |

| Preface                             | vii |

| Related Documentation               | vii |

| Specifications                      | 1   |

| Atmospheric Characteristics         | 2   |

| System Characteristics              | 2   |

| Performance Verification Procedures | 17  |

| Summary Verification                | 17  |

| Test Equipment                      | 18  |

| Functional Verification             | 18  |

| Certification                       | 20  |

| Performance Verification Procedures | 20  |

| Threshold Accuracy Test             | 22  |

| Setup and Hold                      | 25  |

| Test Fixtures                       | 29  |

| Threshold Accuracy Test Fixture     | 29  |

| Setup and Hold Test Fixture         | 30  |

| Calibration Data Report             | 32  |

| TLA6000 Test Record                 | 32  |

| Test Data                           | 32  |

|                                     |     |

# **List of Figures**

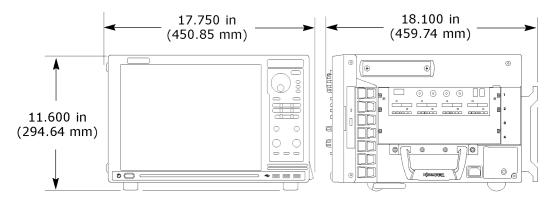

| Figure 1: Dimensions of the TLA6000 series logic analyzer | 15 |

|-----------------------------------------------------------|----|

| Figure 2: Setting trigger parameters                      | 23 |

| Figure 3: Set the trigger states                          | 27 |

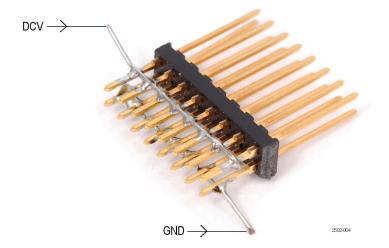

| Figure 4: Threshold Accuracy test fixture                 | 29 |

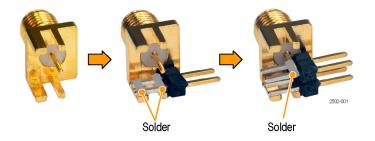

| Figure 5: Solder square pins to the SMA connector         | 30 |

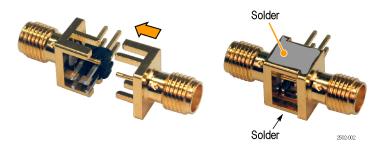

| Figure 6: Solder the SMA connectors together              | 31 |

| Figure 7: Completed fixture with termination and coupler  | 31 |

# **List of Tables**

| Table 1: Atmospheric characteristics                                  | 2  |

|-----------------------------------------------------------------------|----|

| Table 2: Backplane interface                                          | 2  |

| Table 3: System trigger and external signal input latencies (Typical) | 2  |

| Table 4: System trigger and external signal output latencies(Typical) | 3  |

| Table 5: External signal interface                                    | 3  |

| Table 6: Display system                                               | 5  |

| Table 7: Front-panel interface                                        | 5  |

| Table 8: Rear-panel interface.                                        | 6  |

| Table 9: AC power source                                              | 6  |

| Table 10: Transportation and storage                                  | 7  |

| Table 11: Cooling                                                     | 7  |

| Table 12: Input parameters (with probes)                              | 7  |

| Table 13: Analog output                                               | 8  |

| Table 14: Channel width and depth                                     | 8  |

| Table 15: Clocking                                                    | 9  |

| Table 16: Trigger system                                              | 12 |

| Table 17: MagniVu acquisition                                         | 14 |

| Table 18: Data placement                                              | 14 |

| Table 19: NVRAM                                                       | 14 |

| Table 20: Mechanical                                                  | 15 |

| Table 21: Test equipment                                              | 18 |

| Table 22: Parameters checked by verification procedures               | 20 |

# **General safety summary**

|                                     | Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it.                                                                                                                                                                                         |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | To avoid potential hazards, use this product only as specified.                                                                                                                                                                                                                                                     |

|                                     | Only qualified personnel should perform service procedures.                                                                                                                                                                                                                                                         |

|                                     | While using this product, you may need to access other parts of a larger system.<br>Read the safety sections of the other component manuals for warnings and<br>cautions related to operating the system.                                                                                                           |

| To avoid fire or personal<br>injury | <b>Use proper power cord.</b> Use only the power cord specified for this product and certified for the country of use.                                                                                                                                                                                              |

|                                     | <b>Connect and disconnect properly.</b> Do not connect or disconnect probes or test leads while they are connected to a voltage source.                                                                                                                                                                             |

|                                     | <b>Ground the product.</b> This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded. |

|                                     | <b>Observe all terminal ratings.</b> To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.                                                                                           |

|                                     | The inputs are not rated for connection to mains or Category II, III, or IV circuits.                                                                                                                                                                                                                               |

|                                     | Connect the probe reference lead to earth ground only.                                                                                                                                                                                                                                                              |

|                                     | <b>Power disconnect.</b> The power cord disconnects the product from the power source. Do not block the power cord; it must remain accessible to the user at all times.                                                                                                                                             |

|                                     | <b>Do not operate without covers.</b> Do not operate this product with covers or panels removed.                                                                                                                                                                                                                    |

|                                     | <b>Do not operate with suspected failures.</b> If you suspect that there is damage to this product, have it inspected by qualified service personnel.                                                                                                                                                               |

|                                     | <b>Avoid exposed circuitry.</b> Do not touch exposed connections and components when power is present.                                                                                                                                                                                                              |

|                                     | Use proper fuse. Use only the fuse type and rating specified for this product.                                                                                                                                                                                                                                      |

|                                     |                                                                                                                                                                                                                                                                                                                     |

|                                     |                                                                                                                                                                                                                                                                                                                     |

Do not operate in wet/damp conditions.

Do not operate in an explosive atmosphere.

Keep product surfaces clean and dry.

Provide proper ventilation. Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

Terms in this manual These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in damage to this product or other property.

#### Symbols and terms on the product

These terms may appear on the product:

- DANGER indicates an injury hazard immediately accessible as you read the marking.

- WARNING indicates an injury hazard not immediately accessible as you read the marking.

- CAUTION indicates a hazard to property including the product.

The following symbol(s) may appear on the product:

OFF (Power)

WARNING High Voltage

Protective Ground (Earth) Terminal

Earth Terminal Chassis Ground

Standb

# Service safety summary

Only qualified personnel should perform service procedures. Read this *Service safety summary* and the *General safety summary* before performing any service procedures.

**Do not service alone.** Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect power.** To avoid electric shock, switch off the instrument power, then disconnect the power cord from the mains power.

**Use care when servicing with power on**. Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

# Preface

This document lists the characteristics and specifications of the TLA6000 series logic analyzers. It also includes the performance verification procedures. Microprocessor-related products and individual logic analyzer probes have their own documentation for characteristics and specifications.

To prevent personal injury or damage consider the following requirements before attempting service:

- The procedures in this manual should be performed only by qualified service personnel.

- Read the General Safety Summary and Service Safety Summary found at the beginning of this manual.

Be sure to follow all warnings, cautions, and notes in this manual.

## **Related Documentation**

The following list and table provide information on the related documentation available for your Tektronix product. For additional information, refer to the Tektronix Web site (www.tektronix.com/manuals).

| Item                                                            | Purpose                                                                                                |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| TLA Quick Start User Manuals                                    | High-level operational overview                                                                        |

| Online Help                                                     | In-depth operation and UI help                                                                         |

| Installation Reference Sheets                                   | High-level installation information                                                                    |

| Installation Manuals                                            | Detailed first-time installation information                                                           |

| XYZs of Logic Analyzers                                         | Logic analyzer basics                                                                                  |

| Declassification and Securities instructions                    | Data security concerns specific to sanitizing<br>or removing memory devices from Tektronix<br>products |

| Application notes                                               | Collection of logic analyzer application specific notes                                                |

| Product Specifications & Performance<br>Verification Procedures | TLA Product specifications and performance verification procedures                                     |

| TPI.NET Documentation                                           | Detailed information for controlling the logic<br>analyzer using .NET                                  |

| Field upgrade kits                                              | Upgrade information for your logic analyzer                                                            |

| Optional Service Manuals                                        | Self-service documentation for modules and mainframes                                                  |

#### Related documentation

### Preface

# **Specifications**

The following tables list the specifications for the TLA6000 series logic analyzers. All specifications are guaranteed unless noted *Typical*. Typical characteristics describe typical or average performance and provide useful reference information.

Specifications that are marked with the  $\nvdash$  symbol are checked directly (or indirectly) in the *Performance Verification* chapter of this document.

The performance limits in this specification are valid with these conditions:

- The instrument must be in an environment with temperature, altitude, humidity, and vibration within the operating limits described in these specifications.

- The instrument must have had a warm-up period of at least 30 minutes.

- The instrument must have been calibrated/adjusted at an ambient temperature between +20 °C and +30 °C.

For optimum performance using an external oscilloscope, please consult the documentation for any external oscilloscopes used with your Tektronix logic analyzer to determine the warm-up period and signal-path compensation requirements.

## **Atmospheric Characteristics**

The following table lists the Atmospheric characteristics of components in the TLA6000 series logic analyzers.

| Characteristic    | Description                                                                                                                                                                                                       |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Temperature       | Operating (no media in CD or DVD drive)<br>+5 °C to +40 °C (+41 °F to +104 °F), 11 °C/hr (52 °F/hr) maximum gradient, noncondensing (derated<br>1 °C (34 °F) per 305 m (1000 ft) above 1524 m (5000 ft) altitude) |  |  |

|                   |                                                                                                                                                                                                                   |  |  |

|                   | Nonoperating (no media in drive)                                                                                                                                                                                  |  |  |

|                   | -20 °C to +60 °C (-4 °F to +104 °F), 15 °C/hr (59 °F/hr) maximum gradient, noncondensing                                                                                                                          |  |  |

| Relative Humidity | Operating (no media in drive)                                                                                                                                                                                     |  |  |

|                   | 5% to 80% relative humidity, up to +30 °C (+86 °F), 75% from +30 to +40 °C (+86 °F to +104 °F) noncondensing. Maximum wet bulb temperature: +29.4 °C (+85 °F)                                                     |  |  |

|                   | Nonoperating (no media in drive)                                                                                                                                                                                  |  |  |

|                   | 5% to 90% relative humidity, noncondensing. Maximum wet bulb temperature: +40 °C (+104 °F)                                                                                                                        |  |  |

| Altitude          | Operating                                                                                                                                                                                                         |  |  |

|                   | To 3000 m (9843 ft), (derated 1 °C (34 °F) per 305 m (1000 ft) above 1524 m (5000 ft) altitude.                                                                                                                   |  |  |

|                   | Nonoperating                                                                                                                                                                                                      |  |  |

|                   | 12,190 m (40,000 ft )                                                                                                                                                                                             |  |  |

#### Table 1: Atmospheric characteristics

## **System Characteristics**

#### Table 2: Backplane interface

| Characteristic                   | Description     |

|----------------------------------|-----------------|

| Clock10 Frequency (system clock) | 10 MHz ±100 ppm |

#### Table 3: System trigger and external signal input latencies (Typical)

| Logic analyzer source characteristic                                           | Description   |  |

|--------------------------------------------------------------------------------|---------------|--|

| External system trigger input to LA probe tip <sup>1</sup>                     | –626 ns       |  |

| External Signal In to LA probe tip via Signals 3, 4 (TTLTRG 0,1) <sup>2</sup>  | –535 ns + Clk |  |

| External Signal In to LA probe tip via Signals 1, 2 (ECLTRG 0,1) <sup>23</sup> | –627 ns + Clk |  |

In the Waveform window, triggers are always marked immediately except when delayed to the first sample. In the Listing window, triggers are always marked on the next sample period following their occurrence.

<sup>2</sup> Clk represents the time to the next master clock at the destination logic analyzer module. With asynchronous clocking this represents the delta time to the next sample clock. With synchronous sampling this represents the time to the next master clock generated by the setup of the clocking state machine and the supplied SUT clocks and qualification data.

3 Signals 1 and 2 (ECLTRG0, 1) are limited to a broadcast mode where only one source can drive the signal node at any one time. The signal source can be used to drive any combination of destinations.

#### Table 4: System trigger and external signal output latencies(Typical)

| Logic analyzer source characteristic <sup>1</sup>                             | Deacripton    |  |  |

|-------------------------------------------------------------------------------|---------------|--|--|

| LA probe tip to external system trigger out (skid) <sup>2</sup>               | 794 ns + Smpl |  |  |

| LA probe tip to External Signal Out via Signal 3, 4 (TTLTRG 0,1) <sup>3</sup> |               |  |  |

| OR function                                                                   | 793 ns + Smpl |  |  |

| AND function                                                                  | 803 ns + Smpl |  |  |

| LA probe tip to External Signal Out via Signals 1, 2 (ECLTRG0,1) 34           | 793 ns + Smpl |  |  |

SMPL represents the time from the event to the next valid data sample at the probe tip of the LA module. With asynchronous sampling, this represents the delta time to the next sample clock. With MagniVu asynchronous sampling, this represents 500 ps or less. With synchronous sampling, this represents the time to the next master clock generated by the setup of the clocking state machine, the system-under-test supplied clocks, and the qualification data.

2 Skid is commonly referred to as the system level system trigger and signaling output latency. This is the absolute time from when the event first appears at the input probe tips of a module to when the corresponding event that it generates appears at the system trigger or external signal outputs.

<sup>3</sup> All signal output latencies are validated to the rising edge of an active (true) high output.

4 Signals 1 and 2 (ECLTRG0, 1) are limited to a broadcast mode where only one source can drive the signal node at any one time. The signal source can be used to drive any combination of destinations.

#### Table 5: External signal interface

| Characteristic        |                                | Description                                                                                                                                        |  |  |

|-----------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System Trigger Input  |                                | TTL compatible input via rear panel mounted BNC connectors                                                                                         |  |  |

|                       | Input levels                   | 0 V to 3.0 V                                                                                                                                       |  |  |

|                       | Minimum input voltage<br>swing | 300 mV                                                                                                                                             |  |  |

|                       | Threshold range                | 0.5 V to 1.5 V                                                                                                                                     |  |  |

|                       | Threshold step size            | 50 mV                                                                                                                                              |  |  |

|                       | Input destination              | System trigger                                                                                                                                     |  |  |

|                       | Input Mode                     | Falling edge sensitive, latched (active low)                                                                                                       |  |  |

|                       | Minimum Pulse Width            | 12 ns                                                                                                                                              |  |  |

|                       | Active Period                  | Accepts system triggers during valid acquisition periods via real-time gating, resets system trigger input latch between valid acquisition periods |  |  |

|                       | Maximum Input Voltage          | 0 to + 5 V peak                                                                                                                                    |  |  |

| External Signal Input |                                | TTL compatible input via rear panel mounted BNC connectors                                                                                         |  |  |

|                       | Input Destination              | Signal 1, 2, 3, 4                                                                                                                                  |  |  |

|                       | Input levels                   | 0 V to 3.0 V                                                                                                                                       |  |  |

|                       | Minimum input voltage<br>swing | 300 mV                                                                                                                                             |  |  |

|                       | Threshold range                | 0.5 V to 1.5 V                                                                                                                                     |  |  |

|                       | Threshold step size            | 50 mV                                                                                                                                              |  |  |

|                       | Input Mode                     | Active (true) low, level sensitive                                                                                                                 |  |  |

|                       | Input Bandwidth <sup>1</sup>   | Signal 1, 2 Signal 3, 4                                                                                                                            |  |  |

|                       |                                | 50 MHz square wave minimum 10 MHz square wave minimum                                                                                              |  |  |

|                       | Active Period                  | Accepts signals during valid acquisition periods via real-time gating                                                                              |  |  |

|                       | Maximum Input Voltage          | 0 V to 5 V peak                                                                                                                                    |  |  |

#### Table 5: External signal interface (cont.)

| Characteristic                    |                                               | Description                                                                                                                                  |                                     |  |

|-----------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| System Trigger Output             |                                               | TTL compatible output via rear panel mounted BNC connectors<br>System trigger                                                                |                                     |  |

|                                   | Source selection                              |                                                                                                                                              |                                     |  |

|                                   | Source Mode                                   | Active (true) low, falling edge latched                                                                                                      |                                     |  |

|                                   | Active Period                                 | Outputs system trigger state during valid acquisition period, resets system trigger output to false state between valid acquisitions         |                                     |  |

|                                   | Output Levels V <sub>OH</sub> V <sub>OL</sub> | 50 Ω back terminated TTL-compatible output                                                                                                   |                                     |  |

|                                   |                                               | ≥4 V into open circuit, ≥2 V into 50                                                                                                         | ) $\Omega$ to ground                |  |

|                                   |                                               | ≤0.7 V sinking 10 mA                                                                                                                         |                                     |  |

|                                   | Output Protection                             | Short-circuit protected (to ground)                                                                                                          |                                     |  |

| External Signal Output            |                                               | TTL compatible outputs via rear pa                                                                                                           | nel mounted BNC connectors          |  |

|                                   | Source Selection                              | Signal 1, 2                                                                                                                                  |                                     |  |

|                                   |                                               | Signal 3, 4                                                                                                                                  |                                     |  |

|                                   |                                               | 10 MHz clock                                                                                                                                 |                                     |  |

|                                   | Output Modes                                  | User definable                                                                                                                               |                                     |  |

|                                   | Level Sensitive                               | Active (true) low or active (true) high                                                                                                      |                                     |  |

|                                   | Output Levels V <sub>OH</sub> V <sub>OL</sub> | 50 Ω back terminated TTL output                                                                                                              |                                     |  |

|                                   |                                               | ≥4 V into open circuit, ≥2 V into 50 Ω to ground                                                                                             |                                     |  |

|                                   |                                               | ≤0.7 V sinking 10 mA                                                                                                                         |                                     |  |

|                                   | Output Bandwidth <sup>2</sup>                 | Signal 1, 2                                                                                                                                  | Signal 3, 4                         |  |

|                                   |                                               | 50 MHz square wave minimum                                                                                                                   | 10 MHz square wave minimum          |  |

|                                   | Active Period                                 | Outputs signals during valid acquisition periods, resets signals to false state between valid acquisitions Outputs 10 MHz clock continuously |                                     |  |

|                                   | Output Protection                             | Short-circuit protected (to ground)                                                                                                          |                                     |  |

| Intermodule Signal Line Bandwidth |                                               | Minimum bandwidth up to which th to operate correctly                                                                                        | e intermodule signals are specified |  |

|                                   |                                               | Signal 1, 2                                                                                                                                  | Signal 3, 4                         |  |

|                                   |                                               | 50 MHz square wave minimum                                                                                                                   | 10 MHz square wave minimum          |  |

<sup>1</sup> The Input Bandwidth specification only applies to signals to the modules; it does not apply to signals applied to the External Signal Input and sent back to the External Signal Output.

<sup>2</sup> The Output Bandwidth specification only applies to signals from the modules; it does not apply to signals applied to the External Signal Input and sent back to the External Signal Output.

## Table 6: Display system

| Characteristic         |                                               | Description                                                                                                                                                                                                                                                                                                                     |                                             |                              |  |

|------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|--|

| Display selection      |                                               | The motherboard can                                                                                                                                                                                                                                                                                                             | The motherboard can drive 3 video displays. |                              |  |

|                        |                                               | One VGA and one DVI connector are provided for external monitors.<br>The connectors provide the same video information                                                                                                                                                                                                          |                                             |                              |  |

|                        | This connection is via display. One of the ex | The third display connector is available only as an internal connection.<br>This connection is via LVDS. This port drives the internal 15-inch<br>display. One of the external connectors and the internal connection are<br>connected to the same video information.                                                           |                                             |                              |  |

| External display drive |                                               | One VGA, SVGA, or X<br>& DVI)                                                                                                                                                                                                                                                                                                   | GA-compatible o                             | utput on two connectors (VGA |  |

|                        |                                               | Resolution (Pixels)                                                                                                                                                                                                                                                                                                             | Colors                                      | Refresh Rates                |  |

|                        | Minimum                                       | 800 x 600                                                                                                                                                                                                                                                                                                                       | 16-bit                                      | 60                           |  |

|                        | Maximum                                       | 2048 x 1536                                                                                                                                                                                                                                                                                                                     | 32-bit                                      | 85                           |  |

| Internal display       | Classification                                | Color LCD (NEC TFT NL10276BC30-24D)                                                                                                                                                                                                                                                                                             |                                             |                              |  |

|                        |                                               | Color LCD module NL10276BC30-24D is composed of the amorphous<br>silicon thin film transistor liquid crystal display (a-Si TFT LCD) panel<br>structure with driver LSIs for driving the TFT (Thin Film Transistor)<br>array and a backlight. This LCD display will be driven directly by the<br>motherboard via LVDS signaling. |                                             |                              |  |

|                        | Resolution/Refresh rate and area              | 1024 pixels horizontal by 768 pixels vertical (1024X768) at 60 Hz refresh rate                                                                                                                                                                                                                                                  |                                             |                              |  |

|                        |                                               | Area of 304 mm (11.7 in) by 228 mm (9 in) of viewing area.                                                                                                                                                                                                                                                                      |                                             |                              |  |

|                        | Color scale                                   | 262, 144 colors (6-bit RGB) with a color gamut of 42% at center to NTSC                                                                                                                                                                                                                                                         |                                             |                              |  |

### Table 7: Front-panel interface

| Characteristic Description |                     | Description                                                                        |

|----------------------------|---------------------|------------------------------------------------------------------------------------|

| Keypad                     |                     | 18 buttons allow user to perform the most common tasks required to operate the TLA |

| Special function knobs     | Multi-function Knob | Various increment, decrement functions dependent on screen/window selected.        |

|                            | Vertical position   | Scrolling and positioning dependent on display type.                               |

|                            | Vertical scale      | Scales waveform displays only.                                                     |

|                            | Horizontal position | Scrolling and positioning dependent on display type.                               |

|                            | Horizontal scale    | Scales waveform displays only.                                                     |

| USB Port                   |                     | Three USB 2.0 connectors at lower right of front panel                             |

## Table 8: Rear-panel interface

| Characteristic           |                                 | Description                                                                                                                           |

|--------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| TekLink interface<br>bus |                                 | Connector supports Reference Clock (10 MHz), Power On Signaling, Run event, System Trigger, General purpose events                    |

|                          | Input signal characteristics    | LVDS compatible inputs via rear-panel 40-pin connector                                                                                |

|                          | Output signal characteristics   | LVDS compatible outputs via rear-panel 40-pin connector                                                                               |

|                          | Reference clock characteristics | LVDS compatible inputs via rear-panel 40-pin connector                                                                                |

| SVGA output ports        |                                 | One DVI and one 15-pin D-sub VGA connector                                                                                            |

| External Trigger input   |                                 | Trigger input routed to the system trigger line                                                                                       |

| External Signal input    |                                 | Signal input routed to one of four internal signals                                                                                   |

| System Trigger output    |                                 | Internal system trigger routed as TTL-compatible output                                                                               |

| External Signal output   |                                 | One of four internal signals routed to the signal output connector. The internal 10 MHz reference clock can be routed to this output. |

| USB 2.0 ports            |                                 | Four USB 2.0 connections                                                                                                              |

| GBit LAN port            |                                 | Two RJ-45 LAN ports                                                                                                                   |

| Serial interface port    |                                 | Two 9-pin male D-sub connectors to support RS-232                                                                                     |

| Mouse port               |                                 | PS/2 compatible mouse port                                                                                                            |

| Keyboard port            |                                 | PS/2 compatible keyboard port                                                                                                         |

|                          |                                 |                                                                                                                                       |

### Table 9: AC power source

| Characteristic                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Source voltage and frequency                                                                                                                                                                                                                                                    | 100 V <sub>RMS</sub> to 240 V <sub>RMS</sub> ±10%, 50 Hz to 60 Hz                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                 | 115 V <sub>RMS</sub> ±10%, 400 Hz                                                                                                                                                                                                         |

| Maximum power consumption                                                                                                                                                                                                                                                       | 750 W                                                                                                                                                                                                                                     |

| Steady-state input current                                                                                                                                                                                                                                                      | 6 $A_{RMS}$ maximum at 90 VAC <sub>RMS</sub> , 60 Hz or 100 VAC <sub>RMS</sub> , 400 Hz                                                                                                                                                   |

| Inrush surge current                                                                                                                                                                                                                                                            | 70 A maximum                                                                                                                                                                                                                              |

| Power factor correction                                                                                                                                                                                                                                                         | Yes                                                                                                                                                                                                                                       |

| On/Sleep indicator Green/yellow front panel LED located left of the On/Standby<br>provides visual feedback when the switch is actuated. When<br>green, the instrument is powered and the processor is not sl<br>the LED is yellow, the instrument is powered, but the processor |                                                                                                                                                                                                                                           |

| On/Standby switch and indicator                                                                                                                                                                                                                                                 | Front panel On/Standby switch allows users to turn the instrument on. A soft power down is implemented so that users can turn the instrument off without going through the Windows shutdown process; the instrument powers down normally. |

|                                                                                                                                                                                                                                                                                 | The power cord provides main power disconnect                                                                                                                                                                                             |

### Table 10: Transportation and storage

| Characteristic                  | Description                                                                                                                                                                                                                                               |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transportation package material | Transportation Package material meets recycling criteria as described<br>in Environmental Guidelines for Package Design (Tektronix part number<br>063-1290-00) and Environmentally Responsible Packaging Handbook<br>(Tektronix part number 063-1302-00). |

### Table 11: Cooling

| Characteristic                                                                                                                                                                  | Description                                                                                    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| Cooling system                                                                                                                                                                  | Forced air circulation system with no removable filters using eight fans operating in parallel |  |  |

| Pressurization                                                                                                                                                                  | Negative pressurization system in all chambers including modules                               |  |  |

| Air intake                                                                                                                                                                      | Front sides and bottom                                                                         |  |  |

| Air exhaust                                                                                                                                                                     | Back rear                                                                                      |  |  |

| Cooling clearance 6 inches (152 mm) front, sides, top, and rear. Prevent blocks<br>to bottom of instrument by placing on a solid, noncompressa<br>can be operated on rear feet. |                                                                                                |  |  |

| Fan speed and operation All fans operational at half their rated potential and speed (12                                                                                        |                                                                                                |  |  |

|                                                                                                                                                                                 |                                                                                                |  |  |

### Table 12: Input parameters (with probes)

| Characteristic                                                |                     | Description                                                                                                                                                           |                                      |  |

|---------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| Threshold accuracy                                            |                     | ±(35 mV + 1% of the threshold voltage setting)                                                                                                                        |                                      |  |

| (Certifiable parameter)                                       |                     |                                                                                                                                                                       |                                      |  |

| Threshold range and s                                         | tep size            | Settable from +4.5 V to -2.0 V in                                                                                                                                     | 5 mV steps                           |  |

| Threshold channel selection                                   |                     | 16 threshold groups assigned to channels. Each probe has four threshold settings, one for each of the clock/qualifier channels and one per group of 16 data channels. |                                      |  |

| Channel to channel                                            | el skew             | ≤400 ps maximum                                                                                                                                                       | ≤400 ps maximum                      |  |

| Channel-to-channel sk                                         | ew (Typical)        | ≤300 ps                                                                                                                                                               |                                      |  |

| Sample uncertainty                                            |                     | Asynchronous                                                                                                                                                          | Synchronous                          |  |

|                                                               |                     | Sample period                                                                                                                                                         | 125 ps                               |  |

| Minimum slew rate (Ty                                         | pical)              | 0.2 V/ns                                                                                                                                                              |                                      |  |

| Input voltage range                                           |                     | -2.5 V to +5 V                                                                                                                                                        |                                      |  |

| Maximum operating vo                                          | Itage swing         | 6.0 V peak-to-peak                                                                                                                                                    |                                      |  |

| Probe overdrive Single ended probes                           |                     | ±150 mV or ±25% of signal swin whichever one is greater                                                                                                               | g minimum required beyond threshold, |  |

|                                                               | Differential probes | V <sub>pos</sub> -V <sub>neg</sub> is ≥150 mV <sub>p-p</sub>                                                                                                          |                                      |  |

| Maximum nondestructive input signal to probe                  |                     | ±15V                                                                                                                                                                  |                                      |  |

| Minimum input pulse width (single channel) ( <i>Typical</i> ) |                     | P6860, P6880, P6960, and<br>P6980 probes                                                                                                                              | 500 ps                               |  |

|                                                               |                     | P6810 probes                                                                                                                                                          | 750 ps                               |  |

### Table 12: Input parameters (with probes) (cont.)

| Characteristic                                     | Description                    |              |

|----------------------------------------------------|--------------------------------|--------------|

| Delay time from probe tip to input probe connector | P6860, P6960, and P6980 probes | 7.7 ns ±60ps |

| (Typical)                                          | P6810 and P6880 probes         | 7.7 ns ±80ps |

### Table 13: Analog output

| Characteristic                       | Description                                                                                                             |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Number of outputs                    | Four analog outputs regardless of the channel width. Any four of the channels can be mapped to the four analog outputs. |

| Attenuation                          | 10X mode for normal operation 5X mode for small signals (-1.5 V to +2.5 V)                                              |

| Bandwidth <i>(Typical)</i>           | 2 GHz                                                                                                                   |

| Accuracy (gain and offset) (Typical) | ±(50 mV + 2% of signal amplitude)                                                                                       |

### Table 14: Channel width and depth

| Characteristic              |         | Description                 |  |

|-----------------------------|---------|-----------------------------|--|

| Number of TLA6204           |         | 128 data, 8 clock/qualifier |  |

| channels                    | TLA6203 | 96 data, 6 clock/qualifier  |  |

|                             | TLA6202 | 64 data, 4 clock/qualifier  |  |

| Acquisition<br>memory depth |         | 128 M per channel, maximum  |  |

## Table 15: Clocking

| Characteristic                                               | Description                                                                                                                    |                                                   |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| Asynchronous sampling                                        |                                                                                                                                |                                                   |  |

| Sampling period                                              | 500 ps to 50 ms in a 1-2-5 sequence. Storage control can be used to only store data when it has changed (transitional storage) |                                                   |  |

|                                                              | 2 ns minimum for all o                                                                                                         | channels                                          |  |

|                                                              | 1 ns minimum for half                                                                                                          | channels (using 2:1 Demultiplex mode)             |  |

|                                                              | 0.5 ns minimum for qu                                                                                                          | uarter channels (using 4:1 Demultiplex mode)      |  |

| Minimum recognizable word <sup>1</sup> (across all           | Channel-to-channel s                                                                                                           | kew + sample uncertainty                          |  |

| channels)                                                    | Example for a P6860                                                                                                            | high-density probe and a 2 ns sample period:      |  |

|                                                              | 400 ps + 2 ns = 2.4 n                                                                                                          | S                                                 |  |

| Synchronous sampling                                         |                                                                                                                                |                                                   |  |

| Master clock channels <sup>2</sup>                           | 4                                                                                                                              |                                                   |  |

| Qualifier channels                                           | Product                                                                                                                        | Qualifier channels                                |  |

| Note: Qualifier channels are stored.                         | TLA6202                                                                                                                        | 0                                                 |  |

|                                                              | TLA6203                                                                                                                        | 2                                                 |  |

|                                                              | TLA6204                                                                                                                        | 4                                                 |  |

| Single channel setup and hold window size ( <i>Typical</i> ) | 500 ps                                                                                                                         |                                                   |  |

| Setup and hold window size (data and qualifiers)             | Maximum window siz<br>uncertainty) + 100 ps                                                                                    | e = Maximum channel-to-channel skew + (2 x sample |  |

|                                                              | Maximum setup time = User interface setup time + 75 ps                                                                         |                                                   |  |

|                                                              | Maximum hold time = User interface hold time + 50 ps                                                                           |                                                   |  |

|                                                              | Example using a P6800 series probe and user interface setup and hold of 625/0 typical:                                         |                                                   |  |

|                                                              | Maximum window size = 400 ps + 250 ps + 100 ps = 750 ps                                                                        |                                                   |  |

|                                                              | Maximum setup time = 625 ps + 75 ps = 700 ps                                                                                   |                                                   |  |

|                                                              | Maximum hold time = 0.0 ps + 50 ps = 50 ps                                                                                     |                                                   |  |

## Table 15: Clocking (cont.)

| Characteristic                                                     | Description                                                                            |                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Setup and hold window size (data and qualifiers) ( <i>Typical)</i> | Typical window size = Typical channel-to-channel skew + (2 x sample uncertaint + 75 ps |                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                    | Example using P                                                                        | '6860 probe: 300 ps + 250 ps + 75 ps = 625 ps                                                                                                                                                                                                                                                                                                              |  |

| Setup and hold window range                                        |                                                                                        | el, the setup and hold window can be moved from +8.0 ns ( $T_s$ s ( $T_s$ typical) in 0.125 ns steps (setup time).                                                                                                                                                                                                                                         |  |

|                                                                    | 8 ns. With a 0 ns<br>+12 ns to -4 ns;<br>selection region                              | old window can be shifted toward the setup region by 0 ns, 4 ns, or<br>s shift, the range is +8 ns to -8 ns; with a 4 ns shift, the range is<br>with an 8 ns shift, the range is +16 ns to 0 ns. The sample point<br>is the same setup and hold window. Setup times are specified as<br>old time follows the setup time by the setup and hold window size. |  |

| Demultiplex clocking                                               |                                                                                        |                                                                                                                                                                                                                                                                                                                                                            |  |

| Demultiplex channels (2:1)<br>TLA6203, TLA6204                     | is enabled, all of                                                                     | annel can be demultiplexed with its partner channel. If multiplexing<br>the A and D channels are multiplexed; there is no individual<br>els demultiplex as follows:                                                                                                                                                                                        |  |

|                                                                    | A3(7:0) to/from                                                                        | D3(7:0)                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                    | A2(7:0) to/from                                                                        | D2(7:0)                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                    | A1(7:0) to/from                                                                        | D1(7:0)                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                    | A0(7:0) to/from                                                                        | D0(7:0)                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                    | E3(7:0) to/from                                                                        | E1(7:0) TLA6204 only                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                    | E2(7:0) to/from                                                                        | E0(7:0) TLA6204 only                                                                                                                                                                                                                                                                                                                                       |  |