# Model 4200-SCS Semiconductor Characterization System

# **Applications Manual**

4200-904-01 Rev. E / June 2008

ECA 44845

# Model 4200-SCS

# License Agreement

NOTICE TO USERS: CAREFULLY READ THE FOLLOWING LICENSE AGREEMENT (THE "AGREEMENT"). USE OF THE SOFTWARE (THE "SOFTWARE") PROVIDED WITH THE 4200-SEMICONDUCTOR CHARACTERIZATION SYSTEM (THE "4200-SCS") CONSTITUTES YOUR ACCEPTANCE OF THESE TERMS. IF YOU DO NOT AGREE WITH THE TERMS OF THIS AGREEMENT, PROMPTLY RETURN THE SOFTWARE AND THE ACCOMPANYING ITEMS, INCLUDING ANY WRITTEN MATERIALS AND PACKAGING, TO THE LOCATION WHERE YOU OBTAINED THEM FOR A FULL REFUND.

#### **Grant of License**

Keithley Instruments ("Keithley") grants to you, subject to the terms and conditions of this Agreement, a non-exclusive, non-transferable license to use the portion of the Software developed and owned by Keithley (the "Keithley Software") on the 4200-SCS and to use the manuals and other related materials pertaining to the Software which are necessary or desirable for the implementation, training or use of the Software (the "Documentation") for your own internal business use and not for the benefit of any other person or entity. You may copy the Keithley Software into any machine-readable or printed form only for backup purposes or as necessary to use the Keithley Software or the 4200-SCS in accordance with this Agreement. The Keithley Software and Documentation and any copies or modifications thereof are referred to herein as the "Licensed Product."

## **Ownership**

Keithley and certain third party suppliers (the "Owners") own all right, title and interest in and to the Licensed Product. You acknowledge that all right, title and interest in and to the Licensed Product will remain the exclusive property of the Owners, and you will not acquire any rights in or to the Licensed Product except as expressly set forth in this Agreement. The Licensed Product contains material that is protected by U.S. copyright laws, trade secret laws and international treaty provisions.

#### **Limitations on Use**

You may not make the Software available over the Internet or any similar networking technology. You may not remove any copyright, trademark or other proprietary notices from the Licensed Product or any media relating thereto. You agree that you will not attempt to reverse compile, reverse engineer, modify, translate, adapt or disassemble the Software, nor attempt to create the source code from the object code for the Software, in whole or in part.

#### **Sublicense**

You may sublicense the Keithley Software, subject to the sublicensee's acceptance of the terms and conditions of this Agreement. You may not rent, lease or otherwise transfer the Licensed Product.

#### **Termination**

This Agreement is effective until terminated. Either party shall have the right to terminate this Agreement if the other fails to perform or observe any provision, term, covenant, warranty or condition of this Agreement (a "Default") provided fifteen (15) days notice of termination (the "Notice") is provided to the defaulting party and the defaulting party fails to cure the claimed Default within ten (10) days from the date of receipt of the Notice. Within three (3) days from the date of any termination of this Agreement, each and every embodiment of the Software in any form whatsoever, and all documentation, files and other materials in any form relating thereto, shall be destroyed, and all traces of the Software shall be permanently purged from the 4200-SCS.

#### **Export Restrictions**

You may not export or re-export the Software or any copy or adaptation in violation of any applicable laws or regulations.

#### **U.S. Government Restricted Rights**

Use, duplication and disclosure by the U.S. Government is subject to the restrictions as set forth in FAR §52.227-14 Alternates I, II and III (JUN 1987), FAR §52.227-19 (JUN 1987), and/or FAR §12.211/12.212 (Commercial Technical Data/Computer Software), and DFARS §252.227-7015 (NOV 1995) (Technical Data) and/or DFARS §227.7202 (Computer Software), as applicable.

#### **Limited Warranty**

Keithley does not warrant that operation of the Software will be uninterrupted or error-free or that the Software will be adequate for the customer's intended application or use. Keithley warrants to you that the Keithley Software will substantially perform in accordance with the specifications set forth in this manual for a period of ninety (90) days after your receipt of the Keithley Software (the "Warranty Period"); provided the Keithley Software is used on the products for which it is intended and in accordance with the Documentation. If the Keithley Software is not performing as warranted during the Warranty Period, as determined by Keithley in its sole discretion (a "Nonconformity"), your exclusive remedy under this limited warranty is either a correction of the Keithley Software or an explanation by Keithley of how to use the Keithley Software despite the Nonconformity, at Keithley's option. The foregoing limited warranty shall be null and void upon any modification of the Software, unless approved in writing by Keithley. The portions of the Software not developed and owned by Keithley shall not be covered by this limited warranty, and Keithley shall have no duty or obligation to enforce any third party supplier's warranties on your behalf. The failure to notify Keithley of a Nonconformity during the Warranty Period shall relieve Keithley of its obligations and liabilities under this limited warranty.

EXCEPT FOR THE FOREGOING, THE SOFTWARE IS PROVIDED "AS IS" WITHOUT ANY WARRANTY OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE

THE SOFTWARE IS NOT FAULT TOLERANT AND IS NOT DESIGNED OR INTENDED FOR USE IN HAZARDOUS ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE INCLUDING WITHOUT LIMITATION, IN THE OPERATION OF NUCLEAR

FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION SYSTEMS, AIR TRAFFIC CONTROL, WEAPONS SYSTEMS, DIRECT LIFE-SUPPORT MACHINES, OR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE SOFTWARE COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PHYSICAL OR PROPERTY DAMAGE (COLLECTIVELY "HAZARDOUS ACTIVITIES"). KEITHLEY EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS FOR HAZARDOUS ACTIVITIES.

### **Limitation of Liability**

KEITHLEY'S SOLE LIABILİTY OR OBLIGATION UNDER THIS AGREEMENT IS SET FORTH ABOVE IN THE LIMITED WARRANTY SECTION OF THIS AGREEMENT. IN NO EVENT SHALL KEITHLEY BE LIABLE FOR ANY DAMAGES. WITHOUT LIMITING THE FOREGOING, KEITHLEY SHALL NOT BE LIABLE OR ASSUME LIABILITY FOR: (1) ECONOMICAL, INCIDENTAL, CONSEQUENTIAL, INDIRECT, SPECIAL, PUNITIVE OR EXEMPLARY DAMAGES, WHETHER CLAIMED UNDER CONTRACT, TORT OR ANY OTHER LEGAL THEORY, (2) LOSS OF OR DAMAGE TO YOUR DATA OR PROGRAMMING, (3) PENALTIES OR PENALTY CLAUSES OF ANY DESCRIPTION, OR (4) INDEMNIFICATION OF YOU OR OTHERS FOR COSTS, DAMAGES, OR EXPENSES RELATED TO THE GOODS OR SERVICES PROVIDED UNDER THIS LIMITED WARRANTY.

#### Miscellaneous

In the event of invalidity of any provision of this Agreement, the parties agree that such invalidity shall not affect the validity of the remaining portions of this Agreement. This Agreement shall be governed by and construed in accordance with the laws of the state of Ohio, without regard to conflicts of laws provisions thereof. This is the entire agreement between you and Keithley and supersedes any prior agreement or understanding, whether written or oral, relating to the subject matter of this license. Any waiver by either party of any provision of this Agreement shall not constitute or be deemed a subsequent waiver of that or any other provision.

Should you have any questions concerning this Agreement, or if you desire to contact Keithley Instruments for any reason, please call Keithley at 1-800-552-1115, or write at Keithley Instruments, 28775 Aurora Rd., Solon, Ohio, USA 44139.

# **Limited Hardware Warranty**

Keithley warrants to you that the Keithley manufactured portion of the hardware (the "Keithley Hardware") purchased by you will substantially perform in accordance with the specifications set forth in this manual for a period of one (1) year after your receipt of the Keithley Hardware (the "Warranty Period"); provided the Keithley Hardware is used on the products for which it is intended and in accordance with the documentation. This limited warranty shall be null and void upon (1) any modifications of the Keithley Hardware, unless approved in writing by Keithley, (2) any operation of the 4200-Semiconductor Characterization System (the "4200-SCS") with third party software, unless the software is explicitly approved and supported by Keithley, and (3) any operation of the 4200-SCS on an operating system not explicitly approved and supported by Keithley.

If the Keithley Hardware is not performing as warranted during the Warranty Period, as determined in Keithley's sole discretion (a "Nonconformity"), your exclusive remedy under this limited warranty is the repair or replacement of the Keithley Hardware, at Keithley's option. The portions of the hardware not developed and owned by Keithley shall not be covered by this limited hardware warranty, and Keithley shall have no duty or obligation to enforce a third party supplier's warranties on your behalf. The failure to notify Keithley of a Nonconformity during the Warranty Period shall relieve Keithley of its obligations and liabilities under this limited hardware warranty.

EXCEPT FOR THE FOREGOING, THE HARDWARE IS PROVIDED "AS IS" WITHOUT ANY WARRANTY OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

KEITHLEY'S SOLE LIABILITY OR OBLIGATION UNDER THIS LIMITED HARDWARE WARRANTY IS THE REPAIR OR REPLACEMENT OF THE KEITHLEY HARDWARE. IN NO EVENT SHALL KEITHLEY BE LIABLE FOR ANY DAMAGES. WITHOUT LIMITING THE FOREGOING, KEITHLEY SHALL NOT BE LIABLE OR ASSUME LIABILITY FOR: (1) ECONOMICAL, INCIDENTAL, CONSEQUENTIAL, INDIRECT, SPECIAL, PUNITIVE OR EXEMPLARY DAMAGES, WHETHER CLAIMED UNDER CONTRACT, TORT OR ANY OTHER LEGAL THEORY, (2) LOSS OF OR DAMAGE TO YOUR DATA OR PROGRAMMING, (3) PENALTIES OR PENALTY CLAUSES OF ANY DESCRIPTION, OR (4) INDEMNIFICATION OF YOU OR OTHERS FOR COSTS, DAMAGES OR EXPENSES RELATED TO THE GOODS OR SERVICES PROVIDED UNDER THIS LIMITED HARDWARE WARRANTY.

Should you have any questions concerning this Agreement, or if you desire to contact Keithley Instruments for any reason, please call 1-800-552-1115, or write at Keithley Instruments, 28775 Aurora Rd., Solon, Ohio, USA 44139.

A GREATER MEASURE OF CONFIDENCE

Keithley Instruments, Inc.

Corporate Headquarters • 28775 Aurora Road • Cleveland, Ohio 44139 440-248-0400 • Fax: 440-248-6168 • 1-888-KEITHLEY (534-8453) • www.keithley.com

# 4200-SCS Semiconductor Characterization System Applications Manual

©2008, Keithley Instruments, Inc.

All rights reserved.

Any unauthorized reproduction, photocopy, or use the information herein, in whole or in part, without the prior written approval of Keithley Instruments, Inc. is strictly prohibited.

TSP<sup>TM</sup>, TSP-Link<sup>TM</sup>, and TSP-Net<sup>TM</sup> are trademarks of Keithley Instruments, Inc. All Keithley Instruments product names are trademarks or registered trademarks of Keithley Instruments, Inc. Other brand names are trademarks or registered trademarks of their respective holders.

Document Number: 4200-904-01 Rev. E / June 2008

# KEITHLEY

# **Safety Precautions**

The following safety precautions should be observed before using this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation, operation, and maintenance information carefully before using the product. Refer to the user documentation for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product warranty may be impaired.

The types of product users are:

**Responsible body** is the individual or group responsible for the use and maintenance of equipment, for ensuring that the equipment is operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

**Operators** use the product for its intended function. They must be trained in electrical safety procedures and proper use of the instrument. They must be protected from electric shock and contact with hazardous live circuits.

**Maintenance personnel** perform routine procedures on the product to keep it operating properly, for example, setting the line voltage or replacing consumable materials. Maintenance procedures are described in the user documentation. The procedures explicitly state if the operator may perform them. Otherwise, they should be performed only by service personnel.

**Service personnel** are trained to work on live circuits, perform safe installations, and repair products. Only properly trained service personnel may perform installation and service procedures.

Keithley Instruments products are designed for use with electrical signals that are rated Measurement Category I and Measurement Category II, as described in the International Electrotechnical Commission (IEC) Standard IEC 60664. Most measurement, control, and data I/O signals are Measurement Category I and must not be directly connected to mains voltage or to voltage sources with high transient over-voltages. Measurement Category II connections require protection for high transient over-voltages often associated with local AC mains connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise marked or described in the user documentation.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential human contact. Product operators in these circumstances must be trained to protect themselves from the risk of electric shock. If the circuit is capable of operating at or above 1000V, no conductive part of the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance-limited sources. NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, ensure that the line cord is connected to a properly-grounded power receptacle. Inspect the connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input power disconnect device must be provided in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its specifications and operating instructions, or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with the same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a lid interlock.

If a  $\stackrel{\triangle}{=}$  screw is present, connect it to safety earth ground using the wire recommended in the user documentation.

The  $rac{1}{2}$  symbol on an instrument indicates that the user should refer to the operating instructions located in the user documentaion.

The symbol on an instrument shows that it can source or measure 1000V or more, including the combined effect of normal and common mode voltages. Use standard safety precautions to avoid personal contact with these voltages.

The symbol on an instrument shows that the surface may be hot. Avoid personal contact to prevent burns.

The  $\stackrel{1}{m}$  symbol indicates a connection terminal to the equipment frame.

The **WARNING** heading in the user documentation explains dangers that might result in personal injury or death. Always read the associated information very carefully before performing the indicated procedure.

The **CAUTION** heading in the user documentation explains hazards that could damage the instrument. Such damage may invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits - including the power transformer, test leads, and input jacks - must be purchased from Keithley Instruments. Standard fuses with applicable national safety approvals may be used if the rating and type are the same. Other components that are not safety-related may be purchased from other suppliers as long as they are equivalent to the original component (note that selected parts should be purchased only through Keithley Instruments to maintain accuracy and functionality of the product). If you are unsure about the applicability of a replacement component, call a Keithley Instruments office for information.

To clean an instrument, use a damp cloth or mild, water-based cleaner. Clean the exterior of the instrument only. Do not apply cleaner directly to the instrument or allow liquids to enter or spill on the instrument. Products that consist of a circuit board with no case or chassis (e.g., a data acquisition board for installation into a computer) should never require cleaning if handled according to instructions. If the board becomes contaminated and operation is affected, the board should be returned to the factory for proper cleaning/servicing.

# **Table of Contents**

| 1 | Graphical Data Analysis and Basic Test Sequencing |      |

|---|---------------------------------------------------|------|

|   | SubVt slope                                       | 1-2  |

|   | Open "default" project                            |      |

|   | Open "subvt" test and display graph               |      |

|   | Line-fit analysis                                 |      |

|   | Modify the line-fit                               |      |

|   | Graphical analysis                                |      |

|   | Open "default" project and "vds-id" test          |      |

|   | Display and analyze the "vds-id" graph            |      |

|   | Sequencing tests on a single device               | 1-9  |

|   | Open "default" project                            | 1-9  |

|   | Open "4terminal-n-fet" tests                      | 1-9  |

|   | Modify tests                                      |      |

|   | Change the execution sequence                     | 1-10 |

|   | Run "4terminal-n-fet" test sequence               | 1-11 |

|   | Save and export test data                         | 1-12 |

| 2 | Advanced Applications                             |      |

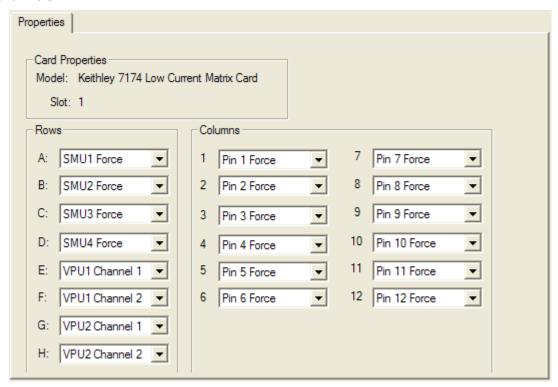

|   | Controlling a switch matrix                       | 2-2  |

|   | KCON setup                                        |      |

|   | Open KITE and the "ivswitch" project              |      |

|   | Running test sequences                            |      |

|   | "connect" test description                        |      |

|   | Sequencing tests on multiple devices              | 2-10 |

|   | Open "ivswitch" project                           |      |

|   | Execute the test sequence (Subsite Plan)          | 2-12 |

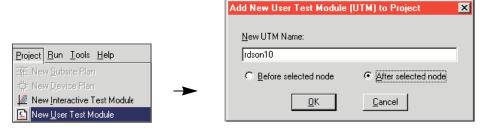

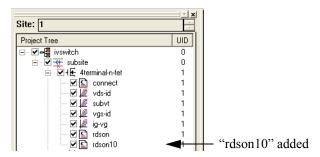

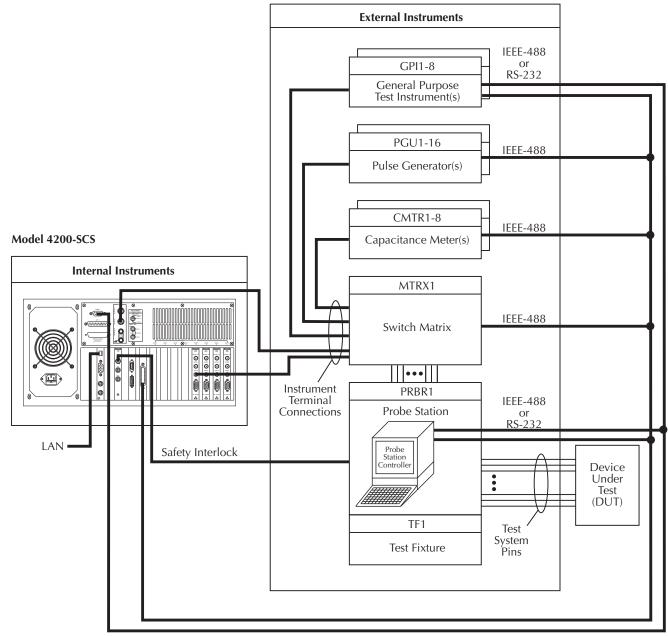

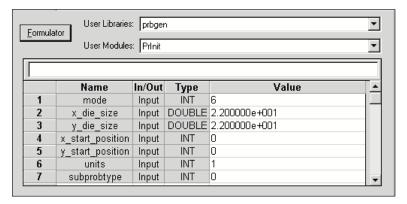

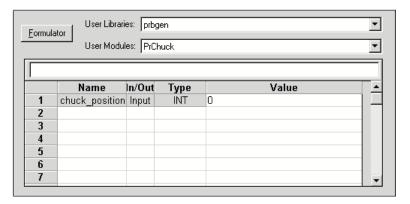

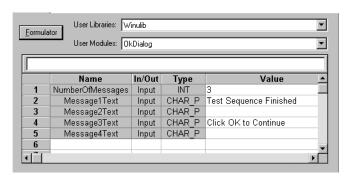

|   | Customizing a user test module (UTM)              | 2-12 |

|   | Open KULT                                         | 2-13 |

|   | Open the "ki42xxulib" user library                | 2-14 |

|   | Open the "Rdson42XX" user module                  | 2-15 |

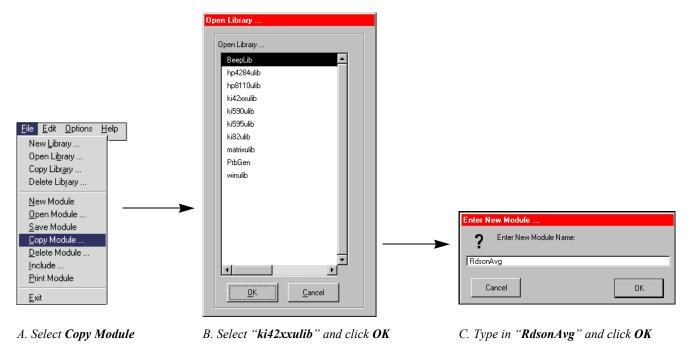

|   | Copy "Rdson42XX" to "RdsonAvg"                    | 2-16 |

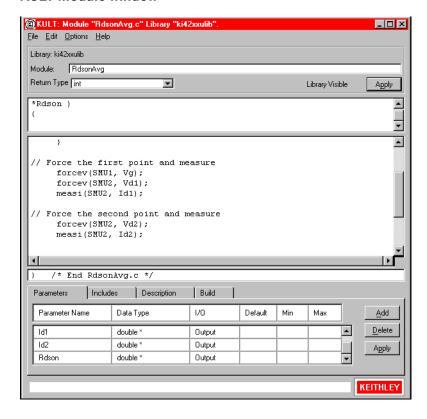

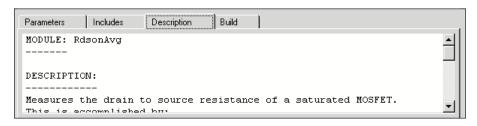

|   | Open and modify the "RdsonAvg" user module        | 2-17 |

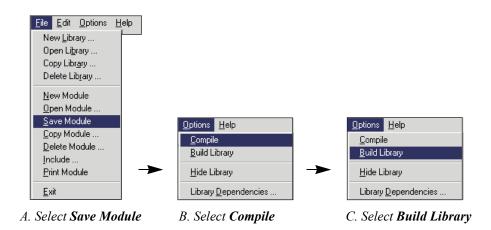

|   | Save, compile, and build the modified library     | 2-19 |

|   | Add a new UTM to the "ivswitch" project           | 2-20 |

|   | Test description                                  | 2-21 |

| 3 | Controlling External Equipment                    |      |

|   | Controlling external equipment overview           | 3-2  |

|   | Controlling a CV Analyzer                         | 3-5  |

|   | Connections                                       |      |

|   | KCON setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-0                                                                                                                 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

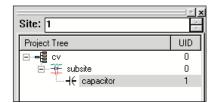

|   | Create a new project                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-7                                                                                                                 |

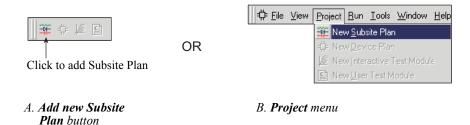

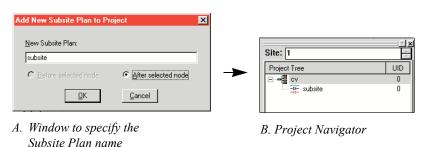

|   | Add a Subsite Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-8                                                                                                                 |

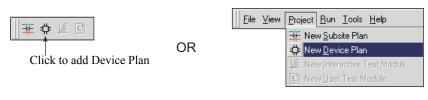

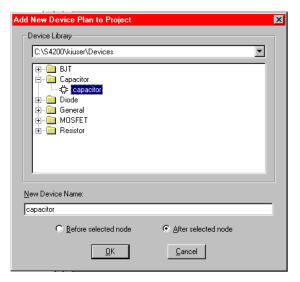

|   | Add a Device Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-8                                                                                                                 |

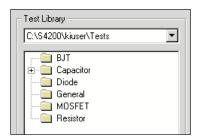

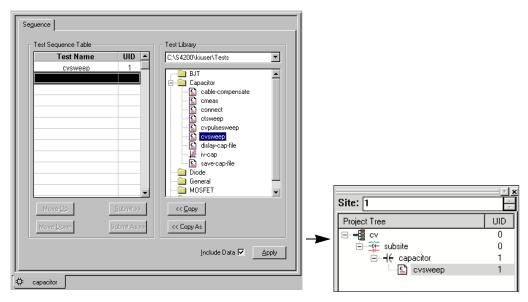

|   | Add a UTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-9                                                                                                                 |

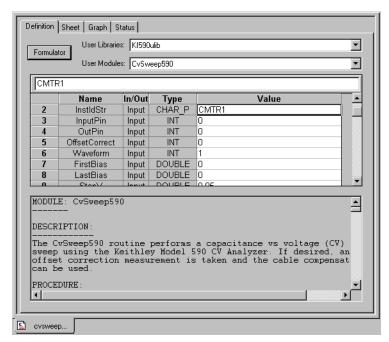

|   | Modifying the "cvsweep" UTM                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

|   | Executing the test                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

|   | Controlling a pulse generator                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|   | Test system connections                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

|   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

|   | KCON setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

|   | Open the "ivpgswitch" project                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

|   | Description of tests                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

|   | Running the test sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|   | Compare the test results                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

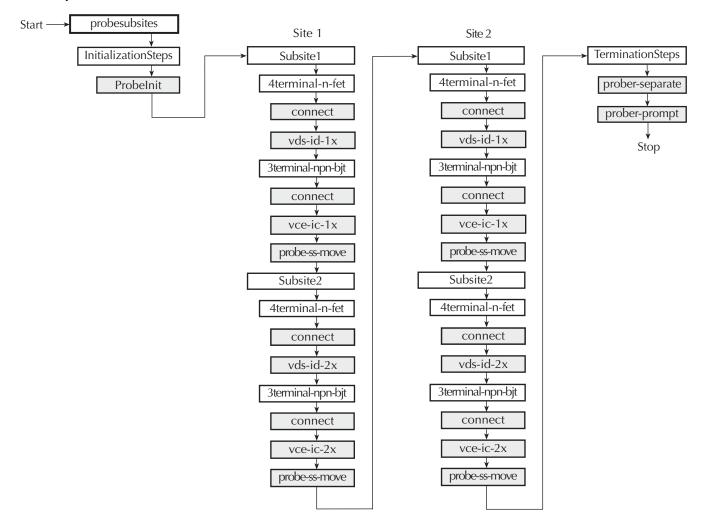

|   | Controlling a probe station                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-21                                                                                                                |

|   | Prober control overview                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-22                                                                                                                |

|   | Test system connections                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-23                                                                                                                |

|   | KCON setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-23                                                                                                                |

|   | Probe station configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

|   | Open the "probesubsites" project                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

|   | Open the project plan window                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

|   | Test descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

|   | Running the test sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|   | Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|   | Running individual plans or tests                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

|   | Running individual plans of tests                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-32                                                                                                                |

| 4 | Pulse Applications Charge Pumping                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-2                                                                                                                 |

|   | CP Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

|   | Of 1.1000 and 5                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

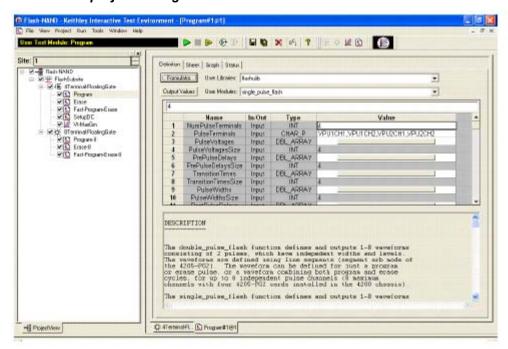

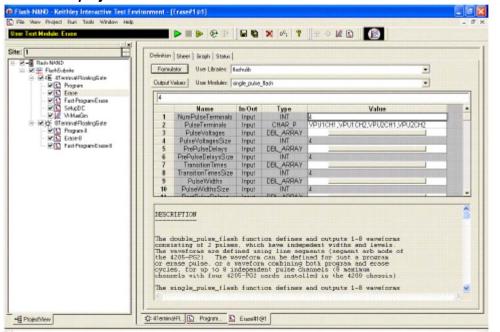

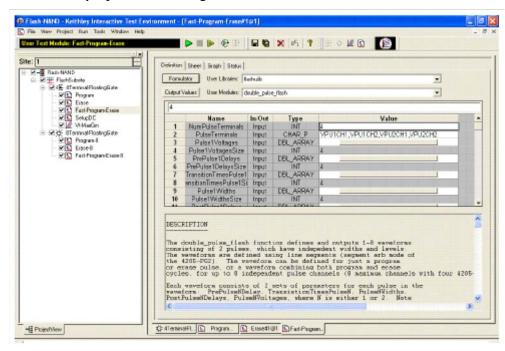

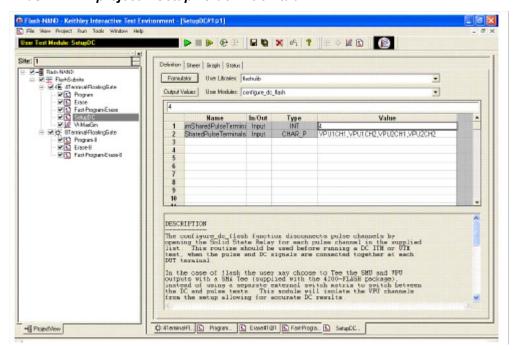

|   | Charge pumping UTM descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-6                                                                                                                 |

|   | Charge pumping UTM descriptionsamplsweep                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-6<br>4-6                                                                                                          |

|   | Charge pumping UTM descriptions amplsweep basesweep                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-6<br>4-6<br>4-8                                                                                                   |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV                                                                                                                                                                                                                                                                                                                                         | 4-6<br>4-8<br>4-9<br>4-10<br>4-12<br>4-13<br>4-15                                                                   |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q)                                                                                                                                                                                                                                                                                                          | 4-6<br>4-8<br>4-9<br>4-10<br>4-13<br>4-15<br>4-15                                                                   |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV                                                                                                                                                                                                                                                                                                                                         | 4-6<br>4-8<br>4-9<br>4-10<br>4-13<br>4-15<br>4-15                                                                   |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections                                                                                                                                                                                                                                               | 4-6<br>4-8<br>4-8<br>4-9<br>4-10<br>4-13<br>4-15<br>4-15<br>4-16<br>4-17                                            |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A                                                                                                                                                                                                                                                                      | 4-6<br>4-8<br>4-8<br>4-9<br>4-10<br>4-13<br>4-15<br>4-15<br>4-16<br>4-17                                            |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections                                                                                                                                                                                                                                               | 4-6<br>4-8<br>4-9<br>4-10<br>4-13<br>4-15<br>4-15<br>4-16<br>4-17<br>4-24                                           |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions                                                                                                                                                               | 4-6<br>4-8<br>4-9<br>4-10<br>4-12<br>4-13<br>4-15<br>4-15<br>4-16<br>4-17<br>4-24<br>4-36                           |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv                                                                                                                                                   | 4-6 4-8 4-9 4-10 4-13 4-15 4-16 4-17 4-24 4-36 4-36                                                                 |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv                                                                                                                                     | 4-6 4-8 4-9 4-10 4-13 4-15 4-16 4-17 4-24 4-36 4-36                                                                 |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv                                                                                                        | 4-6 4-8 4-8 4-9 4-10 4-12 4-15 4-15 4-16 4-17 4-24 4-36 4-37 4-39                                                   |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv                                                                                                        | 4-6 4-8 4-8 4-9 4-10 4-12 4-15 4-15 4-16 4-17 4-24 4-36 4-36 4-37 4-39                                              |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv                                                                                 | 4-6 4-8 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-17 4-24 4-36 4-36 4-37 4-39 4-42 4-43                               |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv                                                                                 | 4-6 4-8 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-17 4-24 4-36 4-36 4-39 4-42 4-43 4-43                               |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv                                                                                 | 4-6 4-8 4-9 4-10 4-13 4-15 4-15 4-16 4-36 4-36 4-37 4-39 4-42 4-43 4-46 4-47                                        |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv  vgsid_pulseiv scopeshot_cal_pulseiv                                            | 4-6 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-36 4-36 4-37 4-39 4-42 4-43 4-44 4-44 4-47 4-49                         |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgsid_pulseiv vgsid_pulseiv scopeshot_cal_pulseiv                                                     | 4-6 4-8 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-17 4-24 4-36 4-36 4-37 4-39 4-42 4-43 4-44 4-43 4-46 4-47 4-49 4-51 |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv  vgsid_pulseiv scopeshot_cal_pulseiv  scopeshot_cal_pulseiv | 4-6 4-8 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-17 4-24 4-36 4-37 4-39 4-42 4-43 4-46 4-47 4-49 4-51                |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgsid_DC_Pulse_pulseiv  vgsid_pulseiv scopeshot_cal_pulseiv  scopeshot_pulseiv vdsid_pulseiv_demo     | 4-6 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-36 4-36 4-37 4-39 4-42 4-43 4-46 4-47 4-49 4-51 4-53                    |

|   | Charge pumping UTM descriptions amplsweep basesweep FallTimeLinearSweep FreqFactorSweep FreqLinearSweep RiseTimeLinearSweep RiseTimeLinearSweep Pulse IV Introduction (PIV-A and PIV-Q) Pulse IV for CMOS: Model 4200-PIV-A PIV-A test connections Using the PulseIV-Complete project for the first time Pulse IV UTM descriptions cal_pulseiv vdsid_pulseiv Vdid_Pulse_DC_Family_pulseiv  Vgid_DC_Pulse_pulseiv  vgsid_pulseiv scopeshot_cal_pulseiv  scopeshot_cal_pulseiv | 4-6 4-8 4-9 4-10 4-12 4-13 4-15 4-15 4-16 4-36 4-36 4-37 4-39 4-42 4-43 4-46 4-47 4-49 4-51 4-53                    |

| Slow single pulse charge trapping high K gate stack               | 4-54  |

|-------------------------------------------------------------------|-------|

| Charge trapping procedure                                         |       |

| Charge Trapping UTM descriptions                                  |       |

| chargetrapping_single_pulse_slow                                  | 4-58  |

| AC stress for WLR                                                 |       |

| Q-Point Pulse IV – Model 4200-PIV-Q                               | 4-64  |

| What is the PIV-Q Package?                                        | 4-64  |

| Target applications and test projects                             | 4-64  |

| PIV-Q Test Procedure                                              | 4-65  |

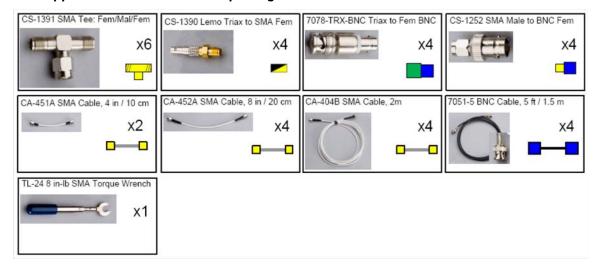

| Interconnect Assembly Procedure                                   | 4-66  |

|                                                                   |       |

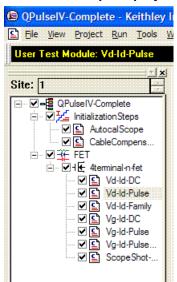

| Using the Model 4200 Project QPulseIV-Complete for the first time | 4-70  |

| Running AutocalScope                                              | 4-71  |

| Running CableCompensation                                         | 4-71  |

| PIV-Q user libraries                                              | 4-77  |

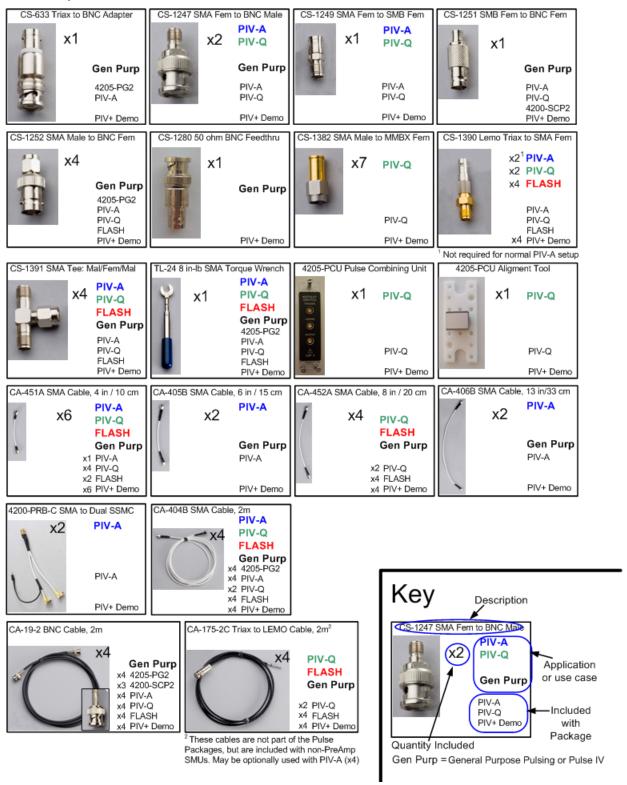

| Pulse adapters, cables, hardware and PCU                          |       |

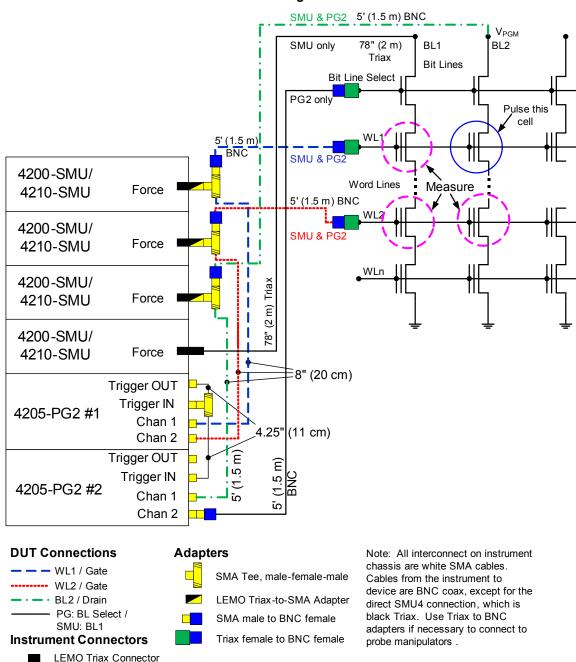

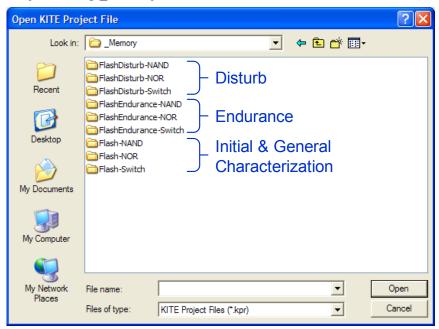

| Flash Memory Testing                                              | 4-119 |

| Introduction                                                      |       |

| Theory of operation                                               | 4-119 |

| FLASH Connections                                                 | 4-132 |

| Flash Projects                                                    |       |

|                                                                   |       |

# **List of Figures**

| 1           | Graphical Data Analysis and Basic Test Sequencing |                  |

|-------------|---------------------------------------------------|------------------|

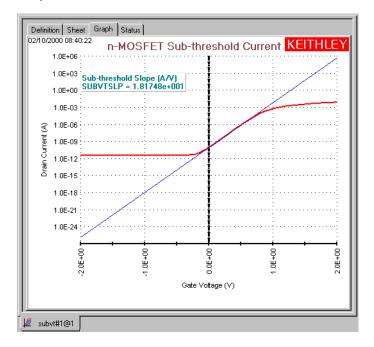

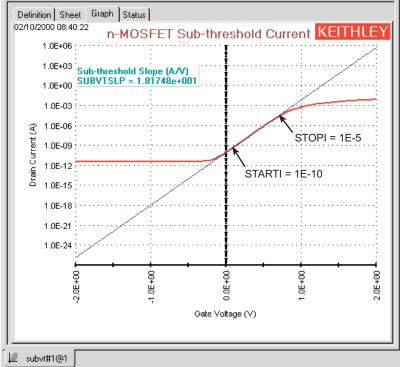

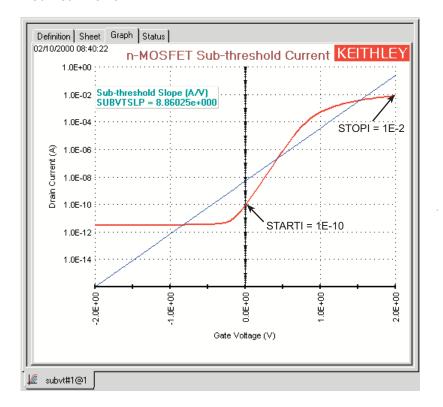

| Figure 1-1  | Graph for the "subvt" test                        | 1-2              |

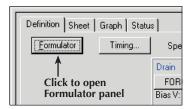

| Figure 1-2  | Open Formulator window                            | 1-3              |

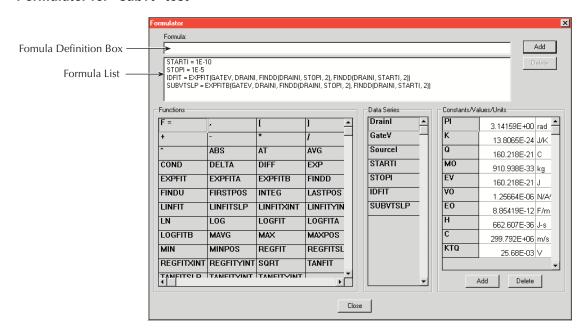

| Figure 1-3  | Formulator for "subvt" test                       | 1-3              |

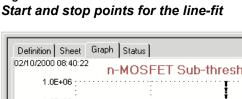

| Figure 1-4  | Start and stop points for the line-fit            |                  |

| Figure 1-5  | Changing the STOPI value                          |                  |

| Figure 1-6  | Modified line fit                                 |                  |

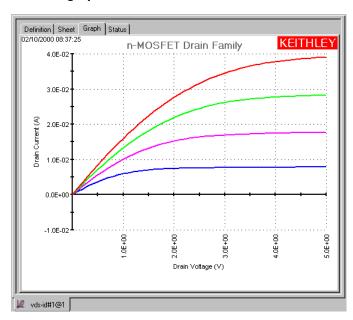

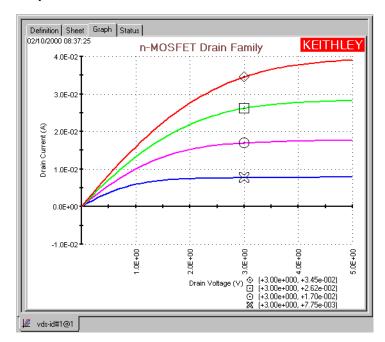

| Figure 1-7  | "vds-id" graph                                    |                  |

| Figure 1-8  | Tools menu access to Graph Settings               |                  |

| Figure 1-9  | Graph Settings                                    |                  |

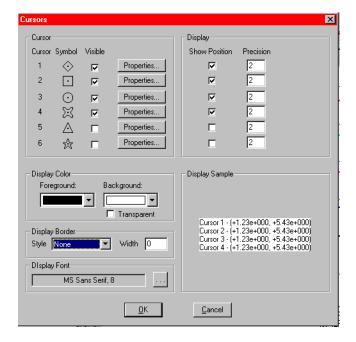

| Figure 1-10 | Cursors window                                    |                  |

| Figure 1-11 | Initial Cursor position                           |                  |

| Figure 1-12 | Graph with Cursors                                |                  |

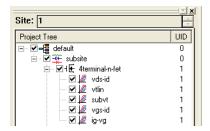

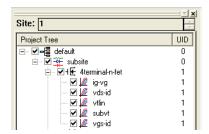

| Figure 1-13 | Project Navigator — "4terminal-n-fet" tests       |                  |

| Figure 1-14 | "4terminal-n-fet" tests opened in Workspace       |                  |

| Figure 1-15 | Device Plan window for "4terminal-n-fet"          |                  |

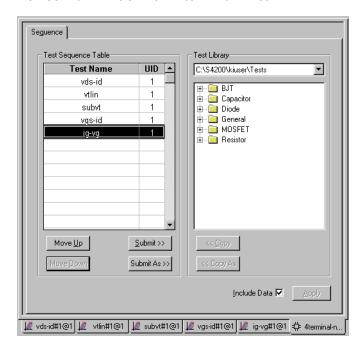

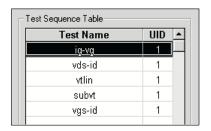

| Figure 1-16 | New order for test sequence table                 |                  |

| Figure 1-17 | Project Navigator — new execution sequence        |                  |

| Figure 1-18 | "4terminal-n-fet" selected to run                 |                  |

| Figure 1-19 | Saving test data                                  |                  |

| 2           | Advanced Applications                             |                  |

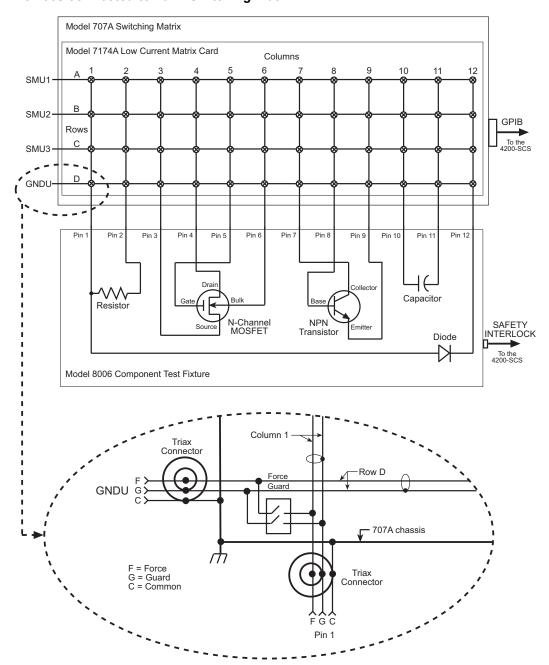

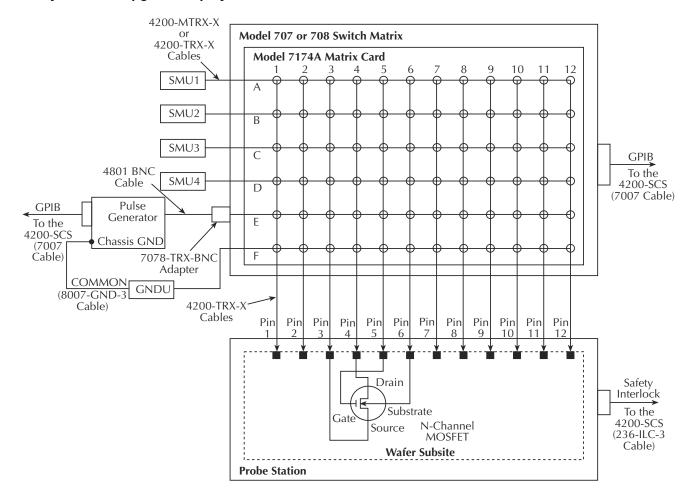

| Figure 2-1  | Devices connected to 707A switching matrix        | 2-3              |

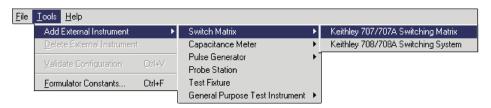

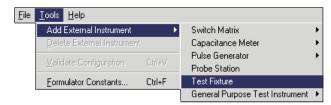

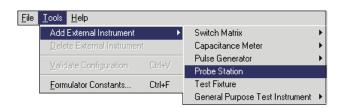

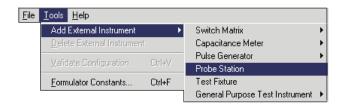

| Figure 2-2  | Add a switch matrix to the system configuration   | 2-4              |

| Figure 2-3  | Add a test fixture to the system configuration    | 2-4              |

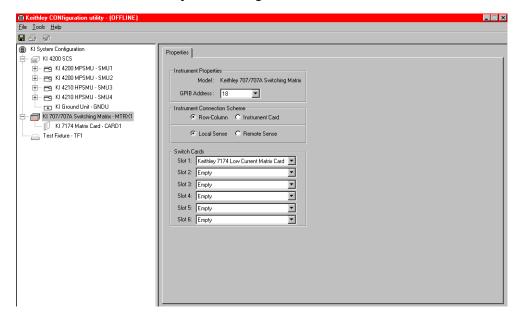

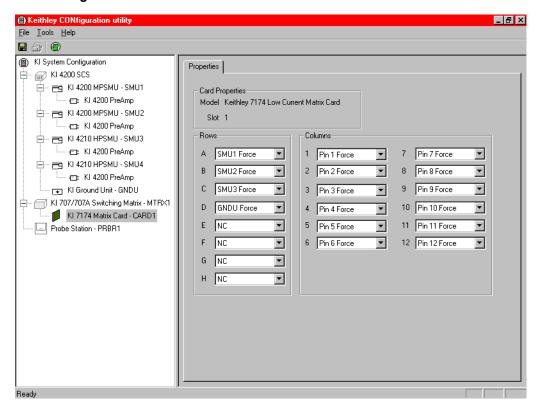

| Figure 2-4  | Add a switch card to the system configuration     | 2-5              |

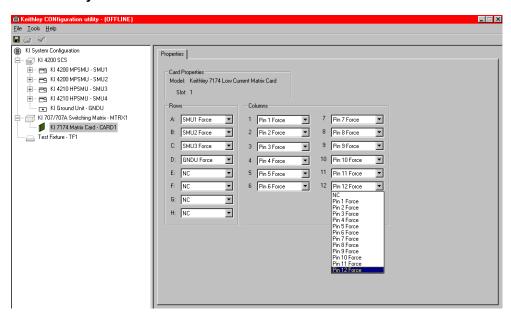

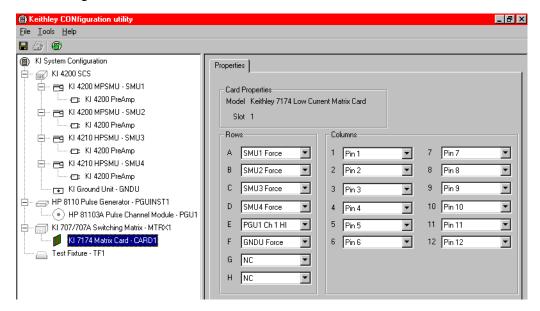

| Figure 2-5  | Define the system connections                     | 2-5              |

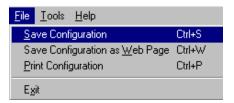

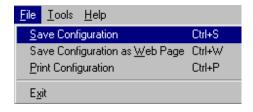

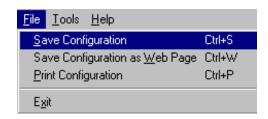

| Figure 2-6  | Save the system configuration                     | 2-6              |

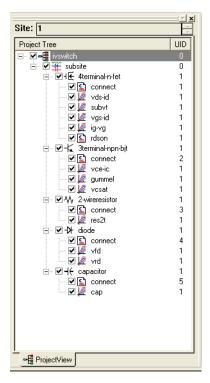

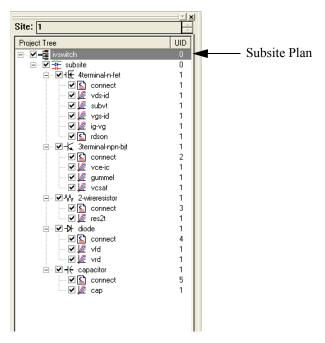

| Figure 2-7  | Project Navigator - "ivswitch" project            | <mark>2-6</mark> |

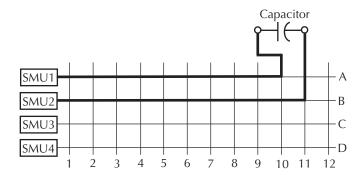

| Figure 2-8  | Signal paths for "4terminal-n-fet" tests          | 2-7              |

| Figure 2-9  | Signal paths for "3terminal-npn-bjt" tests        | 2-7              |

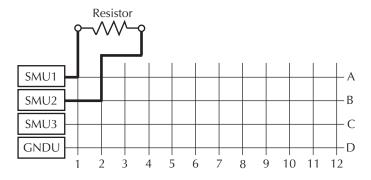

| Figure 2-10 | Signal paths for "2-wireresistor" tests           | 2-8              |

| Figure 2-11 | Signal paths for "diode" tests                    | 2-8              |

| Figure 2-12 | Signal paths for "capacitor" test                 | 2-8              |

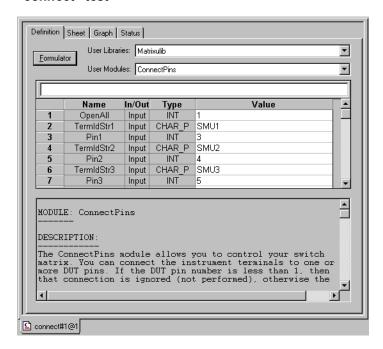

| Figure 2-13 | "connect" test                                    |                  |

| Figure 2-14 | "connect" parameters for "4terminal-n-fet" device | 2-10             |

| Figure 2-15 | Project Navigator - "ivswitch" project            |                  |

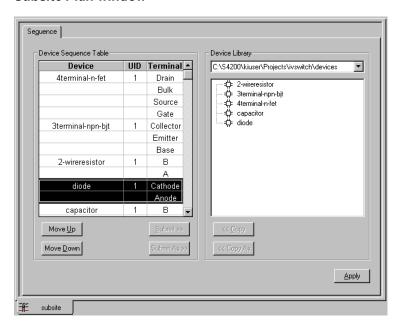

| Figure 2-16 | Subsite Plan window                               | 2-11             |

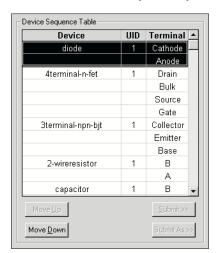

| Figure 2-17 | "diode" moved to top of sequence table            | 2-11             |

| Figure 2-18 | "diode" moved to top of Project Navigator         | 2-12             |

| Figure 2-19 | Execution indicator box                           | 2-12             |

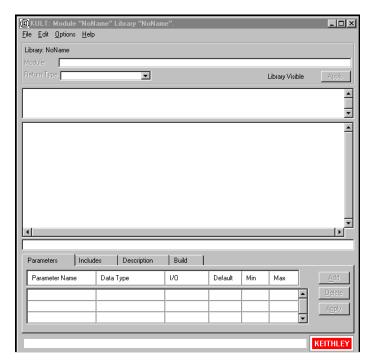

| Figure 2-20 | KULT main window                                                            | 2-13 |

|-------------|-----------------------------------------------------------------------------|------|

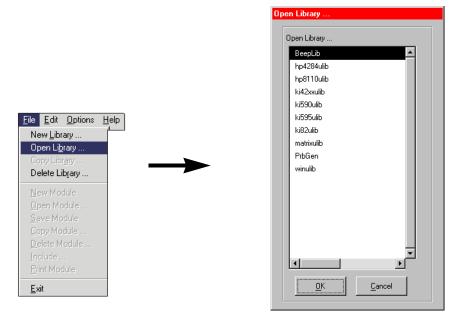

| Figure 2-21 | Open "ki42xxulib" library                                                   |      |

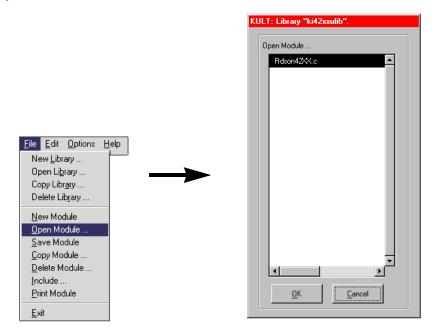

| Figure 2-22 | Open "Rdson42XX" module                                                     |      |

| Figure 2-23 | Copy "Rdson42xx" module as "RdsonAvg"                                       |      |

| Figure 2-24 | KULT module window                                                          |      |

| Figure 2-25 | Program modifications                                                       |      |

| -           |                                                                             |      |

| Figure 2-26 | Module name for Description                                                 |      |

| Figure 2-27 | Save, compile, and build library                                            |      |

| Figure 2-28 | Project Navigator for "ivswitch" project                                    |      |

| Figure 2-29 | Add new UTM                                                                 |      |

| Figure 2-30 | "rdson10" added to Project Navigator                                        |      |

| Figure 2-31 | "rdson10" UTM                                                               | 2-21 |

| 3           | Controlling External Equipment                                              |      |

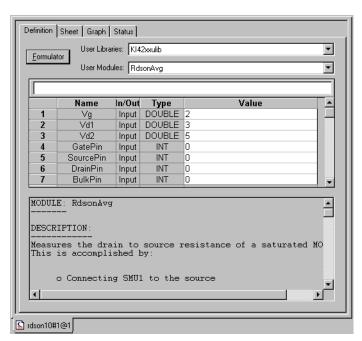

| Figure 3-1  | System configuration with external instruments                              | 3-3  |

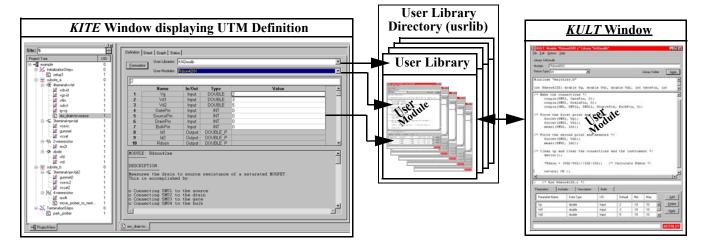

| Figure 3-2  | Relationships between KULT and KITE and between user libraries, user mo 3-4 |      |

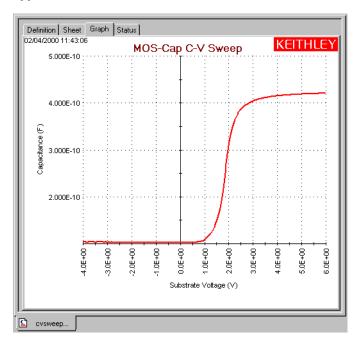

| Figure 3-3  | Typical CV curve                                                            | 3-5  |

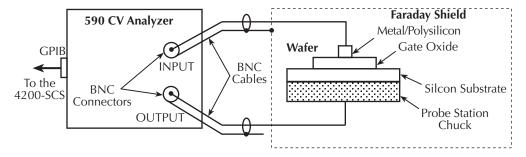

| Figure 3-4  | Keithley Model 590 CV Analyzer DUT connections                              | 3-5  |

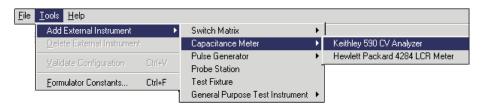

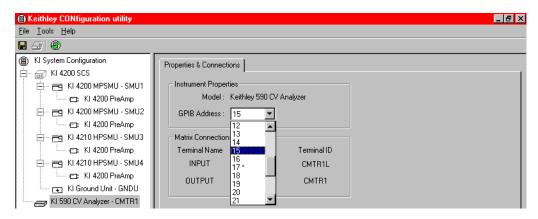

| Figure 3-5  | Adding a Keithley 590 CV Analyzer to the system configuration               | 3-6  |

| Figure 3-6  | Setting the Model 590 GPIB address                                          | 3-6  |

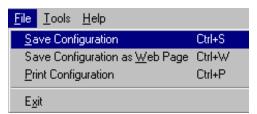

| Figure 3-7  | Saving the system configuration                                             | 3-6  |

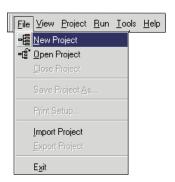

| Figure 3-8  | New Project menu selection                                                  |      |

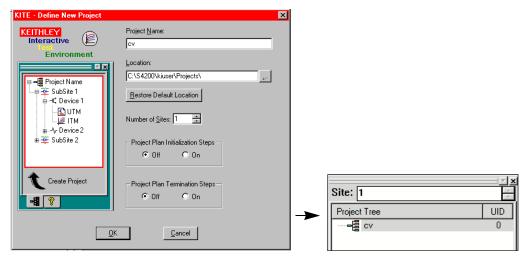

| Figure 3-9  | Define new project                                                          |      |

| Figure 3-10 | Add a new Subsite Plan to a KITE project                                    | 3-8  |

| Figure 3-11 | Add a new Subsite Plan                                                      |      |

| Figure 3-12 | Add a new Device Plan to a KITE project                                     |      |

| Figure 3-13 | Add a Device Plan                                                           |      |

| Figure 3-14 | Default test library folders                                                |      |

| Figure 3-15 | Add the "cvsweep" UTM                                                       |      |

| Figure 3-16 | "cvsweep" UTM                                                               |      |

| Figure 3-17 | Test system for "ivpgswitch" project                                        |      |

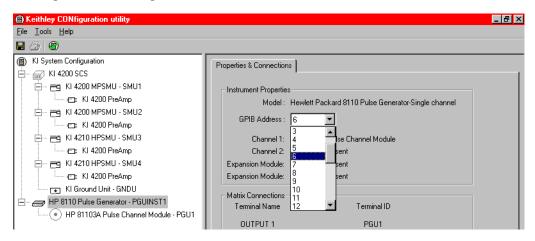

| Figure 3-18 | Adding a pulse generator                                                    |      |

| Figure 3-19 | Pulse generator configuration                                               |      |

| -           |                                                                             |      |

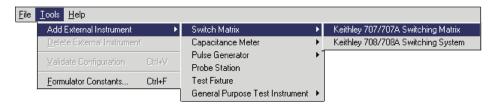

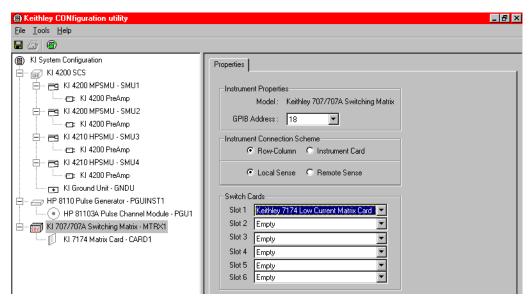

| Figure 3-20 | Adding a switch matrix                                                      |      |

| Figure 3-21 | Configuring the switch matrix                                               |      |

| Figure 3-22 | Adding a probe station                                                      |      |

| Figure 3-23 | Connecting the switch matrix                                                |      |

| Figure 3-24 | Saving the system configuration                                             |      |

| Figure 3-25 | Project Navigator - "ivpgswitch" project                                    |      |

| Figure 3-26 | First "connect" test - connects the device to the SMUs                      |      |

| Figure 3-27 | Signal paths for the pre and post stress tests                              |      |

| Figure 3-28 | Second "connect" test - connects the device to the PGU                      |      |

| Figure 3-29 | Signal paths to apply the pulse stress                                      |      |

| Figure 3-30 | PGU initialization                                                          |      |

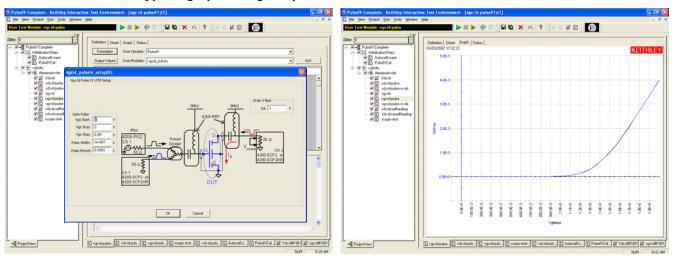

| Figure 3-31 | "pgu1-setup" - configure the PGU channel                                    | 3-18 |

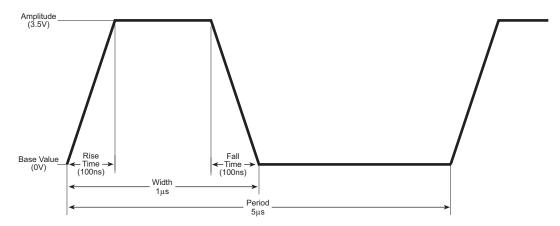

| Figure 3-32 | PGU stress pulse specifications                                             | 3-18 |

| Figure 3-33 | "pgu-trigger" test - trigger the burst of stress pulses                     | 3-18 |

| Figure 3-34 | Buttons to close or reduce size of test documents                           | 3-19 |

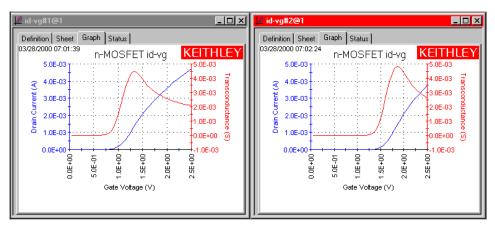

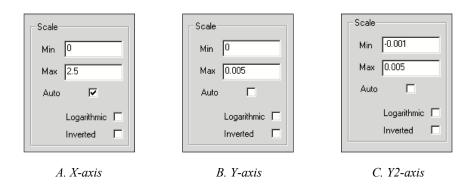

| Figure 3-35 | "id-vg" graphs                                                              | 3-20 |

| Figure 3-36 | Graph scale settings                                                        | 3-20 |

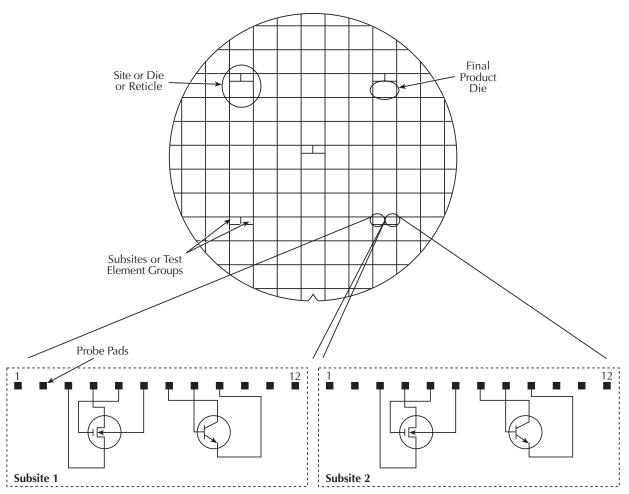

| Figure 3-37 | Sample wafer organization                                                   |      |

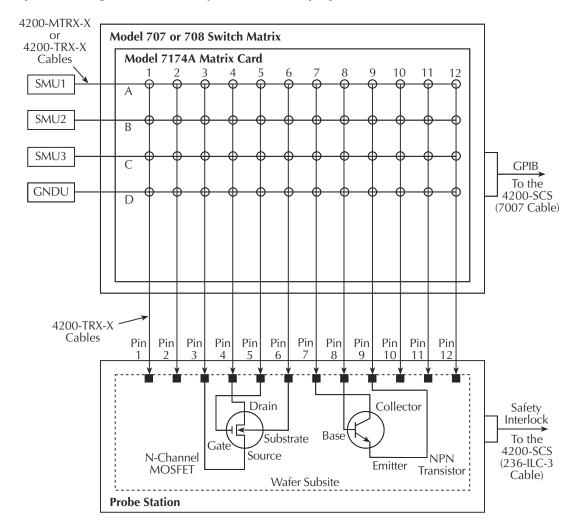

| Figure 3-38 | System configuration for the "probesubsites" project                        |      |

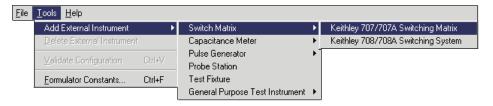

| Figure 3-39 | Adding a switch matrix                                                      |      |

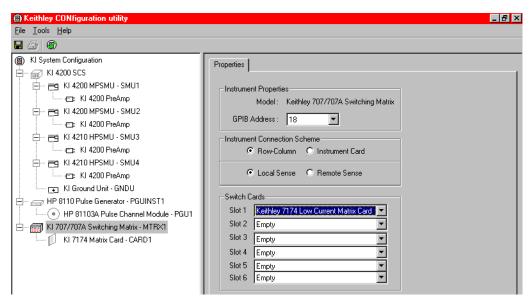

| Figure 3-40 | Configuring the switch matrix                                               |      |

| Figure 3-41 | Adding a probe station                                                              | 3-24 |

|-------------|-------------------------------------------------------------------------------------|------|

| Figure 3-42 | Connecting the switch matrix                                                        | 3-25 |

| Figure 3-43 | Saving the system configuration                                                     |      |

| Figure 3-44 | Project Navigator - probesubsites project                                           |      |

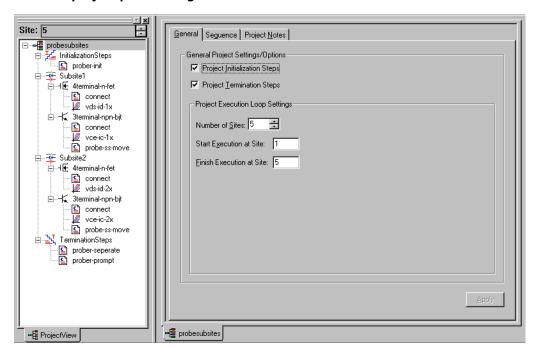

| Figure 3-45 | Modified project plan settings                                                      |      |

| Figure 3-46 | prober-init                                                                         |      |

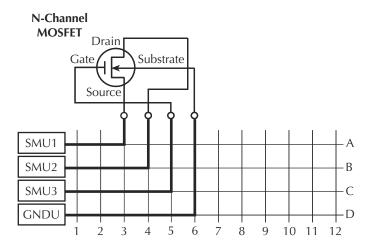

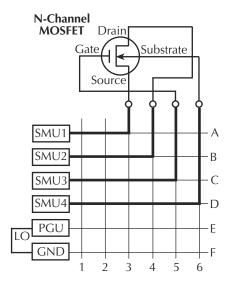

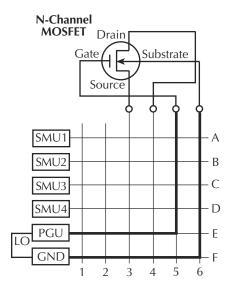

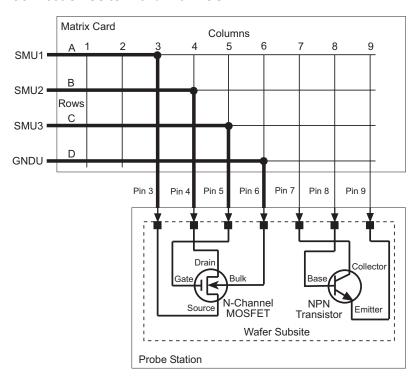

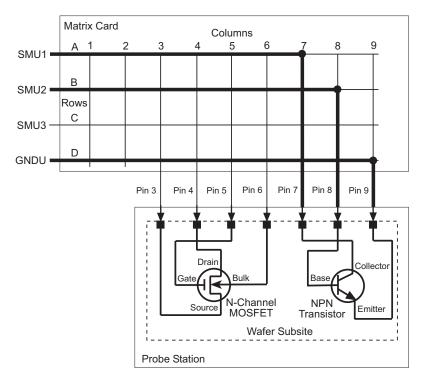

| Figure 3-47 | Connect SMUs to N-channel MOSFET                                                    |      |

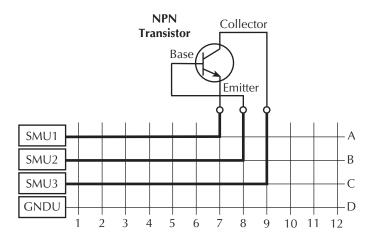

| Figure 3-48 | Connect SMUs to NPN transistor                                                      |      |

| Figure 3-49 | prober-separate                                                                     |      |

| Figure 3-50 | prober-prompt test and dialog window                                                |      |

| Figure 3-51 | Test sequence                                                                       |      |

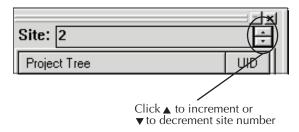

| Figure 3-52 | Site Navigator                                                                      |      |

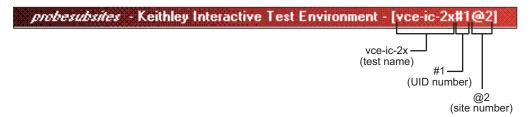

| Figure 3-53 | KITE title bar                                                                      |      |

| 4           | Pulse Applications                                                                  |      |

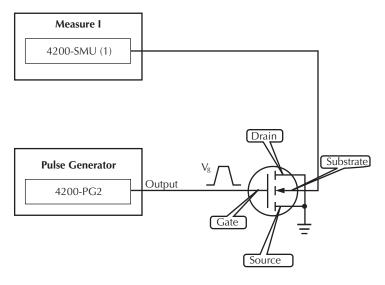

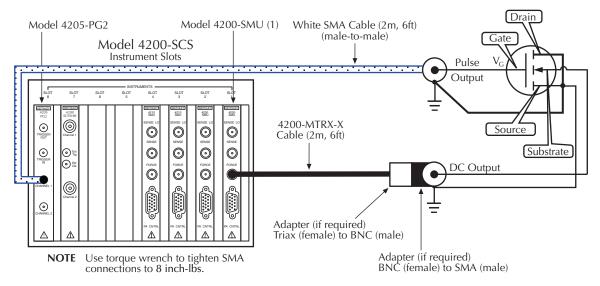

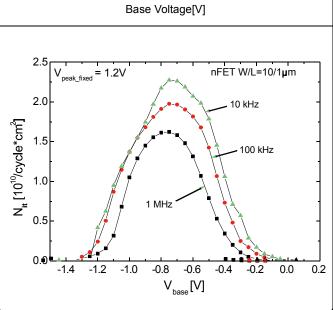

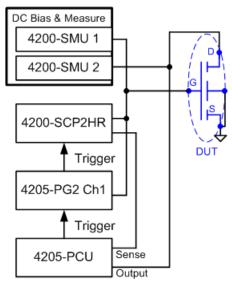

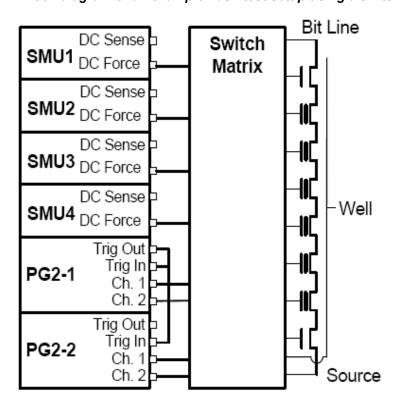

| Figure 4-1  | Charge Pumping—hardware setup block diagram                                         | 12   |

| •           |                                                                                     |      |

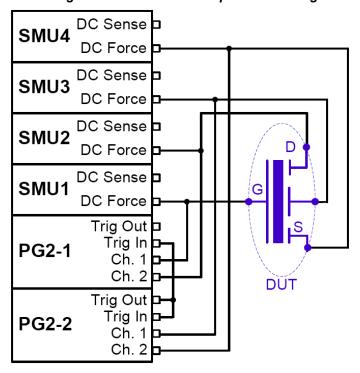

| Figure 4-2  | Charge pumping — hardware connection                                                |      |

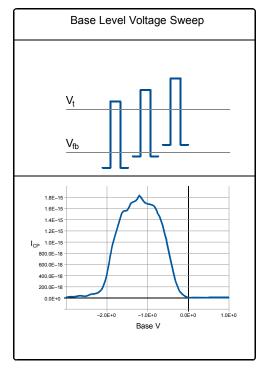

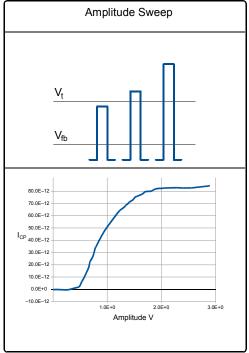

| Figure 4-3  | Two types of sweeps for charge pumping                                              |      |

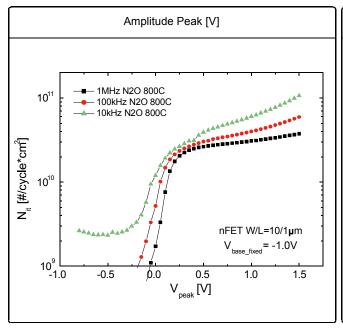

| Figure 4-4  | Example data plots for N <sub>it</sub>                                              | 4-5  |

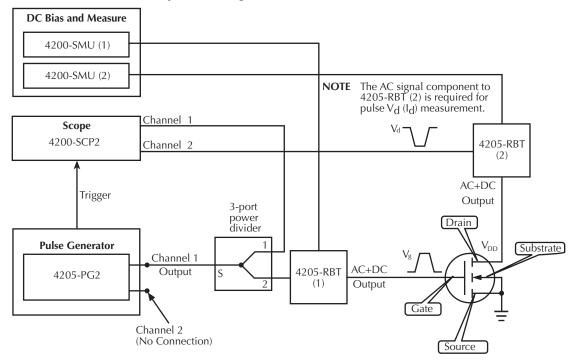

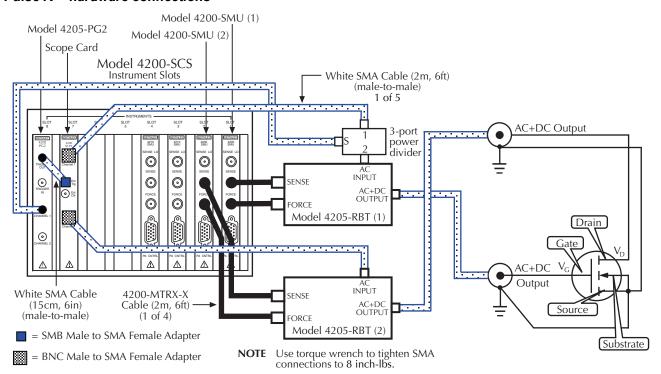

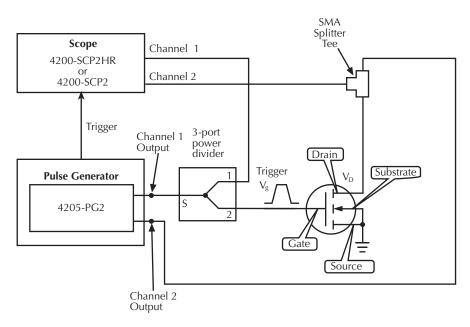

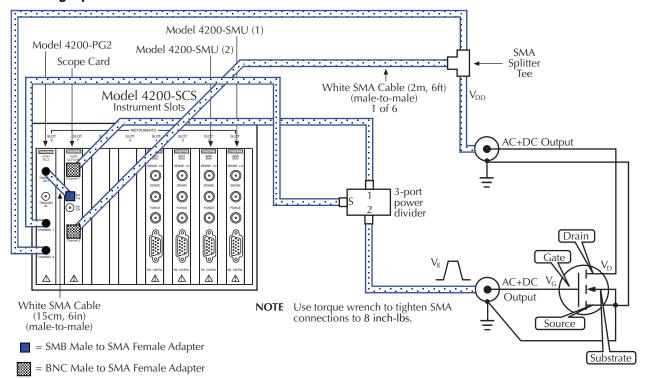

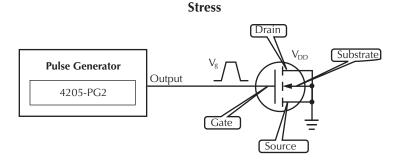

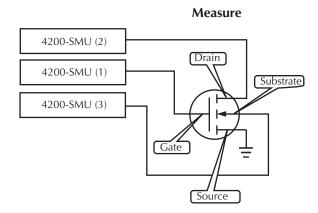

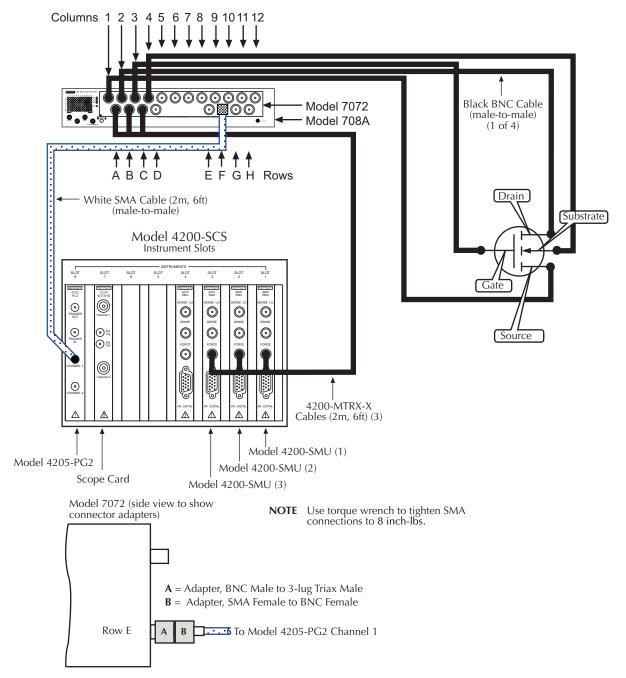

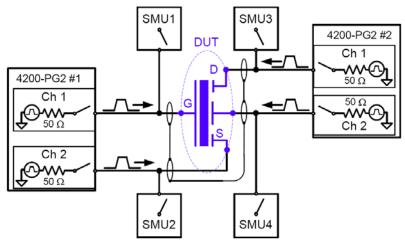

| Figure 4-5  | Pulse IV—hardware setup block diagram                                               |      |

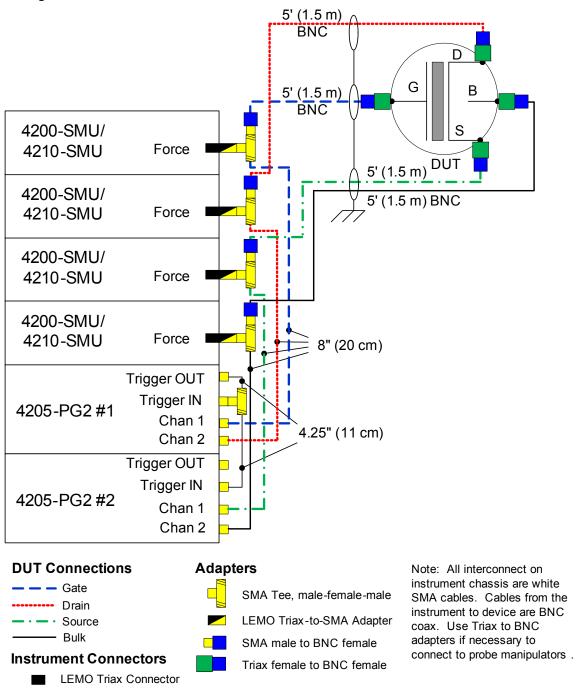

| Figure 4-6  | Pulse IV—hardware connections                                                       |      |

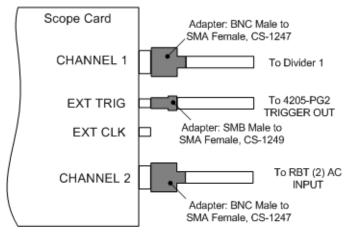

| Figure 4-7  | Side view of scope card connections                                                 | 4-18 |

| Figure 4-8  | Model 8101-PIV test fixture                                                         |      |

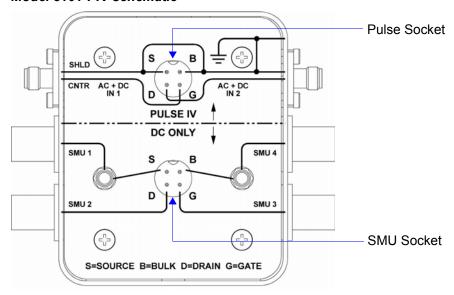

| Figure 4-9  | Model 8101-PIV schematic                                                            |      |

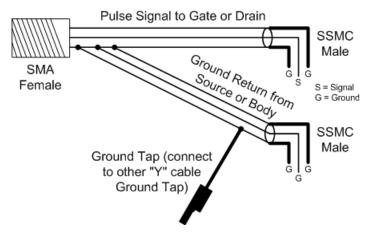

| Figure 4-10 | PRB-C adapter cable – pulse SMA to SSMC Y                                           |      |

| Figure 4-11 | Schematic diagram of the PRB-C adapter cable                                        |      |

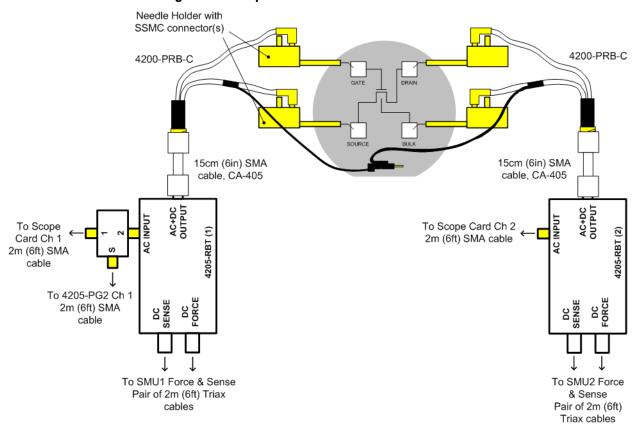

| Figure 4-12 | Pulse IV connections using PRB-C adapter cables                                     |      |

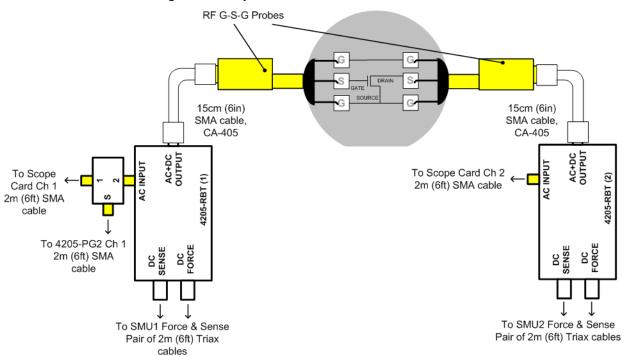

| Figure 4-13 | Pulse IV connections using RF G-S-G probes                                          |      |

| Figure 4-14 | Pulse IV connections using the 8101-PIV test fixture                                |      |

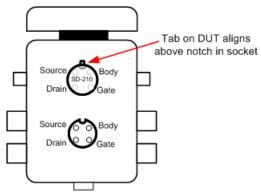

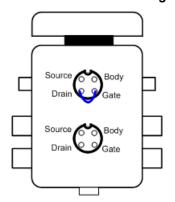

| Figure 4-15 | DUT inserted in pulse socket of 8101-PIV test fixture                               |      |

| Figure 4-16 | Project plan for Pulse-IV Complete                                                  |      |

| Figure 4-17 | PulseIVCal dialog boxes                                                             |      |

| Figure 4-18 | 8101-PIV shorted/through socket                                                     |      |

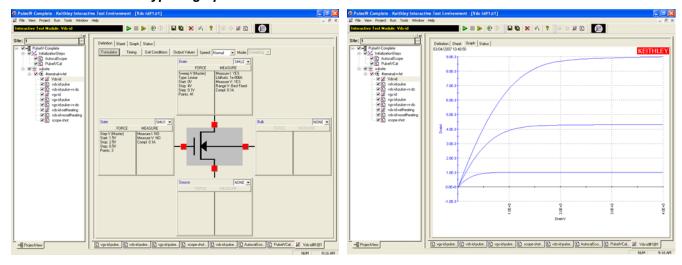

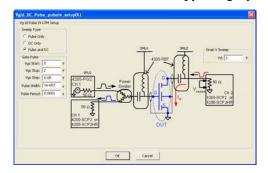

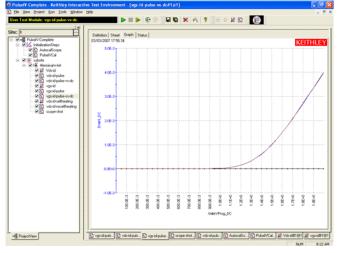

| Figure 4-19 | Default definition and typical graph for Vds-id                                     |      |

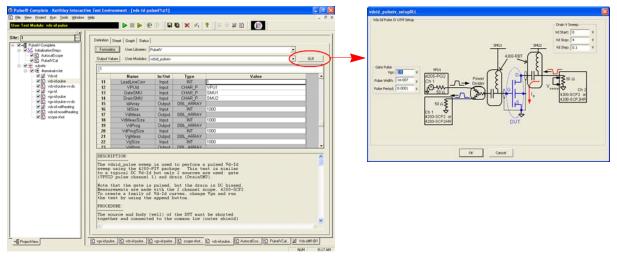

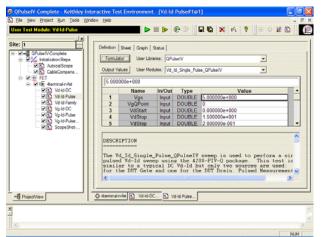

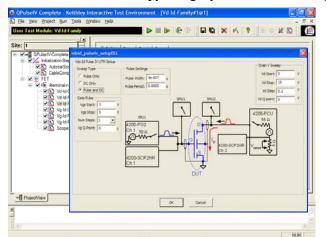

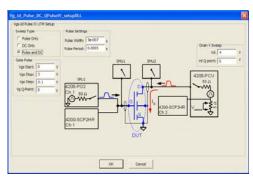

| Figure 4-20 | Default Definition tab and GUI For vds-id-pulse                                     |      |

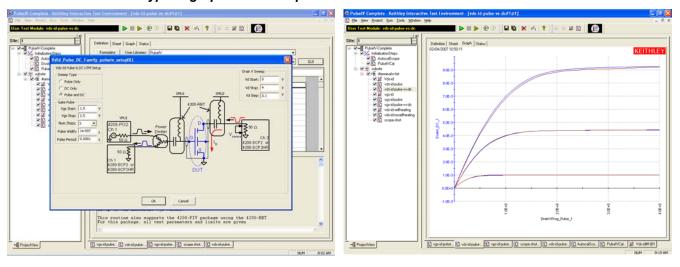

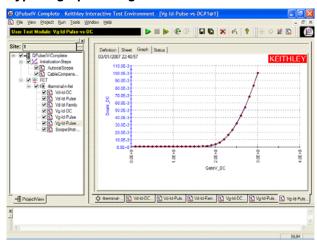

| Figure 4-21 | Default definition and typical graph for vds-id-pulse-vs-dc                         |      |

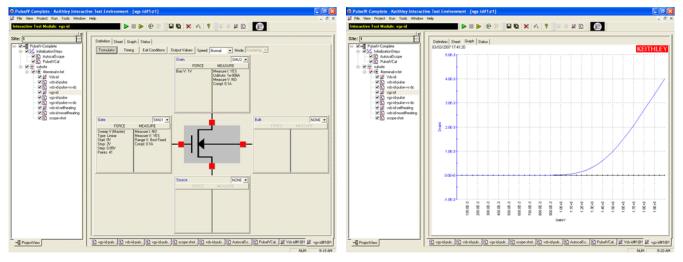

| Figure 4-22 | Default definition and typical graph for vgs-id                                     |      |

| Figure 4-23 | Default definition and typical graph for vgs-id-pulse                               |      |

| Figure 4-24 | Default GUI definition and typical graph for vgs-id-pulse-vs-dc                     |      |

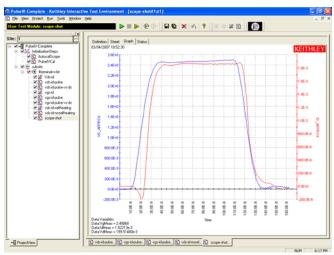

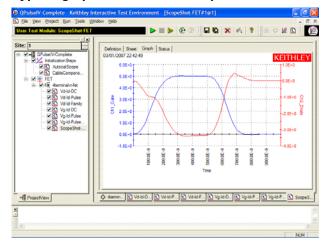

| Figure 4-25 | Typical graphical result for scope-shot                                             |      |

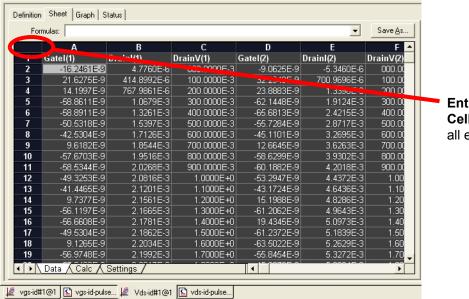

| Figure 4-26 | Highlighting all entries in vds-id data sheet                                       |      |

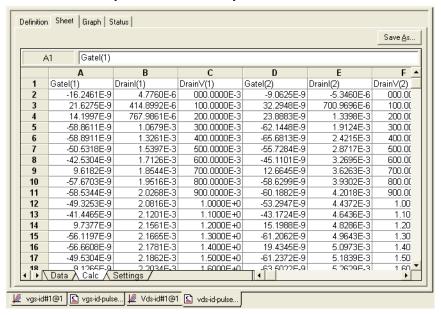

| Figure 4-27 | Data from vds-id pasted into vds-id-pulse calc sheet                                |      |

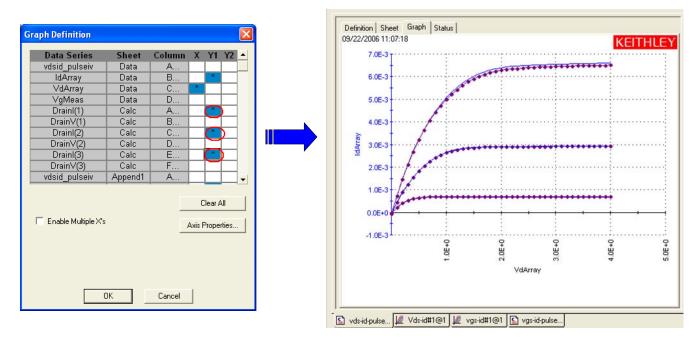

| Figure 4-28 | Graph Definition dialog box and resulting graph that shows the three added curves . |      |

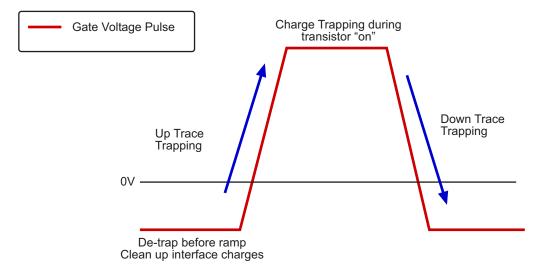

| Figure 4-29 | Trapping and de-trapping in a single gate voltage pulse                             |      |

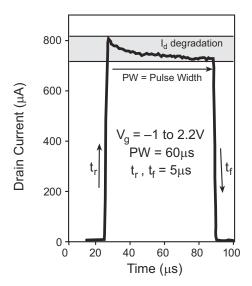

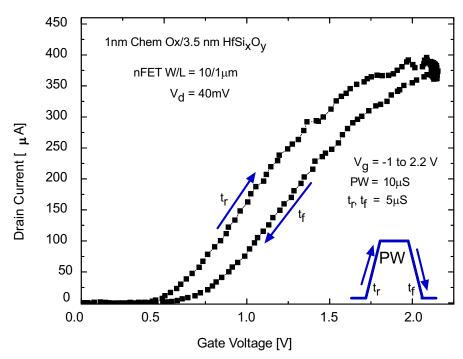

| Figure 4-30 | Slow single pulse—hardware setup block diagram                                      |      |

| Figure 4-31 | Slow single pulse—hardware connection                                               |      |

| Figure 4-32 | Example slow single pulse waveform graph                                            |      |

| Figure 4-33 | Single slow pulse example data plot                                                 |      |

| Figure 4-34 | AC Pulse stress-measure—hardware setup block diagram                                |      |

| Figure 4-35 | AC Pulse stress-measure—hardware matrix card simplified schematic                   |      |

| Figure 4-36 | AC Pulse stress-measure—hardware connections                                        |      |

| Figure 4-37 | PIV-Q Block Diagram                                                                 |      |

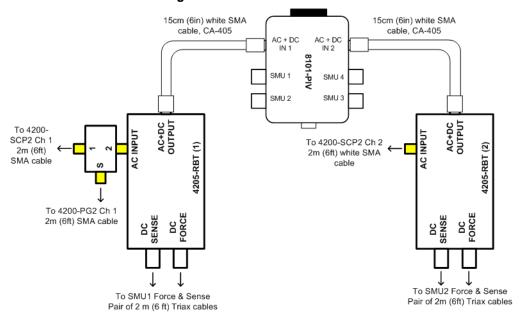

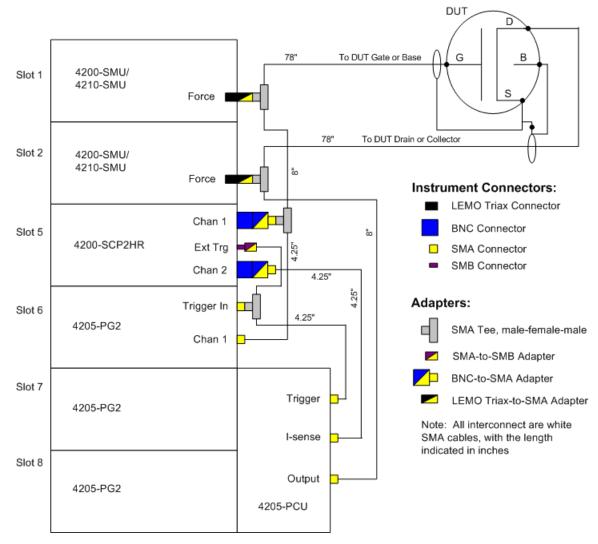

| Figure 4-38 | PIV-Q connections diagram                                                           |      |

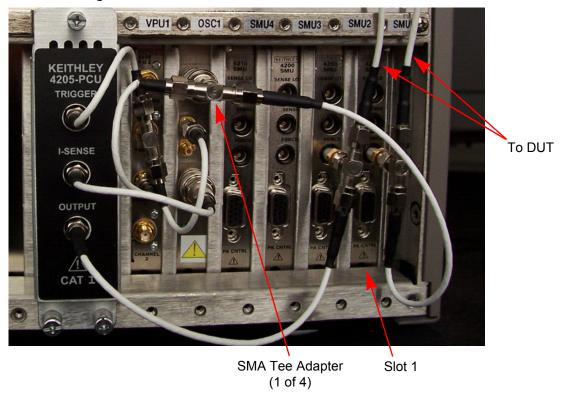

| Figure 4-39 | Photo showing PIV-Q connections                                                     |      |

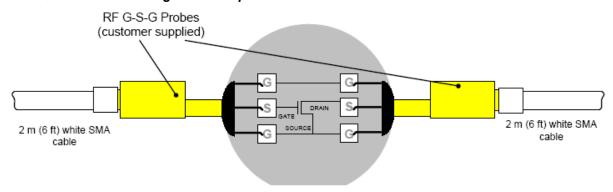

| Figure 4-40 | PIV-O connections using RF G-S-G probes                                             | 4-69 |

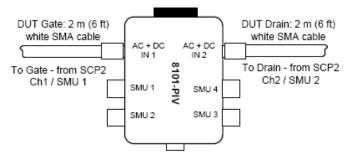

| Figure 4-41                | PIV-Q connections using the 8101-PIV test fixture                                                              | 4-70     |

|----------------------------|----------------------------------------------------------------------------------------------------------------|----------|

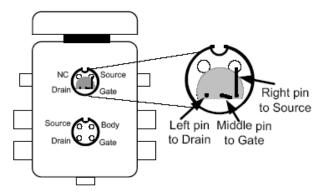

| Figure 4-42                | Proper orientation for the plastic package TO-92 n-channel enhancement mode FET                                |          |

| Figure 4-43                | QPulse-IV-Complete project                                                                                     |          |

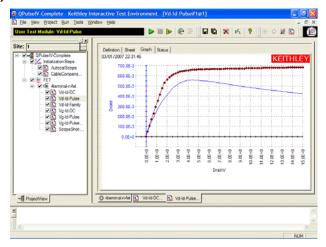

| Figure 4-44                | Definition and Graph tabs for Vd-Id-Pulse (Vgs = 5V)                                                           |          |

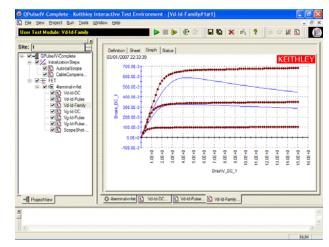

| Figure 4-45                | Default definition and typical graph for Vd-ld-Family                                                          |          |

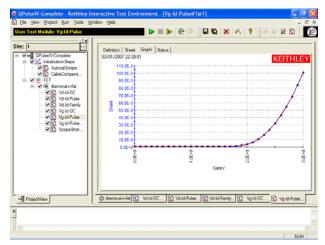

| Figure 4-46                | Vg-Id-Pulse Graph tab                                                                                          |          |

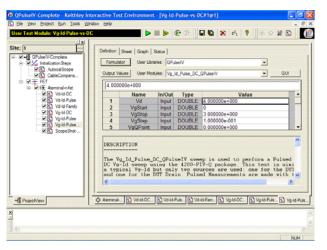

| Figure 4-47                | Default GUI definition for Vg-Id-Pulse-vs-DC                                                                   |          |

| Figure 4-48                | Typical graph for Vg-ld-Pulse-vs-DC                                                                            |          |

| Figure 4-49                | Typical graphical result for ScopeShot -FET                                                                    |          |

| Figure 4-50                | Pulse adapters, cables and hardware                                                                            |          |

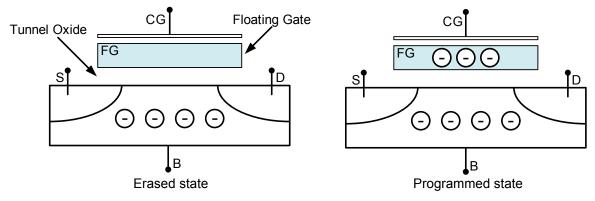

| Figure 4-51                | Cross section of a floating gate transistor in both the erased and programmed states                           |          |

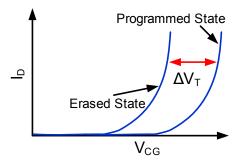

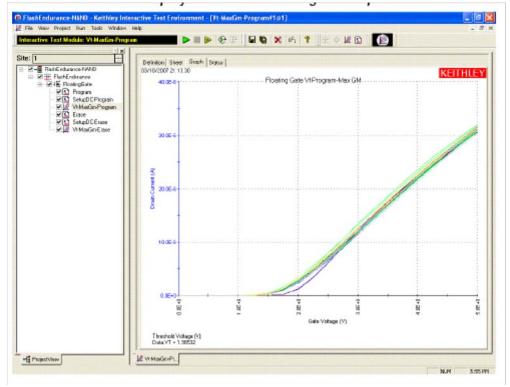

| Figure 4-52                | Graph of shifted voltage threshold, VT, due to stored charge on floating gate on a 1 bit (2 level) cell.       | 4-120    |

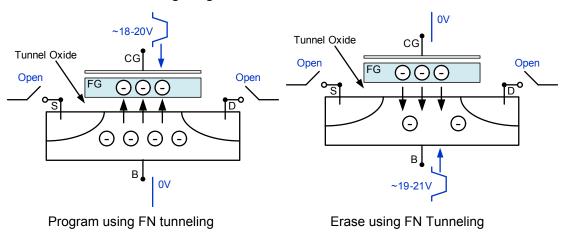

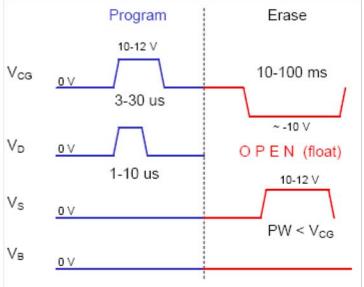

| Figure 4-53                | Fowler-Nordheim tunneling Program and Erase                                                                    |          |

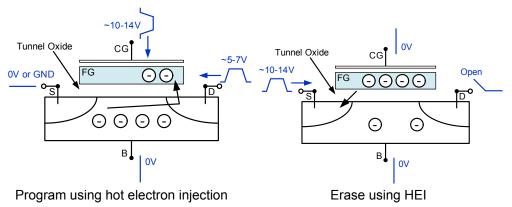

| Figure 4-54                | Hot Electron Injection (HEI) Program and Erase.                                                                |          |

| Figure 4-55                | Block diagram of an example flash test setup using a switch matrix                                             |          |

| Figure 4-56                | Block diagram of a flash test setup without using a switch matrix (direct connect)                             |          |

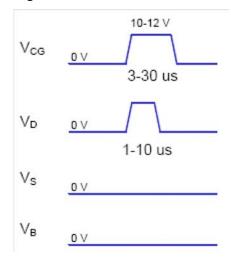

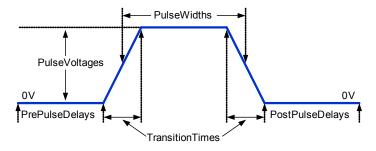

| Figure 4-57                | Program pulse waveforms for a floating gate DUT, with separate                                                 |          |

| 900 . 0.                   | pulse waveforms for the DUT gate, drain, source, and bulk                                                      | 4-123    |

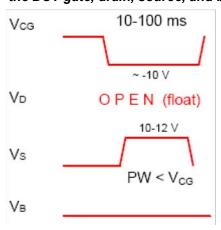

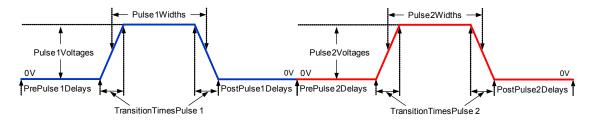

| Figure 4-58                | Example erase pulse waveforms for a floating gate DUT, with separate                                           |          |

| J                          | pulse waveforms for the DUT gate, drain, source, and bulk                                                      | 4-123    |

| Figure 4-59                | Program + Erase pulse waveforms for a floating gate DUT, with separate                                         |          |

| J                          | pulse waveforms for the DUT gate, drain, source, and bulk.                                                     | 4-124    |

| Figure 4-60                | Basic schematic of flash testing without a switch matrix                                                       | 4-124    |

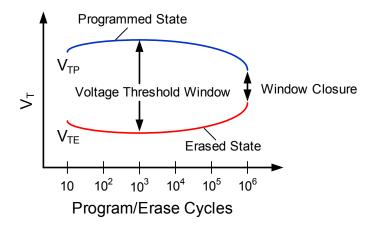

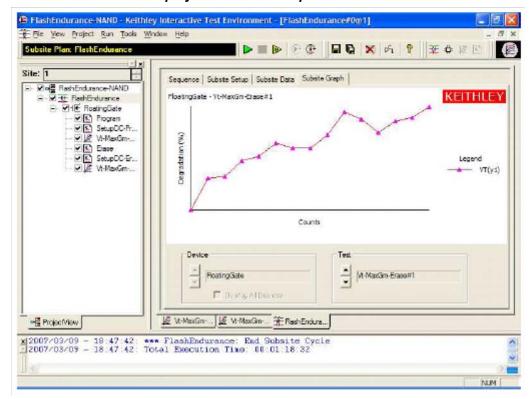

| Figure 4-61                | Example results of VT shift in an Endurance test on a NOR flash cell                                           | 4-125    |

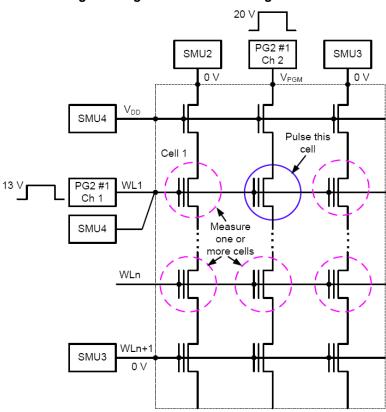

| Figure 4-62                | Disturb testing – configuration to test a single device                                                        | 4-126    |

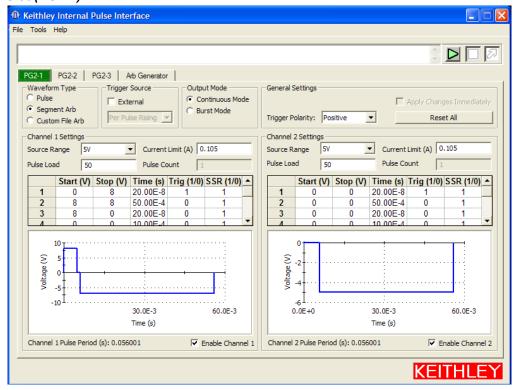

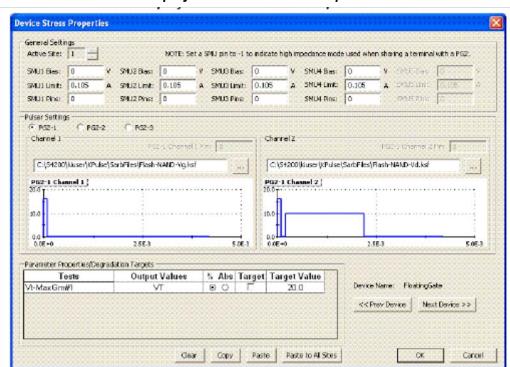

| Figure 4-63                | Kpulse showing the Segment Arb settings for the 4205-PG2 card in the lowest numbered-slot (PG2-1)              | 4-128    |

| Figure 4-64                | Kpulse showing the Segment Arb settings for the 4205-PG2 card in the                                           | 4-128    |

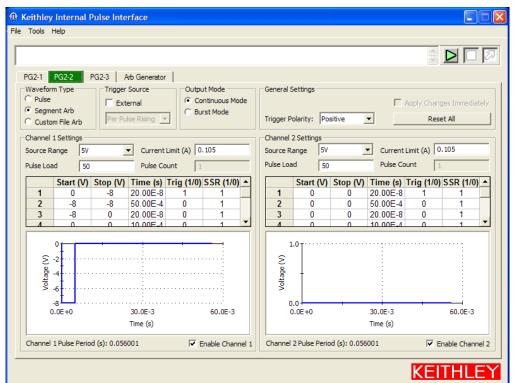

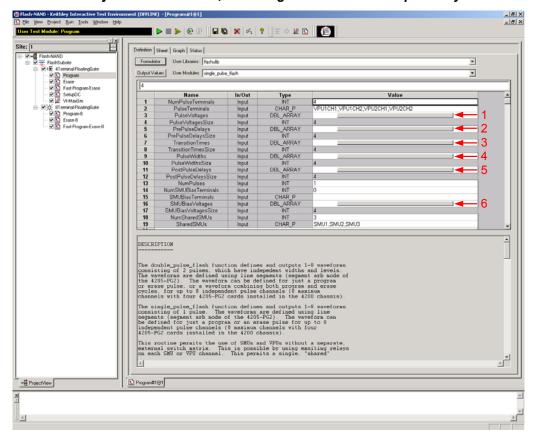

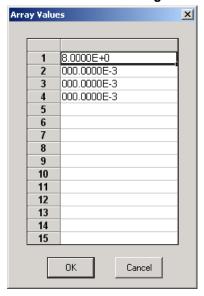

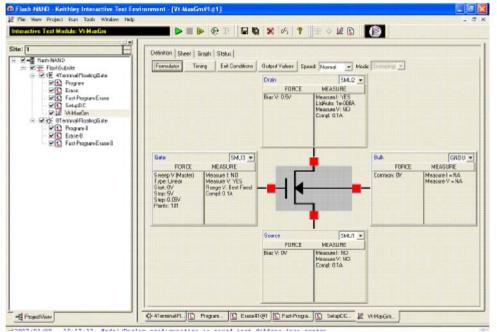

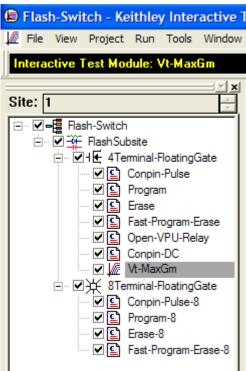

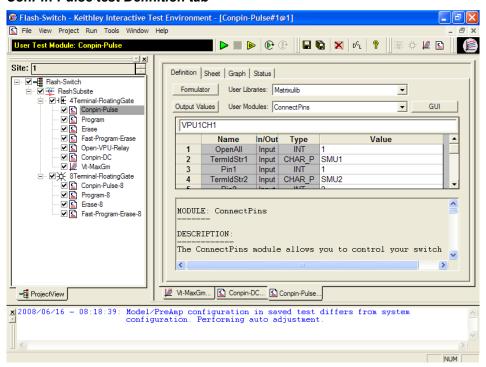

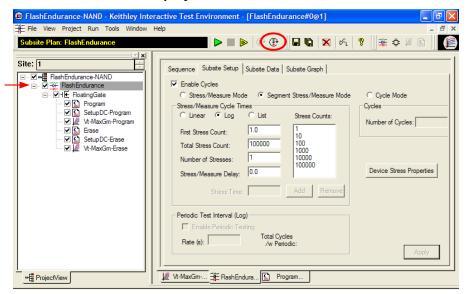

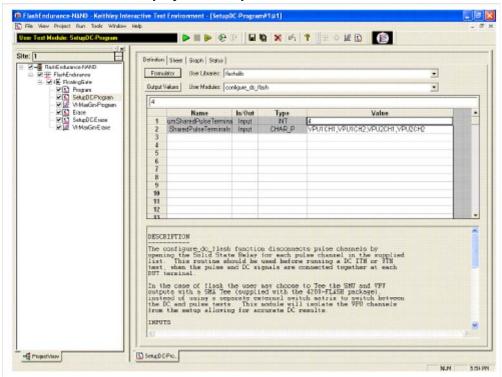

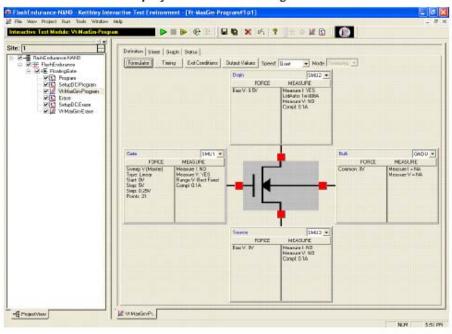

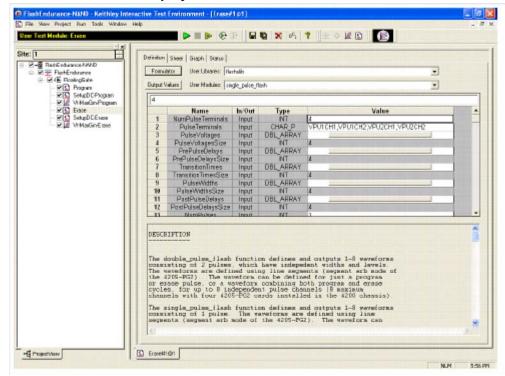

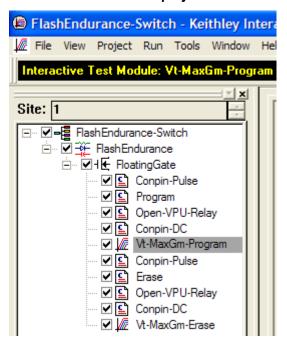

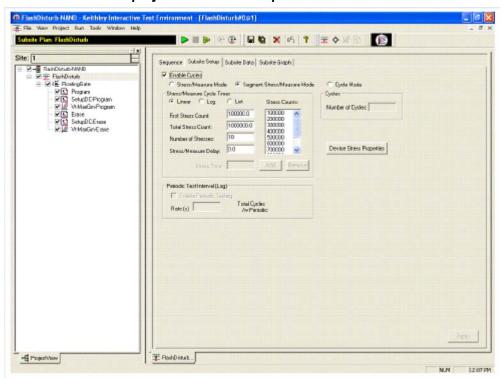

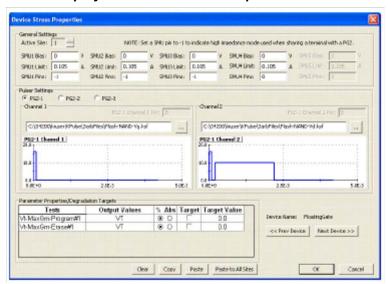

| Figure 4-65                | second lowest-numbered slot (PG2-2) Flash-NAND Project Definition Tab, including arrows for the 6 input arrays |          |