# TLA7Bxx Logic Analyzer Series Product Specifications & Performance Verification

**Technical Reference**

This document applies to TLA System Software Version 5.6 or higher

www.tektronix.com

077-0148-01

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are protected by national copyright laws and international treaty provisions.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### **Contacting Tektronix**

Tektronix, Inc. 14150 SW Karl Braun Drive P.O. Box 500 Beaverton, OR 97077 USA

For product information, sales, service, and technical support:

- In North America, call 1-800-833-9200.

- Worldwide, visit www.tektronix.com to find contacts in your area.

#### Warranty

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product. Parts, modules and replacement products used by Tektronix for warranty work may be new or reconditioned to like new performance. All replaced parts, modules and products become the property of Tektronix.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THE PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

[W2 - 15AUG04]

# **Table of Contents**

| Preface                                      | iii |

|----------------------------------------------|-----|

| Related Documentation                        | iii |

| Specifications and Characteristics           | 1   |

| Atmospheric Characteristics                  | 2   |

| TLA7Bxx Logic Analyzer Module Specifications | 3   |

| Performance Verification Procedures          | 13  |

| Test Equipment                               | 13  |

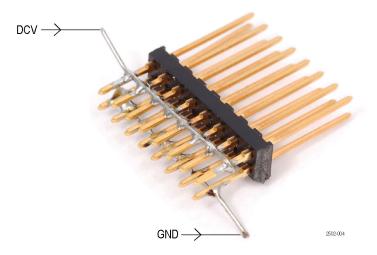

| Threshold Accuracy Test Fixture              | 14  |

| Threshold Accuracy Test                      | 15  |

| Setup & Hold Test                            | 17  |

| Functional Check Procedures                  | 21  |

| Functional Verification                      | 21  |

# **List of Tables**

| Table 1: Atmospheric characteristics  | 2  |

|---------------------------------------|----|

| Table 2: Input parameters with probes | 3  |

| Table 3: Analog output                | 4  |

| Table 4: Channel width and depth      | 4  |

| Table 5: Asynchronous sampling        | 5  |

| Table 6: Synchronous sampling         | 5  |

| Table 7: Demultiplex sampling         | 6  |

| Table 8: Source synchronous sampling  | 7  |

| Table 9: Clocking state machine       | 7  |

| Table 10: Trigger system              | 7  |

| Table 11: MagniVu feature             | 10 |

| Table 12: Merged modules              | 11 |

| Table 13: Data placement.             | 11 |

| Table 14: NVRAM                       | 12 |

| Table 15: Mechanical                  | 12 |

| Table 16: Test equipment              | 13 |

|                                       |    |

# Preface

This document lists the characteristics and specifications of the TLA7Bxx Logic Analyzer products. It also contains performance verification and functional check procedures for the TLA7ABxx Logic Analyzer module.

For information on safety summaries, environmental considerations, and compliance information, refer to the *Tektronix Logic Analyzer Family Product Safety and Compliance Instructions* (Tektronix part number 071-2591-xx).

## **Related Documentation**

TThe following table lists related documentation, available as printed documents or as PDF documents on the TLA Documentation CD and on the Tektronix Web site (www.tektronix.com). Other documentation, such as online help, is available on the instrument.

#### **Related documentation**

| ltem                                                            | Purpose                                                                                                |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| TLA Quick Start User manuals                                    | High-level operational overview                                                                        |

| Online Help                                                     | In-depth operation and UI help                                                                         |

| Installation Reference sheets                                   | High-level installation information                                                                    |

| Installation manuals                                            | Detailed first-time installation information                                                           |

| XYZs of Logic Analyzers                                         | Logic analyzer basics                                                                                  |

| Declassification and Securities instructions                    | Data security concerns specific to sanitizing<br>or removing memory devices from Tektronix<br>products |

| Application notes                                               | Collection of logic analyzer application specific notes                                                |

| Product Specifications & Performance<br>Verification procedures | TLA Product specifications and performance<br>verification procedures                                  |

| Field upgrade kits                                              | Upgrade information for your logic analyzer                                                            |

| Optional service manuals                                        | Self-service documentation for modules and mainframes                                                  |

### Preface

# **Specifications and Characteristics**

All specifications in this document are guaranteed unless noted *Typical*. Typical characteristics describe typical or average performance and provide useful reference information.

Specifications that are marked with the  $\nu$  symbol are checked directly (or indirectly) at your nearest Tektronix location or by using the performance verification procedures described in this document. (See page 13, *Performance Verification Procedures*.)

The performance limits in this specification are valid with these conditions:

- The instrument must be in an environment with temperature, altitude, humidity, and vibration within the operating limits described in these specifications.

- The instrument must have had a warm-up period of at least 20 minutes.

For modules, the performance limits in this specification are valid with these conditions:

- The module must be installed in a Tektronix Logic Analyzer Mainframe.

- The module must have been calibrated/adjusted at an ambient temperature between +18 °C and +28 °C.

# **Atmospheric Characteristics**

### Table 1: Atmospheric characteristics

| Characteristic    | Description                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature       | Operating (no media in CD or DVD drive of the mainframe)                                                                                                                                              |

|                   | +0 °C to +40 °C, 15 °C/hr maximum gradient, noncondensing (derated 1 °C per 305 m (1000 ft) above 1524 m (5000 ft) altitude)                                                                          |

|                   | Nonoperating (no media)                                                                                                                                                                               |

|                   | -20 °C to +60 °C, 15 °C/hr maximum gradient, noncondensing                                                                                                                                            |

| Relative Humidity | Operating (no media)                                                                                                                                                                                  |

|                   | 5% to 90% relative humidity at 30 °C, 75% relative humidity between 30 °C to 40 °C, noncondensing. Maximum wet bulb temperature: +29.4 °C (derates relative humidity to approximately 57% at +40 °C). |

|                   | Nonoperating (no media)                                                                                                                                                                               |

|                   | 5% to 90% relative humidity to 50 °C, noncondensing. Maximum wet bulb temperature: +40 °C (derates relative humidity to approximately 22% at +50 °C).                                                 |

| Altitude          | Operating                                                                                                                                                                                             |

|                   | To 3000 m (9843 ft), (derated 1 °C per 305 m (1000 ft) above 1524 m (5000 ft) altitude.                                                                                                               |

|                   | Nonoperating                                                                                                                                                                                          |

|                   | 12,000 m (39,370 ft )                                                                                                                                                                                 |

# **TLA7Bxx Logic Analyzer Module Specifications**

| Characteristic                    | Description                                                                             |

|-----------------------------------|-----------------------------------------------------------------------------------------|

| Threshold accuracy                | ± (35 mV + 1% of threshold voltage setting)                                             |

|                                   | For certification trace the characteristic                                              |

| Threshold range and step size     |                                                                                         |

| Large mode <sup>1</sup>           | Settable from -2.0 V to + 4.5 V in 5 mV steps                                           |

| Fast mode <sup>2</sup>            | Settable from -1.8 V to + 2.8 V in 5 mV steps                                           |

| P6960HS probe                     | Settable from -1.0 V to +2.25 V in 5 mv steps                                           |

| Threshold channel selection       | There is an independent threshold control for each signal.                              |

| Channel-to-channel skew           | ±40 ps maximum (module only)                                                            |

|                                   | Add:±60 ps for P6810, P6860, and P6880 probes                                           |

| Channel-to-channel skew (Typical) | For module only:±20 ps                                                                  |

| Merged module-to-module skew      | Inside slave modules (next to master module): +/-120ps (modules only)                   |

| (Typical)                         | Outside slave modules (not next to master module): +/-220ps (modules only)              |

| Sample uncertainty                |                                                                                         |

| Asynchronous                      | Sample period                                                                           |

| Synchronous                       | 20 ps                                                                                   |

| Input voltage range               |                                                                                         |

| Large mode <sup>1</sup>           | -2.0 V to + 5.5 V                                                                       |

| Fast mode <sup>2</sup>            | –2.5 V to + 3.5 V                                                                       |

| P6960HS probe                     | -1.25 V to +2.5 V                                                                       |

| Minimum slew rate (Typical)       | 0.2 V/ns                                                                                |

| Maximum operating signal swing    |                                                                                         |

| Large mode <sup>1</sup>           | 6.0 V <sub>p-p</sub>                                                                    |

| Fast mode <sup>2</sup>            | 2.0 V <sub>p-p</sub>                                                                    |

| Probe overdrive                   | (Relationship between signal amplitude and threshold setting)                           |

| Single ended probes               | ±150 mV (Large mode) <sup>1</sup>                                                       |

|                                   | ±100 mV (Fast mode) <sup>2</sup>                                                        |

|                                   | or $\pm 25\%$ of signal swing minimum required beyond threshold, whichever is greater   |

|                                   | ±50 mV or ±25% (P6960HS probe)                                                          |

| Differential probes               | V <sub>pos</sub> –V <sub>neg</sub> is ≥1250 mV <sub>p-p</sub> (Large mode) <sup>1</sup> |

|                                   | ±50 mV <sub>p-p</sub> (Fast mode) <sup>2</sup>                                          |

|                                   | V <sub>pos</sub> -V <sub>neg</sub> is ±50 mV <sub>p-p</sub> (P6960HS probe)             |

| Maximum nondestructive input      | ±15 V                                                                                   |

| signal to probe                   | ±7.5 V (P6960HS probe)                                                                  |

### Table 2: Input parameters with probes

| Characteristic                                                        | Description                                                                  |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------|

| Minimum input pulse width (single                                     | 200 ps (high-density and differential probes)                                |

| channel) <i>(Typical)</i>                                             | 250 ps (general purpose probe)                                               |

| Electrical delay from probe tip to input connector ( <i>Typical</i> ) | 7.70 ns $\pm$ 60 ps (general purpose, high-density, and differential probes) |

#### Table 2: Input parameters with probes (cont.)

1 The Large mode specification applies when the voltage swing of the input signal is over two volts; the performance can degrade in Large mode.

<sup>2</sup> The Fast mode specification applies when the voltage swing of the input signal is less than two volts; performance is not degraded in Fast mode.

#### Table 3: Analog output

| Characteristic                    | Description                                                                                                                     |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| Number of outputs                 | Four analog outputs regardless of the module width. Any four of the module's channels can be mapped to the four analog outputs. |  |

| Attenuation                       | 10X                                                                                                                             |  |

| Bandwidth (Typical)               | >3 GHz                                                                                                                          |  |

| Accuracy (Gain & Offset)(Typical) | ±(50 mV + 2% of signal amplitude)                                                                                               |  |

#### Table 4: Channel width and depth

| Characteristic            | Description                 |

|---------------------------|-----------------------------|

| Number of data channels   |                             |

| TLA7BB4, TLA7BC4          | 128 data, 8 clock/qualifier |

| TLA7BB3                   | 96 data, 6 clock/qualifier  |

| TLA7BB2                   | 64 data, 4 clock/qualifier  |

| Acquisition memory depth  |                             |

| TLA7BB2, TLA7BB3, TLA7BB4 | 64 M per channel, maximum   |

| TLA7BC4                   | 128 M per channel, maximum  |

| Characteristic                                     | Description                                                                                                                    |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| ✓ Internal sampling period                         | 1.25 ns, 800 MS, all channels                                                                                                  |

|                                                    | 625 ps, 1600 MS, all channels                                                                                                  |

|                                                    | 313 ps, 3200 MS, half channels                                                                                                 |

|                                                    | 157 ps, 6400 MS, quarter channels                                                                                              |

|                                                    | 50 ms is the slowest sampling rate. A 1-2-5 sequence is supported, but it starts with 157 ps.                                  |

| Minimum recognizable word<br>(across all channels) | Channel-to-channel skew + sample uncertainty                                                                                   |

|                                                    | Example for a P6860 high-density probe and a 1.25 ns sample period: 160 ps ( $\pm$ 60 ps) + 1.25 ns = 1.47 ns                  |

|                                                    | This specification applies only with asynchronous sampling. With synchronous sampling, the setup and hold window size applies. |

## Table 5: Asynchronous sampling

### Table 6: Synchronous sampling

| Characteristic                  | Description                                                                                                                                                                                        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronous sampling            |                                                                                                                                                                                                    |

| Master clock signals            | Clock signals                                                                                                                                                                                      |

| TLA7BB2                         | 4                                                                                                                                                                                                  |

| TLA7BB3                         | 4                                                                                                                                                                                                  |

| TLA7BB4, TLA7BC4                | 4                                                                                                                                                                                                  |

|                                 | You can enable any or all of the clock signals. For an enabled clock signal, you can select the rising, falling, or both edges as active clock edge(s). The clock signals are stored.              |

| Merged slave clock signals      | Clock signals                                                                                                                                                                                      |

| TLA7BB2                         | 4                                                                                                                                                                                                  |

| TLA7BB3                         | 4                                                                                                                                                                                                  |

| TLA7BB4, TLA7BC4                | 4                                                                                                                                                                                                  |

|                                 | (In addition to the two clock signals that the Master can send to merged slave modules, each slave module can have additional clocks.)                                                             |

|                                 | You can enable any or all of the clock signals For an enabled clock signal you can select the rising, falling, or both edges as active clock edge(s). Merging is allowed with all TLA7Bxx modules. |

| Qualifier signals               | Qualifier signals                                                                                                                                                                                  |

| TLA7BB2                         | 0                                                                                                                                                                                                  |

| TLA7BB3                         | 2                                                                                                                                                                                                  |

| TLA7BB4, TLA7BC4                | 4                                                                                                                                                                                                  |

|                                 | Qualifier signals are stored.                                                                                                                                                                      |

| u Single channel setup and hold | Single channel on single module 220 ps maximum                                                                                                                                                     |

| window size                     | Single channel on two to five merged modules 240 ps maximum                                                                                                                                        |

|                                 | If Deskew is used, add 20 ps (one oversampler step size) to the above numbers.                                                                                                                     |

## Table 6: Synchronous sampling (cont.)

| Characteristic              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup and hold window range | For each signal, the setup and hold window can be moved from +7.5 ns (setup time, typical) to -7.5 ns (setup time, typical) in 20 ps steps. You can shift the setup and hold window towards the setup region with 0 ns, 2.5 ns, 5 ns, or 7.5 ns. With a 0 ns shift the range is [+7.5, -7.5] ns, with a 2.5 ns shift the range is [+10,-5] ns, and with a shift of 7.5 ns the range is [+15,0]. The sample point selection region is the same setup and hold window. This is specified for the setup time with typical figures. Hold time follows the setup time by the Setup and hold window size. |

| Maximum synchronous clock   | 750 MHz, one sample point per clock, all channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rate                        | 750 MHz, two sample points per clock, all channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             | 750 MHz, four samples points per clock, half channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                             | 1400 MHz, one sample point per clock, all channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             | 1400 MHz, two sample points per clock, half channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Table 7: Demultiplex sampling

| Characteristic                                          | Description                                                  |

|---------------------------------------------------------|--------------------------------------------------------------|

| Base signals (2:1)                                      | A3[7:0], A2[7:0], A1[7:0], A0[7:0]                           |

| TLA7BB4, TLA7BC4                                        | C3[7:0], C2[7:0]                                             |

|                                                         | E3[7:0], E2[7:0]                                             |

|                                                         | CK3, CK2, CK1, CK0                                           |

| TLA7BB3                                                 | A3[7:0], A2[7:0], A1[7:0], A0[7:0]                           |

|                                                         | C3[7:0], C2[7:0]                                             |

|                                                         | CK1, CK0                                                     |

| TLA7BB2                                                 | A3[7:0], A2[7:0], A1[7:0], A0[7:0]                           |

|                                                         | CK3, CK1                                                     |

| Base signals (4:1)                                      | A3[7:0], A1[7:0]                                             |

| TLA7BB4, TLA7BC4                                        | C3[7:0]                                                      |

|                                                         | E3[7:0]                                                      |

|                                                         | CK3, CK1                                                     |

| TLA7BB3                                                 | A3[7:0], A1[7:0]                                             |

|                                                         | C3[7:0]                                                      |

|                                                         | CK1                                                          |

| TLA7BB2                                                 | A1[7:0]                                                      |

|                                                         | C3[7:0]                                                      |

| Time between demultiplex clock edges ( <i>Typical</i> ) | Same limitations as that for normal synchronous acquisition. |

| Characteristic                                        | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Source synchronous edge detectors per module          | 4                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Source synchronous edge detectors with merged modules | Slave modules have four source synchronous edge detectors. Two clocks are passed over from the master module.                                                                                                                                                                                                                                                                                          |  |

| Clock groups                                          | Four for both single module and for a merged system                                                                                                                                                                                                                                                                                                                                                    |  |

| Size of clock group valid FIFO                        | Four stages (source synchronous or other) clocks to occur before the clock that completes the Clock Group Valid signal for that group.                                                                                                                                                                                                                                                                 |  |

| Source synchronous clock alignment window             | Channel-to-channel skew only                                                                                                                                                                                                                                                                                                                                                                           |  |

| Source synchronous clock reset                        | The Clock Group Valid FIFOs can be reset in the following ways:                                                                                                                                                                                                                                                                                                                                        |  |

|                                                       | 1. By the overflow of a presettable (0-255) 8-bit counter that counts by the 1.25 ns system clock<br>or by the master heartbeat clock (synchronous or asynchronous). An active edge on a source<br>synchronous clock places the reset count to its preset value. The timing is such that an active<br>clock edge will clear the Clock Group Reset before arriving at the FIFO so that no data is lost. |  |

|                                                       | 2. By enabling an external reset. In this mode, one of the clock signals must be traded on the master module to act as a level-sensitive reset input. Any one of the clocks can be chosen and a polarity selection is available. This mode affects all Clock Group Complete circuits.                                                                                                                  |  |

|                                                       | The two modes cannot be intermixed; one or the other must be chosen.                                                                                                                                                                                                                                                                                                                                   |  |

## Table 8: Source synchronous sampling

#### Table 9: Clocking state machine

| Characteristic  | Description                                                                                                                                                                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pipeline delays | Each signal can be individually programmed with a pipeline delay of 0 through 31 active clock edges. The value held by the pipelines at the beginning of an acquisition can be preset high or low (all stages of a particular signal are forced to the same value). |

### Table 10: Trigger system

| Characteristic                                                | Description                                                                                                                                                      |                     |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Triggering resources                                          |                                                                                                                                                                  |                     |

| Word, range, and<br>channel-to-channel compare<br>recognizers | 24, word/range recognizers. The word recognizers can be traded off to form full width, double-bounded range recognizers. The following selections are available: |                     |

|                                                               | 24 word recognizers                                                                                                                                              | 0 range recognizers |

|                                                               | 21 word recognizers                                                                                                                                              | 1 range recognizer  |

|                                                               | 18 word recognizers                                                                                                                                              | 2 range recognizers |

|                                                               | 15 word recognizers                                                                                                                                              | 3 range recognizers |

|                                                               | 12 word recognizers                                                                                                                                              | 4 range recognizers |

|                                                               | 9 word recognizers                                                                                                                                               | 5 range recognizers |

|                                                               | 6 word recognizers                                                                                                                                               | 6 range recognizers |

|                                                               | 3 word recognizers                                                                                                                                               | 7 range recognizers |

|                                                               | 0 word recognizers                                                                                                                                               | 8 range recognizers |

## Table 10: Trigger system (cont.)

| Characteristic                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Range recognizer channel order                                | From most-significant probe group to least-significant probe group:                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                               | Missing channels for modules with fewer than 136 channels are omitted. When merged, the range recognition extends across the two modules. The master module contains the most-significant groups.                                                                                                                                                                                                                                                                                                                                           |

| TLA7BB4, TLA7BC4                                              | CK3 Q1 C3 C2 C1 C0 Q3 Q2 E3 E2 E1 E0 CK0 Q0 A3 A2 D3 D2 CK1 CK2 A1 A0 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TLA7BB3                                                       | CK3 Q1 C3 C2 C1 C0 CK0 Q0 A3 A2 D3 D2 CK1 CK2 A1 A0 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TLA7BB2                                                       | CK3 CK0 C3 C2 A3 A2 CK1 CK2 A1 A0 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Glitch detector (Asynchronous                                 | Any signal can be individually enabled to detect a glitch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| clock mode)                                                   | A glitch is two or more signal transitions on a signal between the Asynchronous sample points.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Minimum detectable glitch pulse                               | Minimum input pulse width (single-signal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| width (Typical)                                               | 200 ps for high-density probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                               | 250 ps for general purpose probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Setup and hold violation detector<br>(Synchronous clock mode) | Any signal can be individually enabled to detect a setup or hold violation. The window range is from 7.5 ns before the clock edge to 7.5 ns after the clock edge. This range may be shifted towards the positive region by 0 ns, 2.5 ns, 5 ns, or 7.5 ns. With a 0 ns shift the range is [+7.5,-7.5] ns, with a 2.5 ns shift it is [+10,-5] ns, with a 5 ns shift the range is [+12.5, -2.5] ns, and with a shift of 7.5 ns the range is [+15, 0] ns. The sample point selection region is the same as the setup and hold violation window. |

|                                                               | The size of each signal's setup/hold violation window can be individually programmed. The maximum width of the window (and granularity of adjustment) depends on the decimation setting:                                                                                                                                                                                                                                                                                                                                                    |

|                                                               | @ 20 ps granularity, max window size = 2.5 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                               | @ 40 ps granularity, max window size = 5.0 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                               | @ 80 ps granularity, max window size = 15 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                               | Any setup value is subject to variation of up to the skew specification. Any hold value is subject to variation of up to the skew specification.                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                               | Setup and hold detection is restricted to a group rather than individual signals; you can define individual groups for individual signals.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transition detector                                           | 24, any signal can be individually enabled or disabled to detect a rising or falling transition (or either) between the current valid data sample and the previous valid data sample.                                                                                                                                                                                                                                                                                                                                                       |

|                                                               | Transition detection is restricted to a group rather than individual signals; you can define individual groups for individual signals.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fast counter/timers                                           | Two fast counter/timers. Each is 48 bits wide and can be clocked up to 800 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                               | maximum count = 2 <sup>48</sup> –1 (including sign bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                               | maximum time = $\sim 3.5 \times 10^5$ sec = $\sim 4$ days                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                               | Zero clock TC latency, with zero reset latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                               | Counters can be reset, do nothing, incremented or decremented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                               | Timers can be reset, not changed, started or stopped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                               | ····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Signal In [3:0]                                               | Mainframe backplane input signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Characteristic                                                                                                                     | Description                                                                                                                                                                                                                           |  |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Trigger In                                                                                                                         | Mainframe backplane input signal that causes both the main acquisition and MagniVu acquisition to trigger (if they are not already triggered).                                                                                        |  |

| Active trigger resources                                                                                                           | 24 maximum (excluding the counter/timers and Signal In)                                                                                                                                                                               |  |

| Trigger states                                                                                                                     | 16                                                                                                                                                                                                                                    |  |

| Trigger state machine (TSM)                                                                                                        | DC to 800 MHz (1.25 ns)                                                                                                                                                                                                               |  |

| sequence rate                                                                                                                      | For data rates of 800 Mb/s or less, the TSM evaluates one data sample per TSM clock. For data rates greater than 800 Mb/s, the TSM evaluates multiple data samples per TSM clock up to the maximum acquired data rate.                |  |

| Trigger machine actions                                                                                                            |                                                                                                                                                                                                                                       |  |

| Main acquisition trigger                                                                                                           | Trigger the main acquisition memory.                                                                                                                                                                                                  |  |

| Main trigger position                                                                                                              | Programmable to any data sample (1.25 ns boundaries).                                                                                                                                                                                 |  |

| MagniVu trigger                                                                                                                    | Triggering of MagiVu memory is controlled by the main acquisition trigger machine.                                                                                                                                                    |  |

| MagniVu trigger position                                                                                                           | Programmable within 1.25 ns boundaries and separate from the main acquisition memory trigger position.                                                                                                                                |  |

| Increment and decrement counter                                                                                                    | Either of the two counter/timers used as counters can be incremented or decremented.                                                                                                                                                  |  |

| Snapshot recognizer                                                                                                                | Loads the current acquired data sample into the reference value of the word recognizer via a trigger machine action. All the data signals are loaded into their respective word recognizer reference register on a one-to-one manner. |  |

|                                                                                                                                    | With merged modules, the snapshot recognizer only works with the master module.                                                                                                                                                       |  |

| Snapshot load latency                                                                                                              | 325 ns                                                                                                                                                                                                                                |  |

| Start/stop timer                                                                                                                   | Either of the two counter/timers used as a timer can be started or stopped.                                                                                                                                                           |  |

| Reset counter/timer                                                                                                                | Either of the counter/timers can be reset.                                                                                                                                                                                            |  |

|                                                                                                                                    | When a timer is reset, the timer continues in the started or stopped state it was in prior to the reset.                                                                                                                              |  |

| Signal Out[3:0]                                                                                                                    | A signal sent to the backplane to be used by other modules.                                                                                                                                                                           |  |

| Trigger Out                                                                                                                        | A signal sent to the backplane to trigger other modules.                                                                                                                                                                              |  |

| Probe/Trigger/Backplane delay rela                                                                                                 | itionships                                                                                                                                                                                                                            |  |

| Delay time from probe tip to<br>multiplex Signal Out (TLA7Bxx<br>module front panel analog output<br>connector) ( <i>Typical</i> ) | 9.45 ns, ± 500 ps                                                                                                                                                                                                                     |  |

| Delay time from probe tip to trigger machine action ( <i>Typical</i> )                                                             | 1254 ns + Sample error                                                                                                                                                                                                                |  |

| Delay time from trigger machine                                                                                                    | Driving Signal 3:4 35 ns                                                                                                                                                                                                              |  |

| action to Signal Out (TLA7Bxx<br>module P2 connector) ( <i>Typical</i> )                                                           | Driving Signal 2:1 35 ns                                                                                                                                                                                                              |  |

| Delay time from trigger machine<br>action to Trigger Out (TLA7Bxx<br>module P2 connector) ( <i>Typical</i> )                       | 38 ns                                                                                                                                                                                                                                 |  |

### Table 10: Trigger system (cont.)

#### Table 10: Trigger system (cont.)

|                                                                                                                                                                                                                                                                                                                                                         | aracteristic Desc                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| le CLK <sup>1</sup>                                                                                                                                                                                                                                                                                                                                     | ay time from Signal In to trigger Signa<br>chine action (not used as ARM)<br><i>bical</i> )                           |

|                                                                                                                                                                                                                                                                                                                                                         | ay time from Signal In (TLA7Bxx 53 ns<br>dule P2 connector) to trigger<br>chine action (used as ARM)<br><i>bical)</i> |

|                                                                                                                                                                                                                                                                                                                                                         | ay time from Trigger In 38 ns<br>A7Bxx module P2 connector)<br>rigger machine action <i>(Typical)</i>                 |

|                                                                                                                                                                                                                                                                                                                                                         | rage control                                                                                                          |

| ition can use any of the trigger<br>fined in the current trigger                                                                                                                                                                                                                                                                                        |                                                                                                                       |

| initially turned on (default),                                                                                                                                                                                                                                                                                                                          | Globa<br>or off.                                                                                                      |

| Storage may be turned on or off, or only the current sample may be stored. Event storage control overrides any global storage commands.                                                                                                                                                                                                                 |                                                                                                                       |

| l sample.                                                                                                                                                                                                                                                                                                                                               | ck storage When                                                                                                       |

| k storage is disallowed when                                                                                                                                                                                                                                                                                                                            | is allows users to store a group This h<br>amples around a valid data glitch<br>aple when storage control is<br>d.)   |

| Glitch violation information can be stored to acquisition memory with each data sample when asynchronous sampling is used. The acquisition data storage size is reduced by half when this mode is enabled (the other half holds the violation information). The fastest asynchronous sampling rate when Glitch violation storage is enabled is 1.25 ns. |                                                                                                                       |

| The acquisition memory can be enabled to store setup and hold violation information with each data sample when synchronous sampling is used. The acquisition data storage size is reduced by one half when this mode is enabled (the other half holds the violation information). The maximum sync clock rate in this mode is 750 MHz.                  |                                                                                                                       |

| on data storage siz                                                                                                                                                                                                                                                                                                                                     | data s<br>by on                                                                                                       |

1 Sample CLK is the delay due to logic analyzer sampling. For asynchronous sampling, this delay is equal to the internal sampling period. For synchronous sampling, this delay is equal to time until the next active clock edge.

#### Table 11: MagniVu feature

| Characteristic          | Description                                                                                                                                                                                                                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|